# 5-V DUAL RS-232 LINE DRIVER/RECEIVER WITH $\pm$ 15-kV ESD PROTECTION

- ESD Protection for RS-232 Bus Pins

±15-kV Human-Body Model

- Meets or Exceeds the Requirements of TIA/EIA-232-F and ITU v.28 Standards

- Operates at 5-V V<sub>CC</sub> Supply

- Operates Up To 120 kbit/s

- External Capacitors . . .  $4 \times 0.1 \mu F$

- Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

- Applications

- Battery-Powered Systems, PDAs, Notebooks, Laptops, Palmtop PCs, and Hand-Held Equipment

#### D, DW, N, OR PW PACKAGE (TOP VIEW) 16 VCC C1+ ∏ 1 V+ **1** 2 15 GND C1− []3 14 DOUT1 C2+ [] 4 13 RIN1 C2- [ 5 12∏ ROUT1 V−¶6 11 DIN1 10 DIN2 DOUT2 I 7 9 ROUT2 RIN2 8

## description/ordering information

The SP202 device consists of two line drivers, two line receivers, and a dual charge-pump circuit with  $\pm 15$ -kV ESD protection pin to pin (serial-port connection pins, including GND). The device meets the requirements of TIA/EIA-232-F and provides the electrical interface between an asynchronous communication controller and the serial-port connector. The charge pump and four small external capacitors allow operation from a single 5-V supply. The device operates at data signaling rates up to 120 kbit/s and a maximum of 30-V/ $\mu$ s driver output slew rate.

#### **Function Tables**

#### **EACH DRIVER**

| INPUT<br>D <sub>IN</sub> | OUTPUT<br>DOUT |

|--------------------------|----------------|

| L                        | Н              |

| Н                        | L              |

H = high level, L = low level

#### **EACH RECEIVER**

| INPUT<br>R <sub>IN</sub> | OUTPUT<br>ROUT |

|--------------------------|----------------|

| L                        | Н              |

| Н                        | L              |

| Open                     | Н              |

H = high level, L = low level, Open = input disconnected or connected driver off

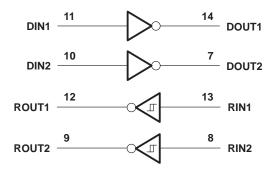

# logic diagram (positive logic)

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)              | –0.3 V to 6 V                    |

|-----------------------------------------------------------------|----------------------------------|

| Positive charge pump voltage range, V+ (see Note 1)             | V <sub>CC</sub> – 0.3 V to 14 V  |

| Negative charge pump voltage range, V- (see Note 1)             | –14 V to 0.3 V                   |

| Input voltage range, V <sub>I</sub> : Drivers                   | 0.3 V to V+ + 0.3 V              |

| Receivers                                                       | ±30 V                            |

| Output voltage range, V <sub>O</sub> : Drivers                  | V0.3 V to V+ + 0.3 V             |

| Receivers                                                       | 0.3 V to V <sub>CC</sub> + 0.3 V |

| Short-circuit duration: D <sub>OUT</sub>                        | Continuous                       |

| Package thermal impedance, θ <sub>JA</sub> (see Notes 2 and 3): | D package 73°C/W                 |

|                                                                 | DW package 57°C/W                |

|                                                                 | N package 67°C/W                 |

|                                                                 | PW package 108°C/W               |

| Operating virtual junction temperature, T <sub>J</sub>          |                                  |

| Storage temperature range, T <sub>stg</sub>                     | –65°C to 150°C                   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. All voltages are with respect to network GND.

- 2. Maximum power dissipation is a function of  $T_J(max)$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any allowable ambient temperature is  $P_D = (T_J(max) T_A)/\theta_{JA}$ . Operating at the absolute maximum  $T_J$  of 150°C can affect reliability.

- 3. The package thermal impedance is calculated in accordance with JESD 51-7.

### recommended operating conditions (see Note 4 and Figure 4)

|                 |                                 |                 |     | NOM | MAX | UNIT |

|-----------------|---------------------------------|-----------------|-----|-----|-----|------|

|                 | Supply voltage                  |                 | 4.5 | 5   | 5.5 | V    |

| VIH             | Driver high-level input voltage | D <sub>IN</sub> | 2   |     |     | V    |

| V <sub>IL</sub> | Driver low-level input voltage  | D <sub>IN</sub> |     |     | 0.8 | V    |

| .,              | Driver input voltage            | D <sub>IN</sub> | 0   |     | 5.5 |      |

| VI              | Receiver input voltage          |                 | -30 |     | 30  | V    |

| _               | Operating free-air temperature  | SP202C          | 0   |     | 70  | 00   |

| TA              |                                 | SP202I          | -40 |     | 85  | °C   |

NOTE 4: Test conditions are C1–C4 = 0.1  $\mu$ F at V<sub>CC</sub> = 5 V  $\pm$  0.5 V.

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Note 4 and Figure 4)

| PARAMETER          | TEST CONDITIONS                | MIN TYP‡ | MAX | UNIT |

|--------------------|--------------------------------|----------|-----|------|

| ICC Supply current | No load, V <sub>CC</sub> = 5 V | 8        | 15  | mA   |

<sup>&</sup>lt;sup>‡</sup> All typical values are at  $V_{CC}$  = 5 V, and  $T_A$  = 25°C.

NOTE 4: Test conditions are C1–C4 = 0.1  $\mu F$  at V\_CC = 5 V  $\pm$  0.5 V.

#### **DRIVER SECTION**

#### electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Note 4 and Figure 4)

| PARAMETER        |                              | TEST CONDITIONS                                           |                       | MIN | TYP | MAX  | UNIT |

|------------------|------------------------------|-----------------------------------------------------------|-----------------------|-----|-----|------|------|

| Vон              | High-level output voltage    | D <sub>OUT</sub> at R <sub>L</sub> = 3 k $\Omega$ to GND, | D <sub>IN</sub> = GND | 5   | 9   |      | V    |

| VOL              | Low-level output voltage     | $D_{OUT}$ at $R_L = 3 \text{ k}\Omega$ to GND,            | $D_{IN} = V_{CC}$     | -5  | -9  |      | V    |

| lН               | High-level input current     | $V_I = V_{CC}$                                            |                       |     | 15  | 200  | μΑ   |

| IIL              | Low-level input current      | V <sub>I</sub> at 0 V                                     |                       |     | -15 | -200 | μΑ   |

| los <sup>‡</sup> | Short-circuit output current | V <sub>CC</sub> = 5.5 V,                                  | V <sub>O</sub> = 0 V  |     | ±10 | ±60  | mA   |

| r <sub>O</sub>   | Output resistance            | $V_{CC}$ , V+, and V- = 0 V,                              | V <sub>O</sub> = ±2 V | 300 |     |      | Ω    |

NOTE 4: Test conditions are C1–C4 = 0.1  $\mu$ F at V<sub>CC</sub> = 5 V  $\pm$  0.5 V.

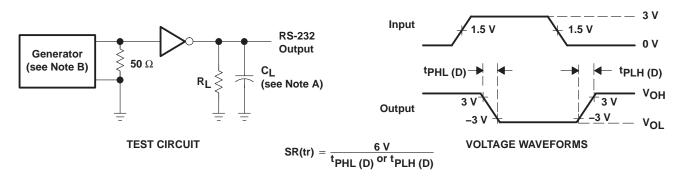

#### switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Note 4 and Figure 4)

| PARAMETER            |                                                      | TEST C                                                               | ONDITIONS                                                | MIN | TYP <sup>†</sup> | MAX | UNIT   |

|----------------------|------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------|-----|------------------|-----|--------|

|                      | Maximum data rate                                    | C <sub>L</sub> = 50 to1000 pF,<br>One D <sub>OUT</sub> switching,    | $R_L$ = 3 kΩ to 7 kΩ,<br>See Figure 1                    | 120 |                  |     | kbit/s |

| <sup>t</sup> PLH (D) | Propagation delay time, low- to high-level output    | C <sub>L</sub> = 2500 pF,<br>All drivers loaded,                     | $R_L = 3 kΩ$ ,<br>See Figure 1                           |     | 2                |     | μs     |

| <sup>t</sup> PHL (D) | Propagation delay time,<br>high- to low-level output | C <sub>L</sub> = 2500 pF,<br>All drivers loaded,                     | $R_L = 3 \text{ k}\Omega$ ,<br>See Figure 1              |     | 2                |     | μs     |

| t <sub>sk(p)</sub>   | Pulse skew§                                          | $C_L = 150 \text{ pF to } 2500 \text{ pF},$                          | $R_L$ = 3 kΩ to 7 kΩ,<br>See Figure 2                    |     | 300              |     | ns     |

| SR(tr)               | Slew rate, transition region (see Figure 1)          | $C_L = 50 \text{ pF to } 1000 \text{ pF,}$<br>$V_{CC} = 5 \text{ V}$ | $R_L = 3 \text{ k}\Omega \text{ to } 7 \text{ k}\Omega,$ | 3   | 6                | 30  | V/µs   |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ , and  $T_A = 25^{\circ}\text{C}$ .

#### **ESD** protection

| PIN       | TEST CONDITIONS  | TYP | UNIT |

|-----------|------------------|-----|------|

| Dout, RIN | Human-Body Model | ±15 | kV   |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, and T<sub>A</sub> = 25°C. ‡ Short-circuit durations should be controlled to prevent exceeding the device absolute power-dissipation ratings, and not more than one output should be shorted at a time.

<sup>§</sup> Pulse skew is defined as  $|tp_{LH} - tp_{HL}|$  of each channel of the same device. NOTE 4: Test conditions are C1–C4 = 0.1  $\mu$ F at  $V_{CC}$  = 5 V  $\pm$  0.5 V.

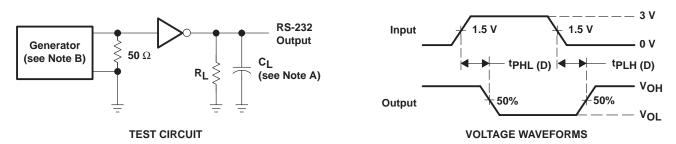

#### **RECEIVER SECTION**

#### electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Note 4 and Figure 4)

| PARAMETER        |                                                         | TEST CONDITIONS                              |                       | MIN  | TYP†                   | MAX | UNIT |

|------------------|---------------------------------------------------------|----------------------------------------------|-----------------------|------|------------------------|-----|------|

| Vон              | High-level output voltage                               | $I_{OH} = -1 \text{ mA}$                     |                       | 3.5V | V <sub>CC</sub> -0.4 V |     | V    |

| VOL              | Low-level output voltage                                | I <sub>OL</sub> = 1.6 mA                     |                       |      |                        | 0.4 | V    |

| V <sub>IT+</sub> | Positive-going input threshold voltage                  | $V_{CC} = 5 V$ ,                             | T <sub>A</sub> = 25°C |      | 1.7                    | 2.4 | V    |

| VIT-             | Negative-going input threshold voltage                  | $V_{CC} = 5 V$ ,                             | T <sub>A</sub> = 25°C | 0.8  | 1.2                    |     | V    |

| V <sub>hys</sub> | Input hysteresis (V <sub>IT+</sub> - V <sub>IT-</sub> ) |                                              |                       | 0.2  | 0.5                    | 1   | V    |

| rį               | Input resistance                                        | $V_I = \pm 3 \text{ V to } \pm 25 \text{ V}$ |                       | 3    | 5                      | 7   | kΩ   |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5$  V, and  $T_A = 25$ °C.

NOTE 4: Test conditions are C1–C4 = 0.1  $\mu$ F at V<sub>CC</sub> = 5 V  $\pm$  0.5 V.

#### switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Note 4 and Figure 3)

|                      | PARAMETER                                         | TEST CONDITIONS         | MIN | TYP <sup>†</sup> | MAX | UNIT |

|----------------------|---------------------------------------------------|-------------------------|-----|------------------|-----|------|

| <sup>t</sup> PLH (R) | Propagation delay time, low- to high-level output | C <sub>L</sub> = 150 pF |     | 0.5              | 10  | μs   |

| <sup>t</sup> PHL (R) | Propagation delay time, high- to low-level output | C <sub>L</sub> = 150 pF |     | 0.5              | 10  | μs   |

| tsk(p)               | Pulse skew <sup>‡</sup>                           |                         |     | 300              |     | ns   |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5$  V, and  $T_A = 25$ °C.

‡ Pulse skew is defined as  $|t_{PLH} - t_{PHL}|$  of each channel of the same device. NOTE 4: Test conditions are C1–C4 = 0.1  $\mu$ F, at V<sub>CC</sub> = 5 V  $\pm$  0.5 V.

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A.  $C_L$  includes probe and jig capacitance.

B. The pulse generator has the following characteristics: PRR = 120 kbit/s,  $Z_O = 50 \Omega$ , 50% duty cycle,  $t_f \le 10$  ns.  $t_f \le 10$  ns.

Figure 1. Driver Slew Rate

#### PARAMETER MEASUREMENT INFORMATION

- NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

- B. The pulse generator has the following characteristics: PRR = 120 kbit/s,  $Z_O = 50 \Omega$ , 50% duty cycle,  $t_f \le 10$  ns.

Figure 2. Driver Pulse Skew

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

B. The pulse generator has the following characteristics:  $Z_O = 50~\Omega$ , 50% duty cycle,  $t_\Gamma \le 10~\text{ns}$ .

Figure 3. Receiver Propagation Delay Times

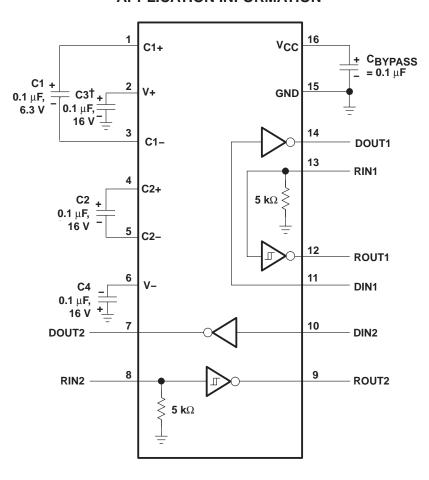

## **APPLICATION INFORMATION**

$^\dagger\text{C3}$  can be connected to  $\text{V}_{\mbox{CC}}$  or GND.

NOTES: A. Resistor values shown are nominal.

B. Nonpolarized ceramic capacitors are acceptable. If polarized tantalum or electrolytic capacitors are used, they should be connected as shown.

Figure 4. Typical Operating Circuit and Capacitor Values

#### **APPLICATION INFORMATION**

#### capacitor selection

The capacitor type used for C1–C4 is not critical for proper operation. The SP202 requires 0.1-  $\mu$ F capacitors, although capacitors up to 10  $\mu$ F can be used without harm. Ceramic dielectrics are suggested for the 0.1- $\mu$ F capacitors. When using the minimum recommended capacitor values, make sure the capacitance value does not degrade excessively as the operating temperature varies. If in doubt, use capacitors with a larger (e.g., 2×) nominal value. The capacitors' effective series resistance (ESR), which usually rises at low temperatures, influences the amount of ripple on V+ and V-.

Use larger capacitors (up to 10  $\mu$ F) to reduce the output impedance at V+ and V-.

Bypass  $V_{CC}$  to ground with at least 0.1  $\mu$ F. In applications sensitive to power-supply noise generated by the charge pumps, decouple  $V_{CC}$  to ground with a capacitor the same size as (or larger than) the charge-pump capacitors (C1–C4).

#### **ESD** protection

SP202 devices have standard ESD protection structures incorporated on the pins to protect against electrostatic discharges encountered during assembly and handling. In addition, the RS232 bus pins (driver outputs and receiver inputs) of these devices have an extra level of ESD protection. Advanced ESD structures were designed to successfully protect these bus pins against ESD discharge of ±15-kV when powered down.

#### **ESD** test conditions

Stringent ESD testing is performed by TI, based on various conditions and procedures. Please contact TI for a reliability report that documents test setup, methodology, and results.

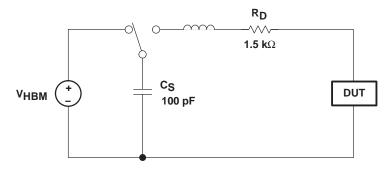

#### **Human-Body Model (HBM)**

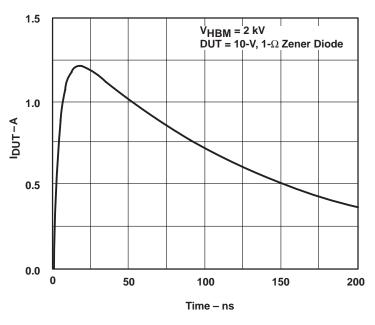

The HBM of ESD testing is shown in Figure 5. Figure 6 shows the current waveform that is generated during a discharge into a low impedance. The model consists of a 100-pF capacitor, charged to the ESD voltage of concern, and subsequently discharged into the device under test (DUT) through a 1.5-k $\Omega$  resistor.

Figure 5. HBM ESD Test Circuit

#### **APPLICATION INFORMATION**

Figure 6. Typical HBM Current Waveform

## Machine Model (MM)

The MM ESD test applies to all pins using a 200-pF capacitor with no discharge resistance. The purpose of the MM test is to simulate possible ESD conditions that can occur during the handling and assembly processes of manufacturing. In this case, ESD protection is required for all pins, not just RS-232 pins. However, after PC board assembly, the MM test no longer is as pertinent to the RS-232 pins.

# Important statement:

Huaguan Semiconductor Co,Ltd. reserves the right to change the products and services provided without notice. Customers should obtain the latest relevant information before ordering, and verify the timeliness and accuracy of this information.

Customers are responsible for complying with safety standards and taking safety measures when using our products for system design and machine manufacturing to avoid potential risks that may result in personal injury or property damage.

Our products are not licensed for applications in life support, military, aerospace, etc., so we do not bear the consequences of the application of these products in these fields.

Our documentation is only permitted to be copied without any tampering with the content, so we do not accept any responsibility or liability for the altered documents.