## ZGAD250S12 12 位单通道高速模数转换器 (ADC)

### 1 特性

- 采样率 10Msps 至 250Msps

- 1.8V 单电压供电

- 输出: DDR LVDS

- 输入范围: 1.5Vpp

- 信噪比 (SNR): 68dB

- 无杂散动态范围 (SFDR): 85dB

- 全功率带宽: 1500MHz

- 全速率运行功耗: 362mW

- 单通道采样

- 可选时钟占空比稳定器

- 节能的低功耗模式和休眠模式

- 可配置的 SPI 串行口 (支持 1.8V 到 3.6V)

- 封装: QFN40

- 工作温度: -40°C 至 85°C

- 测试测量仪器

- 医疗设备

- 视频设备

- 蜂窝基站

- 激光雷达

### 3 综述

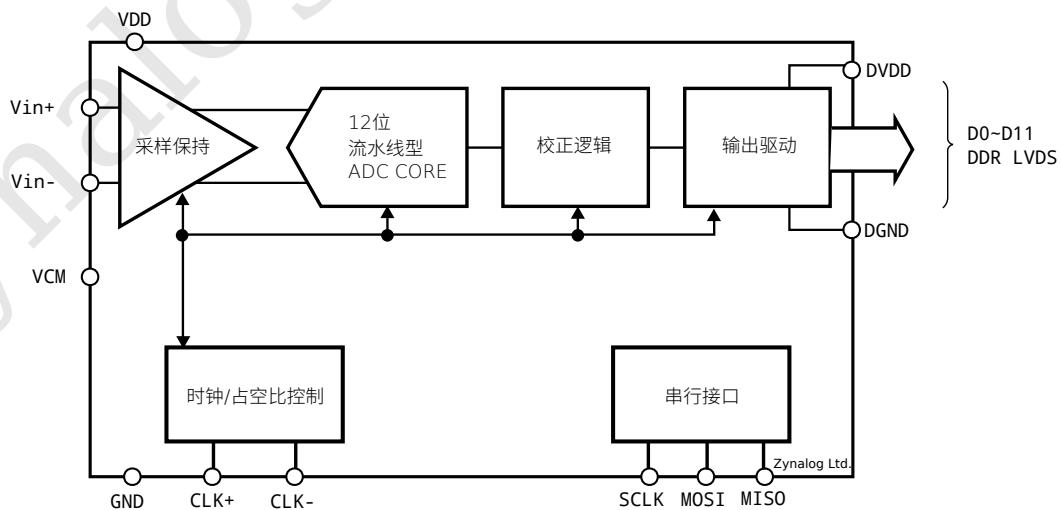

ZGAD250S12 是单通道 12 位 250Msps 的模数转换器 (ADC)。设计应用于高频率, 宽动态范围信号的数字化。系列具有包括 68dB 信噪比 (SNR) 和 85dB 无杂散动态范围 (SFDR) 的性能, 完美适用于高要求的信号链应用。1500MHz 的输入带宽允许 ADC 在高频下采样的同时保持良好性能。延迟只有六个时钟周期。静态特性包括 +/- 0.6LSB 积分非线性误差 (INL) (典型值), +/- 0.25LSB 微分非线性误差 (DNL) (典型值)。时钟输入可以用正弦波、PECL、LVDS、TTL 或 CMOS 输入差分驱动。可选时钟占空比稳定器允许在很宽的时钟占空比范围内全速工作的高性能表现。

### 2 应用领域

- 信号链

图 1: 基本功能框架

**目录**

|                                     |           |                                            |           |

|-------------------------------------|-----------|--------------------------------------------|-----------|

| <b>1 特性</b>                         | <b>1</b>  | <b>13 关于微格</b>                             | <b>19</b> |

| <b>2 应用领域</b>                       | <b>1</b>  | 13.1 公司简介 . . . . .                        | 19        |

| <b>3 综述</b>                         | <b>1</b>  | 13.2 联系方式 . . . . .                        | 19        |

| <b>4 性能参数</b>                       | <b>4</b>  |                                            |           |

| <b>5 性能特性</b>                       | <b>5</b>  |                                            |           |

| <b>6 绝对最大额定值</b>                    | <b>6</b>  |                                            |           |

| <b>7 引脚配置</b>                       | <b>7</b>  |                                            |           |

| <b>8 时序图</b>                        | <b>10</b> |                                            |           |

| <b>9 应用信息</b>                       | <b>11</b> |                                            |           |

| 9.1 模拟信号输入 . . . . .                | 11        | 1 基本功能框架 . . . . .                         | 1         |

| 9.2 时钟信号 . . . . .                  | 12        | 2 典型性能特性 . . . . .                         | 5         |

| 9.3 时钟占空比稳定器 . . . . .              | 12        | 3 线性特性 . . . . .                           | 5         |

| 9.4 LVDS 数字输出 . . . . .             | 12        | 4 正面视图 6mmx6mmQFN40 封装 . . . . .           | 7         |

| 9.4.1 数据输出格式 . . . . .              | 13        | 5 数据输出 . . . . .                           | 10        |

| 9.4.2 随机发生器 . . . . .               | 13        | 6 输入信号满量程示意图 . . . . .                     | 11        |

| 9.4.3 输出时钟 (CLKOUT) 的相位移动 . . . . . | 13        | 7 输入频率在第一个 Nyquist Zone 的推荐前端电路 . . . . .  | 11        |

| 9.4.4 交替位极性 . . . . .               | 13        | 8 输入频率大于第一个 Nyquist Zone 的推荐前端电路 . . . . . | 11        |

| 9.4.5 数字输出测试模式 . . . . .            | 14        | 9 使用单端转差分的高速运放的推荐前端电路 (隔离直流信号) . . . . .   | 11        |

| 9.4.6 输出关闭 . . . . .                | 14        | 10 使用单端转差分的高速运放的推荐前端电路 . . . . .           | 12        |

| 9.5 低功耗模式 . . . . .                 | 14        | 11 模拟时钟信号输入 . . . . .                      | 12        |

| 9.6 休眠模式 . . . . .                  | 14        | 12 LVDS/PECL 时钟信号输入 . . . . .              | 12        |

| 9.7 软件复位 . . . . .                  | 14        | 13 相位偏移 . . . . .                          | 13        |

| <b>10 SPI 和控制寄存器</b>                | <b>15</b> | 14 SPI 时序图 . . . . .                       | 15        |

| 10.1 SPI . . . . .                  | 15        | 15 封装信息 . . . . .                          | 18        |

| 10.2 控制寄存器 . . . . .                | 16        |                                            |           |

| <b>11 封装</b>                        | <b>18</b> |                                            |           |

| <b>12 订购信息</b>                      | <b>18</b> |                                            |           |

**插图**

|                                            |    |

|--------------------------------------------|----|

| 1 基本功能框架 . . . . .                         | 1  |

| 2 典型性能特性 . . . . .                         | 5  |

| 3 线性特性 . . . . .                           | 5  |

| 4 正面视图 6mmx6mmQFN40 封装 . . . . .           | 7  |

| 5 数据输出 . . . . .                           | 10 |

| 6 输入信号满量程示意图 . . . . .                     | 11 |

| 7 输入频率在第一个 Nyquist Zone 的推荐前端电路 . . . . .  | 11 |

| 8 输入频率大于第一个 Nyquist Zone 的推荐前端电路 . . . . . | 11 |

| 9 使用单端转差分的高速运放的推荐前端电路 (隔离直流信号) . . . . .   | 11 |

| 10 使用单端转差分的高速运放的推荐前端电路 . . . . .           | 12 |

| 11 模拟时钟信号输入 . . . . .                      | 12 |

| 12 LVDS/PECL 时钟信号输入 . . . . .              | 12 |

| 13 相位偏移 . . . . .                          | 13 |

| 14 SPI 时序图 . . . . .                       | 15 |

| 15 封装信息 . . . . .                          | 18 |

**表格**

|                         |    |

|-------------------------|----|

| 1 文档版本 . . . . .        | 3  |

| 2 电源性能参数 . . . . .      | 4  |

| 3 转换性能参数 . . . . .      | 4  |

| 4 数字输出参数 . . . . .      | 4  |

| 5 绝对最大额定值 . . . . .     | 6  |

| 6 引脚定义和功能说明 . . . . .   | 7  |

| 7 数据输出格式 . . . . .      | 13 |

| 8 复位寄存器 . . . . .       | 16 |

| 9 掉电寄存器 . . . . .       | 16 |

| 10 时序寄存器 . . . . .      | 16 |

| 11 输出模式寄存器 . . . . .    | 17 |

| 12 数字信号格式寄存器 . . . . .  | 17 |

| 13 ADC 系列产品信息 . . . . . | 18 |

表 1: 文档版本

| 版本号  | 说明                 |

|------|--------------------|

| 2.02 | 更新 OFB, CLKB 的时序图。 |

| 2.03 | 修正 VDD 的一个描述错误。    |

| 2.04 | 更新应用设计。            |

| 2.05 | 修正一个引脚错误。          |

| 2.06 | 修正频谱图频率与描述不符的错误。   |

Zynalog Semiconductor

## 4 性能参数

表 2: 电源性能参数

| 标志         | 说明                | 最小  | 典型    | 最大  | 单位 |

|------------|-------------------|-----|-------|-----|----|

| 电源         |                   |     |       |     |    |

| VDD        | 模拟电源输入电压          | 1.7 | 1.8   | 1.9 | V  |

| DVDD       | 数字电源输入电压          | 1.7 | 1.8   | 1.9 | V  |

| I_VDD      | 模拟电源输入电流          |     | 165   | 168 | mA |

| I_DVDD     | 数字电源输入电流          |     | 37    |     | mA |

| 功耗         |                   |     |       |     |    |

| P_1.75     | 1.75mA LVDS 输出时功耗 |     | 328   |     | mW |

| P_3.5      | 3.5mA LVDS 输出时功耗  |     | 362   |     | mW |

| P_lowpower | 低功耗模式             |     | 102.5 |     | mW |

| P_sleep    | 睡眠模式              |     | 0.65  |     | mW |

表 3: 转换性能参数

| 标志           | 说明      | 最小   | 典型       | 最大   | 单位  |

|--------------|---------|------|----------|------|-----|

| INL          | 积分非线性   | -2   | +/-0.6   | +2   | LSB |

| DNL          | 微分非线性   | -0.6 | +/- 0.25 | +0.6 | LSB |

| Offset Error | 偏置误差    | -13  | +/-5     | +13  | mV  |

| Gain Error   | 增益误差    | -4   | +/-1     | 2.2  | %FS |

| SNR          | 信噪比     |      | 68       |      | dB  |

| SFDR         | 无杂散动态范围 |      | 85       |      | dB  |

表 4: 数字输出参数

| 标志   | 说明                    | 最小    | 典型   | 最大    | 单位 |

|------|-----------------------|-------|------|-------|----|

| V_OD | 数字输出差分电压 (3.5mA 模式下)  | 247   | 350  | 454   | mV |

| V_OD | 数字输出差分电压 (1.75mA 模式下) | 125   | 175  | 250   | mV |

| V_OS | 数字输出共模电压              | 1.125 | 1.25 | 1.375 | V  |

## 5 性能特性

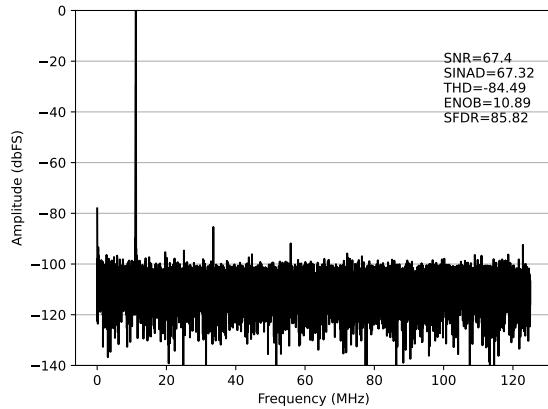

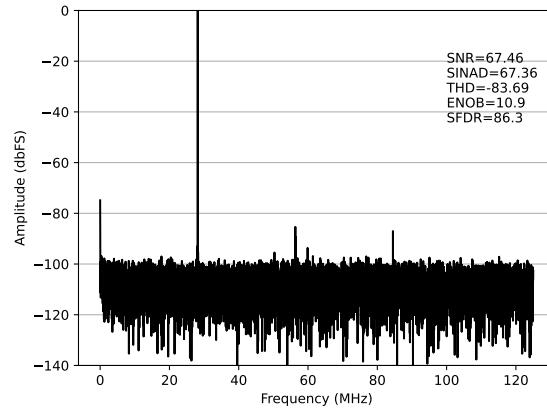

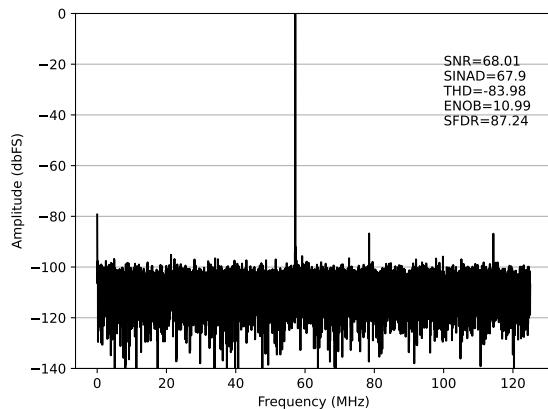

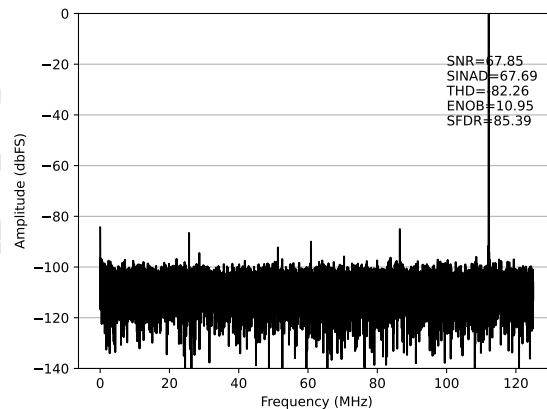

频谱特性，测试条件为 250MHz 采样率，采样点 32768 个。

(a) 输入信号频率 = 11MHz

(b) 输入信号频率 = 28MHz

(c) 输入信号频率 = 57MHz

(d) 输入信号频率 = 112MHz

图 2: 典型性能特性

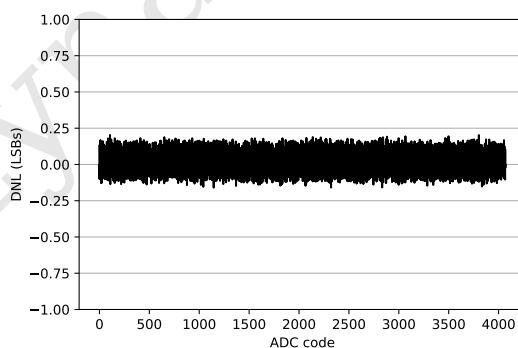

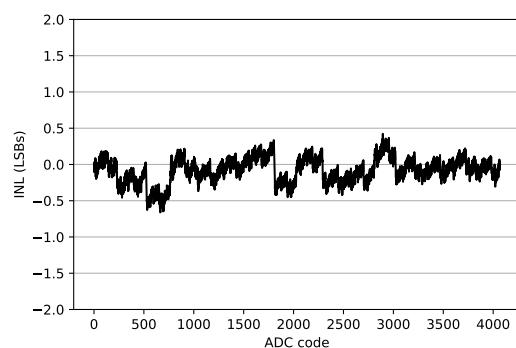

(a) DNL

(b) INL

图 3: 线性特性

## 6 绝对最大额定值

表 5: 绝对最大额定值

| 标志           | 说明                | 最大              | 单位  |

|--------------|-------------------|-----------------|-----|

| VDD,DVDD     | 最大输入电压范围          | -0.3 至 2        | V   |

| Analog Vin   | 最大输入模拟电压范围        | -0.3 至 VDD+0.2  | V   |

| CLK,SENSE    | 最大输入模拟电压范围        | -0.3 至 VDD+0.2  | V   |

| SPI          | SPI/GPIO 最大数字电压范围 | VDD 至 3.9       | V   |

| Data Output  | LVDS 输出最大数字电压范围   | -0.3 至 DVDD+0.2 | V   |

| WORKING TEMP | 工作温度              | -40 至 85        | 摄氏度 |

| STORAGE TEMP | 储存温度              | -65 至 150       | 摄氏度 |

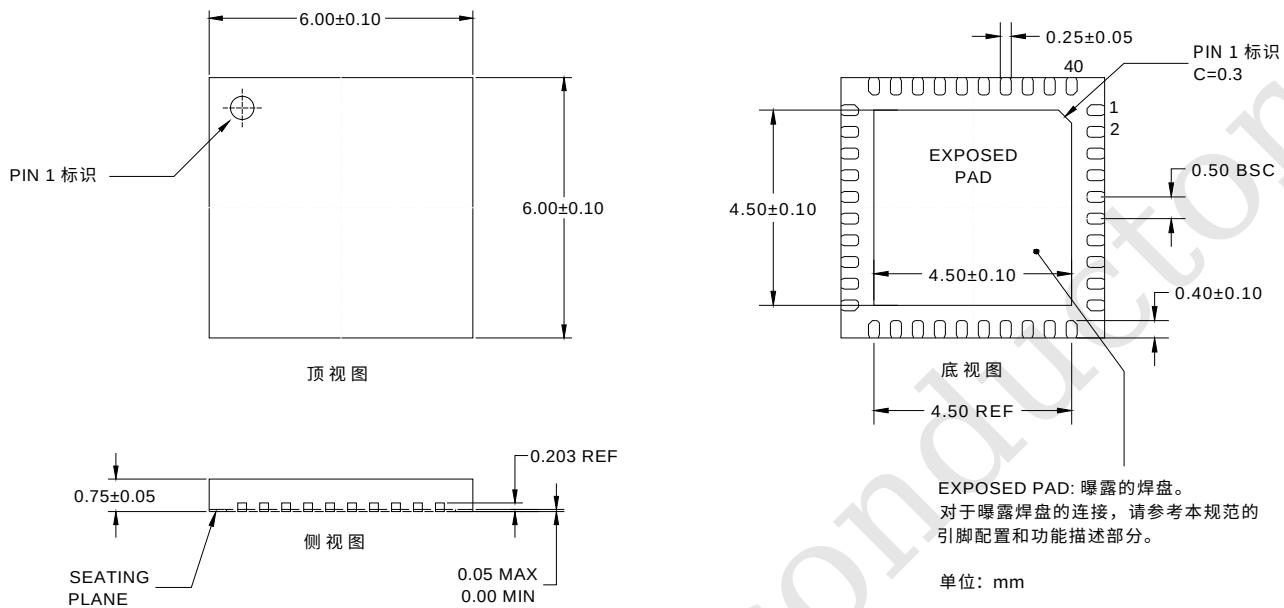

## 7 引脚配置

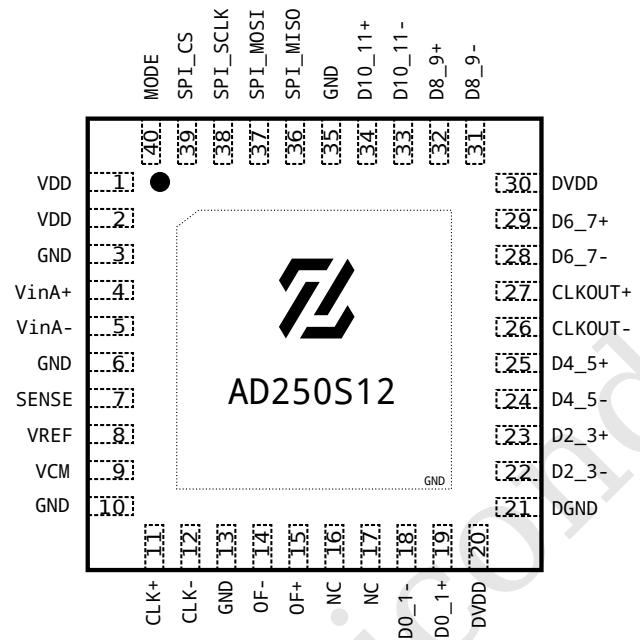

图 4: 正面视图

6mmx6mmQFN40 封装

表 6: 引脚定义和功能说明

| 引脚号                    | 引脚名称  | 类型     | 说明                                                                                            |

|------------------------|-------|--------|-----------------------------------------------------------------------------------------------|

| <b>电源</b>              |       |        |                                                                                               |

| 1,2                    | VDD   | Supply | 1.8V 模拟电源。用 $0.1\mu F$ 陶瓷电容器旁路到地。引脚 1,2 可以共用一个旁路电容。                                           |

| 3,6,10,13,35<br>20, 30 | GND   | Ground | 电源地。背面裸露焊盘必须焊接到 PCB 的地上。                                                                      |

|                        | DVDD  | Supply | 1.8V 数字输出驱动的电源。使用单独的 $0.1\mu F$ 陶瓷电容器将每个引脚旁路到地。                                               |

| 21                     | DGND  | Ground | 数字输出驱动的电源地。                                                                                   |

| <b>模拟信号</b>            |       |        |                                                                                               |

| 4                      | Vin+  | Input  | 差分模拟输入正端。                                                                                     |

| 5                      | Vin-  | Input  | 差分模拟输入负端。                                                                                     |

| 7                      | SENSE | Input  | 外部基准电压输入；连接到 VDD 可选择内部基准， $\pm 0.75V$ 输入范围。连接 1.2V 和 1.3V 之间的外部基准，可选择 $\pm 0.6*VSENSE$ 的输入范围。 |

| 8                      | VREF  | Output | 参考电压输出。使用 $2.2\mu F$ 陶瓷电容器旁路接地。标称 $1.25V$ 。                                                   |

| 9                      | VCM   | Output | 共模偏置输出。标称等于 $0.435*VDD$ 。VCM 应该用于设置模拟输入的共模偏置。使用 $0.1\mu F$ 陶瓷电容器旁路接地。                         |

| 11                     | CLK+  | Input  | 时钟输入。转换在上升沿开始。                                                                                |

| 12                     | CLK-  | Input  | 时钟输入。转换在下降沿开始。                                                                                |

| <b>SPI 信号</b>          |       |        |                                                                                               |

| 见下页...                 |       |        |                                                                                               |

... 接上页

| 引脚号   | 引脚名称           | 类型     | 说明                                                                                                                                                                                                       |

|-------|----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40    | MODE           | Input  | 串行接口并行模式选择引脚。<br>当接地时启用串行接口 SPI 模式，其中 SPI_CS、SPI_SCLK、SPI_MISO、SPI_MOSI 成为控制运行模式的串行接口。<br>当连接到 VDD 时启用并行 GPIO 模式，其中 SPI_CS、SPI_SCLK、SPI_MOSI 成为一组简化操作模式的并行逻辑输入控制信号。<br>MODE 应直接连接到 GND 或 VDD，而不是由逻辑信号驱动。 |

| 39    | SPI_CS         | Input  | 在串行接口模式 (MODE=0) 下为 SPI 的 CS 端口。<br>在并行模式 (MODE=VDD) 下，以 GPIO 方式控制时钟占空比稳定器：<br>SPI_CS=0 (GND) 时，时钟占空比稳定器关闭；<br>SPI_CS=1 (逻辑电压范围 1.8V 到 3.3V) 时，时钟占空比稳定器开启。                                               |

| 38    | SPI_SCLK       | Input  | 在串行接口模式 (MODE=0) 下为 SPI 的 SCLK 端口。在并行模式 (MODE=VDD) 下，以 GPIO 方式控制休眠模式：<br>SPI_SCLK=0 (GND) 时，工作在普通模式；<br>SPI_SCLK=1 (逻辑电压范围 1.8V 到 3.3V) 时，进入休眠模式 (AC Power down)。                                        |

| 37    | SPI_MOSI       | Input  | 在串行接口模式 (MODE=0) 下为 SPI 的 MOSI 端口。在并行模式 (MODE=VDD) 下，以 GPIO 方式控制 LVDS 输出电流：<br>SPI_MOSI=0 (GND) 时，3.5mA LVDS 输出驱动电流；<br>SPI_MOSI=1 (逻辑电压范围 1.8V 到 3.3V) 时，1.75mA LVDS 输出驱动电流。                            |

| 36    | SPI_MISO       | Output | 在串行接口模式 (MODE=0) 下为 SPI 的 MISO 端口。漏极开路输出，需要从 SPI 读回数据时，需上拉一个 2K 的电阻至 SPI 电源 (1.8V 到 3.3V)。在并行模式下无作用。                                                                                                     |

| 数字信号  |                |        |                                                                                                                                                                                                          |

| 14/15 | OF-/OF+        | Output | 上溢/下溢数字输出。当发生上溢或下溢时 OF+ 为高电平。                                                                                                                                                                            |

| 26/27 | CKLOUT/CLKOUT+ | Output | 数据输出 LVDS 的时钟。LDVS 输出通常与 CLKOUT+ 的下降沿和上升沿同时转换。通过对模式控制寄存器进行编程，CLKOUT+ 的相位也可以相对于数据输出延迟。                                                                                                                    |

| 18/19 | D0_1-/D0_1+    | Output | DDR LVDS 输出，CLKOUT+ 为低时，输出 D0 位，CLKOUT+ 为高时，输出 D1 位。                                                                                                                                                     |

| 22/23 | D2_3-/D2_3+    | Output | DDR LVDS 输出，CLKOUT+ 为低时，输出 D2 位，CLKOUT+ 为高时，输出 D3 位。                                                                                                                                                     |

| 24/25 | D4_5-/D4_5+    | Output | DDR LVDS 输出，CLKOUT+ 为低时，输出 D4 位，CLKOUT+ 为高时，输出 D5 位。                                                                                                                                                     |

| 28/29 | D6_7-/D6_7+    | Output | DDR LVDS 输出，CLKOUT+ 为低时，输出 D6 位，CLKOUT+ 为高时，输出 D7 位。                                                                                                                                                     |

见下页...

... 接上页

| 引脚号   | 引脚名称            | 类型     | 说明                                                            |

|-------|-----------------|--------|---------------------------------------------------------------|

| 31/32 | D8_9-/D8_9+     | Output | DDR LVDS 输出, CLKOUT+ 为低时, 输出 D8 位,<br>CLKOUT+ 为高时, 输出 D9 位。   |

| 33/34 | D10_11-/D10_11+ | Output | DDR LVDS 输出, CLKOUT+ 为低时, 输出 D10<br>位, CLKOUT+ 为高时, 输出 D11 位。 |

Zynalog Semiconductor

## 8 时序图

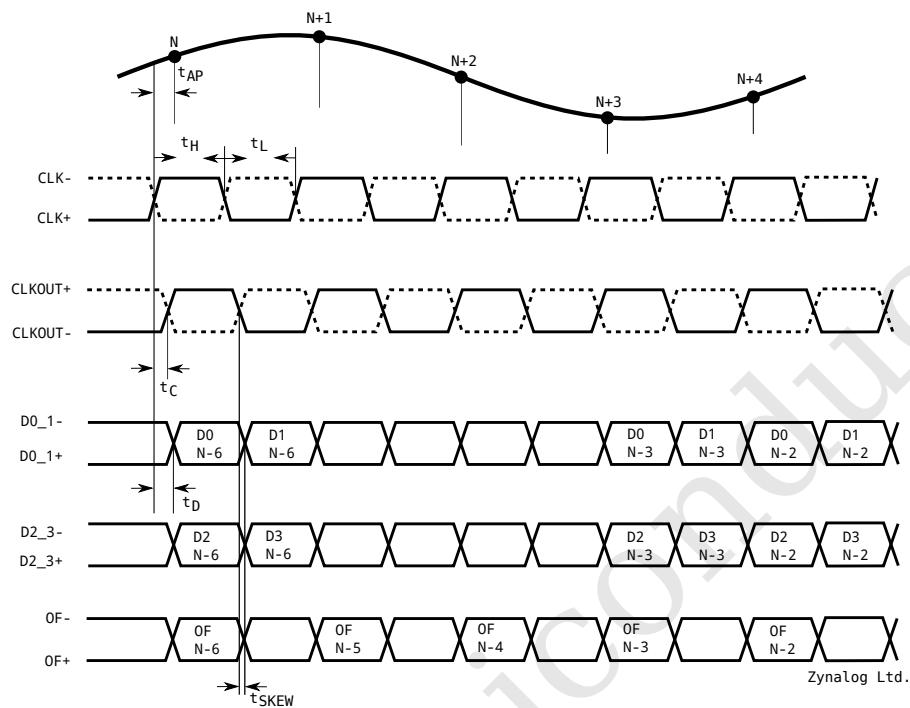

图 5: 数据输出

| 标志        | 说明*                          | 最小  | 典型  | 最大   | 单位 |

|-----------|------------------------------|-----|-----|------|----|

| $t_{AP}$  | 时钟输入和数据采集的延迟 <sup>†</sup>    |     | 1   |      | ns |

| $t_H$     | 时钟输入高保持时间                    | 1.9 | 2   |      | ns |

| $t_L$     | 时钟输入低保持时间                    | 1.9 | 2   |      | ns |

| $t_C$     | 时钟输入和时钟输出的延迟                 | 1.3 | 1.6 | 2    | ns |

| $t_D$     | 时钟输入和数据输出的延迟                 | 1.7 | 2   | 2.3  | ns |

| $t_{SKW}$ | 时钟输出和数据输出的差值 ( $t_C - t_D$ ) | 0.3 | 0.4 | 0.55 | ns |

\*时序延迟参数测试条件 VDD=1.8V, DVDD=1.8V, f<sub>S</sub>=250MHz<sup>†</sup>数据位延迟 6 个周期

## 9 应用信息

### 9.1 模拟信号输入

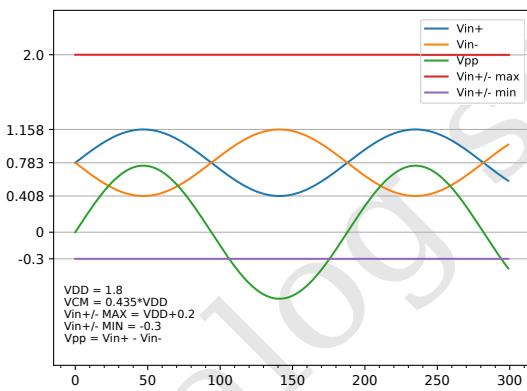

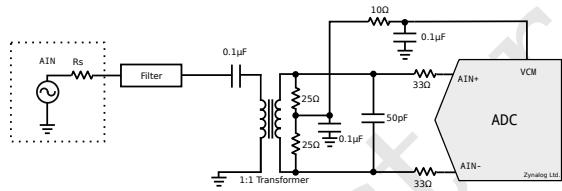

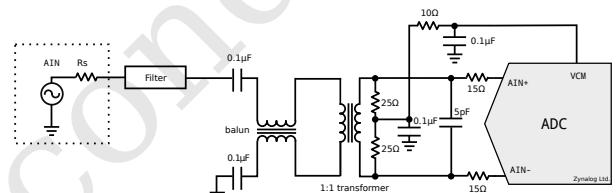

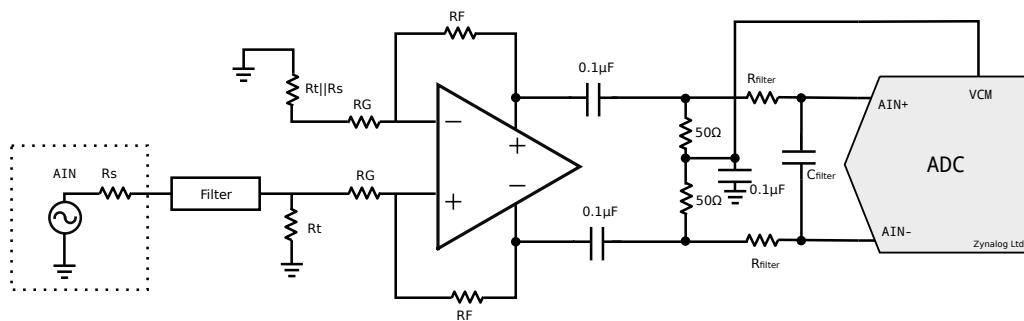

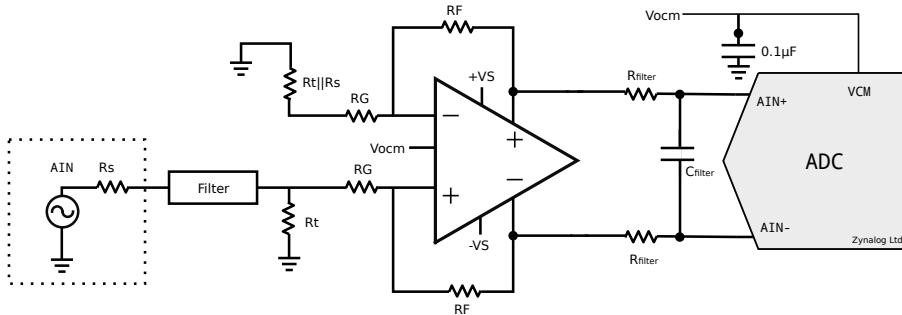

ZGAD250S12 模拟信号输入端内部是差分 CMOS 采样保持电路，模拟信号输入必须依赖由 VCM 输出引脚设置的共模电压进行差分驱动，VCM 电压的标称值为  $0.435 \times VDD$ 。输入差分电压应在 1.5V 之内。输入之间应该有  $180^\circ$  的相位差。如果可能，模拟输入端应该有一个 RC 低通滤波器。该低通滤波器将驱动电路与 ADC 采样保持开关隔离，并抑制驱动电路的宽带噪声。图7 显示了输入 RC 滤波器的示例。应根据应用的特定输入频率选择 RC 元件值。在较高的输入频率下，使用传输线巴伦变压器（图8和9）具有更好的平衡性，从而降低 ADC 失真。使用内部基准电压时，将 SENSE 引脚上拉至 VDD，此时输入信号的范围为  $\pm 0.75V$ 。使用外部基准电压时，将 SENSE 引脚拉至 1.2V 到 1.3V 之间的基准电压，此时输入信号的范围为  $\pm 0.6V \times \text{SENSE}$ 。

图 6: 输入信号满量程示意图

图 7: 输入频率在第一个 Nyquist Zone 的推荐前端电路

图 8: 输入频率大于第一个 Nyquist Zone 的推荐前端电路

图9和图10显示了使用单端转差分高速运放的前端电路设计。其中对  $Rt$  和  $Rt||Rs$  电阻的选择对应于信号源的阻抗匹配；选择合适的高带宽的运放对整个系统有巨大影响，特别是信号放大带来的谐波失真； $Rfilter$  和  $Cfilter$  构造一个 charge bucket filter， $Rfilter$  和  $Cfilter$  的值应根据输入信号的频率进行选择，一般  $Rfilter$  不超过  $50\Omega$ ， $Cfilter$  不超过  $50\text{pF}$ 。

对于图10中的应用，需要注意的是，大部分运放都需要提供正 VS 和负 VS，以满足共模电压  $VCM(0.435 \times VDD)$  的标称值。

图 9: 使用单端转差分的高速运放的推荐前端电路 (隔离直流信号)

图 10: 使用单端转差分的高速运放的推荐前端电路

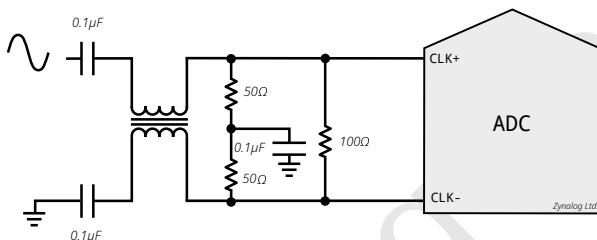

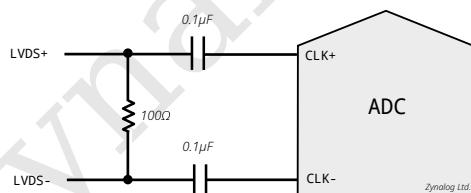

## 9.2 时钟信号

采样时钟输入的信号质量会强烈影响 ADC 的噪声性能。时钟信号应被视为模拟信号, 不要将它们放置到电路板上的数字信号旁边。采样时钟输入通过 10k 等效电阻在 ADC 内部偏置为 1.2V。如果驱动器的共模电压在 1.1V 到 1.5V 之间, 则可以直接驱动时钟输入, 否则需要通过变压器或耦合电容(图11和12)。输入信号的最大(峰值)电压不应超过 VDD+0.1V 或低于-0.1V。建议时钟信号的抖动应小于 160fs 以达到转换器的最佳性能。

图 11: 模拟时钟信号输入

图 12: LVDS/PECL 时钟信号输入

## 9.3 时钟占空比稳定器

为了获得良好的性能, 采样时钟信号应具有 50% ( $\pm 5\%$ ) 的占空比。如果启用可选的时钟占空比

稳定器 (Duty Cycle Stabilizer, DCS) 电路, 时钟占空比可以在 30% 到 70% 之间变化, 占空比稳定器输出将保持恒定的 50% 内部占空比。占空比稳定器通过 SPI 时序寄存器 (见表10) 或并行模式下的 SPI\_CS 启用。对于需要快速更改采样率的应用, 可以禁用时钟占空比稳定器。在这种情况下, 应注意使时钟具有 50% ( $\pm 5\%$ ) 的占空比。

## 9.4 LVDS 数字输出

数字输出是双倍数据速率 LVDS 信号。两个数据位被复用并在每个差分输出对上输出。通道有 6 对 LVDS 输出 (D0\_1+/D0\_1- 到 D10\_11+/D10\_11-)。溢出 (OF+/OF-) 和数据输出时钟 (CLKOUT+/CLKOUT-) 各有 1 对 LVDS 输出。输出对上。请参考时序图 (图5)。默认情况下, 输出为标准 LVDS 电平:3.5mA 输出电流和 1.25V 输出共模电压。输出电流可以通过输出模式寄存器进行调节 (见表11)。可用电流级别为 1.75mA、2.1mA、2.5mA、3mA、3.5mA、4mA 和 4.5mA。

LVDS 输出由 DVDD 和 DGND 供电。DVDD 和 DGND 和 ADC 内核的电源以及地隔离。每个 LVDS 输出对都需要一个外部 100Ω 差分终端电阻。终端电阻应尽可能靠近 LVDS 接收器。在大多数情况下, 仅使用 100Ω 外部终端电阻可以提供出色的 LVDS 信号完整性。此外, 可以通过输出模式寄存器 (表11) 启用可选的内部 100Ω 终端电阻。内部端接有助于吸收由接收器端引起的反射。当内部端接使能时, 输出驱动电流会自动加倍以保持相同的输出电压摆幅。

表 7: 数据输出格式

| 输入电压 ( $V_{in+}$ ) - ( $V_{in-}$ ) | OF | Offset Binary Mode | Twos Complement Mode |

|------------------------------------|----|--------------------|----------------------|

|                                    |    | D11 - D0           | D11 - D0             |

| >0.75 V                            | 1  | 1111 1111 1111     | 0111 1111 1111       |

| +0.75V                             | 0  | 1111 1111 1111     | 0111 1111 1111       |

| +0.74963378V                       | 0  | 1111 1111 1110     | 0111 1111 1110       |

| +0.0007324V                        | 0  | 1000 0000 0010     | 0000 0000 0010       |

| +0.0003662V                        | 0  | 1000 0000 0001     | 0000 0000 0001       |

| +0.0000000V                        | 0  | 1000 0000 0000     | 0000 0000 0000       |

| -0.0003662V                        | 0  | 0111 1111 1111     | 1111 1111 1111       |

| -0.0007324V                        | 0  | 0111 1111 1110     | 1111 1111 1110       |

| -0.74963378V                       | 0  | 0000 0000 0001     | 1000 0000 0001       |

| -0.75V                             | 0  | 0000 0000 0000     | 1000 0000 0000       |

| <-0.75V                            | 1  | 0000 0000 0000     | 1000 0000 0000       |

#### 9.4.1 数据输出格式

默认情况下，输出数据格式为偏移二进制格式 (Offset Binary Mode)，可以通过输出模式寄存器 (表12) 来选择二进制补码格式 (Twos Complement Mode)。表7 显示了模拟输入电压、数字数据输出位和溢出位之间的关系。

#### 9.4.2 随机发生器

ADC 数字输出的干扰有时是不可避免的。数字干扰可能来自电容或电感耦合或通过接地平面耦合。即使很小的耦合因子也会在 ADC 输出频谱中产生不需要的音。通过在数字信号输出之前将其随机化，可以将这些不需要的音随机化，从而降低不需要的音幅度。ADC 内部随机发生器可以通过数字信号格式寄存器 (表12) bit1 启用。启用后，通过在 D0 位和所有其他数据位之间应用“异或逻辑”运算来随机化数字输出。在数字信号的接收端，比如 FPGA 内部，解码则应用同样操作，D0 和所有其他位之间再次“异或逻辑”运算。公式如下：

- 编码:  $D_1 = D_1 \oplus D_0; D_2 = D_2 \oplus D_0; \dots$

- 解码:  $D_1 = D_1 \oplus D_0; D_2 = D_2 \oplus D_0; \dots$

D0、OF 和 CLKOUT 输出不受影响。

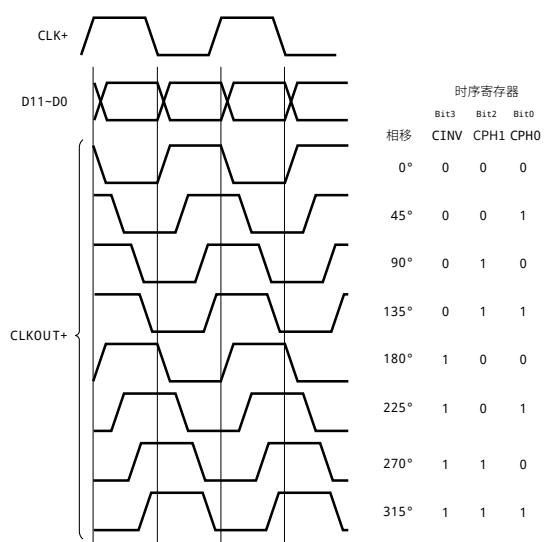

#### 9.4.3 输出时钟 (CLKOUT) 的相位移动

为了在锁存输出数据时有足够的设置和保持时间，可能需要将 CLKOUT 信号相对于数据输出位进行相移。大多数 FPGA 都带有这个功能，通常在 FPGA 内部是调整时序的最佳位置。或者，也可以通

过 ADC 时序寄存器 (表10) 对 CLKOUT 信号进行相移。输出时钟可以偏移  $0^\circ$ 、 $45^\circ$ 、 $90^\circ$  或  $135^\circ$ 。要使用相移功能，必须打开时钟占空比稳定器。另外还可以通过时序寄存器反转 CLKOUT 的极性，与相移无关。这两个功能的组合可实现  $45^\circ$  至  $315^\circ$  的相移 (图13)。

图 13: 相位偏移

#### 9.4.4 交替位极性

针对非常小的模拟输入信号，因为高位一直保持不变，可以启用交替位极性模式，来减少可能出现的数字干扰。启用此模式后，所有奇数位 ( $D_1, D_3, D_5, \dots$ ) 在输出之前被反转。偶数位 ( $D_0, D_2, D_4, \dots$ )、OF 和 CLKOUT 不受影响。数字输出在接收端，如 FPGA 内部，通过反转奇数位 ( $D_1, D_3, D_5, \dots$ ) 解

码。交替位极性模式独立于随机发生器，可以同时开启这两种功能，也可以两种功能都不开启。交替位极性模式通过数字信号格式寄存器（表12）bit4 启用。

#### 9.4.5 数字输出测试模式

为了对 ADC 的数字接口进行在线测试，数字输出测试模式可以强制 ADC 数据输出 (OF、D11 到 D0) 为以下值：

- 全 1：所有输出均为 1

- 全 0：所有输出均为 0

- 交替：交替采样时输出从全 1 变为全 0

- 棋盘格：交替采样的输出从 010101010101 变为 101010101010。

数字输出测试模式由数字信号格式寄存器（表12）启用。在测试模式下，其他格式化模式进入无效状态，如二进制补码、随机发生器。

#### 9.4.6 输出关闭

通过设置输出模式寄存器（表11）bit0 可以关闭包含 OF 和 CLKOUT 的所有数字输出。

### 9.5 低功耗模式

ADC 允许运行在低功耗模式下来节能。在低功耗模式下，ADC 的内部核心电路会关掉，外围电路保持激活状态，此时功耗约为 102.5mW。低功耗模式由掉电寄存器（表9）bit2 来控制。从低功耗模式恢复，如果外部采样时钟在低功耗模式期间持续输入，则需要至少 100 个时钟周期，否则和休眠模式恢复时间相等。

### 9.6 休眠模式

在休眠模式下，ADC 的整个电路会被关断，包括核心电路和外围电路。如果外部采样时钟也停止输入，则功耗低于 0.65mW，外部采样时钟保持输入，则功耗在 0.65mW 左右。休眠模式由掉电寄存器（表9）bit3 来控制。从休眠模式恢复，唤醒时间约等于 2500\* 时钟周期 +0.1 毫秒。

### 9.7 软件复位

如果使用 SPI 模式，则应在初始上电并稳定后尽快对控制寄存器进行配置。第一个 SPI 命令必须是软件复位，它将所有寄存器数据位复位为逻辑 0。要执行软件复位，必须在复位寄存器（表8）bit7 中写入 1。复位完成后，bit7 自动设置回 0。该复位寄存器是只写的。

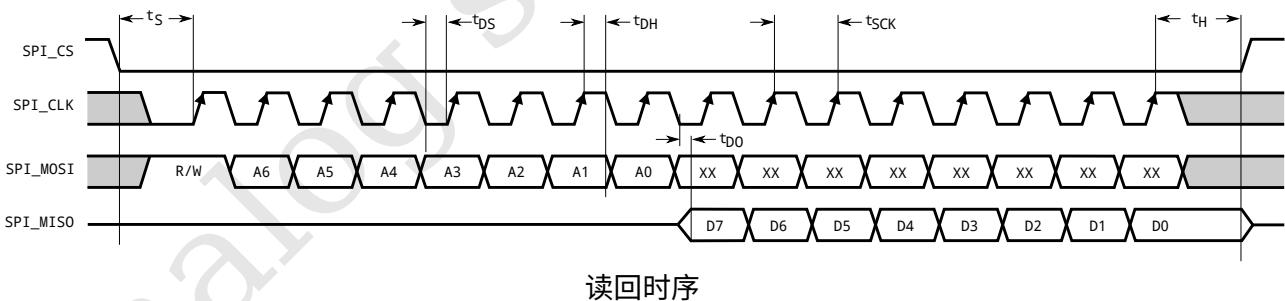

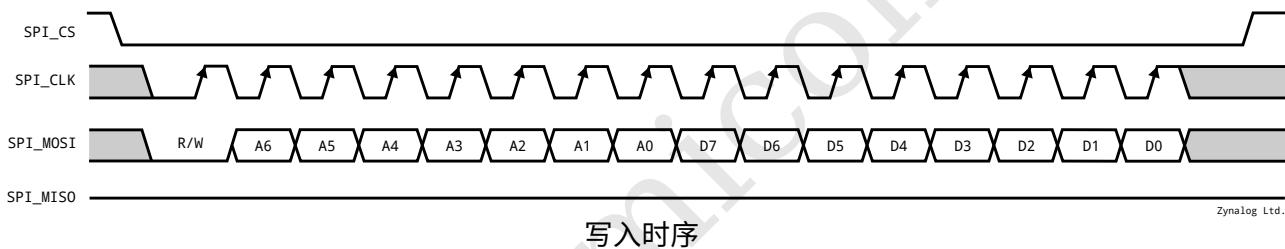

## 10 SPI 和控制寄存器

### 10.1 SPI

在串行接口模式 (MODE=0) 下, 数据以 16 位串行位写入寄存器。也可以从寄存器读回数据以验证其内容。当 SPI\_CS 被拉低时串行数据传输开始。SPI\_MOSI 引脚上的数据在 SPI\_CLK 的前 16 个上升沿被锁存。前 16 个之后的任何 SPI\_CLK 上升沿都将被忽略。当 SPI\_CS 再次拉高时, 数据传输结束。

16 位输入的第一位是 R/W 位。接下来的七位是寄存器的地址 (A6:A0), 后八位是寄存器数据 (D7:D0)。如果 R/W 位为低, 串行数据 (D7:D0) 将

写入由地址位 (A6:A0) 设置的寄存器。如果 R/W 位为高, 由地址位 (A6:A0) 设置的寄存器中的数据将在 SPI\_MISO 引脚上被读回 (参见图 14)。在回读命令期间, 寄存器不会更新并且 SPI\_MOSI 上的数据会被忽略。

SPI\_MISO 引脚是一个开漏输出, 如果通过 SPI\_MISO 回读寄存器数据, 则需要外接  $2\text{K}\Omega$  上拉电阻。如果只写串行数据不需要回读, 那么 SPI\_MISO 可以悬空, 不需要上拉电阻。

图 14: SPI 时序图

| 标志        | 说明 <sup>‡</sup>     | 最小  | 典型 | 最大  | 单位 |

|-----------|---------------------|-----|----|-----|----|

| $t_S$     | CS 拉低到时钟 CLK 的建立时间  | 5   |    |     | ns |

| $t_{DS}$  | 数据建立时间              | 5   |    |     | ns |

| $t_{DH}$  | 数据保持时间              | 5   |    |     | ns |

| $t_{DO}$  | 时钟 CLK 到数据输出的延迟     |     |    | 125 | ns |

| $t_{SCK}$ | 时钟周期 (写入)           | 40  |    |     | ns |

|           | 时钟周期 (读回)           | 250 |    |     | ns |

| $t_H$     | 时钟 CLK 到 CS 拉高的保持时间 | 5   |    |     | ns |

<sup>‡</sup>参数测试条件: SPI\_MISO 上拉电阻  $2\text{K}\Omega$

## 10.2 控制寄存器

表 8: 复位寄存器

| 地址<br>(HEX) | bit7                                               | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | 初始值  | 备注 |

|-------------|----------------------------------------------------|------|------|------|------|------|------|------|------|----|

| 0x00        | RESET                                              | X    | X    | X    | X    | X    | X    | X    | 0x00 | 只写 |

| bit7        | RESET 软件复位位。写入 0 禁用; 写入 1 = 软件复位。复位完成后, 该位自动设置回 0。 |      |      |      |      |      |      |      |      |    |

| bit6-0      | 未使用。                                               |      |      |      |      |      |      |      |      |    |

表 9: 掉电寄存器

| 地址<br>(HEX) | bit7                                    | bit6 | bit5 | bit4 | bit3  | bit2 | bit1 | bit0 | 初始值  | 备注 |

|-------------|-----------------------------------------|------|------|------|-------|------|------|------|------|----|

| 0x01        | X                                       | X    | X    | X    | SLEEP | LP   | X    | 0    | 0x00 | 读写 |

| bit7:4      | 未使用。读回为 0。                              |      |      |      |       |      |      |      |      |    |

| bit3        | SLEEP, 休眠位, 0= 正常工作模式; 1= 关断整个芯片。       |      |      |      |       |      |      |      |      |    |

| bit2        | Low Power, 低功耗位, 0= 正常工作模式; 1= 均为低功耗模式。 |      |      |      |       |      |      |      |      |    |

| bit1        | 未使用。读回为 0。                              |      |      |      |       |      |      |      |      |    |

| bit0        | 必须写入 0。                                 |      |      |      |       |      |      |      |      |    |

表 10: 时序寄存器

| 地址<br>(HEX) | bit7                                                                                                                                                                                                                                                     | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | 初始值  | 备注 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|----|

| 0x02        | X                                                                                                                                                                                                                                                        | X    | X    | X    | CINV | CPH1 | CPH0 | DCS  | 0x00 | 读写 |

| bit7:4      | 未使用。读回为 0。                                                                                                                                                                                                                                               |      |      |      |      |      |      |      |      |    |

| bit3        | CLKOUT inverse, 输出时钟反转位。<br>0= 正常 CLKOUT 极性 (如图5所示);<br>1= 反向 CLKOUT 极性。                                                                                                                                                                                 |      |      |      |      |      |      |      |      |    |

| bit2:1      | CLKOUT PHASE1:CLKOUT PHASE0 输出时钟相位延迟位<br>00 = 无 CLKOUT 延迟 (如图5所示)<br>01 = CLKOUT 延迟 45°(时钟周期 • 1/8)<br>10 = CLKOUT 延迟 90°(时钟周期 • 1/4)<br>11 = CLKOUT 延迟 135°(时钟周期 • 3/8)<br>注意: 如果使用 CLKOUT 相位延迟功能, 则还必须打开时钟占空比稳定器。<br>Duty Cycle Stabilizer, 时钟占空比稳定器位。 |      |      |      |      |      |      |      |      |    |

| bit0        | 0 = 时钟占空比稳定器关闭<br>1 = 时钟占空比稳定器开启                                                                                                                                                                                                                         |      |      |      |      |      |      |      |      |    |

表 11: 输出模式寄存器

| 地址<br>(HEX) | bit7                                                                                                                                                                                                                                | bit6 | bit5 | bit4   | bit3   | bit2   | bit1 | bit0 | 初始值  | 备注 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--------|--------|--------|------|------|------|----|

| 0x03        | X                                                                                                                                                                                                                                   | X    | X    | ILVDS2 | ILVDS1 | ILVDS0 | TON  | OFF  | 0x00 | 读写 |

| bit7:5      | 未使用。读回为 0。                                                                                                                                                                                                                          |      |      |        |        |        |      |      |      |    |

| bit4:2      | ILVDS2:ILVDS0 LVDS 输出电流位<br>000 = 3.5mA LVDS 输出驱动电流<br>001 = 4.0mA LVDS 输出驱动电流<br>010 = 4.5mA LVDS 输出驱动电流<br>011 = 未使用<br>100 = 3.0mA LVDS 输出驱动电流<br>101 = 2.5mA LVDS 输出驱动电流<br>110 = 2.1mA LVDS 输出驱动电流<br>111 = 1.75mA LVDS 输出驱动电流 |      |      |        |        |        |      |      |      |    |

| bit1        | TERMINATION ON, LVDS 内部终端使能位<br>0 = 内部终端关闭<br>1 = 内部终端开启。LVDS 输出驱动电流等于 ILVDS2:ILVDS0 设置的电流的 2 倍                                                                                                                                     |      |      |        |        |        |      |      |      |    |

| bit0        | OUTPUT OFF, 数字输出控制位<br>0 = 启用数字输出<br>1 = 数字输出被禁用 (高阻抗)                                                                                                                                                                              |      |      |        |        |        |      |      |      |    |

表 12: 数字信号格式寄存器

| 地址<br>(HEX) | bit7                                                                                                                                                                                                               | bit6  | bit5  | bit4 | bit3 | bit2 | bit1 | bit0 | 初始值  | 备注 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|------|------|------|------|------|----|

| 0x04        | TEST2                                                                                                                                                                                                              | TEST1 | TEST0 | ABP  | 0    | TON  | RAND | 2SC  | 0x00 | 读写 |

| bit7:5      | OUTTEST2:OUTTEST0 数字输出测试模式位<br>000 = 所有数字输出 = 0<br>001 = 所有数字输出 = 1<br>010 = 交替输出模式。OF, D11-D0 在 000000000000 和 111111111111 之间交替<br>100 = 棋盘格输出模式。OF, D11-D0 在 101010101010 和 010101010101 之间交替<br>注 1: 不使用其他位组合。 |       |       |      |      |      |      |      |      |    |

| bit4        | ABP 交替位极性模式控制位<br>0 = 交替位极性模式关闭<br>1 = 交替位极性模式开启。奇数位 D1,D3,D5...D11 极性反转                                                                                                                                           |       |       |      |      |      |      |      |      |    |

| bit3        | 必须设置为 0                                                                                                                                                                                                            |       |       |      |      |      |      |      |      |    |

| bit2        | TEST ON, 启用数字输出测试模式 (输出模式由位 7:5 设置)<br>0 = 正常模式<br>1 = 启用数字输出测试模式                                                                                                                                                  |       |       |      |      |      |      |      |      |    |

| bit1        | RAND 数据输出随机发生器模式控制位<br>0 = 随机发生器模式关闭<br>1 = 随机发生器模式开启                                                                                                                                                              |       |       |      |      |      |      |      |      |    |

| bit0        | Twos Complement Mode 补码模式控制位<br>0 = 偏移二进制数据格式 (Offset Binary Output)<br>1 = 二进制补码数据格式 (Twos Complement Mode)                                                                                                       |       |       |      |      |      |      |      |      |    |

## 11 封装

图 15: 封装信息

## 12 订购信息

表 13: ADC 系列产品信息

| 型号          | 通道  | 位数   | 采样率  | 封装    | 数字接口     |

|-------------|-----|------|------|-------|----------|

| ZGAD250D12  | 双通道 | 12 位 | 250M | QFN64 | DDR LVDS |

| ZGAD250D14  | 双通道 | 14 位 | 250M | QFN64 | DDR LVDS |

| ZGAD250S12  | 单通道 | 12 位 | 250M | QFN40 | DDR LVDS |

| ZGAD250S14  | 单通道 | 14 位 | 250M | QFN40 | DDR LVDS |

| ZGAD125D12  | 双通道 | 12 位 | 125M | QFN64 | DDR LVDS |

| ZGAD125D14  | 双通道 | 14 位 | 125M | QFN64 | DDR LVDS |

| ZGAD125D12C | 双通道 | 12 位 | 125M | QFN64 | CMOS     |

| ZGAD125D14C | 双通道 | 14 位 | 125M | QFN64 | CMOS     |

| ZGAD125S12  | 单通道 | 12 位 | 125M | QFN40 | DDR LVDS |

| ZGAD125S14  | 单通道 | 14 位 | 125M | QFN40 | DDR LVDS |

| ZGAD125S12C | 单通道 | 12 位 | 125M | QFN40 | CMOS     |

| ZGAD125S14C | 单通道 | 14 位 | 125M | QFN40 | CMOS     |

| ZGAD65D12C  | 双通道 | 12 位 | 65M  | QFN64 | CMOS     |

| ZGAD65D14C  | 双通道 | 14 位 | 65M  | QFN64 | CMOS     |

| ZGAD65S12C  | 单通道 | 12 位 | 65M  | QFN40 | CMOS     |

| ZGAD65S14C  | 单通道 | 14 位 | 65M  | QFN40 | CMOS     |

## 13 关于徵格

### 13.1 公司简介

徵格半导体【Zynalog Semiconductor Co.,Ltd.】是国内高性能模拟芯片研发设计的高科技企业。公司拥有国际顶尖的模拟芯片设计团队，先进的测试设备和完善的供应链体系，遵循严苛的品控标准，由公司全正向设计研发的三十多款高速高精度模数转换芯片（ADC）产品凭借卓越的高性能及高可靠性，已被国内多家头部知名科技企业所选用，完美应用于旗下各款高新产品之中。

徵格半导体秉持“技术自主创新，引领行业未来”的理念，以客户需求为导向，聚焦技术创新，坚持核心技术的长期研发投入，公司已在高性能模拟芯片领域拥有多项自主知识产权，ADC 多项核心技术指标已达到或超越国际主流同类产品。至此，徵格半导体已然定义和树立起国内高性能 ADC 行业新标杆。

当今中国，数字化和智能化将成为国内领先企业应对未来挑战的必由之路，为此徵格半导体将持续加码在高性能模拟芯片的研发进程，在“高性能芯片国产替代”成为确定性趋势和国家构建产业链供应链稳定安全的今天，我们将以客户技术变革和产业升级为指引，满足客户高科技产品应用的设计多样化及复杂化需求，灵活匹配客户产品的技术更迭和保障供应链的安全可靠，为客户提供全方位全流程模拟芯片标准解决方案。

徵格半导体将进一步拓展和深耕国内高性能模拟芯片应用端，实现以客户为中心的高速度高质量增长。公司将以前瞻性战略思维及雄厚的研发能力为基础，遵循严苛品控标准和安全可靠的供应链管理体系，与企业用户携手打造共创、共享、共赢的模拟芯片行业新生态。

### 13.2 联系方式

地址：上海市普陀区丹巴路 98 弄 7 号龙裕财富中心 10 层

地址：苏州市高新区城际路 21 号 2 幢汇融广场 2110 室

地址：杭州市临平区科城街 180 号算力小镇 C 幢 8 层

网站：<https://www.zynalog.com>

电子邮箱：[sales@zynalog.com](mailto:sales@zynalog.com)