## CM2322 数据手册

## 特征

■ 单电源供电: 1.8V

■ 逻辑接口电压: 1.8V、2.5V、3V、5V

■ 真差分模拟输入范围: ±VREF

■ 18 位分辨率、无失码

■ 吞吐率: 1MSPS

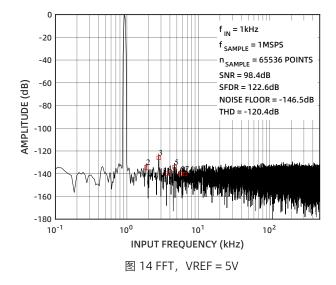

■ 性能

INL: 典型值为 ±1.2LSB (VREF = 5V)

动态范围: 98.9dB (VREF = 5V)

SNR: 97.3dB ( $f_{IN} = 1kHz$ , VREF = 5V)

SNDR: 96.2dB ( $f_{IN} = 1kHz$ , VREF = 5V) THD: -119dB ( $f_{IN} = 1kHz$ , VREF = 5V)

■ 串行接口: SPI/QSPI/MICROWIRE 兼容

■ 以级联形式连接多个 ADC,提供繁忙指示

■ 无流水线延迟

■ 低功耗

3.3mW (1MSPS,仅 VDD)

5.7mW (1MSPS, 总功耗)

56.5µW (10kSPS,总功耗)

■ MSOP10 3mm × 3mm 和 DFN10 3mm × 3mm 封装

### 应用

- 仪器仪表

- 自动化测试设备

- 高精度数据采集卡

- 医疗仪器

### 概述

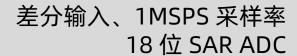

CM2322 是一款 18 位、逐次逼近型模数转换器 (ADC),采用单电源供电。它内置一个低功耗、高速、18 位采样 ADC 和一个多功能串行接口。在 CNV 上升沿,CM2322 对 IN+与 IN-管脚之间的电压差进行采样,两个输入管脚上的信号通常相位相反,电压摆幅在 0V 至 VREF 之间。基准电压 VREF 由外部提供,并且可以独立于电源电压 VDD,其功耗与吞吐率呈正比例变化关系。

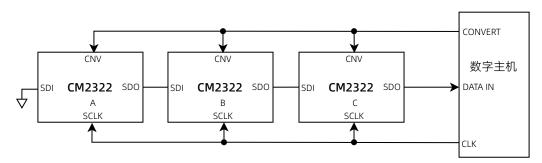

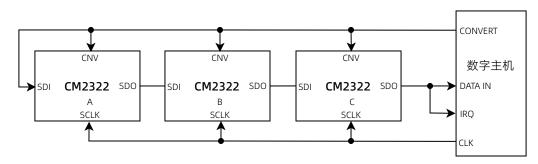

利用 SPI 接口的 SDI 输入管脚,可以采用菊花链的方式将多个 ADC 连接在一起,并提供一个可选的繁忙指示。通过独立电源 VIO,该芯片可与 1.8V、2.5V、3V 和 5V 逻辑兼容。

CM2322 采用 MSOP10 型和 DFN10 型封装, 其最佳工作温度范围为-40℃~125℃。

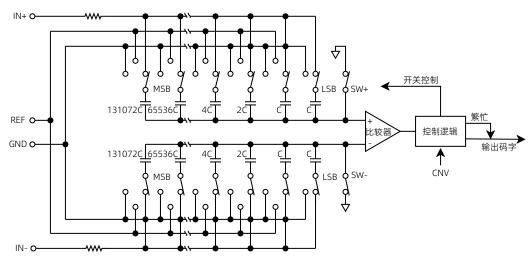

## 架构框图

# 目录

| 封页1      |

|----------|

| 特征1      |

| 应用1      |

| 概述1      |

| 架构框图1    |

| 文档历史3    |

| 管脚配置和功能4 |

| 管脚配置4    |

| 管脚功能4    |

| 绝对最大额定值5 |

| 电气规格6    |

| 时序规格8    |

| 典型特征14   |

| 工作原理16   |

| 转换器操作16  |

| 模拟输入16   |

| 电压基准输入17 |

| 传递函数17   |

| 亚动放大哭 17 |

|    | 单端转差分驱动器  | .17  |

|----|-----------|------|

|    | 功耗        | . 18 |

| 数字 | 接口        |      |

|    | 片选模式      | . 19 |

|    | 三线串口无繁忙指示 | . 19 |

|    | 三线串口有繁忙指示 | . 19 |

|    | 四线串口无繁忙指示 |      |

|    | 四线串口有繁忙指示 | . 20 |

|    | 级联模式      | . 20 |

|    | 无繁忙指示     |      |

|    | 有繁忙指示     |      |

| 应用 |           |      |

|    | 典型连接      |      |

| 封装 | 及订购信息     |      |

|    | 封装方式      |      |

|    | 产品外形图     |      |

|    | MSOP10    |      |

|    | DFN10     | . 23 |

|    | 订购信息      | . 24 |

|    |           |      |

# 文档历史

下表列举了本文档自产品发布后的所有更新。

| 文档版本 | 修订日期       | 内容描述                                                     |

|------|------------|----------------------------------------------------------|

| V0.1 | 2024-06-03 | 预发布。                                                     |

| V0.5 | 2024-09-30 | <ul><li>根据测试结果优化电气规格数据。</li><li>根据测试结果优化典型特征图。</li></ul> |

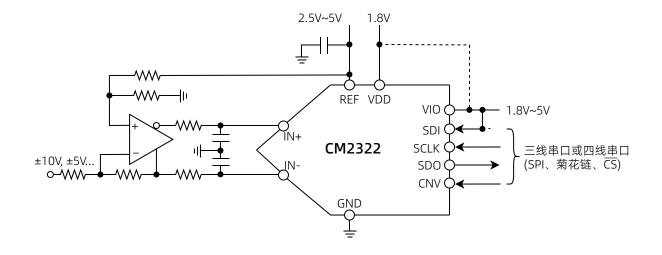

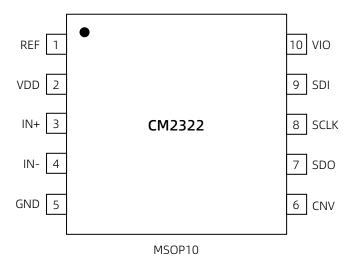

# 管脚配置和功能

## 管脚配置

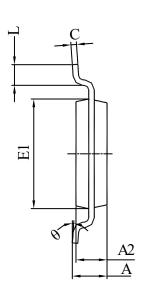

以下为 CM2322 封装管脚示意图:

## 管脚功能

表1管脚功能描述

| 编号 | 名称   | 类型  | 说明                                                                                                                                                                                                                         |

|----|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | REF  | AI  | 基准输入电压。REF 范围为 2.4 V 至 5.1 V。此管脚与 GND 管脚之间应连接 10μF 的去耦电容。                                                                                                                                                                  |

| 2  | VDD  | PWR | 电源。电压范围为 1.71V 至 1.89V,典型值为 1.8V。                                                                                                                                                                                          |

| 3  | IN+  | Al  | 正向差分模拟输入。                                                                                                                                                                                                                  |

| 4  | IN-  | Al  | 负向差分模拟输入。                                                                                                                                                                                                                  |

| 5  | GND  | GND | 地。                                                                                                                                                                                                                         |

| 6  | CNV  | DI  | 转换启动信号。此信号除了可在上升沿启动转换外,还可选择数字接口工作模式:级联模式或片选模式。级联模式下,数据在 CNV 为高电平时读取。片选模式下,CNV 为低电平时 SDO 管脚使能。                                                                                                                              |

| 7  | SDO  | DO  | 串行数据输出。转换结果通过此管脚输出,与 SCLK 同步。                                                                                                                                                                                              |

| 8  | SCLK | DI  | 时钟输入。在级联模式下,如果 CNV 上升沿期间 SCLK 为高电平,则产生繁忙指示。                                                                                                                                                                                |

| 9  | SDI  | DI  | 串行数据输入。如果 CNV 上升沿时 SDI 为低电平,则数字接口工作在级联模式。此模式下,SDI 作为数据输入,将两个或更多的 ADC 转换结果以级联模式传输到单一 SDO 上。SDI 上的数据经过 18 SCLK 周期延迟后输出到 SDO。如果 CNV 上升沿时 SDI 为高电平,则数字接口工作在片选模式。此模式下,SDI 或 CNV 在低电平时均可使能 SDO。当转换完成时,如果 SDI 或 CNV 为低电平,则产生繁忙指示。 |

| 10 | VIO  | PWR | 输入/输出数字接口电源。此管脚的标称电源与主机接口电源相同(1.8 V、2.5 V、3 V 或 5 V),电压范围为 1.71V 至 5.5V。                                                                                                                                                   |

|    | EPAD |     | 裸露焊盘。对于 DFN10 封装,将裸露焊盘连接至 GND。                                                                                                                                                                                             |

|    |      |     | •                                                                                                                                                                                                                          |

# **地对最大额定值**

|               | 参数                 | 最小值  | 最大值        | 单位 |  |  |  |

|---------------|--------------------|------|------------|----|--|--|--|

| 温度            |                    |      |            |    |  |  |  |

| 工作温度          |                    | -40  | 125        | °C |  |  |  |

| 存储温度          |                    | -65  | 150        | °C |  |  |  |

| 结温            |                    |      | 150        | °C |  |  |  |

| 同次相           | 铅锡焊接温度(10 秒到 30 秒) |      | 240        | °C |  |  |  |

| 回流焊           | 无铅焊接温度             |      | 260        | °C |  |  |  |

| 耐压            |                    |      |            |    |  |  |  |

| REF、VIO 至 GND |                    | -0.3 | 6          | V  |  |  |  |

| VDD 至 GNE     | )                  | -0.3 | 2          | V  |  |  |  |

| VDD 至 VIO     |                    | 2.3  | -6         | V  |  |  |  |

| IN+、IN-至      | GND                | -0.3 | VREF + 0.3 | V  |  |  |  |

| 数字输入电压        | 玉至 GND             | -0.3 | VIO + 0.3  | V  |  |  |  |

| 数字输出电压至 GND   |                    | -0.3 | VIO + 0.3  | V  |  |  |  |

| ESD           |                    |      | •          |    |  |  |  |

| НВМ           |                    | 2000 |            | V  |  |  |  |

| CDM           |                    | 750  |            | V  |  |  |  |

# 电气规格

默认测试条件: VDD = 1.8V、VIO = 1.71V~5.5V、VREF = 5V、f<sub>SAMPLE</sub> = 1MSPS、TA = − 40°C~125°C。

| 参数          | 测试条件                                                 | 最小值          | 典型值      | 最大值          | 单位     |

|-------------|------------------------------------------------------|--------------|----------|--------------|--------|

| 直流精度        |                                                      |              |          |              |        |

|             | 无失码                                                  | 18           |          |              | Bits   |

| DNL         |                                                      | -0.9         | ±0.7     | 0.9          | LSB    |

| INL         |                                                      | -1.5         | ±1.2     | ±2           | LSB    |

| 增益误差        |                                                      | -0.004       | 0.001    | 0.004        | %FS    |

| 增益误差温漂      |                                                      |              | 0.13     |              | ppm/°C |

| 0 码误差       |                                                      | -4           | ±3       |              | LSB    |

| 0 码误差温漂     |                                                      |              | 0.094    |              | ppm/°C |

| 动态性能        |                                                      |              |          |              |        |

|             | VREF = 5V                                            | 96.9         | 98.9     |              | dB     |

| 动态范围        | VREF = 2.5V                                          | 90.7         | 92.9     |              | dB     |

| 过采样动态范围 1   | $F_0 = 1$ kSPS                                       |              | 129      |              | dB     |

|             | f <sub>IN</sub> = 1kHz, VREF = 5V                    | 96.6         | 97.3     |              | dB     |

| SNR         | $f_{IN} = 1kHz$ , VREF = 2.5V                        | 91.8         | 92.3     |              | dB     |

| CNDD        | f <sub>IN</sub> = 1kHz, VREF = 5V                    | 95.5         | 96.2     |              | dB     |

| SNDR        | $f_{IN} = 1 \text{kHz}, \text{ VREF} = 2.5 \text{V}$ | 91.3         | 91.8     |              | dB     |

| THD         | f <sub>IN</sub> = 1kHz                               |              | -119     |              | dB     |

| SFDR        | f <sub>IN</sub> = 1kHz                               |              | -120     |              | dB     |

| ^+ <u>~</u> | -3dB                                                 |              | 10       |              | MHz    |

| 全功率带宽       | 孔径延迟                                                 |              | 1        |              | ns     |

| PSRR        |                                                      |              | 91       |              | dB     |

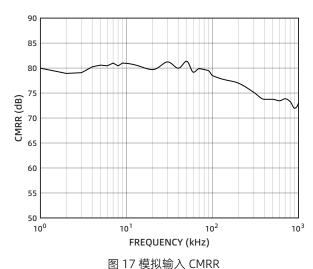

| CMRR        | f <sub>IN</sub> = 450kHz                             |              | 73       |              | dB     |

| 模拟输入        |                                                      | •            |          | <u>.</u>     |        |

| 电压范围        | IN+ - IN-                                            | -VREF        |          | VREF         | V      |

| 绝对输入电压      | IN+, IN-                                             | -0.1         |          | VREF + 0.1   | V      |

| 共模输入范围      | IN+, IN-                                             | VREF × 0.475 | 0.5 VREF | VREF × 0.525 | V      |

| 漏电流         | 采样阶段, TA = 25℃                                       |              | 200      |              | nA     |

| 基准          | •                                                    | •            |          |              |        |

| 电压范围        |                                                      | 2.4          |          | 5.1          | V      |

| 负载电流        |                                                      |              | 470      |              | μΑ     |

| 数字输入/输出     |                                                      |              |          |              |        |

| \/          | VIO > 3V                                             | -0.3         |          | 0.3 VIO      | V      |

| $V_{IL}$    | VIO ≤ 3V                                             | -0.3         |          | 0.1 VIO      | V      |

| 参数              | 测试条件                                 | 最小值       | 典型值  | 最大值       | 单位 |

|-----------------|--------------------------------------|-----------|------|-----------|----|

| V               | VIO > 3V                             | 0.7 VIO   |      | VIO + 0.3 | V  |

| V <sub>IH</sub> | VIO ≤ 3V                             | 0.9 VIO   |      | VIO + 0.3 | V  |

| I <sub>IL</sub> |                                      | -1        |      | 1         | μΑ |

| I <sub>IH</sub> |                                      | -1        |      | 1         | μΑ |

| V <sub>OL</sub> | I <sub>SINK</sub> = 500μA            |           |      | 0.4       | V  |

| V <sub>OH</sub> | I <sub>SOURCE</sub> = -500µA         | VIO - 0.3 |      |           | V  |

| 电源              |                                      | •         |      |           |    |

| VDD             |                                      | 1.71      | 1.8  | 1.89      | V  |

| VIO             |                                      | 1.71      |      | 5.5       | V  |

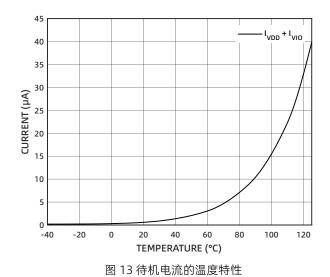

| 待机电流            | VDD = 1.8V, VIO = 3.3V               |           | 0.72 | 40.06     | μΑ |

|                 | 总功耗,f <sub>S</sub> = 10kSPS          |           | 56.5 | 137.8     | μW |

|                 | 总功耗,f <sub>S</sub> =1MSPS            |           | 5.7  | 6.1       | mW |

| Th.#E           | 仅 VDD = 1.8V,f <sub>S</sub> = 10kSPS |           | 33.8 | 106       | μW |

| 功耗              | 仅 VREF = 5V,f <sub>S</sub> = 10kSPS  |           | 21.9 | 31.8      | μW |

|                 | 仅 VDD = 1.8V,f <sub>S</sub> = 1MSPS  |           | 3.3  | 3.6       | mW |

|                 | 仅 VREF = 5V,f <sub>S</sub> = 1MSPS   |           | 2.4  | 2.5       | mW |

注 1: ADC 以  $f_S$  = 1MSPS 的吞吐率采样的数据,经过后级数字滤波器滤波和降采样后,以  $F_O$  = 1kSPS 输出信号的动态范围。

# 时序规格

默认测试条件: VDD = 1.71V~1.89V、VIO = 2.3V~5.5V、f<sub>SAMPLE</sub> = 1MSPS、TA = −40°C~125°C。

| 参数                    | 描述                                    | 最小值  | 典型值 | 最大值 | 单位 |

|-----------------------|---------------------------------------|------|-----|-----|----|

| 通用时序                  |                                       |      |     |     |    |

| t <sub>CONV</sub>     | CNV 上升沿到转换结果有效的转换时间。                  |      | 600 |     | ns |

| t <sub>ACQ</sub>      | 采样时间。                                 |      | 400 |     | ns |

| t <sub>CYC</sub>      | 转换周期。                                 | 1000 |     |     | ns |

| t <sub>CNVHW</sub>    | CNV 高电平脉冲宽度(片选模式)。                    | 10   | -   |     | ns |

| SCLK                  |                                       |      |     |     | l  |

|                       | SCLK 周期(片选模式)。                        |      |     |     |    |

|                       | VIO > 4.5V                            | 10.5 |     |     | ns |

| t <sub>sckcs</sub>    | VIO > 3.3V                            | 12   | ,   | ,   | ns |

|                       | VIO > 2.7V                            | 13   |     |     | ns |

|                       | VIO > 2.3V                            | 15   |     |     | ns |

|                       | SCLK 周期(级联模式)。                        |      |     |     |    |

|                       | VIO > 4.5V                            | 11.5 |     |     | ns |

| t <sub>SCKCH</sub>    | VIO > 3.3V                            | 13   |     |     | ns |

|                       | VIO > 2.7V                            | 14   |     |     | ns |

|                       | VIO > 2.3V                            | 16   |     |     | ns |

| t <sub>SCKLW</sub>    | SCLK 低电平脉冲宽度。                         | 4.5  |     |     | ns |

| t <sub>SCKHW</sub>    | SCLK 高电平脉冲宽度。                         | 4.5  |     |     | ns |

| t <sub>sdohd</sub>    | SCLK 下降沿后数据仍有效保持时间。                   | 3    | 5.6 | 9   | ns |

|                       | SCLK 下降沿到数据有效时间间隔。                    |      | ,   | ,   |    |

|                       | VIO > 4.5V                            |      | 6.5 | 10  | ns |

| t <sub>sdod</sub>     | VIO > 3.3V                            |      | 6.5 | 10  | ns |

|                       | VIO > 2.7V                            |      | 7.3 | 11  | ns |

|                       | VIO > 2.3V                            |      | 8.4 | 13  | ns |

| ————————<br>片选模式时序    |                                       |      | ,   | ,   |    |

|                       | CNV/SDI 变为低电平到 SDO 数据有效时间间隔。          |      |     |     |    |

| t <sub>EN</sub>       | VIO > 3.3V                            |      | ,   | 10  | ns |

|                       | VIO > 2.3V                            |      |     | 16  | ns |

| t <sub>DIS</sub>      | CNV/SDI/最后一个 SCLK 下降沿到 SDO 变为高阻态时间间隔。 |      |     | 20  | ns |

| t <sub>SDICNVST</sub> | CNV 上升沿前 SDI 有效的建立时间。                 | 5    |     |     | ns |

| t <sub>sdicnvhd</sub> | CNV 上升沿后 SDI 有效的保持时间。                 | 2    |     | ,   | ns |

| <br>级联模式时序            |                                       |      |     |     | 1  |

| 参数                    | 描述                            | 最小值 | 典型值 | 最大值 | 单位 |

|-----------------------|-------------------------------|-----|-----|-----|----|

| t <sub>SDICNVHD</sub> | CNV 上升沿后 SDI 有效的保持时间。         | 0   |     |     | ns |

| t <sub>SCKCNVST</sub> | CNV 上升沿前 SCLK 有效的建立时间。        | 5   |     |     | ns |

| t <sub>SCKCNVHD</sub> | CNV 上升沿后 SCLK 有效的保持时间。        | 5   |     |     | ns |

| t <sub>SDISCKST</sub> | SCLK 下降沿前 SDI 有效的建立时间。        | 2   |     |     | ns |

| t <sub>SDISCKHD</sub> | SCLK 下降沿后 SDI 有效的保持时间。        | 3   |     |     | ns |

| t <sub>SDISDOD</sub>  | SDI 高电平到 SDO 高电平时间间隔(带繁忙指示器)。 |     |     | 15  | ns |

默认测试条件: VDD = 1.71V~1.89V、VIO = 1.71V~2.3V、f<sub>SAMPLE</sub> = 800kSPS、TA = -40°C~125°C。

| 参数                    | 描述                                    | 最小值  | 典型值  | 最大值  | 单位 |

|-----------------------|---------------------------------------|------|------|------|----|

| 通用时序                  |                                       |      |      |      | •  |

| t <sub>CONV</sub>     | CNV 上升沿到转换结果有效的转换时间。                  |      | 600  |      | ns |

| t <sub>ACQ</sub>      | 采样时间。                                 |      | 400  |      | ns |

| t <sub>CYC</sub>      | 转换周期。                                 | 1.25 |      |      | μs |

| t <sub>CNVHW</sub>    | CNV 高电平脉冲宽度(片选模式)。                    | 10   |      |      | ns |

| SCLK                  |                                       |      |      |      |    |

| t <sub>SCKCS</sub>    | SCLK 周期(片选模式)。                        | 22   |      |      | ns |

| t <sub>SCKCH</sub>    | SCLK 周期(级联模式)。                        | 23   |      |      | ns |

| t <sub>SCKLW</sub>    | SCLK 低电平脉冲宽度。                         | 6    |      |      | ns |

| t <sub>SCKHW</sub>    | SCLK 高电平脉冲宽度。                         | 6    |      |      | ns |

| t <sub>SDOHD</sub>    | SCLK 下降沿后数据仍有效保持时间。                   | 7    |      |      | ns |

| t <sub>SDOD</sub>     | SCLK 下降沿到数据有效时间间隔。                    |      | 10.9 | 16.5 | ns |

| 片选模式时序                |                                       |      |      |      | •  |

| t <sub>EN</sub>       | CNV/SDI 变为低电平到 SDO 数据有效时间间隔。          |      | 18   | 40   | ns |

| t <sub>DIS</sub>      | CNV/SDI/最后一个 SCLK 下降沿到 SDO 变为高阻态时间间隔。 |      |      | 20   | ns |

| t <sub>SDICNVST</sub> | CNV 上升沿前 SDI 有效的建立时间。                 | 5    |      |      | ns |

| t <sub>SDICNVHD</sub> | CNV 上升沿后 SDI 有效的保持时间。                 | 5    |      |      | ns |

| 级联模式时序                |                                       |      |      |      |    |

| t <sub>SDICNVHD</sub> | CNV 上升沿后 SDI 有效的保持时间。                 | 0    |      |      | ns |

| t <sub>SCKCNVST</sub> | CNV 上升沿前 SCLK 有效的建立时间。                | 5    |      |      | ns |

| t <sub>SCKCNVHD</sub> | CNV 上升沿后 SCLK 有效的保持时间。                | 5    |      |      | ns |

| t <sub>SDISCKST</sub> | SCLK 下降沿前 SDI 有效的建立时间。                | 2    |      |      | ns |

| t <sub>SDISCKHD</sub> | SCLK 下降沿后 SDI 有效的保持时间。                | 3    |      |      | ns |

| t <sub>SDISDOD</sub>  | SDI 高电平到 SDO 高电平时间间隔(带繁忙指示器)。         |      |      | 22   | ns |

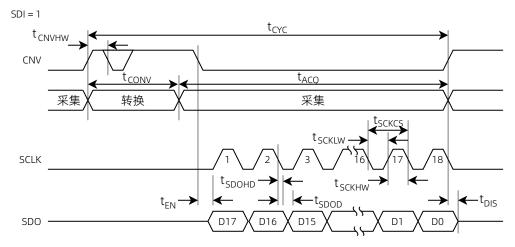

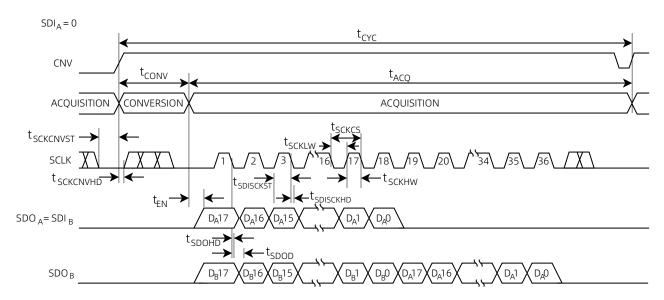

图 1 无繁忙指示三线串行接口时序(片选模式)

图 2 有繁忙指示三线串行接口时序(片选模式)

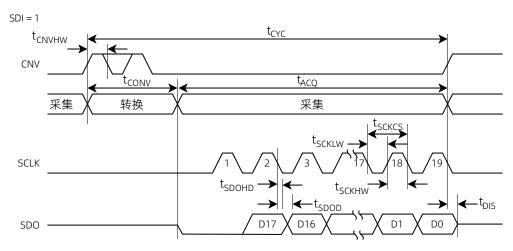

图 3 无繁忙指示四线串行接口时序(片选模式)

图 4 有繁忙指示四线串行接口时序(片选模式)

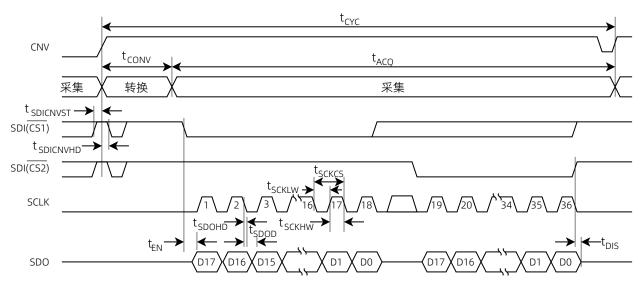

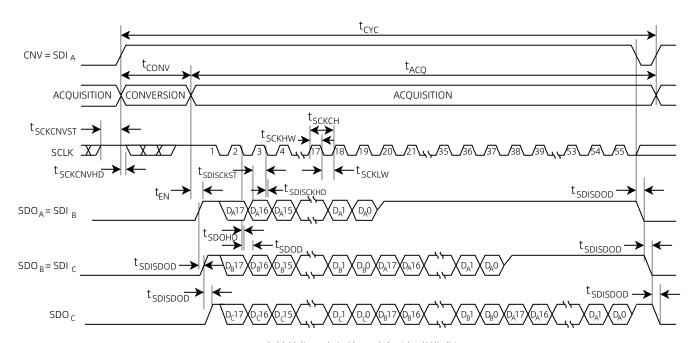

图 5 无繁忙指示串行接口时序(级联模式)

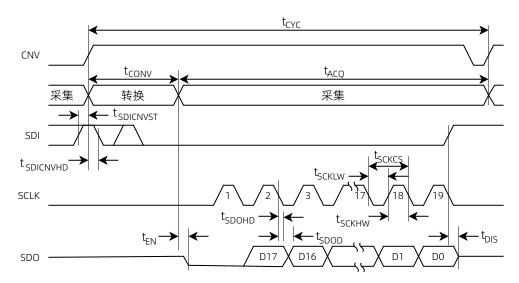

图 6 有繁忙指示串行接口时序(级联模式)

## 典型特征

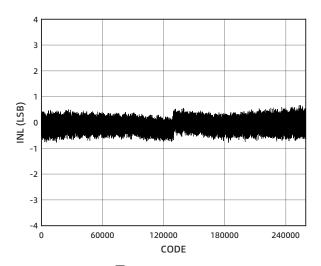

图 7 INL, VREF = 5V

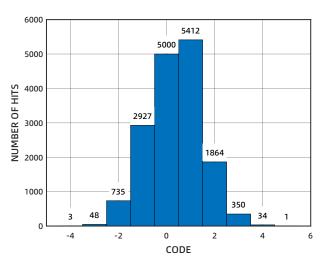

图 9 直流输入直方图 (码中心)

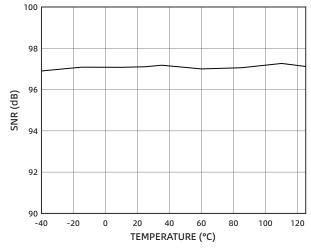

图 11 SNR 的温度特性

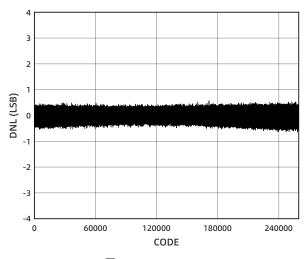

图 8 DNL, VREF = 5V

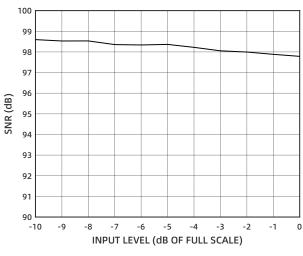

图 10 SNR 随输入电平的变化

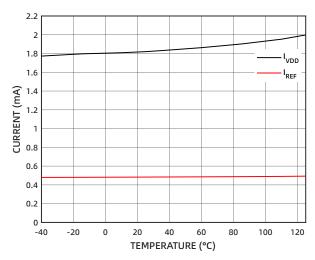

图 12 工作电流的温度特性

### 工作原理

图 15 ADC 原理示意图

CM2322 是一款高速、低功耗、单电源、精密 18 位 SAR ADC。

CM2322 最高转换速率可达 1MSPS, 两次转换之间芯片处于关断状态。以 10kSPS 速率工作时, 典型功耗为 56.5µW, 是电池供电应用的理想选择。

CM2322 为用户提供片内采样保持电路,没有任何流水线延迟, 非常适合多通道复用的应用。

CM2322 可与任何 1.8V 至 5V 数字逻辑接口相连,提供 MSOP10 和 DFN10 封装,节省空间,配置灵活。

CM2322 的管脚和 CM2220 的管脚完全兼容。

## 转换器操作

CM2322 是一款基于电荷再分配 DAC 的 SAR ADC。图 15 显示 了该 ADC 的简化电路图。容性 DAC 包含两个完全相同的 18 位 二进制加权电容阵列,分别连接到比较器的两个输入端。

在采样阶段,与比较器输入端相连的电容阵列的顶板通过SW+和SW-连接到GND。所有独立开关都连接到模拟输入端。因此,电容阵列用作采样电容,并采集IN+和IN-输入端的模拟信号。当采样阶段完成且CNV输入变为高电平时,转换阶段启动。当转换阶段开始时,SW+和SW-首先断开,然后两个电容阵列从输入端断开,并连接到GND输入端。采样阶段结束时捕捉到的IN+和IN-之间的电压差施加于比较器输入端,将会导致比较器不平衡。电容阵列中的各电容底板在GND和REF之间切换,比较器输入将按照二进制加权电压步进(VREF/2、VREF/4...VREF/262144)变化。控制逻辑从MSB开始切换这些开关,以使比较器重新回到平衡状态。完成此过程后,芯片返回采样阶段,控制逻辑将产生ADC输出码和繁忙信号指示。

CM2322 具有一个片上转换时钟,转换过程不需要串行时钟 SCLK。

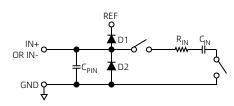

### 模拟输入

图 16 显示了 CM2322 输入等效电路。两个二极管 D1 和 D2 为模拟输入 IN+和 IN-提供 ESD 保护。注意,模拟输入信号不能超过供电轨 0.3V 以上,否则会造成二极管正偏,并开始传导电流。这些二极管可以处理最高 130mA 的正偏电流。当输入缓冲器的电源与 REF 不同时,可以利用具有过流保护功能的输入缓冲器保护芯片。

图 16 等效模拟输入电路

该模拟输入结构支持 IN+和 IN-之间真差分信号的采样。借助这些差分输入,可以抑制两个输入端的共模信号,如图 17 所示。

在采样阶段,IN+和 IN-模拟输入电路可看成是  $R_{IN}$  和  $C_{IN}$  串联后,整体与输入管脚的寄生电容  $C_{PIN}$  并联。 $C_{PIN}$  是指管脚寄生电容。 $R_{IN}$  典型值为  $400\Omega$ ,由输入串联电阻与采样开关的导通电阻构成。 $C_{IN}$  典型值为 30pF,是指 ADC 采样电容。

在采样阶段,开关闭合时,输入阻抗受限于  $C_{PIN}$ 。  $R_{IN}$  和  $C_{IN}$  构成一个单极点低通滤波器,可以降低混叠效应并限制噪声。

当驱动电路的源阻抗较低时,可以直接驱动 CM2322。较大的源阻抗会显著影响交流特性,特别是 THD,而直流特性对输入阻抗的敏感度较低。源阻抗最大值取决于可容许的总谐波失真 THD。THD 性能下降程度是源阻抗和最大输入频率的函数。

## 电压基准输入

CM2322 电压基准输入 REF 端具有动态输入阻抗,因此应利用低阻抗源驱动,REF 与 GND 管脚之间应有效去耦。

利用低输出阻抗基准源电压驱动器驱动 REF 端时,为了使 ADC 实现最佳性能,需要在驱动器输出端加 10µF (X5R) 陶瓷电容,而且在 PCB 布局中电容应尽量靠近 ADC 芯片的 REF 端。

如果使用无缓冲基准电压,去耦值取决于所使用的基准电压源。

REF 和 GND 管脚之间不需要额外的低值陶瓷去耦电容(如 100nF)。

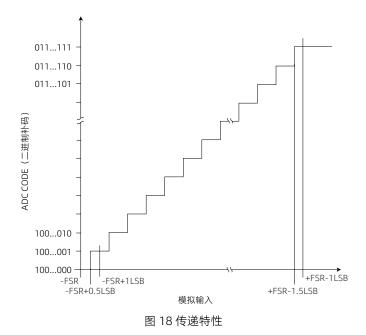

## 传递函数

CM2322 的理想传递特性如图 18 和表 2 所示。

表 2 输出码和理想输入电压

| 描述        | 模拟输入       |             |  |  |

|-----------|------------|-------------|--|--|

| 佃处        | VREF = 5V  | 数字输出码(十六进制) |  |  |

| FSR-1LSB  | 4.999962V  | 0x1FFFF     |  |  |

| 中间电平+1LSB | 38.15µV    | 0x00001     |  |  |

| 中间电平      | 0V         | 0x00000     |  |  |

| 中间电平-1LSB | -38.15µV   | 0x3FFFF     |  |  |

| -FSR+1LSB | -4.999962V | 0x20001     |  |  |

| -FSR      | -5V        | 0x20000     |  |  |

#### 驱动放大器

虽然 CM2322 易于驱动, 但驱动放大器仍需满足以下要求:

驱动放大器产生的噪声需尽可能低,以保持 CM2322 的 SNR 和转换噪声性能。来自驱动器的噪声由 CM2322 模拟输入电路中 R<sub>IN</sub> 和 C<sub>IN</sub> 所构成的单极点低通滤波器进行滤波,或者由外部滤波器(如存在)进行滤波。CM2322 的典型噪声为40μVrms,则放大器引起的 SNR 性能降幅为:

SNR<sub>LOSS</sub> = 20log

$$\sqrt{\frac{40}{\sqrt{40^2 + \frac{\pi}{2}} f_{-3dB} (Ne_N)^2}}$$

其中:  $f_{-3dB}$  为 CM2322 的输入带宽 (10MHz),或者输入滤波器 (如存在)的截止频率。N 为放大器的噪声增益(例如,缓冲器配置时为 1)。 $e_N$  为运算放大器的等效输入电压噪声,单位为 $nV/\sqrt{Hz}$ 。

- 对于交流应用,驱动器的 THD 性能应与 CM2322 相当。

- 对于多通道、多路复用应用,要满足满量程阶跃信号的采样精度,驱动放大器和前端模拟输入电路必须在采样时间内将采样电容底板电压建立到满量程输入的 18 位精度水平(误差小于 0.0004%,4ppm)。而常见放大器建立时间的规格是基于建立误差在 0.1%或者 0.01%时测量值,这与 18 位精度要求不匹配,因此在选择放大器时需要验证建立时间和精度是否足够。

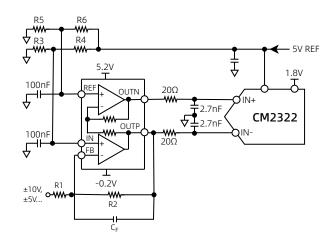

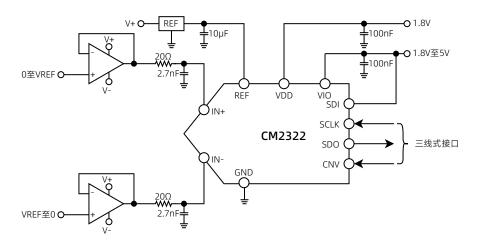

## 单端转差分驱动器

对于使用单端模拟信号(双极性或单极性)的应用,单端转差分驱动器可以为该芯片提供差分输入,原理见图 19。

R1 和 R2 设置输入范围与 VREF 之间的衰减比。R1、R2 和 C<sub>F</sub> 根据所需的输入电阻、信号带宽、抗混叠要求和噪声贡献进行选择。例如,对于 $\pm 10V$  范围和  $4k\Omega$  输入阻抗,R2 =  $1k\Omega$ ,R1 =  $4k\Omega$ 。

R3 和 R4 设置 IN-输入的共模电压,R5 和 R6 设置 IN+输入的共模电压。共模电压应靠近 VREF/2。例如,对于使用单电源的  $\pm 10V$  范围,R3 =  $8.45k\Omega$ ,R4 =  $11.8k\Omega$ ,R5 =  $10.5k\Omega$ ,R6 =  $9.76k\Omega$ 。

图 19 单端转差分驱动器电路

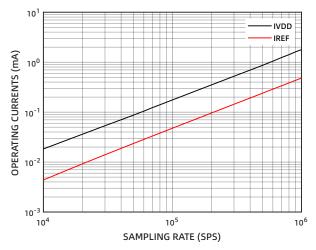

## 功耗

CM2322 使用两个电源管脚: 内核电源 VDD 以及数字输入/输出接口电源 VIO。VIO 可以接 1.8V 至 5.0V 的任意值以适配数字接口逻辑电平。为减少所需的电源数,VIO 和 VDD 管脚可以连在一起。CM2322 中 VIO 和 VDD 的电源时序无关。此外,该芯片在较宽的频率范围内对电源变化不敏感。

CM2322 在每个转换阶段结束时自动关断,并且功耗与采样速率成线性比例关系。这使得该芯片非常适合低采样速率(甚至几Hz)和低功率电池供电的应用。

图 20 工作电流随采样率的变化

## 数字接口

CM2322 提供了四个数字接口管脚,支持片选和级联两种通信模式。在片选模式下,数字接口兼容 SPI、QSPI、MICROWIRE。在级联模式下,CM2322 提供了以菊花链方式连接的属性,实现多个 ADC 的级联读取。

数字接口的通信模式取决于 CNV 上升沿时刻的 SDI 电平:当 CNV 上升沿时,SDI 为高电平,则芯片进入片选模式;当 CNV 上升沿时,SDI 为低电平,或者 CNV 和 SDI 短接在一起(即同沿变化时),芯片进入级联模式。

芯片同时提供繁忙指示信号供主机作为中断源使用,用于指示主机在何时可以开始读取有效转换结果。主机可通过配置选择是否开启繁忙指示功能: 片选模式下,转换结束 (EOC) 时,如果片选使能(三线串口片选使能为 CNV,四线串口片选使能为 SDI)为低电平,则芯片繁忙指示信号使能(参见图 2 和图 4);级联模式下,如果 CNV 上升沿时,SCLK 为高电平,则芯片繁忙指示信号使能(参见图 6)。

芯片繁忙指示信号开启时,SDO 在转换结束且片选有效后变为低电平,主机以此作为中断源触发读取 ADC 转换结果进程:连续发送 SCLK 时钟,芯片将在 SCLK 下降沿,依次将转换结果的 MSB 到 LSB 输出。主机可在 SCLK 下降沿后的上升沿逐个读取 ADC 结果,也可从第二个 SCLK 下降沿开始读取 ADC 结果(只要主机能在数据的保持时间内完成读取,下降沿采样可以获得更高的 SPI 速率)。

芯片繁忙指示信号关闭时,SDO 在转换结束且片选有效后变为当前转换结果的 MSB 电平,随后主机连续发送 SCLK 时钟,芯片将在 SCLK 下降沿,依次将转换结果的 MSB-1 到 LSB 输出。主机可在 SCLK 上升沿或下降沿依次读取转换结果。

## 片选模式

#### 三线串口无繁忙指示

如果主机可用管脚数量受限,可选择三线串口,如图 21 和图 1 所示。三线串口下,SDI 需固定短接到 VIO 电平。CNV 既作为转换启动信号,也作为片选使能信号。CNV 上升沿启动转换,转换结束后,CNV 低电平将选中当前芯片,用于转换结果输出。在转换结束时 (EOC),片选使能 CNV 必须为高电平,确保芯片的繁忙指示信号不被开启。此模式下,主机最少可发送 17 个 SCLK时钟下降沿,将转换结果输出。在转换期间或片选使能 CNV 为高电平期间,SDO 都将保持高阻态输出。在转换结束后,主机发送完 18 个 SCLK 下降沿后,SDO 也将返回高阻态。

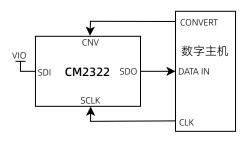

图 21 三线串口无繁忙指示连接图(片选模式)

#### 三线串口有繁忙指示

与三线串口无繁忙指示的区别在于:转换结束时 (EOC),片选使能 CNV 为低电平。此时,芯片繁忙指示信号将被开启。主机将至少发送 18 个 SCLK 时钟下降沿,才可将转换结果全部输出。在第 19 个下降沿后,SDO 返回高阻态,如图 22 和图 2 所示。

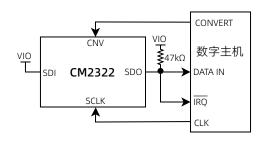

图 22 三线串口有繁忙指示连接图(片选模式)

#### 四线串口无繁忙指示

配置为此模式时,SDI将作为片选使能,CNV仅作为转换启动信号。CNV上升沿启动转换,转换结束后,SDI低电平将选中当前芯片,用于转换结果输出。在转换结束时(EOC),片选使能SDI必须为高电平,确保芯片的繁忙指示信号不被开启。此模式下,主机最少可发送17个SCLK时钟下降沿,将转换结果输出。在转换期间或片选使能SDI为高电平期间,SDO都将保持高阻态输出。在转换结束后,主机发送完18个SCLK下降沿后,SDO也将返回高阻态,如图23和图3所示。

图 23 四线串口无繁忙指示连接图(片选模式)

#### 四线串口有繁忙指示

要配置为此模式,需在转换结束 (EOC) 时,片选使能 SDI 为低电平。主机将至少发送 18 个 SCLK 时钟下降沿,才可将转换结果全部输出。在第 19 个下降沿后,SDO 返回高阻态,如图 24 和图 4 所示。

图 24 四线串口有繁忙指示连接图 (片选模式)

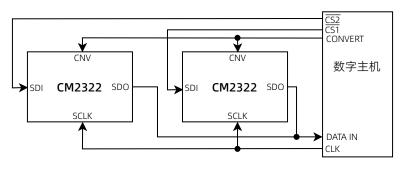

保数据接口的正确性。转换结束时 (EOC),MSB 数据将被输出到 SDO。在主机发送的 SCLK 下降沿,依次将剩余的 MSB-1 到 LSB 数据输出。级联模式下,各级联芯片的 SDI 和 SDO 首尾相接,前一级的转换结果首先被移位输出到下一级,待下一级的转换结果输出后再依次输出。因此,对于 N 个 ADC 级联的场景,需要提供 18 × N 个时钟,才能回读完所有芯片的转换结果,如图 25 和图 5 所示。

#### 有繁忙指示

该模式下,如果 SCLK 在 CNV 上升沿保持高电平,则开启繁忙指示信号。在转换结束时,SDO 会变为低电平输出,作为中断源提供给主机,用于主机进程触发 SCLK 的发送,读取转换结果。相较于无繁忙指示模式,由于 MSB 不会被提前放置到 SDO 上,必须通过 SCLK 下降沿输出。因此,对于 N 个 ADC 级联的场景,需要提供 18× N + 1 个时钟,才能回读完所有芯片的转换结果,如图 26 和图 6 所示。

### 级联模式

#### 无繁忙指示

要配置为此模式,需在 CNV 上升沿,SCLK 保持为低电平。随后,在主机读取完本次转换结果前,CNV 都应保持高电平,以确

图 25 无繁忙指示连接图 (级联模式)

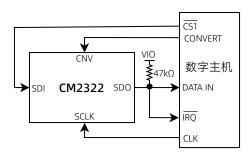

图 26 有繁忙指示连接图(级联模式)

# 应用

## 典型连接

图 27 为采用多个电源时 CM2322 的建议连接图。

图 27 采用多个电源的典型应用电路

# 封装及订购信息

## 封装方式

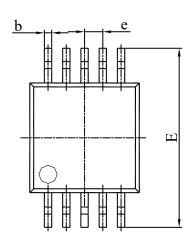

CM2322 采用 MSOP10 和 DFN10 封装。

## 产品外形图

#### MSOP10

产品外形图如下图所示。

| 标识    | 尺寸 (毫米) |            |      |  |

|-------|---------|------------|------|--|

| የሁ ኑላ | 最小值     | 典型值        | 最大值  |  |

| А     | 0.82    | 0.96       | 1.10 |  |

| A1    | 0.02    | 0.09       | 0.15 |  |

| A2    | 0.75    | 0.85       | 0.95 |  |

| b     | 0.18    | 0.23       | 0.28 |  |

| С     | 0.09    | 0.16       | 0.23 |  |

| D     | 2.90    | 3.00       | 3.10 |  |

| е     |         | 0.50 (BSC) |      |  |

| E     | 4.75    | 4.90       | 5.05 |  |

| E1    | 2.90    | 3.00       | 3.10 |  |

| L     | 0.40    | 0.60       | 0.80 |  |

| θ     | 0°      | 3°         | 6°   |  |

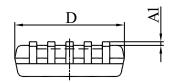

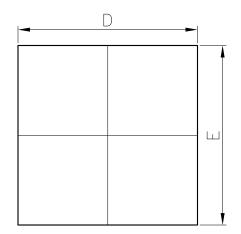

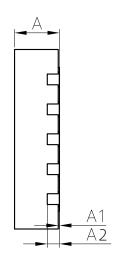

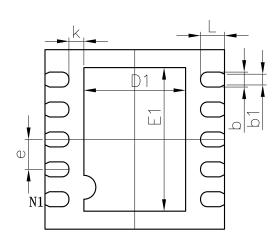

### DFN10

产品外形图如下图所示。

| 标识 | 尺寸 (毫米)    |      |      |  |  |

|----|------------|------|------|--|--|

|    | 最小值        | 典型值  | 最大值  |  |  |

| А  | 0.70       | 0.75 | 0.80 |  |  |

| A1 | 0          | 0.03 | 0.05 |  |  |

| A2 | 0.20 (REF) |      |      |  |  |

| D  | 2.92       | 3.00 | 3.08 |  |  |

| E  | 2.92       | 3.00 | 3.08 |  |  |

| D1 | 1.60       | 1.70 | 1.80 |  |  |

| E1 | 2.30       | 2.40 | 2.50 |  |  |

| b  | 0.20       | 0.25 | 0.30 |  |  |

| b1 | 0.18 (REF) |      |      |  |  |

| е  | 0.50 (BSC) |      |      |  |  |

| k  | 0.25 (REF) |      |      |  |  |

| L  | 0.32       | 0.40 | 0.48 |  |  |

# 订购信息

| 型号           | 温度范围        | 封装     | 包装   | 包装数量 |

|--------------|-------------|--------|------|------|

| CM2322-MSOTA | -40°C~125°C | MSOP10 | Reel | 4000 |

| CM2322-DFNTA | -40°C~125°C | DFN10  | Reel | 5000 |