# JW7726HAD

# 100V, 10mΩ Synchronous Rectifier

Preliminary Specifications Subject to Change without Notice

# **DESCRIPTION**

JW7726HAD is a synchronous rectifier, used for the secondary side rectification of isolation topologies, such as Active Clamp Flyback and CCM/QR/DCM Flyback. JW7726HAD is able to significantly improve the efficiency comparing with the conventional Diode rectifier.

When JW7726HAD senses  $V_{ds}$  of MOSFET less than -140mV, it turns on the internal MOSFET. Once the  $V_{ds}$  is greater than -6mV, JW7726HAD turns off the internal MOSFET.

JW7726HAD supports multiple operation modes, such as DCM, CrCM, CCM and Quasi-Resonant. By implementing the Joulwatt proprietary technology, JW7726HAD is able to handle CCM operation.

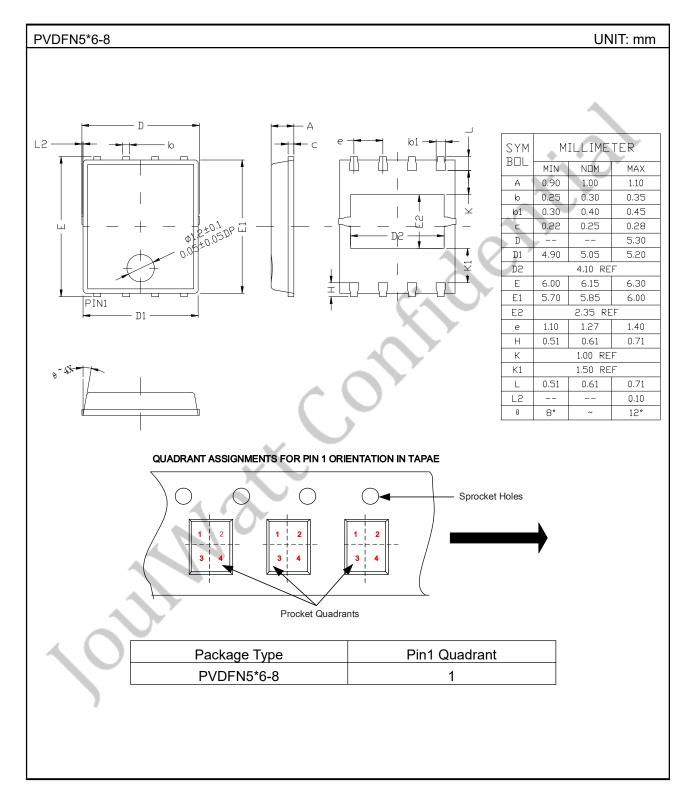

JW7726HAD is available in PVDFN5\*6-8 package.

Company's Logo is Protected, "JW" and "JOULWATT" are Registered

Trademarks of JoulWatt technology Co., Ltd.

#### **FEATURES**

- Supports Active Clamp Flyback, DCM, Quasi-Resonant, and CCM Flyback

- Support High-side and Low-side Rectification

- Output Voltage Directly Supply VCC

- Low Quiescent Current

- Fast Driver Capability for CCM Operation

- PVDFN5\*6-8 Package

## **APPLICATIONS**

- Active Clamp Flyback and Flyback Converters

- Adaptor

- LCD and PDP TV

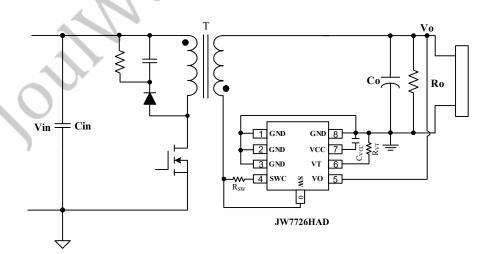

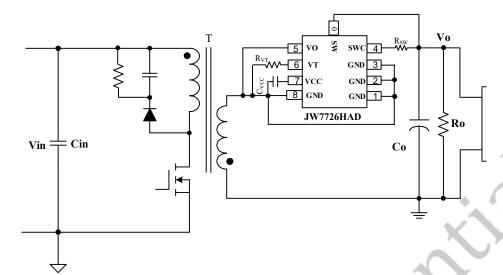

### TYPICAL APPLICATION

JW7726HAD Typical Application for Low-side

JW7726HAD Typical Application for High-side.

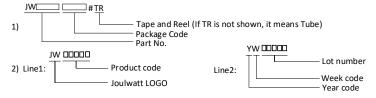

# **ORDER INFORMATION**

| DEVICE <sup>1)</sup> | PACKAGE     | TOP MARKING <sup>2)</sup> | ENVIRONMENTAL <sup>3)</sup> |  |

|----------------------|-------------|---------------------------|-----------------------------|--|

| IW/7726HADDVDLOF#TD  | PVDFN5*6-8  | JW7726HAD                 | Green                       |  |

| JW7726HADPVDLQF#TR   | PADLIN2.0-9 | YW□□□□                    |                             |  |

#### Notes:

3) All Joulwatt products are packaged with Pb-free and Halogen-free materials and compliant to RoHS standards.

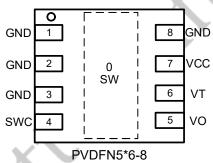

# **PIN CONFIGURATION**

#### **TOP VIEW**

# ABSOLUTE MAXIMUM RATING1)

| SW PIN                                                                   | 100V         |

|--------------------------------------------------------------------------|--------------|

| SWC PIN                                                                  | 1 to 100V    |

| VO PIN                                                                   | 0.3to 28V    |

| VCC PIN                                                                  | 0.3to 9V     |

| VT PIN                                                                   | 0.3 to 7V    |

| Junction Temperature <sup>2) 3)</sup>                                    | 150°C        |

| Lead Temperature                                                         |              |

| Storage Temperature                                                      | 65°C to150°C |

| Continuous Power Dissipation(T <sub>A</sub> =+25°C) <sup>4)</sup> ESOP-8 | 2.5W         |

| ESD Susceptibility (Human Body Model)                                    | 2kV          |

# RECOMMENDED OPERATING CONDITIONS

| SW Pin                                          | 4.7V to 80V                  |

|-------------------------------------------------|------------------------------|

| SWC Pin                                         | 4.7V to 80V                  |

| VO Pin                                          | 4.7V to 25V                  |

| VCC PIN                                         | 4V to 8.5V                   |

| Operation Junction Temperature(T <sub>J</sub> ) | 40°C to 125°C                |

| THERMAL PERFORMANCE <sup>5)</sup>               | $	heta_{J\!A}  	heta_{J\!c}$ |

| PVDFN5*6-8                                      | 3°C/W                        |

#### Note:

- 1) Exceeding these ratings may damage the device. These stress rating do not imply function operation of the device at any other conditions beyond those indicated under RECOMMENDED OPERATING CONDITIONS.

- 2) Continuous operation over the specified absolute maximum operating junction temperature may damage the device.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D(MAX)=(T_J(MAX)-T_A)/\theta_{JA}$ .

- 5) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

TA = 25°C, unless otherwise stated

Advance Information, not production data, subject to change without notice.

| Item                               | Symbol                  | Min.                     | Тур. | Max. | Units |    |

|------------------------------------|-------------------------|--------------------------|------|------|-------|----|

| VCC Section                        |                         |                          |      |      |       |    |

| VCC Voltage                        | VCC                     | SW=40V, VCC=2.2uF        | 7.4  | 7.9  | 8.4   | ٧  |

| VCC Startup Voltage                | V <sub>CC_Startup</sub> |                          | 4.2  | 4.5  | 4.8   | V  |

| VCC UVLO                           | V <sub>CC_UVLO</sub>    |                          | 3.7  | 3.95 | 4.2   | >  |

| Operation Current (GT On)          | lvcc                    | GT=5nF,VCC=2.2uF         | 0.65 | 1.05 | 1.35  | mA |

| Quiescent Current                  | Iq                      | VCC=4.5V, VCC=2.2uF      |      | 110  |       | uA |

| SWC and VO Section                 |                         |                          |      |      |       |    |

| Internal MOS Turn on Threshold     | $V_{\text{MOS\_ON}}$    | *                        | -170 | -140 | -110  | mV |

| Internal MOS Turn off Threshold 6) | V <sub>MOS_OFF</sub>    |                          | )    | -6   |       | mV |

| Internal MOS Minimum on Time 6)    | T <sub>MIN_ON</sub>     |                          | la.  | 560  |       | ns |

| Turn-on Total Delay <sup>6)</sup>  | $T_DON$                 |                          |      | 50   |       | nS |

| Turn-off Total Delay <sup>6)</sup> | $T_DOF$                 |                          |      | 20   |       | nS |

| VCC Charge Current                 | Isw_chg                 | SW=40V, VCC=6V           | 75   | 95   |       | mA |

| VO Enable Charge Voltage           | V <sub>O_EN</sub>       | VCC=4V, SW=0V, rising    | 4.48 | 4.6  | 4.8   | ٧  |

| VO Disable Charge Voltage          | Vo_dis                  | VCC=4V, SW=0V, falling   | 4.4  | 4.55 | 4.7   | V  |

| VO Charge Current                  | Ivo_сна                 | SW=0V, VCC=6V,<br>VO=12V | 28   | 40   | 52    | mA |

| Internal MOSFET(SW) Section        |                         |                          |      |      |       |    |

| Internal MOSFET Rdson              | Rdson                   | VGT=10V                  |      | 10   |       | mΩ |

| Breakdown Voltage                  | B <sub>(BR)DSS</sub>    | 100                      |      |      | V     |    |

#### Note:

6) Guaranteed by design.

# **PIN DESCRIPTION**

| Pin     | Name | Description                                                   |  |  |  |  |  |  |

|---------|------|---------------------------------------------------------------|--|--|--|--|--|--|

| 1,2,3,8 | GND  | Ground.                                                       |  |  |  |  |  |  |

| 4       | SWC  | Internal Power MOSFET Drain Voltage Sensing. Charging to VCC. |  |  |  |  |  |  |

| 5       | VO   | Output Voltage Sensing and Charging to VCC.                   |  |  |  |  |  |  |

| 6       | VT   | Set the Voltage-second Product.                               |  |  |  |  |  |  |

| 7       | VCC  | Power Supply. Bypass a Capacitor Between VCC and GND.         |  |  |  |  |  |  |

| 0       | SW   | Internal Power MOSFET Drain.                                  |  |  |  |  |  |  |

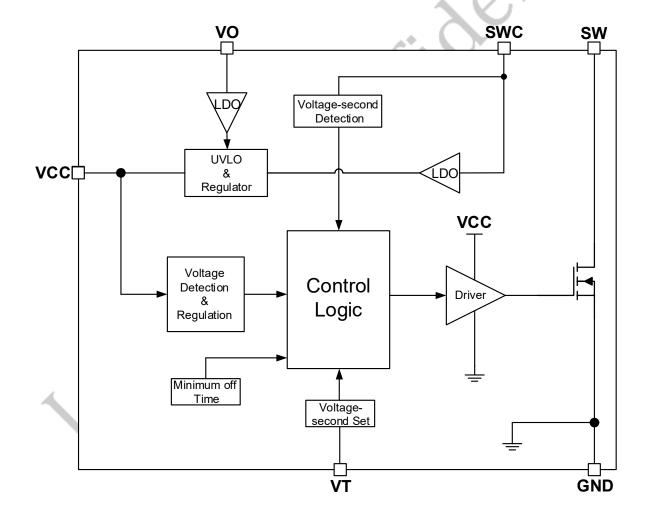

# **BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

#### Operation

JW7726HAD is а synchronous rectifier combined with internal MOSFET can replace the Schottky Barrier Diode. It supports all operations, such as DCM. CrCM. (Quasi-Resonant) and CCM when adopted in Active Clamp Flyback and Flyback converters.

# Startup

During the startup period, when the VCC is charged up by the two internal LDOs connected to SW and VO pin respectively.

When VO is lower than VO EN (falling), JW7726HAD can power itself through the internal LDO connected to SW pin during the SR turn-off period, which means primary the primary side MOSFET is turned on and SW presents a positive voltage. A capacitor between VCC and GND is required to store the energy and supply to IC during the SR turn-on period.

When VO is above Vo EN (rising), the VO pin charges VCC pin.

Once the VCC voltage exceeds Vcc\_Startup, the JW7726HAD exits the UVLO. If VCC is lower than V<sub>CC UVLO</sub>, the internal MOSFET is turned off. The current flows though body diode before the VCC reaches to the startup voltage V<sub>cc</sub> startup.

# **Under-Voltage Lockout (UVLO)**

When the VCC is below UVLO threshold, the internal MOSFET is turned off and pulled low internally. Once the VCC exceeds the startup voltage Vcc startup, the parts is activated again.

#### **Turn On Phase**

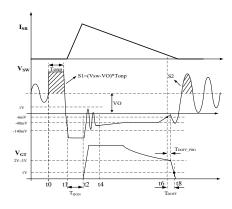

There are two conditions for the JW7726HAD to turn on the internal MOSFET, i.e. V<sub>SW</sub>, voltage-second value on SW pin when primary side switch is on, and the turn on phase is shown in Fig. 1.

- 1) Vsw: when the synchronous MOEFET is conducting, current flows through the body diode of MOSFET, which generates a negative voltage V<sub>SW</sub> across it. When V<sub>SW</sub> is lower than V<sub>MOS ON</sub>, the part will pull the gate high to turn on the synchronous MOSFET after turn on delay time T<sub>DON</sub> if the other condition is met.

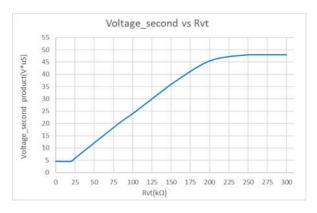

- 2) Volt-second of SW: in DCM and QR operation, there are parasitic oscillations. In some applications, the drain resonant voltage may fall below the SR turn on threshold, especially for the first couple rings. SR could be falsely turned on, which may cause shoot through issue and result in high power loss. The volt-second value of SW pin can be used to distinguish the parasitic ring from normal primary side switch on. The threshold can be set by the resistance at VT pin. The curve is shown in Fig. 2.

Fig. 1 Turn on delay and turn off delay

Fig. 2 Volt-second value vs. VT resistance

Minimum On Time (MOT)

When the synchronous MOSFET is turn on, there is a minimum on time for the SR. The  $V_{SW}$  voltage may have a parasitic ring when the synchronous MOSFET turns on. So, a minimum on time (MOT) is very important to avoid the MOSFET turn off threshold is false triggered.

# **Conducting Phase**

When the synchronous MOSFET is turned on, the drain source voltage  $V_{\text{SW}}$  it is determined by its on resistance and the current through it. The part adjusts the gate voltage and regulates the  $V_{\text{SW}}$  to the internal threshold (typical -40mV) after the synchronous MOSFET turn on. When the  $V_{\text{SW}}$  is lower than -40mV, the gate keeps its maximum voltage. And the synchronous MOSFET is fully on.

The  $V_{SW}$  rises when the current follow through the MOSFET decreases. The gate voltage will be decreased to increase its on resistance and regulate the  $V_{SW}$  around -40mV.

It should be noted that the typical regulation threshold (-40mV) during MOSFET on time is not fixed, it can be internally changed to ensure the proper operation under CCM mode.

#### **Turn Off Phase**

After synchronous MOSFET conducting, once the voltage  $V_{\text{SW}}$  touches the MOSFET turn off threshold , the gate is pulled to low after a turn off delay time  $T_{\text{DOFF}}$ .

### **Output Voltage Detection**

The JW7726HAD has output voltage detection function via VO pin. VCC is charged from VO pin when VO is higher than  $V_{O\_EN}$  to save power loss caused by the LDO when charging from SW pin to VCC pin. When VO drops below  $V_{O\_DIS}$ , the JW7726HAD is powered from SW pin.

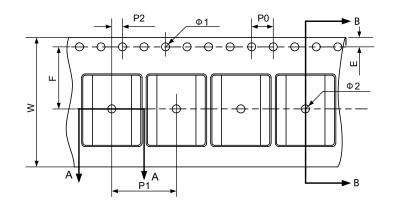

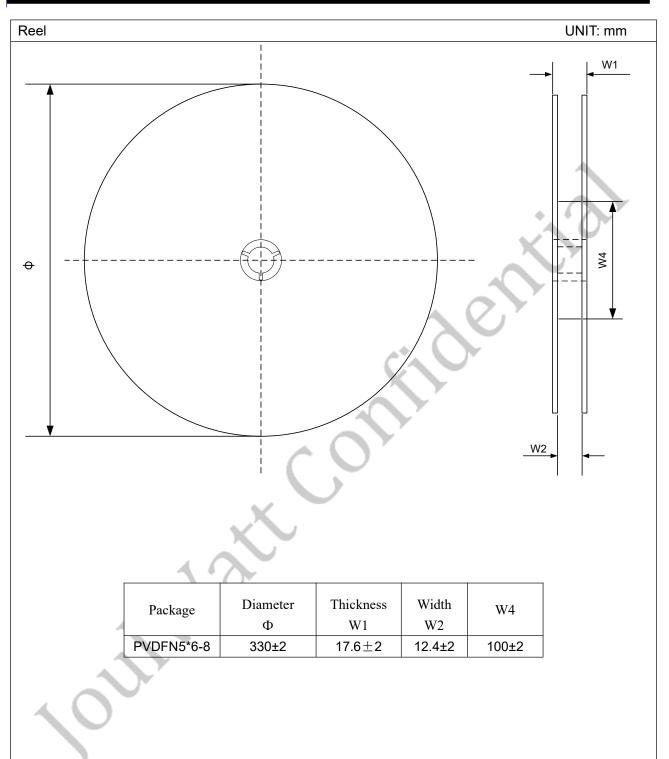

# TAPE AND REEL INFORMATION

UNIT: mm Carrier Tape

SECTION A-A

- The carrier type is black, and colorless transparent.

Carrier camber is within 1mm in 100mm.

- 3) 10 pocket hole pitch cumulative tolerance:±0.20.

- 4) All dimensions are in mm.

| I | Daalaasa   | Tape dimensions (mm) |         |           |          |          |          |         |          |         |         |          |           |

|---|------------|----------------------|---------|-----------|----------|----------|----------|---------|----------|---------|---------|----------|-----------|

| l | Package    | Р0                   | P2      | P1        | A0       | В0       | W        | T       | K0       | Ф1      | Ф2      | Е        | F         |

|   | PVDFN5*6-8 | 4.0±0.1              | 2.0±0.1 | 8.00±0.10 | 6.40±0.2 | 5.42±0.2 | 12.0±0.3 | 0.2±0.1 | 1.25±0.2 | 1.50min | 1.50min | 1.75±0.1 | 5.50±0.10 |

# **PACKAGE OUTLINE**

### **IMPORTANT NOTICE**

Joulwatt Technology Co.,Ltd reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein.

- Any unauthorized redistribution or copy of this document for any purpose is strictly forbidden.

- Joulwatt Technology Co.,Ltd does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- JOULWATT TECHNOLOGY CO.,LTD PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, SAFETY INFORMATION AND OTHER RESOURCES, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

Copyright © 2023 JoulWatt

All rights are reserved by Joulwatt Technology Co., Ltd