# CMC693PR144-L 芯片 数据手册

宁波中控微电子有限公司

## 声明

- 严禁转载本手册的部分或全部内容。

- 在不经预告和联系的情况下,本手册的内容有可能发生变更,请谅解。

- 本手册所记载的内容,不排除有误记或遗漏的可能性。如对本手册内容有疑问, 请与我公司联系。

## 目录

| 1 | 简介                 | <b></b> 1 |

|---|--------------------|-----------|

|   | 1.1 概述             | 1         |

|   | 1.2 典型特性           | 1         |

|   | 1.3 芯片结构图          | 1         |

| 2 | 管脚信息               | 2         |

|   | 2.1 管脚分布           |           |

|   | 2.2 管脚总表           | 3         |

| 3 | 功能描述               |           |

| J | 3.1 系统时钟           |           |

|   | 3.2 工作模式           |           |

|   | 3.3 芯片复位           |           |

|   | 3.4 看门狗 WDT        |           |

|   | 3.5 片内 FLASH       |           |

|   | 3.6 通用定时器          |           |

|   | 3. 7 ITAG          |           |

|   | 3.8 通用输入输出 GPIO    |           |

|   | 3.9 脉冲输入输出 PIPO    |           |

|   | 3.10 通信接口          |           |

|   | 3. 10. 1 UART 串行通信 |           |

|   | 3. 10. 2 I2C 通信    | . 11      |

|   | 3.10.3 SPI 通信      |           |

|   | 3. 10. 4 CAN 通信    |           |

|   | 3.10.5 以太网通信 MAC   |           |

|   | 3.11 逻辑控制          |           |

| 4 | 电气特性               |           |

|   | 4.1 引脚电气特性         |           |

|   | 4.2 供电电路           |           |

|   | 4.3 复位电路           |           |

|   | 4.4 晶振电路           | .14       |

| 5 | 物理尺寸               | 16        |

| 6 | 资料版本说明             | .17       |

|   |                    |           |

#### 1 简介

#### 1.1 概述

CMC693PR144-L 是将组态处理、程序存储、信号输入输出、控制算法、通讯接口等全部集成在一个芯片中的产品,实现的主要功能可以简述为:片内逻辑控制,程序处理及调度管理,数字量信号处理,多种数据接口通信。使用芯片的组态软件进行逻辑控制程序的编程,将编写的程序下载到芯片的片内存储器中。根据用户的程序,对输入的各种信号(包括从通信接口传入的信号)进行处理运算,并进行相应的信号输出。

逻辑控制主要包括对上层用户编写并经过编译的逻辑控制程序(如梯形图、IL、ST等)进行执行处理。数字量处理主要包括开关信号、频率信号处理,脉冲信号输入输出,PWM输出,正交编码器输入等。

芯片集成了 Flash、SRAM、通用定时器、PLL 等功能,以及以太网 MAC、UART、CAN、SPI、I2C 等多种通信接口。

#### 1.2 典型特性

芯片典型特性信息见下表 1-1 典型特性:

| 参数项            |                       | 特性值         |  |  |

|----------------|-----------------------|-------------|--|--|

| CPU 主频         | 10~400Mhz(典型值 200Mhz) |             |  |  |

| 数据位宽           | 32bit                 |             |  |  |

| 片内 SRAM        | 256 KBytes            |             |  |  |

| 片内 Flash       | 2MBytes               |             |  |  |

| 定时器            | 4 个                   |             |  |  |

|                | UART                  | 2           |  |  |

|                | CAN                   | 2           |  |  |

| 通信接口           | SPI                   | 2(1主1从)     |  |  |

|                | I2C                   | 1           |  |  |

|                | 以太网 (MAC)             | 2           |  |  |

| GPIO □         | 84 个 (可复用)            | 84个(可复用)    |  |  |

| I/O 口输出高电平驱动能力 | 9.8~35mA/3.3V         |             |  |  |

| 工作电压           | IO 供电电压               | 3.3V (±10%) |  |  |

| 工作电压           | 内核供电电压                | 1.2V (±10%) |  |  |

| 工作温度           | -40~85℃               |             |  |  |

| 外部时钟信号输入       | 有源晶振,2~15MHz          |             |  |  |

| 片内系统时钟         | 可通过 PLL 配置            |             |  |  |

| 封装形式           | LQFP 144              |             |  |  |

| 芯片尺寸           | 20×20×1.4mm           |             |  |  |

表 1-1 典型特性

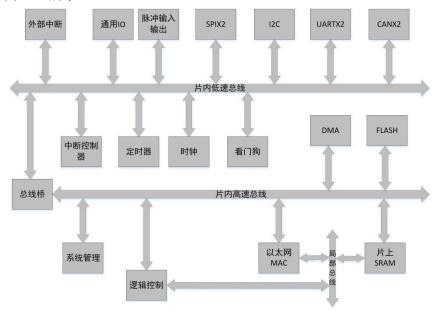

#### 1.3 芯片结构图

芯片由内部总线和功能模块组成。内部总线包括片内高速总线和片内低速总线,功能模块包括公共资源、控制运算、通信接口和数字量处理几大部分,其中公共资源包括中断控制、外部中断、定时器、实时钟、看门狗、DMA 控制器等,控制运算包括系统管理、逻

辑控制,数字量处理包括脉冲输入输出和通用 IO 等,通信接口包括 SPI、I2C、CAN、UART、以太网 MAC 等,各功能模块根据各自的性能和带宽需求,分别挂接在相应的总线上。芯片系统结构如图 1-1 所示。

图 1-1 芯片系统结构图

## 2 管脚信息

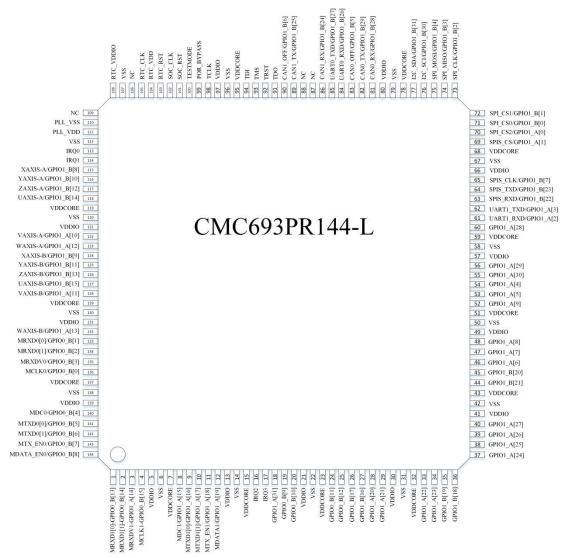

## 2.1 管脚分布

芯片共有 144 个管脚, 1 号管脚位于芯片下方最左侧,管脚按逆时针方向依次排序。管脚分布详见下图 2-1。

图 2-1 芯片管脚分布图

#### 2.2 管脚总表

| 衣 2-1 心力官脚总衣 |      |                        |                      |  |  |  |

|--------------|------|------------------------|----------------------|--|--|--|

| 管脚号          | 类型   | 管脚名称                   | 默认复用功能               |  |  |  |

| 1            | I/O  | GPIO0_B[13] / MRXD1[0] | MAC1数据接收0            |  |  |  |

| 2            | I/O  | GPIO0_B[14] / MRXD1[1] | MAC1数据接收1            |  |  |  |

| 3            | I/O  | GPIO1_A[14] / MRXDV1   | MAC1数据接收使能           |  |  |  |

| 4            | I/O  | GPIO0_B[15] / MCLK1    | MAC1 RMII 时钟输入       |  |  |  |

| 5            | VCC0 | VDDIO                  | IO 电源 <sup>[2]</sup> |  |  |  |

| 6            | GND  | VSS                    | 地[3]                 |  |  |  |

| 7            | VCC1 | VDDCORE                | 内核电源[1]              |  |  |  |

| 8            | I/O  | GPIO1_A[15] / MDC1     | MAC1数据管理时钟           |  |  |  |

| 9            | I/O  | GPIO1_A[16] / MTXD1[0] | MAC1数据发送0            |  |  |  |

| 10           | I/O  | GPIO1_A[17] / MTXD1[1] | MAC1数据发送1            |  |  |  |

| 11           | I/O  | GPIO1_A[18] / MTXEN1   | MAC1数据发送使能           |  |  |  |

表 2-1 芯片管脚总表

| 管脚号      | 类型          | 管脚名称                    | 默认复用功能       |

|----------|-------------|-------------------------|--------------|

| 12       | I/O         | GPIO1_A[19] / MDATA1    | MAC1管理数据     |

| 13       | VCC0        | VDDIO                   | IO 电源        |

| 14       | GND         | VSS                     | 地            |

| 15       | VCC1        | VDDCORE                 | 内核电源         |

| 16       | I/O         | GPIO0_A[2] / IRQ2       | 外部中断2        |

| 17       | I/O         | GPIO0_A[3] / IRQ3       | 外部中断3        |

| 18       | I/O         | GPIO1_A[31]             | GPIO         |

| 19       | I/O         | GPIO0_B[9]              | GPIO         |

| 20       | I/O         | GPIO0_B[10]             | GPIO         |

| 21       | VCC0        | VDDIO                   | IO 电源        |

| 22       | GND         | VSS                     | 地            |

| 23       | VCC1        | VDDCORE                 | 内核电源         |

| 24       | I/O         | GPIO0_B[11]             | GPIO         |

| 25<br>26 | I/O<br>I/O  | GPIO0_B[12]             | GPIO<br>GPIO |

| 27       | I/O         | GPIO1_B[17] GPIO1_B[16] | GPIO         |

| 28       | I/O         | GPIO1_A[20]             | GPIO         |

| 29       | I/O         | GPIO1_A[21]             | GPIO         |

| 30       | VCC0        | VDDIO                   | IO 电源        |

| 31       | GND         | VSS                     | 地            |

| 32       | VCC1        | VDDCORE                 | 内核电源         |

| 33       | I/O         | GPIO1_A[22]             | GPIO         |

| 34       | I/O         | GPIO1_A[23]             | GPIO         |

| 35       | I/O         | GPIO1_B[19]             | GPIO         |

| 36       | I/O         | GPIO1_B[18]             | GPIO         |

| 37       | I/O         | GPIO1_A[24]             | GPIO         |

| 38       | I/O         | GPIO1_A[25]             | GPIO         |

| 39       | I/O         | GPIO1_A[26]             | GPIO         |

| 40       | I/O         | GPIO1_A[27]             | GPIO         |

| 41       | VCC0        | VDDIO                   | IO 电源        |

| 42       | GND         | VSS                     | 地            |

| 43       | VCC1<br>I/O | VDDCORE                 | 内核电源<br>GPIO |

| 45       | I/O         | GPIO1_B[21]             | GPIO         |

| 46       | I/O         | GPIO1_B[20] GPIO1_A[6]  | GPIO         |

| 47       | I/O         | GPIO1_A[0]  GPIO1 A[7]  | GPIO         |

| 48       | I/O         | GPIO1_A[8]              | GPIO         |

| 49       | VCC0        | VDDIO                   | IO 电源        |

| 50       | GND         | VSS                     | 地            |

| 51       | VCC1        | VDDCORE                 | 内核电源         |

| 52       | I/O         | GPIO1_A[9]              | GPIO         |

| 53       | I/O         | GPIO1_A[5]              | GPIO         |

| 54       | I/O         | GPIO1_A[4]              | GPIO         |

| 55       | I/O         | GPIO1_A[30]             | GPIO         |

| 56       | I/O         | GPIO1_A[29]             | GPIO         |

| 57       | VCC0        | VDDIO                   | IO 电源        |

| 管脚号 | 类型   | 管脚名称                    | 默认复用功能                   |

|-----|------|-------------------------|--------------------------|

| 58  | GND  | VSS                     | 地                        |

| 59  | VCC1 | VDDCORE                 | 内核电源                     |

| 60  | I/O  | GPIO1_A[28]             | GPIO                     |

| 61  | I/O  | GPIO1_A[2] / UART1_ RXD | UARTI数据输入                |

| 62  | I/O  | GPIO1_A[3] / UART1_ TXD | UARTI数据输出                |

| 63  | I/O  | GPIO1_B[22] / SPIS_RXD  | SPI 从接口数据输入              |

| 64  | I/O  | GPIO1_B[23] / SPIS_TXD  | SPI 从接口数据输出              |

| 65  | I/O  | GPIO1_B[7] / SPIS_SCLK  | SPI 从接口串行时钟              |

| 66  | VCC0 | VDDIO                   | IO 电源                    |

| 67  | GND  | VSS                     | 地                        |

| 68  | VCC1 | VDDCORE                 | 内核电源                     |

| 69  | I/O  | GPIO1_A[1] / SPIS_CS    | SPI 从接口串行时钟              |

| 70  | I/O  | GPIO1_A[0] / SPI_ CS2   | SPI 主接口芯片选择2             |

| 71  | I/O  | GPIO1_B[0] / SPI_ CS0   | SPI 主接口芯片选择0             |

| 72  | I/O  | GPIO1_B[1] / SPI_ CS1   | SPI 主接口芯片选择1             |

| 73  | I/O  | GPIO1_B[2] / SPI_ SCLK  | SPI 主接口串行时钟              |

| 74  | I/O  | GPIO1_B[3] / SPI_ MISO  | SPI 主接口数据输入              |

| 75  | I/O  | GPIO1_B[4] / SPI_ MOSI  | SPI 主接口数据输出              |

| 76  | I/O  | GPIO1_B[30] / I2C_SCL   | I2C 时钟线                  |

| 77  | I/O  | GPIO1_B[31] / I2C_SDA   | I2C 数据线                  |

| 78  | VCC1 | VDDCORE                 | 内核电源                     |

| 79  | GND  | VSS                     | 地                        |

| 80  | VCC0 | VDDIO                   | IO 电源                    |

| 81  | I/O  | GPIO1_B[28] / CAN0_RX   | CAN0数据输入                 |

| 82  | I/O  | GPIO1_B[29] / CAN0_TX   | CAN0数据输出                 |

| 83  | I/O  | GPIO1_B[5] / CAN0_OFF   | CAN0节点退出总线状态             |

| 84  | I/O  | GPIO1_B[26] / UART0_RXD | UART0数据输入                |

| 85  | I/O  | GPIO1_B[27] / UART0_TXD | UART0数据输出                |

| 86  | I/O  | GPIO1_B[24] / CAN1_RX   | CAN1数据输入                 |

| 87  | NC   | /                       | /                        |

| 88  | NC   | /                       | /                        |

| 89  | I/O  | GPIO1_B[25] / CAN1_TX   | CAN1数据输出                 |

| 90  | I/O  | GPIO1_B[6] / CAN1_OFF   | CAN1节点退出总线状态             |

| 91  | 0    | TDO                     | JTAG 数据输出                |

| 92  | I    | TRST                    | JTAG 复位信号                |

| 93  | I    | TMS                     | JTAG 测试模式选择              |

| 94  | I    | TDI                     | JTAG 数据输入                |

| 95  | VCC1 | VDDCORE                 | 内核电源                     |

| 96  | GND  | VSS                     | 地                        |

| 97  | VCC0 | VDDIO                   | IO电源                     |

| 98  | I    | TCLK                    | JTAG 时钟<br>复位屏蔽,需1K 下拉接地 |

| 99  | I    | POR_BYPASS              |                          |

| 100 | I    | TESTMODE SOC BET D      | 需1K 下拉接地<br>芯片复位         |

| 101 | I    | SOC_RST_B               |                          |

| 102 | I    | OSCCLK                  | 芯片时钟输入                   |

| 管脚号 | 类型   | 管脚名称                   | 默认复用功能                   |

|-----|------|------------------------|--------------------------|

| 103 | I    | RTCRST                 | RTC 复位,本芯片暂不支持,NC 即可     |

| 104 | VCC1 | RTC_VDDCORE            | RTC 内核电源[1]              |

| 105 | I    | RTCCLK                 | RTC 时钟输入,本芯片暂不支持,NC 即可   |

| 106 | NC   | /                      | /                        |

| 107 | GND  | VSS                    | RTC 电源地 <sup>[3]</sup>   |

| 108 | VCC0 | RTC_VDDIO              | RTC_IO 电源 <sup>[2]</sup> |

| 109 | NC   | /                      | /                        |

| 110 | GND  | PLL_VSSIO              | PLL 电源地 <sup>[3]</sup>   |

| 111 | VCC0 | PLL_VDDCORE            | PLL 内核电源[1]              |

| 112 | GND  | VSS                    | 地                        |

| 113 | I/O  | GPIO0_A[0] / IRQ0      | 外部中断0                    |

| 114 | I/O  | GPIO0_A[1] / IRQ1      | 外部中断1                    |

| 115 | I/O  | GPIO1_B[8] / a-X-AXIS  | X轴A路脉冲输入或X轴PWMA输出        |

| 116 | I/O  | GPIO1_B[10] / a-Y-AXIS | Y轴A路脉冲输入或Y轴PWMA输出        |

| 117 | I/O  | GPIO1_B[12] / a-Z-AXIS | Z轴A路脉冲输入或Z轴PWMA输出        |

| 118 | I/O  | GPIO1_B[14] / a-U-AXIS | U轴A路脉冲输入或U轴PWMA输出        |

| 119 | VCC1 | VDDCORE                | 内核电源                     |

| 120 | GND  | VSS                    | 地                        |

| 121 | VCC0 | VDDIO                  | IO 电源                    |

| 122 | I/O  | GPIO1_A[10] / a-V-AXIS | V轴A路脉冲输入或V轴PWMA输出        |

| 123 | I/O  | GPIO1_A[12] / a-W-AXIS | W轴A路脉冲输入或W轴PWMA输出        |

| 124 | I/O  | GPIO1_B[9] / b-X-AXIS  | X轴B路脉冲输入或X轴PWMB输出        |

| 125 | I/O  | GPIO1_B[11] / b-Y-AXIS | Y轴B路脉冲输入或Y轴PWMB输出        |

| 126 | I/O  | GPIO1_B[13] / b-Z-AXIS | Z轴B路脉冲输入或Z轴PWMB输出        |

| 127 | I/O  | GPIO1_B[15] / b-U-AXIS | U轴B路脉冲输入或U轴PWMB输出        |

| 128 | I/O  | GPIO1_A[11] / b-V-AXIS | V轴B路脉冲输入或V轴PWMB输出        |

| 129 | VCC1 | VDDCORE                | 内核电源                     |

| 130 | GND  | VSS                    | 地                        |

| 131 | VCC0 | VDDIO                  | IO 电源                    |

| 132 | I/O  | GPIO1_A[13] / b-W-AXIS | W轴B路脉冲输入或W轴PWMB输出        |

| 133 | I/O  | GPIO0_B[1] / MRXD0[0]  | MAC0数据接收0                |

| 134 | I/O  | GPIO0_B[2] / MRXD0[1]  | MAC0数据接收1                |

| 135 | I/O  | GPIO0_B[3] / MRXDV0    | MAC0数据接收使能               |

| 136 | I/O  | GPIO0_B[0] / MCLK0     | MAC0 RMII 时钟输入           |

| 137 | VCC1 | VDDCORE                | 内核电源                     |

| 138 | GND  | VSS                    | 地                        |

| 139 | VCC0 | VDDIO                  | IO 电源                    |

| 140 | I/O  | GPIO0_B[4] / MDC0      | MAC0数据管理时钟               |

| 141 | I/O  | GPIO0_B[5] / MTXD0[0]  | MAC0数据发送0                |

| 142 | I/O  | GPIO0_B[6] / MTXD0[1]  | MAC0数据发送1                |

| 143 | I/O  | GPIO0_B[7] / MTXEN0    | MAC0数据发送使能               |

| 144 | I/O  | GPIO0_B[8] / MDATA0    | MAC0管理数据                 |

注释:【1】RTC 内核电源、PLL 内核电源和芯片内核电源可共用一个 VDDCORE。

【2】RTC\_IO 电源和芯片 IO 电源可共用一个 VDDIO。

【3】RTC 电源地、PLL 电源地、内核电源地和 IO 电源地可共用一个 VSS。

#### 3 功能描述

#### 3.1 系统时钟

芯片具有一个外部高速时钟(2~15MHz)输入接口,推荐典型值为10MHz,需使用有源晶振。

芯片内的 PLL 模块可将系统输入时钟进行倍频。PLL 上电后默认为 bypass 模式,即外部时钟直接输入模式。上电后,PLL 复位时间至少需要 5us,稳定时间需要 100us。系统时钟输入管脚如下表 3-1 所示:

| - 1 31-50-1 1 Hay 4 H W.L. |    |                                |  |  |

|----------------------------|----|--------------------------------|--|--|

| 管脚名称                       | 类型 | 说明                             |  |  |

| OSCCLK                     | I  | OSC 时钟输入,范围为2~15MHz,经 PLL 倍频后系 |  |  |

|                            |    | 统时钟频率为10~400MHz                |  |  |

表 3-1 系统时钟输入管脚

#### 3.2 工作模式

芯片有4种工作模式,分别为运行模式、等待模式、休眠模式和停止模式。

运行模式,即系统复位之后进入的默认模式。当所有的外设都开启时,系统的功耗达到最高。如果此时有外设处于空闲状态,可以通过软件关闭该外设的时钟信号,从而节省一部分功耗。

等待模式,即芯片的小部分外设停止工作;休眠模式,即芯片的大部分外设停止工作。 系统的唤醒方式有多种可选,如复位、外部中断和内部唤醒计数器等。

停止模式,即几乎所有的模块都进入了睡眠,只有一些用于唤醒功能的模块还处于工作状态。该模式下的系统功耗最低。系统可以通过复位、外部中断或者内部唤醒计数器这些方式之一从停止模式中恢复。

4种模式下,芯片的各内部模块的时钟状态详见下表 3-2:

| 模块名称               | 运行模式 | 等待模式 | 休眠模式 | 停止模式 |

|--------------------|------|------|------|------|

| 管理单元               | √    | ×    | ×    | ×    |

| 总线/时钟/复位管理         | √    | √    | √    | ×    |

| FLASH 控制器/SRAM 控制器 | √    | ✓    | √    | ×    |

| 中断控制               | √    | √    | √    | ×    |

| 逻辑控制               | M1   | M1   | M1   | ×    |

| 以太网 MAC0/MAC1      | M1   | M1   | M1   | ×    |

| DMA 控制器            | M1   | M1   | M1   | ×    |

| CAN0/CAN1          | M1   | M1   | M1   | ×    |

| 脉冲输入输出 PIPO        | M1   | M1   | M1   | ×    |

| I2C                | M1   | M1   | M1   | ×    |

| SPI                | M1   | M1   | M1   | ×    |

| UART0/UART1        | M1   | M1   | M1   | ×    |

表 3-2 各模式下的模块状态

| 模块名称      | 运行模式 | 等待模式 | 休眠模式 | 停止模式 |

|-----------|------|------|------|------|

| EINT/GPIO | M1   | M2   | M2   | M2   |

| 定时器       | M1   | M1   | M1   | ×    |

| 看门狗       | M1   | M1   | M1   | ×    |

注释: ✓:正常操作

× : 没有时钟驱动

M1: 可自由配置成有时钟/没有时钟

M2: 总线内部时钟关闭, 但是外部时钟仍工作

#### 3.3 芯片复位

系统支持 5 种复位方式,分别为上电复位、软件复位、看门狗复位、外部复位和 JTAG 复位。复位管理特性详见下表 3-3:

参数

描述

复位信号时间

至少保持 60us

上电复位

系统级复位

看门狗复位

系统级复位

外部复位

模块级复位

软件复位

模块级复位

测试模式复位

JTAG 复位

表 3-3 复位管理特性

#### 3.4 看门狗 WDT

看门狗从设定好的初始值开始,在每个工作时钟的上升沿进行减 1 操作,在计数值递减为 0 的时候产生一个复位中断信号。看门狗需要周期性的进行喂狗操作,如果在设定时间内没有喂狗,看门狗会因为超时而产生复位信号,该复位信号为系统复位信号。看门狗特性详见下表 3-4:

| 参数     | 描述                            |  |  |

|--------|-------------------------------|--|--|

| 工作时钟   | 片内低速总线时钟                      |  |  |

| 计数宽度   | 32bits                        |  |  |

| 超时中断   | 可配置为一次超时后直接复位系统或两次超时后复<br>位系统 |  |  |

| 中断清除方式 | 2种,读清中断寄存器或重启计数器              |  |  |

表 3-4 看门狗特性

#### 3.5 片内 FLASH

芯片片内自带 2M 容量的 FLASH, FLASH 特性详见下表 3-5:

表 3-5 片内 FLASH 特性

| 参数   | 描述                |

|------|-------------------|

| 总容量  | 2M bytes          |

| 扇区数量 | 128 个             |

| 扇区分页 | 16 页              |

| 扇区大小 | 4K bytes,可进行半页和扇区 |

|      | 擦除和编程操作           |

| 每页大小   | 256 bytes         |

|--------|-------------------|

| 数据输入位宽 | 8 bits            |

| 数据输出位宽 | 8/16/32 bits      |

| 页模式时间  | 擦除时间 3ms,编程时间 2ms |

| 扇区模式时间 | 擦除时间 3.3ms,编程时间   |

|        | 2.3ms             |

| 标准静态电流 | 2uA               |

| 读频率    | 16MHz             |

| 擦除次数   | 大于 100,000 次      |

| 数据存储时间 | 大于 20 年           |

#### 3.6 通用定时器

芯片共有 4 个完全相同的,但分别独立编程的定时器。定时器在设定了预定值后,开始进行自减操作,直到减至 0,则停止减数操作并发出中断信号。定时器特性详见下表 3-6:

| 参数        | 描述                 |  |  |

|-----------|--------------------|--|--|

| 独立的可编程定时器 | 4 个                |  |  |

| 计数宽度      | 32bits             |  |  |

| 时钟信号      | 4个,各定时器间相互独立       |  |  |

| 读写寄存器     | 4组,各定时器间相互独立       |  |  |

| 定时器触发输出   | 可配置,装载计数值时一次,触发时一次 |  |  |

表 3-6 通用定时器特性

#### 3. 7 JTAG

芯片的 JTAG 功能专门用于芯片的 JTAG 测试工作,有专用的 JTAG 管脚,详见下表 3-7: 表 3-7 JTAG 管脚

| 管脚名称 | 属性 | 管脚号 | 说明          |

|------|----|-----|-------------|

| TCLK | I  | 98  | JTAG 时钟     |

| TDI  | I  | 94  | JTAG 数据输入   |

| TMS  | I  | 93  | JTAG 测试模式选择 |

| TRST | I  | 92  | JTAG 复位信号   |

| TDO  | О  | 91  | JTAG 数据输出   |

#### 3.8 通用输入输出 GPIO

芯片的通用输入输出端口 GPIO,采用 CMOS 三态输入/输出设计,上电默认状态为浮空输入状态,用户可以根据需求配置成输入、输出 (0/1)或者高阻状态。芯片共有 84 个 GPIO口,部分 GPIO 口具有默认复用功能,可参考表 2-1。GPIO 特性详见下表 3-8:

表 3-8 通用输入输出特性

| 参数      | 描述                  |

|---------|---------------------|

| 端口状态    | 可配置为输入/输出/高阻        |

| 数据寄存器   | 每个端口可独立配置           |

| 数据方向寄存器 | 每个端口可独立配置           |

| 外部中断源输入 | 可配置成高电平有效、低电平有效、上升沿 |

|         | 触发和下降沿触发 4 种中断方式。   |

#### 3.9 脉冲输入输出 PIPO

芯片的脉冲输入输出功能复用了部分 GPIO 管脚,芯片可通过该功能来测量输入脉冲信号的长度、频率和个数,或者产生输出波形 (PWM,嵌入死区时间的互补 PWM)。管脚详情见下表 3-9:

| 管脚名称     | 类型  | 管脚号 | 说明                  |

|----------|-----|-----|---------------------|

| a-X-AXIS | I/O | 115 | X轴A路脉冲输入口或X轴PWMA输出口 |

| b-X-AXIS | I/O | 124 | X轴B路脉冲输入口或X轴PWMB输出口 |

| a-Y-AXIS | I/O | 116 | Y轴A路脉冲输入口或Y轴PWMA输出口 |

| b-Y-AXIS | I/O | 125 | Y轴B路脉冲输入口或Y轴PWMB输出口 |

| a-Z-AXIS | I/O | 117 | Z轴A路脉冲输入口或Z轴PWMA输出口 |

| b-Z-AXIS | I/O | 126 | Z轴B路脉冲输入口或Z轴PWMB输出口 |

| a-U-AXIS | I/O | 118 | U轴A路脉冲输入口或U轴PWMA输出口 |

| b-U-AXIS | I/O | 127 | U轴B路脉冲输入口或U轴PWMB输出口 |

| a-V-AXIS | I/O | 122 | V轴A路脉冲输入口或V轴PWMA输出口 |

| b-V-AXIS | I/O | 128 | V轴B路脉冲输入口或V轴PWMB输出口 |

| a-W-AXIS | I/O | 123 | W轴A路脉冲输入口或W轴PWMA输出口 |

| b-W-AXIS | I/O | 132 | W轴B路脉冲输入口或W轴PWMB输出口 |

表 3-9 脉冲输入输出管脚

PIPO 功能主要由 4 个 16 位自动装载高级计数器构成。计数器主要特性详见下表 3-10: 表 3-10 脉冲输入输出/计数器特性

| 参数             | 描述                       |

|----------------|--------------------------|

| 向上自动装载计数器宽度    | 32bits                   |

| 向下自动装载计数器宽度    | 32bits                   |

| 向上/向下自动装载计数器宽度 | 32bits                   |

| 可编程预分频器宽度      | 32bits, 计数器时钟频率的分频系数为 1~ |

|                | 65535 之间的任意数             |

| 更新计数值          | 允许                       |

| 工作模式           | 基本定时模式                   |

|                | 输入捕获(测量输入信号的脉冲宽度)        |

|                | 输入测量(测量输入信号的脉冲个数)        |

|                | PWM 生成(边缘或中间对齐模式)        |

|                | 单脉冲模式输出                  |

|                | 正交编码器接口模式                |

### 3.10 通信接口

#### 3.10.1 UART 串行通信

芯片带有 2 个串口, UARTO 和 UART1, 对应管脚描述详见下表 3-11:

表 3-11 串口通信管脚

| 管脚名称      | 类型 | 管脚号 | 说明      |

|-----------|----|-----|---------|

| UART0_RXD | I  | 84  | UART0输入 |

| UART0_TXD | О  | 85  | UART0输出 |

| UART1_RXD | I  | 61  | UART1输入 |

| UART1_TXD | О  | 62  | UART1输出 |

串口通信支持 16C550 工业标准,可支持最快通信速率为 384Kbps,推荐的典型波特率可选择 9600bps、19200bps、38400bps 或 115200bps。通信特性见下表 3-12:

表 3-12 串行通信特性

| 参数       | 描述              |

|----------|-----------------|

| 波特率      | 可编程,波特率 = 串行时钟频 |

|          | 率 / (16* 分频系数)  |

| 全双工      | 支持              |

| DMA 握手接口 | 有               |

#### 3.10.2 I2C 通信

芯片有 1 路硬件 I2C 接口,管脚描述见下表 3-13:

表 3-13 I2C 管脚

| 管脚名称    | 类型  | 管脚号 | 说明      |

|---------|-----|-----|---------|

| I2C_SCL | I/O | 76  | I2C 时钟线 |

| I2C_SDA | I/O | 77  | I2C 数据线 |

I2C 通信支持标准的 I2C 总线接口协议,接口支持主机模式和从机模式,典型通信速度为 100Kbps 或 400Kbps, 通信特性详见下表 3-14:

表 3-14 I2C 通信特性

| 参数       | 描述                                |

|----------|-----------------------------------|

| 主机模式     | 支持                                |

| 从机模式     | 支持                                |

| 串行接口     | 2线                                |

| 通信速度     | 100 Kbps (标准模式) 和 400 Kbps (快速模式) |

| 时钟同步     | 支持                                |

| 多主模式     | 支持                                |

| DMA 握手接口 | 有                                 |

#### 3.10.3 SPI 通信

芯片有两路 SPI 通信接口,管脚描述详见下表 3-15:

表 3-15 SPI 通信管脚

| 管脚名称      | 类型 | 管脚号 | 说明                  |

|-----------|----|-----|---------------------|

| SPI_CS0   | О  | 71  | SPI 主接口芯片选择0, 低电平有效 |

| SPI_ CS1  | О  | 72  | SPI 主接口芯片选择1, 低电平有效 |

| SPI_CS2   | О  | 70  | SPI 主接口芯片选择2, 低电平有效 |

| SPI_ SCLK | О  | 73  | SPI 主接口串行时钟         |

| SPI_MISO  | I  | 74  | SPI 主接口数据输入         |

| SPI_ MOSI | О  | 75  | SPI 主接口数据输出         |

| SPIS_RXD  | I  | 63  | SPI 从接口数据输入         |

| SPIS_TXD  | О  | 64  | SPI 从接口数据输出         |

| SPIS_SCLK | I  | 65  | SPI 从接口串行时钟         |

| SPIS_CS   | О  | 69  | SPI 从接口芯片选择,低电平有效   |

SPI 通信遵循串行外设接口规范。芯片的两路通信接口,一路支持主机模式,具有三个片选信号,最高传输速率为 12.5Mbps。另一路接口支持从机模式,具有一个片选信号,最高传输速率为 12.5Mbps。通信特性详见下表 3-16:

表 3-16 SPI 通信特性

| 参数        | 描述                 |

|-----------|--------------------|

| 内部接收 FIFO | 宽度为 16, 深度为 34     |

| 内部发送 FIFO | 宽度为 16, 深度为 34     |

| 主机模式      | 支持                 |

| 从机模式      | 支持                 |

| 片选线       | 主机模式 3 路, 从机模式 1 路 |

| DMA 握手接口  | 有                  |

#### 3.10.4 CAN 通信

芯片有 2 路 CAN 通信接口,管脚描述详见下表 3-17:

表 3-17 CAN 管脚

| 管脚名称     | 类型 | 管脚号 | 说明       |

|----------|----|-----|----------|

| CANO_TX  | 0  | 82  | CANO 输出  |

| CANO_RX  | I  | 81  | CANO 输入  |

| CANO_OFF | 0  | 83  | 节点退出总线状态 |

| CAN1_TX  | 0  | 89  | CAN1 输出  |

| CAN1_RX  | I  | 86  | CAN1 输入  |

| CAN1_OFF | 0  | 90  | 节点退出总线状态 |

CAN 通信遵循 ISO11898 规范,支持 CAN2. OB 通信协议的标准帧和数据帧传输,最高传输速率为 1Mbps,通信特性详见下表 3-18:

表 3-18 CAN 通信特性

| 参数         | 描述                                        |

|------------|-------------------------------------------|

| 规范         | ISO11898                                  |

| 通信协议       | CAN2.0B                                   |

| 数据链路层传输位速率 | 10Kbps/20Kbps/50Kbps/125Kbps/250Kbps/500K |

|            | bps/800Kbps/1Mbps                         |

| 应用层协议传输速率  | 多种速率,最大 1Mbps                             |

| FIFO 模块    | 64Bytes                                   |

#### 3.10.5 以太网通信 MAC

芯片具有两个以太网 MAC 通信接口,MACO 和 MAC1,管脚遵从 IEEE 802.3-2008 标准,最高传输速率为 100 Mbps。管脚描述详见下表 3-19:

表 3-19 MACO 管脚

| 管脚名称     | 类型 | 管脚号 | 说明                    |

|----------|----|-----|-----------------------|

| MRXD0[0] | I  | 133 | MAC0数据接收              |

| MRXD0[1] | I  | 134 | MAC0数据接收              |

| MRXDV0   | I  | 135 | MAC0数据接收使能            |

| MCLK0    | I  | 136 | MAC0 RMII 时钟输入,50M    |

| MDC0     | О  | 140 | MAC0数据管理时钟,1.0~2.5MHz |

| MTXD0[0] | О  | 141 | MAC0数据发送              |

| 管脚名称     | 类型 | 管脚号 | 说明                     |

|----------|----|-----|------------------------|

| MTXD0[1] | О  | 142 | MAC0数据发送               |

| MTXEN0   | О  | 143 | MAC0数据发送使能             |

| MDATA0   | IO | 144 | MAC0管理数据               |

| MRXD1[0] | I  | 1   | MAC1数据接收               |

| MRXD1[1] | I  | 2   | MAC1数据接收               |

| MRXDV1   | I  | 3   | MAC1数据接收使能             |

| MCLK1    | I  | 4   | MAC1 RMII 时钟输入,50M     |

| MDC1     | О  | 8   | MAC1数据管理时钟, 1.0~2.5MHz |

| MTXD1[0] | О  | 9   | MAC1数据发送               |

| MTXD1[1] | О  | 10  | MAC1数据发送               |

| MTXEN1   | О  | 11  | MAC1数据发送使能             |

| MDATA1   | IO | 12  | MAC1管理数据               |

## 3.11 逻辑控制

逻辑控制主要实现对基于 IEC61131-3 的逻辑控制任务的调度和逻辑控制程序(如 LD、IL、ST 等)的执行处理。逻辑控制特性详见下表 3-20:

| 农 5 20 及科证的存在 |                                     |  |  |

|---------------|-------------------------------------|--|--|

| 参数            | 描述                                  |  |  |

| 指令执行速度        | 0.8us (35M 主频)                      |  |  |

| 数据类型          | 布尔型,整型,单精度浮点型                       |  |  |

| 数据宽度          | 1/8/16/32bits                       |  |  |

| 内部指令缓存        | 1KBytes                             |  |  |

| 支持语言          | LD 梯形图, IL 语言, ST 语言, FBD 功能块图, SFC |  |  |

|               | 顺序功能图                               |  |  |

| 实时监控          | 状态值,错误类型                            |  |  |

表 3-20 逻辑控制特性

## 4 电气特性

## 4.1 引脚电气特性

芯片的管脚典型特性如下表 4-1 所示:

表 4-1 芯片管脚电气特性 (-40~85℃)

| 参数项     | 描述               | 参数值(参考地 VSS) |      | VSS)       |

|---------|------------------|--------------|------|------------|

|         |                  | 最小值          | 典型值  | 最大值        |

| VDDIO   | I/O 供电           | 2.97V        | 3.3V | 3.63V      |

| VDDCORE | 内核供电             | 1.08V        | 1.2V | 1.32V      |

| Vih     | 输入高电平            | 2.0V         |      | VDDIO+0.3V |

| Vil     | 输入低电平            | -0.3V        |      | 0.8V       |

| Voh     | 输出高电平            | 2.4V         |      |            |

| VoL     | 输出低电平            |              |      | 0.4V       |

| Ioh     | 高电平输出电流@Voh=2.4V | 9.8mA        |      | 35.1mA     |

| IoL     | 低电平输出电流          | 8.4mA        |      | 16.3mA     |

| IL      | 输入漏电流            |              |      | ±1uA       |

| Ioz     | 三态输出漏电流          |              |      | ±1uA       |

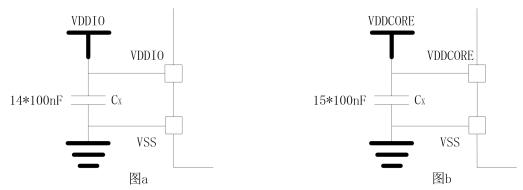

#### 4.2 供电电路

芯片需采用 1.2V 和 3.3V 两种外部电源供电。VDDCORE 采用 1.2V 电源为芯片的内核供电; VDDIO 采用 3.3V 电源为芯片的 I/O 供电。推荐每个电源引脚旁至少放置一颗 100nF 退偶电容,并在电路板上将此电容尽量靠近引脚放置。如下图 4-1 中图 a 部分所示为 VDDIO电源,图 b 部分所示为 VDDCORE 部分电源。

图 4-1 引脚电源

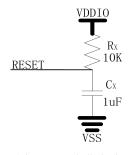

#### 4.3 复位电路

芯片复位功能低电平有效,可采用典型的 RC 复位电路,推荐的典型值为 10K 电阻搭配 1uF 电容,保证复位时间不少于 10mS,可根据实际外围电路适当延长复位时间,也可以根据实际需要选择其他复位电路。RTC 复位电路也可参考此电路设计。典型 RC 复位电路如下图所示:

图 4-2 RC 复位电路

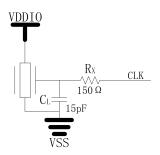

#### 4.4 晶振电路

芯片的系统时钟可选择  $2\sim15 MHz$ ,典型推荐值为 10 MHz,需使用有源晶振。典型推荐电路如下图所示。其中 CL 推荐典型值 15 pF,用户需根据实际使用的晶振参数做相应调整,时钟信号线上可选择串接  $50\sim300 \Omega$ 左右阻值的电阻,能够有效抑制时钟信号的过冲现象,此电阻值需用户根据实际的时钟信号做适当的调整。在电路板上需将 CL 电容尽量靠近晶振的引脚放置。

图 4-3 晶振电路

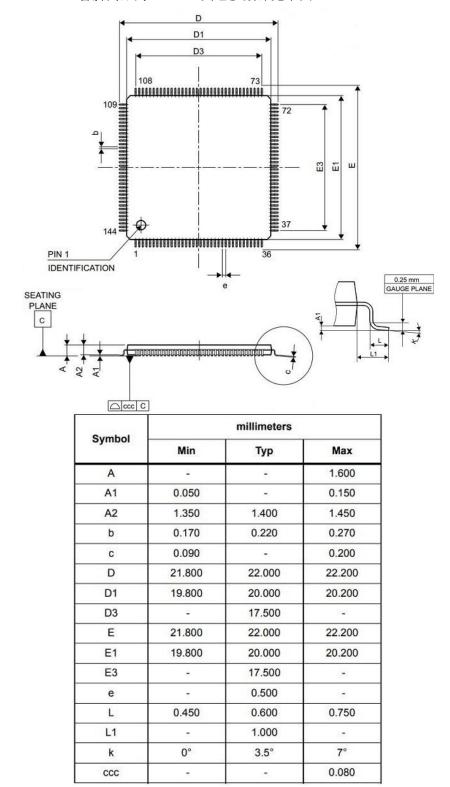

## 5 物理尺寸

芯片采用 LQFP (Low-profile Quad Flat Package) 薄型四方扁平式封装,本体尺寸为 20×20×1.4mm,管脚间距为 0.5mm,其它参数详见下图 5-1。

图 5-1 物理尺寸图

## 6 资料版本说明

表 6-1 版本升级更改一览表

| 版本号  | 起草人        | 发布日期       | 更新点 |

|------|------------|------------|-----|

| V1.0 | Lizongchun | 2022-02-23 | 第一版 |

## 宁波中控微电子有眼公司

NINGBO SUPCON MICROELECTRONICS CO., LTD.

浙江省宁波市海曙区丽园北路 1350 号众创空间 2 号楼 5 楼

WEB:www.nz-ic.com

ZIP:315000

TEL: 0574-87288895

Email:support@nz-ic.com

微信公众号:中控微电子