# 36 V, Low Power, High Precision Op Amp

#### **Features**

- Low Offset Voltage:

10 μV max (B Grade)

20 μV max (A Grade)

- Low Offset Voltage Temperature Drift:

0.5 μV/°C max (B Grade)

1.0 μV/°C max (A Grade)

- · Low Input Bias Current: 25 pA max

- Low Noise Density: 10 nV/ $\sqrt{\text{Hz}}$  (f = 1 kHz)

- Low Noise:  $0.8 \mu V_{P-P}$  (f =  $0.1 \sim 10 \text{ Hz}$ )

- Input Voltage Range Extends to Negative Power Supply

- CMRR: 120 dB min

- PSRR: 120 dB min (full temperature range)

- A<sub>VOL</sub>: 120 dB min (full temperature range)

- Supply Current: 500 μA/amplifier

- · Gain Bandwidth Product: 1.3 MHz, unit gain stable

- Single/dual Power Supply: ±2.25 V to ±18 V, 4.5 V to 36 V

- Specified Temperature Range: -40 °C to +125 °C

### **Applications**

- · Precision Data Acquisition

- Instrumentation

- Sensor Signal Conditioning

- Industrial Control

- Optical Communication

- · Smart Grid

### **General Description**

ZJA3008 series high-precision continuous operational amplifiers featuring lower than 10  $\mu V$  offset voltage, better than 0.5  $\mu V/^{\circ}C$  offset voltage drift, 25 pA input bias current and 10 nV/ $\sqrt{Hz}$  low noise. These features make them exceptionally suitable for precision signal conditioning, such as precision sensor interface, voltage amplification, current to voltage conversion and filtering.

The ZJA3008 has a low supply current of 500  $\mu$ A per channel, making them suitable for applications with strict requirements on power consumption or heat management, such as 4-20 mA loop powered instruments.

ZJA3008's input bias current is better than 25 pA, the offset voltage is better than 10  $\mu\text{V}$ , the offset voltage temperature drift is better than 0.5  $\mu\text{V}/^{\circ}\text{C}$ , and the input range extends to the negative power rail. This makes ZJA3008 very suitable for the sensor signal conditioning, whether in single-supply or dual-supply designs. ZJA3008 can also simplify the entire process of sensor conditioning modules' manufacturing.

The ZJA3008 has a wide power supply voltage range, operating from  $\pm 2.25$  V to  $\pm 18$  V for dual-supply operation or 4.5 V to 36 V for single-supply. It further expands its input capabilities to negative rail, making it ideal for a variety of applications.

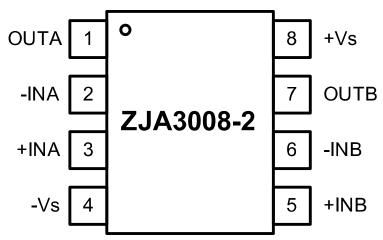

ZJA3008-2 is dual channel part and offered in a 8-lead SOIC and a 8-lead MSOP package.

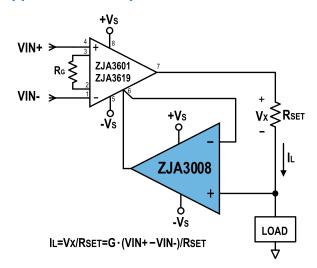

# **Application Examples**

# **Typical Performance Characteristics**

## **Table of contents**

| Features                                     | 1  |

|----------------------------------------------|----|

| Applications                                 | 1  |

| General Description                          | 1  |

| Application Examples                         | 1  |

| Table of contents                            | 2  |

| Version (Release A)                          | 3  |

| Revision History                             | 3  |

| Pin Configurations and Function Descriptions | 4  |

| Absolute Maximum Ratings                     | 5  |

| Thermal Resistance                           | 5  |

| Specifications                               | 6  |

| Typical Performance Characteristics          | 8  |

| Theory of Operation                          | 15 |

| Post-package Trimming                        | 15 |

| Applications Information                     | 16 |

|                                              |    |

| Source Impedance, Input Bias Current Affect both | Output |

|--------------------------------------------------|--------|

| Noise and System Offset Voltage                  | 16     |

| Input Common Mode Voltage Range                  | 16     |

| Output Phase Reversal                            | 16     |

| Overload Recovery Time                           | 17     |

| Over Temperature Protection                      | 17     |

| Input Bias Current Return Path                   | 18     |

| Temperature Hysteresis                           | 19     |

| Applications and Implementation                  | 21     |

| Bandpass KRC Filter                              | 21     |

| ayout Guidance                                   | 22     |

| Outline Dimensions                               | 23     |

| Ordering Guide                                   | 24     |

| Product Order Model                              | 24     |

| Related Parts                                    | 25     |

# Version (Release A) <sup>1</sup>

### **Revision History**

Dec. 2024 — Release A

Updated Pin Configurations, Ordering Guide, Product Order Model and Related Parts

Aug. 2024

Information furnished by ZJW Microelectronics is believed to be accurate and reliable. However, no responsibility is assumed by ZJW Microelectronics for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of ZJW Microelectronics. Trademarks and registered trademarks are the property of their respective owners.

# **Pin Configurations and Function Descriptions**

Figure 1. ZJA3008-2 Pin Configuration (8-lead SOIC and MSOP)

| Mnemonic | Pin No. | I/O 1 | Description                   |

|----------|---------|-------|-------------------------------|

| OUTA     | 1       | AO    | Channel A output              |

| -INA     | 2       | Al    | Channel A inverting input     |

| +INA     | 3       | Al    | Channel A non-inverting input |

| -Vs      | 4       | Р     | Negative power supply         |

| +INB     | 5       | Al    | Channel B non-inverting input |

| -INB     | 6       | Al    | Channel B inverting input     |

| OUTB     | 7       | AO    | Channel B output              |

| +Vs      | 8       | Р     | Positive power supply         |

<sup>&</sup>lt;sup>1</sup> Al: Analog Input; P: Power; AO: Analog Output.

## **Absolute Maximum Ratings** <sup>1</sup>

| Parameter                                         | Rating                                    |

|---------------------------------------------------|-------------------------------------------|

| Supply Voltage                                    | 40 V                                      |

| Input Voltage                                     | ±V <sub>SY</sub>                          |

| Input Current <sup>2</sup>                        | ±10 mA                                    |

| Differential Input Voltage                        | (+V <sub>SY</sub> ) - (-V <sub>SY</sub> ) |

| Output Short-Circuit Duration to GND <sup>3</sup> | Continuous                                |

| Operating Temperature Range                       | -40 °C to +125 °C                         |

| Storage Temperature Range                         | -65 °C to +150 °C                         |

| Junction Temperature Range                        | -65 °C to +150 °C                         |

| Maximum Reflow Temperature 4                      | 260 °C                                    |

| Lead Temperature, Soldering (10 sec)              | 300 °C                                    |

| Electrostatic Discharge (ESD) 5                   |                                           |

| Human Body Model (HBM) 6                          | 750 V                                     |

| Charged Device Model (CDM) <sup>7</sup>           | 1000 V                                    |

#### Thermal Resistance<sup>8</sup>

| Package Type | θЈА | θυς | Unit |

|--------------|-----|-----|------|

| SOIC-8       | 158 | 43  | °C/W |

| MSOP-8       | 190 | 44  | °C/W |

<sup>1</sup> These ratings apply at 25 °C, unless otherwise noted. Note that stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

There are clamping diodes between the input pins and the power pins, and also between each other. When the input signal exceeds the supply rail by 0.3 V, the input current is limited to 10 mA.

<sup>&</sup>lt;sup>3</sup> Limited by Over Temperature Protection (OTP).

<sup>&</sup>lt;sup>4</sup> IPC/JEDEC J-STD-020 Compliant

<sup>&</sup>lt;sup>5</sup> Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>6</sup> ANSI/ESDA/JEDEC JS-001 Compliant

<sup>&</sup>lt;sup>7</sup> ANSI/ESDA/JEDEC JS-002 Complaint

$<sup>^{8}~\</sup>theta_{\text{JA}}$  addresses the conditions for soldering devices onto circuit boards to achieve surface mount packaging.

# **Specifications**

The • denotes the specification which apply over the specified temperature range, otherwise specifications are at  $V_S = \pm 15 \text{ V}$ ,  $V_{CM} = 0 \text{ V}$ ,  $T_A = 25 \text{ °C}$ .

| Parameter                    | Symbol                           | Conditions                                             |   | Min | Тур. | Max  | Unit  |

|------------------------------|----------------------------------|--------------------------------------------------------|---|-----|------|------|-------|

| INPUT CHARACTERISTICS        |                                  |                                                        |   |     |      |      |       |

|                              |                                  | B Grade                                                |   |     | 2.5  | 10   | μ٧    |

| Offset Voltage               | Vos                              | D Graue                                                | • |     |      | 65   | μ٧    |

| Onset voltage                | VOS                              | A Grade                                                |   |     | 5    | 20   | μ٧    |

|                              |                                  | A Grade                                                | • |     |      | 130  | μ٧    |

| Offset Voltage Drift         | TCVos                            | B Grade                                                | • |     | 0.25 | 0.5  | μV/°C |

|                              | 10005                            | A Grade                                                | • |     | 0.5  | 1.0  | μV/°C |

| Input Bias Current           | I <sub>B</sub>                   |                                                        |   |     | 5    | 25   | pА    |

|                              | ıB                               |                                                        | • |     |      | 10   | nA    |

| Input Offset Current         | I <sub>OS</sub>                  |                                                        |   |     | 2    | 10   | pА    |

|                              | 105                              |                                                        | • |     |      | 2    | nA    |

| Input Voltage Range          | IVR                              |                                                        |   | -15 |      | 12   | V     |

|                              |                                  | V <sub>CM</sub> = -15.0 V to 12 V                      |   | 120 | 130  |      | dB    |

| Common-Mode Rejection Ratio  | CMRR                             |                                                        | • | 114 |      |      | dB    |

| Common Mode Rejection Ratio  | OWNER                            | V <sub>CM</sub> = -15.0 V to 12.5 V                    |   | 114 | 124  |      | dB    |

|                              |                                  |                                                        | • | 108 |      |      | dB    |

|                              |                                  | $R_L = 10 \text{ k}\Omega$ , $Vo = \pm 14.5 \text{ V}$ |   | 126 | 140  |      | dB    |

| Open-Loop Voltage Gain       | A <sub>VOL</sub>                 |                                                        | • | 120 |      |      | dB    |

| opon 200p voltage dam        | , WOL                            | $R_L = 2 k\Omega$ , Vo = ±13.0 V                       |   | 126 | 140  |      | dB    |

|                              |                                  | 11(2), 40 ±10.0 4                                      | • | 120 |      |      | dB    |

| Input Resistance/Capacitance | R <sub>IN</sub> /C <sub>IN</sub> | Differential Mode                                      |   |     | TBD  |      | GΩ/pF |

|                              | T TIIV OILY                      | Common Mode                                            |   |     | TBD  |      | TΩ/pF |

| OUTPUT CHARACTERISTICS       |                                  |                                                        |   | T   |      | T    |       |

|                              |                                  | R <sub>L</sub> = 10 kΩ                                 |   |     | 100  | 200  | mV    |

| Output Voltage (High)        | V <sub>OH</sub>                  | 10 1/42                                                | • |     |      | 300  | mV    |

| Salpat Voltago (Flight)      | <b>▼</b> U⊓                      | $R_L = 2 k\Omega$                                      |   |     | 500  | 1000 | mV    |

|                              |                                  |                                                        | • |     |      | 1500 | mV    |

|                              |                                  | R <sub>L</sub> = 10 kΩ                                 |   |     | 50   | 100  | mV    |

| Output Voltage (Low)         | V <sub>OL</sub>                  |                                                        | • |     |      | 150  | mV    |

| Julput voltage (LOW)         |                                  | $R_L = 2 k\Omega$                                      |   |     | 250  | 500  | mV    |

|                              |                                  | IV - 7 1/77                                            | • |     |      | 750  | mV    |

| Short-Circuit Current        | Isc                              |                                                        |   |     | 25   |      | mA    |

| Parameter                             | Symbol             | Conditions                                                                |   | Min | Тур. | Max | Unit              |

|---------------------------------------|--------------------|---------------------------------------------------------------------------|---|-----|------|-----|-------------------|

| POWER SUPPLY                          |                    |                                                                           |   |     |      |     |                   |

| Supply Current (per Amplifier)        | I <sub>SY</sub>    | V <sub>O</sub> = 0 V                                                      |   |     | 500  | 525 | μA                |

| Supply Culterit (per Ampilier)        | isy                | V0-0 V                                                                    | • |     | 667  | 700 | μA                |

| Power Supply Rejection Ratio          | PSRR               | $V_{SY} = \pm 3 \text{ V to } \pm 18 \text{ V}$                           |   | 126 | 140  |     | dB                |

|                                       | TORK               | VSY - 13 V tO 110 V                                                       | • | 120 |      |     | dB                |

| DYNAMIC PERFORMANCE                   |                    |                                                                           |   |     |      |     |                   |

| Slew Rate                             | SR                 | $R_L = 2 k\Omega$                                                         |   |     | 0.9  |     | V/µs              |

| Gain Bandwidth Product                | GBP                | $R_L = 2 k\Omega$ , $G = 100$ , $V_{IN} = 100 \text{ mV}_{P-P}$           |   |     | 1.3  |     | MHz               |

| -3 dB Bandwidth                       |                    | $R_L = 2 \text{ k}\Omega$ , $G = 1$ , $V_O = 100 \text{ m}V_{P-P}$        |   |     | 3.4  |     | MHz               |

| O. III Ti                             | ts                 | to 0.1%, G = -1, 0 to 10 V step                                           |   |     | 15   |     | μs                |

| Settling Time                         |                    | to 0.01%, G = -1, 0 to 10 V step                                          |   |     | 16   |     | μs                |

| Overload Recovery Time                | tor                | $R_L$ = 10 kΩ, G = -10, VIN = ±2 V step                                   |   |     | 2    |     | μs                |

| Total Harmonic Distortion + Noise     | THD + N            | $R_L = 2 \text{ k}\Omega$ , G = 1, f = 1 kHz,<br>$V_O = 3.5 \text{ Vrms}$ |   |     | -112 |     | dB                |

| Phase Margin                          | PM                 | $R_L = 2 \text{ k}\Omega$ , $G = 1$ , $VIN = 100 \text{ mV}_{P-P}$        |   |     | 57   |     | 0                 |

| Multiple Amplifier Channel Separation | Cs                 | $R_L$ = 10 k $\Omega$ , f = 1 kHz                                         |   |     | -120 |     | dB                |

| NOISE PERFORMANCE                     |                    |                                                                           |   |     |      |     |                   |

| Voltage Noise                         | e <sub>n,P-P</sub> | 0.1 Hz to 10 Hz                                                           |   |     | 0.8  |     | μV <sub>P-P</sub> |

| Voltage Noise Density                 | <b>e</b> n         | f = 1 kHz                                                                 |   |     | 10   |     | $nV/\sqrt{Hz}$    |

| Current Noise Density                 | i <sub>n</sub>     | f = 1 kHz                                                                 |   |     | 2    |     | fA /√Hz           |

| OVER TEMPERATURE PROTECTION           |                    |                                                                           |   |     |      |     |                   |

| Trigger Temperature                   | T <sub>IN</sub>    |                                                                           |   |     | 150  |     | °C                |

| Exit Temperature                      | T <sub>EXIT</sub>  |                                                                           |   |     | 130  |     | °C                |

| TEMPERATURE RANGE                     |                    | Specified Temperature Range                                               |   | -40 |      | 125 | °C                |

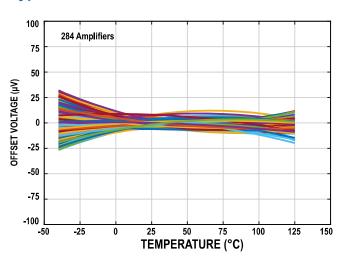

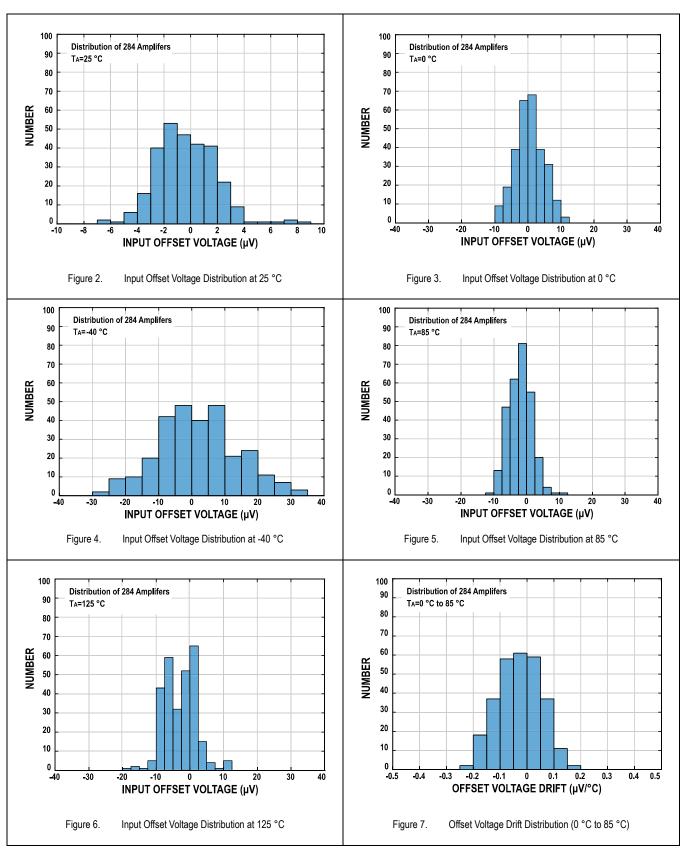

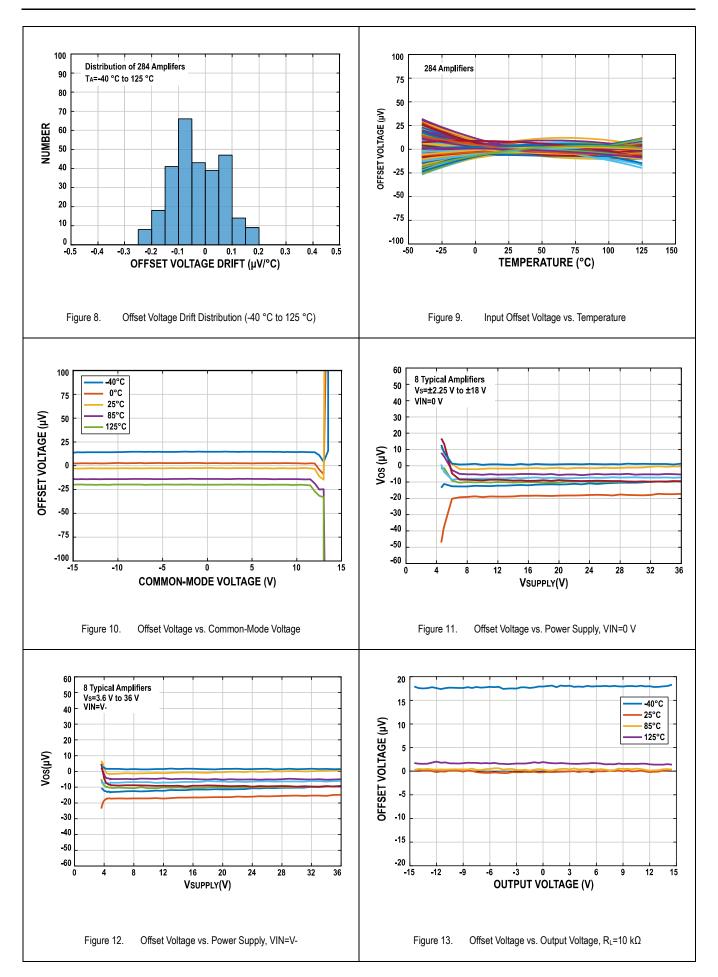

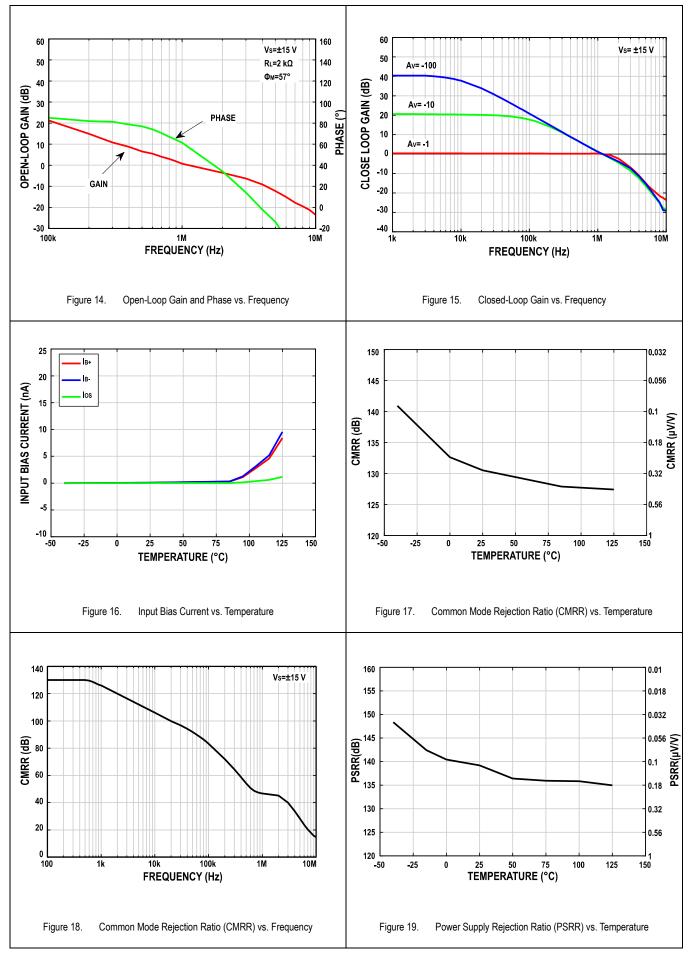

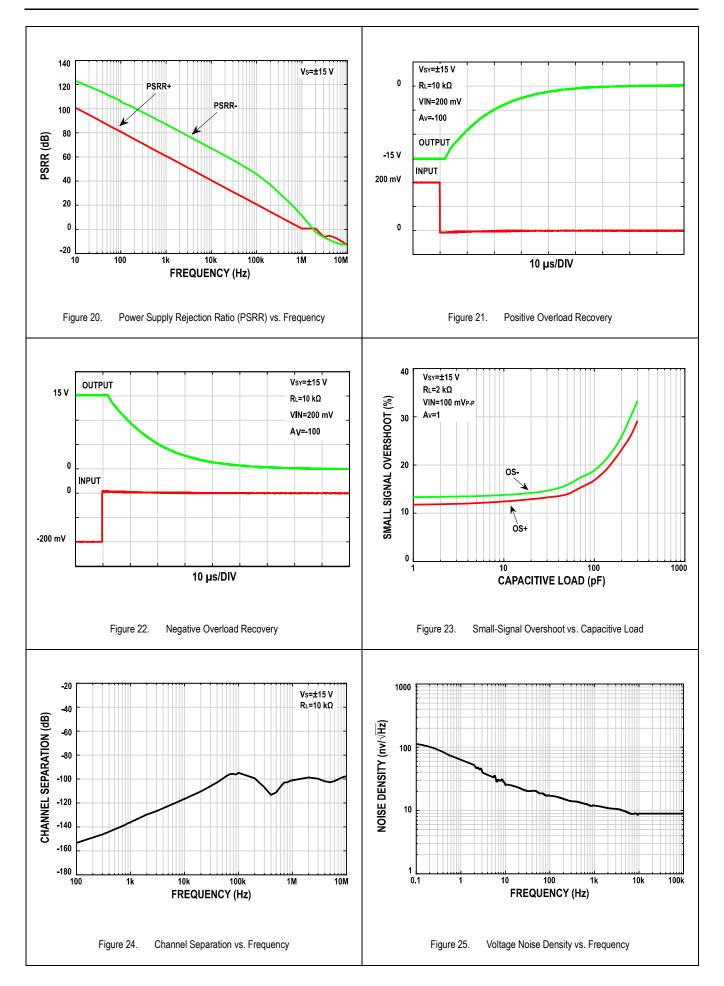

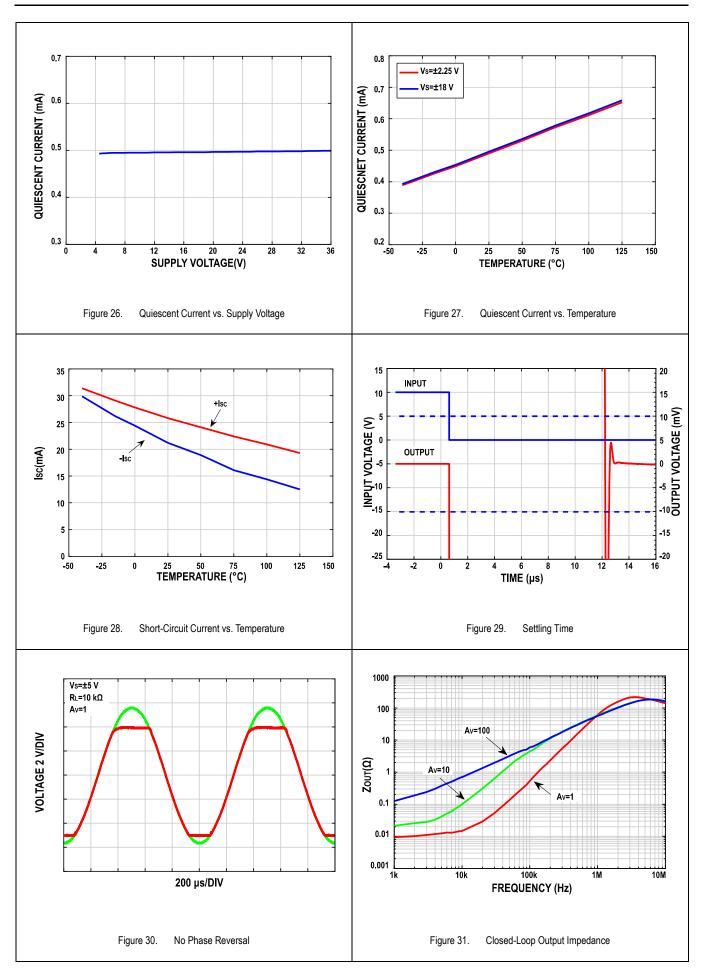

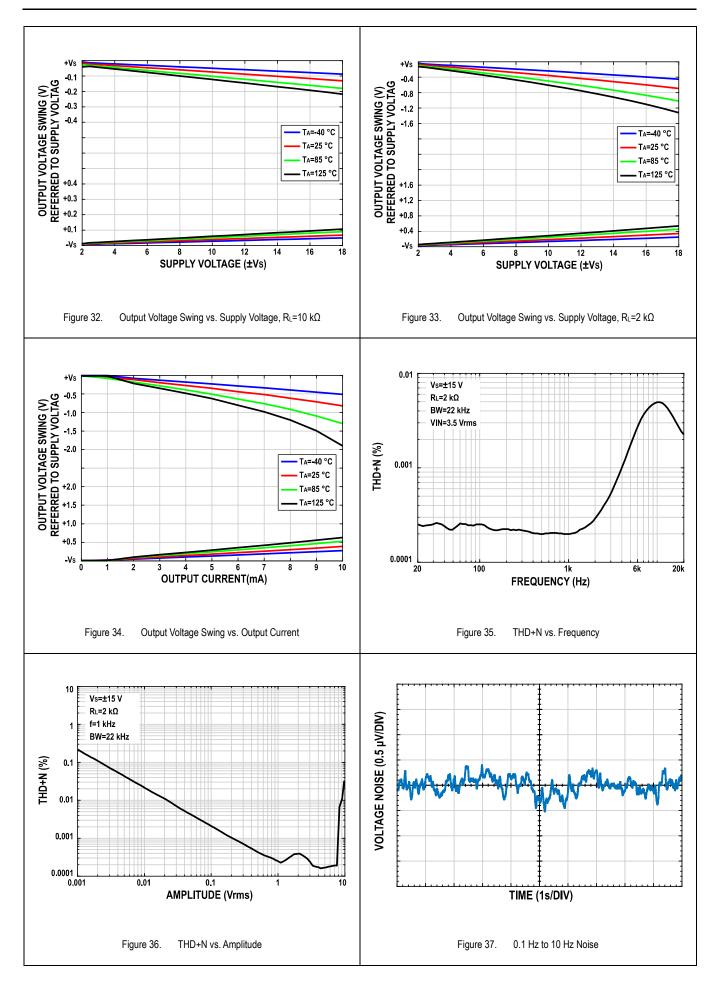

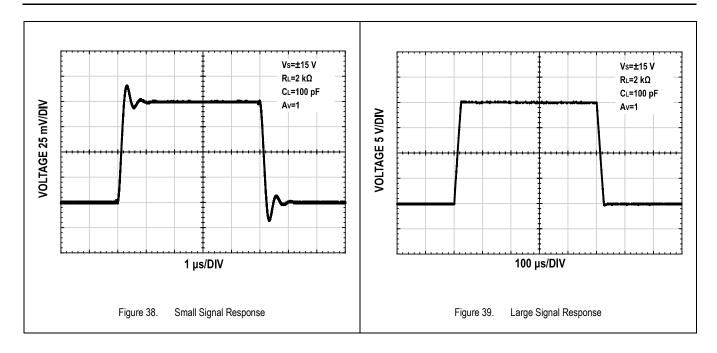

# **Typical Performance Characteristics**

Unless otherwise stated,  $V_{SY} = \pm 15.0 \text{ V}$ ,  $V_{CM} = 0 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$ .

# **Theory of Operation**

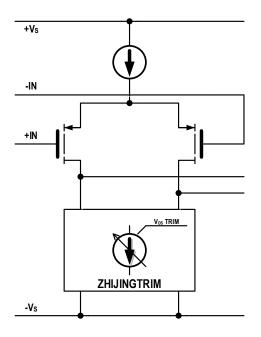

#### Post-package Trimming

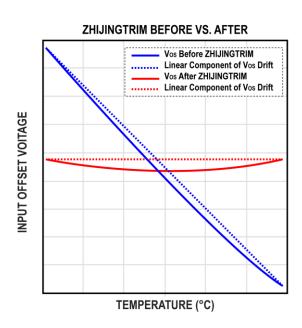

The ZJA3008 precision operational amplifier boasts a carefully designed MOS input stage, enabling it to maintain an exceptionally low input current of 25 pA maximum at 25 °C. Taking precision to the next level, the ZJA3008 employs ZJW's proprietary post-package trimming technology ZHIJINGTRIM®. This innovative approach involves fine-tuning adjustments (as shown in Figure 40), offering distinct advantages over traditional laser trimming techniques used at the wafer test stage. This post-package trimming method not only minimizes inherent process variations introduced during wafer manufacturing, but also significantly reduces additional defects potentially generated during the plastic molding process. Ultimately, the trimming results in the ZJA3008's exceptional performance: ultra-low offset voltage (10 µV maximum at 25 °C) and ultra-low offset voltage drift (0.5 µV/°C maximum across the specified temperature range in SOIC-8 package). Furthermore, ZJA3008 delivers consistent high accuracy cross wide supply voltage range from 4.5 V to 36 V. These remarkable characteristics make the ZJA3008 the ideal choice for demanding applications, such as high-impedance sensors interface, precision filtering and high-voltage high-precision data acquisition.

Figure 40. Diagram of Post-package Trimming Scheme (Left) and Effect (Right)

### **Applications Information**

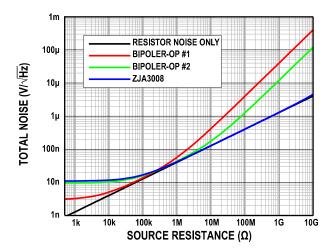

#### Source Impedance, Input Bias Current Affect both Output Noise and System Offset Voltage

As shown in Figure 41, the output noise density of classic bipolar input stage amplifiers #1, #2, and ZJA3008 is depicted at the 1 kHz frequency point under various source impedances. Bipolar amplifiers typically have large input bias current, leading to significant input current noise. When the source impedance exceeds  $100~\text{k}\Omega$ , the system noise rapidly increases. In contrast, the ZJA3008 has exceptionally low input bias current, resulting in minimal input noise current, thus its noise contribution to the system is negligible. When the source impedance surpasses  $10~\text{k}\Omega$ , the system noise is mainly contributed by the source impedance, which appears in the graph as a straight line overlapping the black line representing the noise contributed by source impedance. Similarly, high source impedance can cause considerable system offset voltage and its temperature drift due to the amplifier's input bias current, input offset current, and their temperature drifts. These effects are common in bipolar input amplifiers and zero-drift amplifiers. The ZJA3008, however, leverages its exceptional low input current to fully guarantee low system offset voltage and its temperature drift.

Figure 41. System Total Noise vs. Source Impedance

#### Input Common Mode Voltage Range

While traditional bipolar amplifiers demand 1 V to 2 V of headroom from both supply rails for proper input common-mode voltage operation, often necessitating dual-supply configurations for applications with 0 V input common-mode signals, the ZJA3008 offers a distinct advantage. It accepts input common-mode voltages down to the negative supply rail, enabling seamless operation with both single and dual power supply designs. As illustrated in Figure 10, this capability, along with its wide supply voltage range (4.5 V to 36 V) and rail-to-rail output, empowers the ZJA3008 to address a broader spectrum of application requirements with exceptional flexibility.

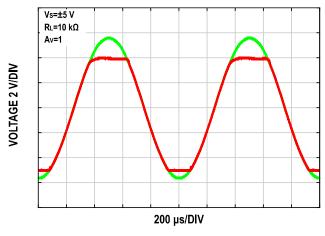

### **Output Phase Reversal**

Phase reversal is defined as a change of polarity in the amplifier transfer function. Many operational amplifiers exhibit phase reversal when the voltage applied to the input is greater than the maximum common-mode voltage. In some instances, this can cause permanent damage to the amplifier. In feedback loops, it can result in system lockups or equipment damage. The ZJA3008 is immune to phase reversal problems even at input voltages beyond the supplies.

Figure 42. ZJA3008 Has No Output Phase Reversal

### **Overload Recovery Time**

Many zero-drift amplifiers, whether auto-zero or chopping, are plagued by a long overload recovery time, often in ms, due to the complicated settling behavior of the internal nulling loops after saturation of the outputs. Recovery time is important in many applications, particularly where the operational amplifier must amplify small signals in the presence of large transient voltages. The ZJA3008, as a continuous signal processing amplifier, stands out in this regard. Compared to zero-drift amplifiers, its overload recovery time is significantly shorter, falling within a remarkable 2 µs, as demonstrably shown in the table below.

| Model        | Positive Overload Recovery (μs) | Negative Overload Recovery (µs) |

|--------------|---------------------------------|---------------------------------|

| ZJA3008      | 2                               | 2                               |

| Competitor A | 12.3                            | 18                              |

#### **Over Temperature Protection**

Due to its high operating voltage (up to 36 V) and short-circuit current (up to 25 mA), the ZJA3008 can dissipate up to 1 W of power during use. As thermal resistance for various package formats typically exceeds 100 °C/W, self-heating and the risk of permanent damage from high temperatures are concerns in real-world applications. To address this, the ZJA3008 incorporates an automatic overtemperature protection (OTP) function. When the chip temperature reaches 150 °C, OTP triggers, putting the chip into shutdown mode. Both input and output terminals enter a high-impedance state, significantly reducing power consumption and facilitating temperature drop. Once the chip cools down to 130 °C, OTP disengages, and the chip resumes normal operation.

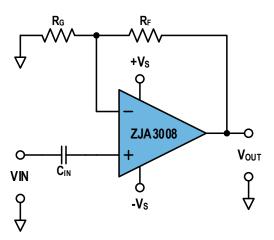

#### **Input Bias Current Return Path**

As shown in Figure 43, a simple AC coupling can be achieved by connecting a capacitor ( $C_{IN}$ ) in series between the non-inverting input (+) of the operational amplifier and the actual input (VIN) to isolate the DC voltage component of the input voltage. This coupling method is especially common in high-gain applications: when the gain is high, even a small DC voltage component at the amplifier input can affect the available output dynamic range of the op amp, and may even cause output saturation. However, for this AC coupling method located at the high-impedance input, if the input current of the positive input is not provided with a proper bias current return path, it will cause serious bias problems: in fact, the input bias current will slowly charge/discharge the capacitor  $C_{IN}$ , depending on the polarity of the input bias current, the capacitor will charge to the positive supply voltage or discharge to the negative supply voltage. This bias current caused offset voltage will be amplified by the op amp's closed-loop DC gain until the op amp's input voltage exceeds its input voltage range, and this process may take a long time. For example, for an operational amplifier with an FET input stage, if its input current is 1 pA, through a 0.1  $\mu$ F capacitor, the offset voltage will be ramped at the speed of:

When the closed-loop DC gain is 100, the output voltage ramp rate is 3.6 V/h. Therefore, the actual circuit will not show obvious failure until after several hours. Using an AC coupled oscilloscope for a short-term test may not be able to find this problem.

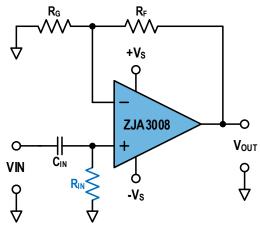

Figure 43. Incorrect AC-Coupled Op Amp Circuit

One simple solution is shown in Figure 44. A resistor ( $R_{IN}$ ) is connected between the input of the operational amplifier and ground, providing an input bias current return path. Unlike operational amplifiers with FET inputs, traditional bipolar operational amplifiers need to set  $R_{IN}$  to the parallel value of  $R_{G}$  and  $R_{F}$  to minimize the input offset voltage caused by input bias current, considering the mismatching between the two inputs of the op amp. Since this resistor will introduce additional noise to the overall circuit, the value of the input coupling capacitor and the resistor should be balanced between non-ideal factors such as input impedance, input high-pass cutoff frequency, and input offset voltage according to actual needs. Typical resistor value is generally between 100 k $\Omega$  and 1 M $\Omega$ .

Figure 44. Creating an Input Bias Current Return Path

### **Temperature Hysteresis**

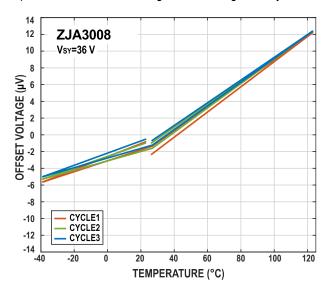

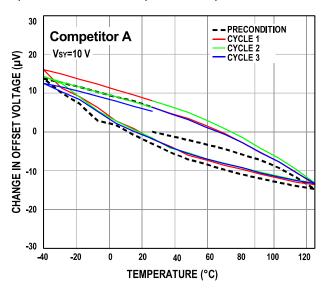

Temperature hysteresis, that is, the stability vs. cycling of temperature. Hysteresis is an important parameter because it tells the system designer how closely the signal returns to its starting amplitude after the ambient temperature changes and subsequent return to room temperature. Figure 45 shows the change in input offset voltage as the temperature cycles three times from room temperature to 125 °C to -40 °C and back to room temperature. In the three full cycles, the offset hysteresis is within 2  $\mu$ V, compared with the competitor A's data shown in Figure 46, it is significantly better without precondition, which is required for competitor A.

Figure 45. ZJA3008 Offset Voltage over Three Full Temperature Cycles

Figure 46. Competitor A Offset Voltage over Three Full Temperature Cycles

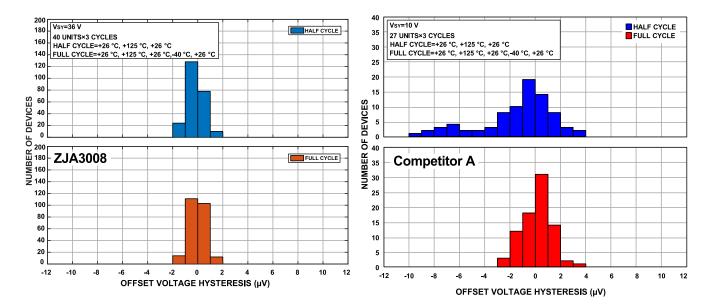

The histogram in Figure 47 shows that ZJA3008's hysteresis is similar no matter the device is cycled through full or only a half cycle, from room temperature to 125 °C and back to room temperature. In contrast, Competitor A's hysteresis demonstrates significant difference between full cycle and half cycle.

Figure 47. Histogram Showing the ZJA3008's Temperature Hysteresis of the Offset Voltage over Three Full Cycles and over Three Half Cycles

Figure 48. Histogram Showing the Competitor A's Temperature Hysteresis of the Offset Voltage over Three Full Cycles and over Three Half Cycles

ZJA3008 exhibits significantly smaller and more consistent temperature hysteresis, regardless of whether it's cycled through a full or half cycle. This makes it more suitable for precision signal conditioning to build more reliable systems. What's more, ZJA3008 does not require the precondition process that is necessary for competitor A. This feature makes it is very easy of use with high performance and can lower the system cost.

## **Applications and Implementation**

### **Bandpass KRC Filter**

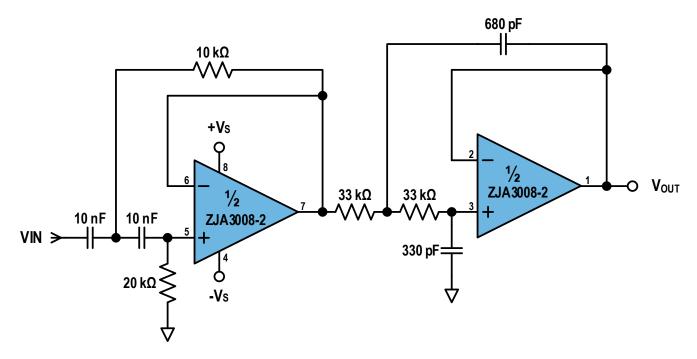

The ZJA3008 series of amplifiers are particularly suitable for use in the design of precision filters, such as the typical KRC filter, as shown in Figure 49. With their excellent low offset and high CMRR performance, precision filters using ZJA3008 can guarantee stable performance over a wide input range while also having sufficient output dynamic range even at high gain. On the other hand, due to the ZJA3008-2 and ZJA3008-4's ultra-high channel separation, even using the dual amplifiers in the same ZJA3008-2 can achieve excellent filter design without worrying about performance degradation caused by channel crosstalk.

ZJA3008's power supply current of 500 μA makes it suitable for both portable, battery powered systems and line powered systems.

Figure 49. Using ZJA3008-2 to Build a 2-stage Band-pass KRC Filter

### **Layout Guidance**

For optimized performances of the device, good PCB layout practices are recommended, including:

Noise may be conducted into the analog circuit through the op amp supply pins, using the low ESR 0.1 µF ceramic capacitor as

decoupling capacitor. Put it as close as possible to the power pin can effectively reduce the noise caused by the power supplies.

- Normally input trace is more sensitive, keep the trace as short as possible. In order to reduce the noise of parasitic coupling, keep the input signals far from the power supply and/or outputs. If this is not possible, the sensitive traces should be perpendicular to others, so that the noise coupled through the parasitic capacitance can be as small as possible.

- If the it is high impedance signal source, it is necessary to design a guard ring. Guard rings can significantly reduce leakage currents from nearby traces that are at different potentials.

- Place the peripheral components as close as possible to the pins of the op amp, such as placing R<sub>F</sub>, C<sub>F</sub> and R<sub>G</sub>. And delete the PCB ground plane below the inverting input to minimize parasitic capacitance.

- For best leakage performance, it is recommended to clean the PCBA after soldering and baking at 85 °C for 30 minutes to remove any potential moisture from the package.

- In addition, separate grounding of the analog and digital parts of the circuit is one of the simplest and most effective noise suppression methods. When designing the PCB, plan the layout of the ground current return paths of the analog and digital parts so that the ground current return paths do not interfere each other. Using one or more layers of the multi-layer PCB as the ground also helps to reduce the ground impedance and noise.

## **Outline Dimensions**

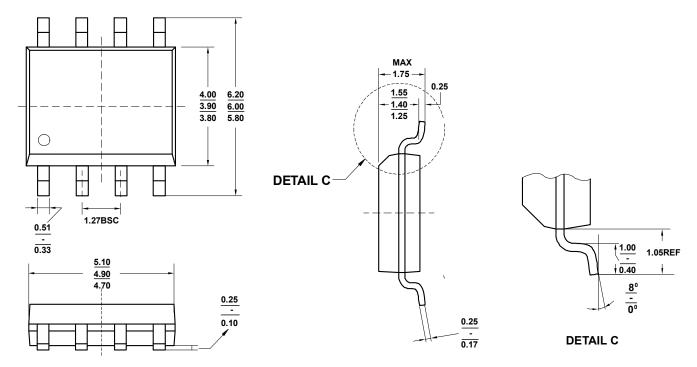

Figure 50. 8-Lead SOIC Package Dimensions shown in millimeters

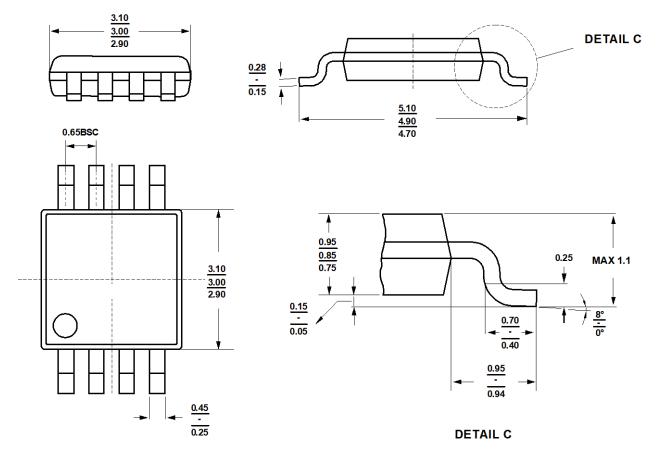

Figure 51. 8-Lead MSOP Package Dimensions shown in millimeters

# **Ordering Guide**

| Model     | Orderable Device | Package | Maximum Vos & TCVos                    | Temperature Range (°C) | External<br>Package |

|-----------|------------------|---------|----------------------------------------|------------------------|---------------------|

|           | ZJA3008-2BSABT   | 0010.0  | 10                                     | 40 to 405              | Tube                |

|           | ZJA3008-2BSABR   | SOIC-8  | 10 μV & 0.5 μV/°C                      | -40 to 125             | 13" reel            |

|           | ZJA3008-2ASABT   | 0010.0  | 20 μV & 1.0 μV/°C                      | -40 to 125             | Tube                |

| 7142000 0 | ZJA3008-2ASABR   | SOIC-8  |                                        |                        | 13" reel            |

| ZJA3008-2 | ZJA3008-2BUABT   | MSOP-8  | 10 μV & 0.5 μV/°C<br>20 μV & 1.0 μV/°C | -40 to 125             | Tube                |

|           | ZJA3008-2BUABR   |         |                                        |                        | 13" reel            |

|           | ZJA3008-2AUABT   |         |                                        |                        | Tube                |

|           | ZJA3008-2AUABR   | MSOP-8  |                                        | -40 to 125             | 13" reel            |

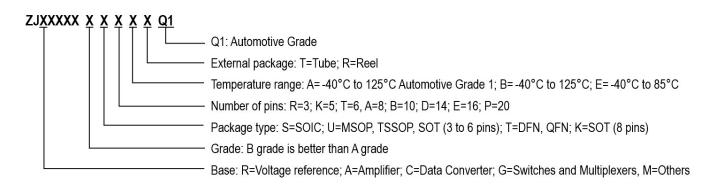

### **Product Order Model**

# **Related Parts**

| Part Number                  | Description                                                                                                   | Comments                                                                                                                                                      |

|------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC                          |                                                                                                               |                                                                                                                                                               |

| ZJC2020                      | 20-bit 350 kSPS SAR ADC                                                                                       | Fully differential input, SINAD 101.4 dB, THD -118 dB                                                                                                         |

| ZJC2000/2010                 | 18-bit 400 kSPS/200 kSPS SAR ADC                                                                              | Fully differential input, SINAD 99.3 dB, THD -113 dB                                                                                                          |

| ZJC2001/2011                 | 16-bit 500 kSPS/250 kSPS SAR ADC                                                                              | Fully differential input, SINAD 95.3 dB, THD -113 dB                                                                                                          |

| ZJC2002/2012                 |                                                                                                               | Pseudo-differential unipolar input, SINAD 91.7 dB, THD -105 dB                                                                                                |

| ZJC2003/2013                 | 16-bit 500 kSPS/250 kSPS SAR ADC                                                                              | Pseudo-differential bipolar input, SINAD 91.7 dB, THD -105 dB                                                                                                 |

| ZJC2004/2014<br>ZJC2005/2015 | 18-bit 400 kSPS/200 kSPS SAR ADC                                                                              | Pseudo-differential unipolar input, SINAD 94.2 dB, THD -105 dB<br>Pseudo-differential bipolar input, SINAD 94.2 dB, THD -105 dB                               |

| ZJC2007/2017<br>ZJC2008/2018 | 14-bit 600 kSPS/300 kSPS SAR ADC                                                                              | Pseudo-differential unipolar input, SINAD 85 dB, THD -105 dB<br>Pseudo-differential bipolar input, SINAD 85 dB, THD -105 dB                                   |

| ZJC2009                      | Small size, 12-bit 1 MSPS SAR ADC                                                                             | Single-ended input, SOT23-6, 2.3 V to 5 V, SINAD 73 dB, THD -89 dB                                                                                            |

| ZJC2100/1-18                 | 18-bit 400 kSPS/200 kSPS 4-ch differential SAR ADC, SIN                                                       | NAD 99.3 dB, THD -113 dB                                                                                                                                      |

| ZJC2100/1-16                 | 16-bit 500 kSPS/250 kSPS 4-ch differential SAR ADC, SIN                                                       | NAD 95.3 dB, THD -113 dB                                                                                                                                      |

| ZJC2102/3-18                 | 18-bit 400 kSPS/200 kSPS 8-ch pseudo-differential SAR A                                                       | ADC, SINAD 94.2 dB, THD -105 dB                                                                                                                               |

| ZJC2102/3-16                 | 16-bit 500 kSPS/250 kSPS 8-ch pseudo-differential SAR A                                                       |                                                                                                                                                               |

| ZJC2102/3-14                 | 14-bit 600 kSPS/300 kSPS 8-ch pseudo-differential SAR A                                                       |                                                                                                                                                               |

| ZJC2104/5-18                 | 18-bit 400 kSPS/200 kSPS 4-ch pseudo-differential SAR A                                                       |                                                                                                                                                               |

| ZJC2104/5-16                 | 16-bit 500 kSPS/250 kSPS 4-ch pseudo-differential SAR A                                                       | ADC, SINAD 91.7 dB, THD -105 dB                                                                                                                               |

| DAC                          |                                                                                                               |                                                                                                                                                               |

| ZJC2541-18/16/14             | 18/16/14-bit 1 MSPS single channel DAC with                                                                   | Power on reset to 0 V (ZJC2541) or V <sub>REF</sub> /2 (ZJC2543), 1 nV-S glitch, SOIC-8, MSOP-10/8,                                                           |

| ZJC2543-18/16/14             | unipolar output                                                                                               | DFN-10 packages                                                                                                                                               |

| ZJC2542-18/16/14             | 18/16/14-bit 1 MSPS single channel DAC with                                                                   | Power on reset to 0 V (ZJC2542) or V <sub>REF</sub> /2 (ZJC2544), 1 nV-S glitch, SOIC-14, TSSOP-16,                                                           |

| ZJC2544-18/16/14             | bipolar output                                                                                                | QFN-16 packages                                                                                                                                               |

| Amplifier                    |                                                                                                               |                                                                                                                                                               |

| ZJA3000-1/2/4                | Single/Dual/Quad 36 V low bias current precision                                                              | 3 MHz, 35 $\mu$ V max Vos, 0.5 $\mu$ V/°C max TCVos, 25 pA max Ibias, 1 mA/ch, input to V-                                                                    |

| ZJA3001-1/2/4                | Op Amps                                                                                                       | (ZJA3000 only), RRO, 4.5 V to 36 V                                                                                                                            |

| ZJA3018-2<br>ZJA3008-2       | OVP ±75 V, 36 V, Low Power, High Precision Op Amp<br>36 V, Low Power, High Precision Op Amp                   | 1.3 MHz, 10 $\mu$ V max Vos, 0.5 $\mu$ V/°C max TCVos, 25 pA max Ibias, 0.5 mA/ch, OVP ±75 V (ZJA3018 only), RRO, 4.5 V to 36 V                               |

| ZJA3512-2                    | Dual 36 V 7 MHz precision JFET Op Amps                                                                        | 7 MHz, 35 V/μS, 50 μV max Vos, 1 μV/°C max TCVos, 2 mA/ch, RRO, 9 V to 36 V                                                                                   |

| ZJA3206/06/02-1/2            | Precision 24/11.6/5.3 MHz CMOS RRIO Op Amps                                                                   | 24/11.6/5.3 MHz, RRIO, 30 μV max Vos, 1 μV/°C max TCVos, 0.6 pA lb, 2.7 V to 5.5 V                                                                            |

| ZJA3600/1                    | 36 V ultra-high precision in-amp                                                                              | CMRR 105 dB min (G = 1), 25 pA max lb, 25 µV max Vosi, ±2.4 V to ±18 V, -40 °C to 125 °C                                                                      |

| ZJA3611, ZJA3609             | 36 V precision wider bandwidth precision in-amp (G≥10)                                                        | CMRR 120 dB min (G = 10), 25 pA max Ibias, 25 µV max Vosi, 1.2 MHz BW (G = 10)                                                                                |

| ZJA3676/7<br>ZJA3678/9       | Low power, G=1 Single/Dual 36 V difference amplifier Low power, G=0.5/2 Single/Dual 36 V difference amplifier | Input protection to ±65 V, CMRR 104 dB min (G = 1), Vos 100 μV max, gain error 15 ppm max, 500 kHz BW (G = 1), 330 μA/channel, 2.7 V to 36 V                  |

| ZJA3669                      | High Common-Mode Voltage Difference Amplifier                                                                 | ±270 V CMV, 2.5 kV ESD, 96 dB min CMRR, 450 kHz BW, 4 V to 36 V, SOIC-8                                                                                       |

| ZJA3100                      | 15 V precision fully differential amplifier                                                                   | 145 MHz, 447 V/μS, 50 nS to 16-bit, 50 μV max Vos, 4.6 mA lq, SOIC/MSOP-8, QFN-16                                                                             |

|                              | ' '                                                                                                           |                                                                                                                                                               |

| ZJA3236/26/22-2              | Low-cost 22/10/5 MHz CMOS RRIO Op Amps                                                                        | 22/11/5 MHz, RRIO, 2 mV max Vos, 6 μV/°C max TCVos, 0.6 pA lb, 2.7 V to 5.5 V                                                                                 |

| ZJA3622/8  Voltage Referen   | 36 V low-cost precision in-amp                                                                                | 0.5 nA max Ibias, 125 $\mu$ V max Vosi, 625 kHz BW (G = 10), 3.3 mA Iq, $\pm$ 2.4 V to $\pm$ 18 V                                                             |

|                              |                                                                                                               |                                                                                                                                                               |

| ZJR1004                      | 40 V supply precision voltage reference                                                                       | V <sub>OUT</sub> = 2.048/2.5/3/3.3/4.096/5/10 V, 5 ppm/°C max drift -40 °C to 125 °C                                                                          |

| ZJR1001/2<br>ZJR1003         | 5.5 V low power voltage reference<br>(ZJR1001 with noise filter option)                                       | V <sub>OUT</sub> = 2.048/2.5/3/3.3/4.096/5 V, 5 ppm/°C max drift -40 °C to 125 °C, ±0.05% initial error, 130 μA, ZJR1001/2 in SOT23-6, ZJR1003 in SOIC/MSOP-8 |

| Switches and M               | lultiplexers                                                                                                  |                                                                                                                                                               |

| ZJG4438/4439                 | 36 V fault protection 8:1/dual 4:1 multiplexer                                                                | Protection to ±50 V power on & off, latch-up immune, Ron 270 Ω, 14.8 pC, ton 166 nS                                                                           |

| ZJG4428/4429                 | 36 V 8:1/dual 4:1 multiplexer                                                                                 | Latch-up immune, Ron 270 Ω, 14.8 pC charge injection, ton 166 nS                                                                                              |

| Quad Matching                | ,                                                                                                             |                                                                                                                                                               |

| ZJM5400                      | ±75 V precision match resistors                                                                               | Mismatch < 100 ppm, 10k:10k:10k:10k, 100k:100k:100k:100k, 100k:10k:10k:10k:10k:1k:1k:1l:1M:1M:1M:1M:5k:1k:1k:5k, 5k:1.25k:1.25k:5k, 9k:1k:1k:9k, ESD: 3.5 kV  |