# **Dual Channel Isolated Gate-Driver ICs**

### Hynetek Semiconductor Co., Ltd.

**HP3600**

#### **FEATURES**

Common-mode transient immunity (CMTI) greater than 150 kV/µs

Fast input-to-output propagation (48 ns)

4-A peak source, 6-A peak sink output

Up to 33-V VDD output drive supply

3-V VDD UVLO

-5V handling capability on input stage

Fast clamping of the output under UVLO conditions

Programmable overlap and dead time

Fast disable for power sequencing

SOP-16 package

Operating junction temperature range of -40 °C to 150 °C

### **APPLICATIONS**

Telecom PSU

Data center

Outdoor PSU

OBC

EV charging

Industry automation

Home appliance

#### **GENERAL DESCRIPTION**

The HP3600 isolated driver is an isolated dual channel gate driver can be configured as high-side/low-side drivers. The peak source output current is 4.0A and the peak sink output current is 6.0A. Programmable dead time (DT) feature is available. Pulling high the DIS pin shuts down both outputs simultaneously and allows for normal operation when the DIS pin is open or pulled low. As a fail-safe measure, primary-side logic failures force both outputs low.

The VDDA and VDDB supply voltage are up to 33 V. A wide input VDDI range from 3 V to 18 V makes the driver suitable for interfacing with both analog and digital controllers. All the supply voltage pins have under voltage lock-out (UVLO) protection.

The HP3600 has 3.0kVRMS isolation for 1 minute per UL 1577 in SOP-16 package.

High CMTI, low propagation delay makes the HP3600 is suitable for a wide range of isolated MOSFET and SiC or GaN FET gate drive applications.

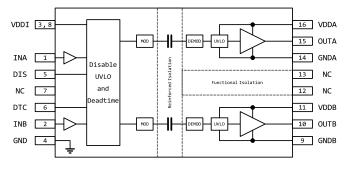

Figure 1 Functional Block Diagram

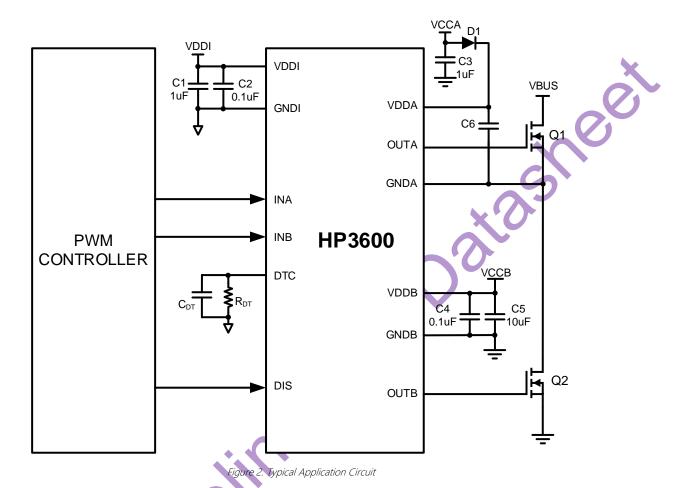

### TYPICAL APPLICATION CIRCUIT

### **TABLE OF CONTENTS**

| Features                                    |    |

|---------------------------------------------|----|

| Applications                                |    |

| General Description                         |    |

| Typical Application Circuit                 |    |

| Table of Contents                           |    |

| Revision History                            |    |

| Pin Configuration and Function Descriptions |    |

| Specifications                              |    |

| Absolute Maximum Ratings                    |    |

| Thermal Resistance                          |    |

| ESD Caution                                 |    |

| Package Outline Dimensions                  |    |

| Ordering Guide                              | 10 |

| Important Notice                            |    |

### **REVISION HISTORY**

| Version  | Date    | Descriptions    |  |

|----------|---------|-----------------|--|

| Rev. 0.1 | 2023/11 | Initial version |  |

**DATA SHEET HP3600**

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

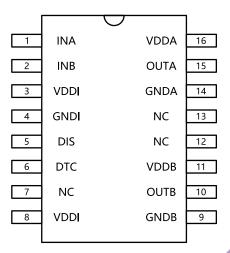

Figure 3 16-Pin SOP-16 Configuration

Table 0-1. Pin Function Descriptions for SOP-16

|     |      |      | 1 INA VDDA 16                                                                                                                                                                                                                                                                                                                             |

|-----|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |      |      | 2 INB OUTA 15                                                                                                                                                                                                                                                                                                                             |

|     |      |      | 3 VDDI GNDA 14                                                                                                                                                                                                                                                                                                                            |

|     |      |      | 4 GNDI NC 13                                                                                                                                                                                                                                                                                                                              |

|     |      |      | 5 DIS NC 12                                                                                                                                                                                                                                                                                                                               |

|     |      |      | 6 DTC VDDB 11                                                                                                                                                                                                                                                                                                                             |

|     |      |      | 7 NC OUTB 10                                                                                                                                                                                                                                                                                                                              |

|     |      |      | 8 VDDI GNDB 9                                                                                                                                                                                                                                                                                                                             |

|     |      |      |                                                                                                                                                                                                                                                                                                                                           |

|     |      |      | Figure 3 16-Pin SOP-16 Configuration                                                                                                                                                                                                                                                                                                      |

|     |      |      | criptions for SOP-16                                                                                                                                                                                                                                                                                                                      |

| No. | Pin  | Туре | Primary Function                                                                                                                                                                                                                                                                                                                          |

| 1   | INA  | I    | Input signal for A channel. INA input has a TTL/CMOS compatible input threshold. This pin is pulled low internally if left open. It is recommended to tie this pin to ground if not used to achieve better noise immunity.                                                                                                                |

| 2   | INB  | I    | Input signal for B channel. INB input has a TTL/CMOS compatible input threshold. This pin is pulled low internally if left open. It is recommended to tie this pin to ground if not used to achieve better noise immunity.                                                                                                                |

| 3   | VDDI | Р    | Primary-side supply voltage. Locally decoupled to GND using a low ESR/ESL capacitor located as close to the device as possible.                                                                                                                                                                                                           |

| 4   | GNDI | Р    | Primary-side ground reference. All signals in the primary side are referenced to this ground.                                                                                                                                                                                                                                             |

| 5   | DIS  | I    | Disables both driver outputs if asserted high, enables if set low or left open. This pin is pulled low internally if left open. It is recommended to tie this pin to ground if not used to achieve better noise immunity. Bypass using a 1 nF low ESR/ESL capacitor close to DIS pin when connecting to a micro controller with distance. |

| 6   | DTC  |      | Dead time programming input. Connect a resistor between DTC and GNDI to program the dead time. A bypassing capacitor, 2.2nF or greater, is recommended to be put between DTC and GNDI to achieve better noise immunity.                                                                                                                   |

| 7   | NC   | -    | No Internal connection.                                                                                                                                                                                                                                                                                                                   |

| 8   | VDDI | Р    | Primary-side supply voltage. This pin is internally shorted to pin 3.                                                                                                                                                                                                                                                                     |

| 9   | GNDB | Р    | Ground for secondary-side driver B. Ground reference for secondary side B channel.                                                                                                                                                                                                                                                        |

| 10  | OUTB | 0    | Output of driver B. Connect to the gate of the B channel FET.                                                                                                                                                                                                                                                                             |

| 11  | VDDB | Р    | Secondary-side power for driver B. Locally decoupled to VSSB using low ESR/ESL capacitor located as close to the device as possible.                                                                                                                                                                                                      |

| 12  | NC   | -    | No Internal connection.                                                                                                                                                                                                                                                                                                                   |

| 13  | NC   | -    | No Internal connection.                                                                                                                                                                                                                                                                                                                   |

|     |      |      |                                                                                                                                                                                                                                                                                                                                           |

DATA SHEET **HP3600**

| No.  | Pin  | Туре | Primary Function                                                                                                                       |

|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------|

| 14 G | INDA | Р    | Ground for secondary-side driver A. Ground reference for secondary side A channel.                                                     |

| 15 C | OUTA | 0    | Output of driver A. Connect to the gate of the A channel FET.                                                                          |

| 16 V | 'DDA | Р    | Secondary-side power for driver A. Locally decoupled to VSSA using a low ESR/ESL capacitor located as close to the device as possible. |

|      | Č,   |      | Preliminary. Datashee                                                                                                                  |

## **SPECIFICATIONS**

$V_{DDI}$  = 5 V, 0.1 $\mu$ F capacitor from VDDI to GNDI,  $V_{DDA}$  =  $V_{DDB}$  =15V, 1 $\mu$ F capacitor from VDDA and VDDB to GNDA and GNDB,  $T_A$  = -40°C to +125°C, unless otherwise specified.

| Tahla | ∩_1    | Flectrical   | Characteristics |  |

|-------|--------|--------------|-----------------|--|

| rabie | V- I . | . Electricai | Characteristics |  |

| Parameter                                          | Symbol                                         | Conditions                                                                                     | Min | Тур  | Max | Unit |

|----------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------|-----|------|-----|------|

| POWER SUPPLY                                       | <u> </u>                                       |                                                                                                |     |      | 0   |      |

| Input supply voltage                               | V <sub>DDI</sub>                               |                                                                                                | 3   |      | 18  | V    |

| Input supply quiescent current                     | I <sub>DDI</sub>                               | V <sub>INA</sub> = 0 V, V <sub>INB</sub> = 0 V                                                 | 1.5 | 2.0  | 2.5 | mA   |

| Input supply operating current                     | I <sub>DDI</sub>                               | $F_{sw}$ = 50 kHz, current per channel, $C_{OUT}$ = 100 pF                                     | 1.9 | 2.0  | 3.1 | mA   |

| Output supply voltage                              | $V_{DDA}/V_{DDB}$                              |                                                                                                | 3.5 |      | 30  | V    |

| Output supply quiescent current                    | IVDDA/IVVDB                                    | V <sub>INA</sub> = 0 V, V <sub>INB</sub> = 0 V                                                 | 0.8 | 1.3  | 2   | mA   |

| Output supply operating current                    | IVDDA/IVVDB                                    | F <sub>sw</sub> = 50 kHz, current per channel, C <sub>OUT</sub> = 100 pF                       | 1.2 | 1.7  | 2.3 | mA   |

| VDDA/VDDB UNDER VOLTAGE                            | LOCKOUT (                                      | (UVLO)                                                                                         |     |      |     |      |

| UVLO turn-on threshold                             | V <sub>UVLO_ON</sub>                           |                                                                                                | 3.2 | 3.5  | 3.8 | V    |

| UVLO turn-off threshold                            | V <sub>UVLO_OFF</sub>                          |                                                                                                | 2.7 | 3.0  | 3.3 | V    |

| UVLO threshold hysteresis                          | Vuvlo_HYST                                     | ~~~                                                                                            |     | 0.5  |     | V    |

| VDDI UNDER VOLTAGE LOCKO                           | OUT (UVLO)                                     |                                                                                                |     |      |     |      |

| UVLO turn-on threshold                             | V <sub>DDI_ON</sub>                            |                                                                                                | 2.5 | 2.7  | 2.9 | ٧    |

| UVLO turn-off threshold                            | V <sub>DDI_OFF</sub>                           |                                                                                                | 2.3 | 2.5  | 2.7 | V    |

| UVLO threshold hysteresis                          | V <sub>DDI_HYST</sub>                          |                                                                                                |     | 0.2  |     | V    |

| INPUT (INA, INB)                                   | -10                                            |                                                                                                |     |      |     |      |

| Input voltage threshold for transition Low to High | Vinh                                           |                                                                                                | -   | 1.7  | 2.1 | V    |

| Input voltage threshold for transition High to Low | VINL                                           |                                                                                                | 0.8 | 1.1  | -   | V    |

| Input voltage threshold hysteresis                 | V <sub>IN_HYST</sub>                           |                                                                                                | 0.4 | 8.0  | 1.2 | V    |

| Pull down Resistance on VIA,VIB,DIS and PWM        | R <sub>PD</sub>                                |                                                                                                | 100 | 170  | 280 | kΩ   |

| DEAD-TIME                                          |                                                |                                                                                                |     |      |     |      |

| Dead time                                          | t <sub>DT</sub>                                | $R_{DTC} = 20 \text{ k}\Omega$                                                                 | 160 | 200  | 240 | ns   |

| OUTPUTS (OUTA, OUTB)                               |                                                |                                                                                                |     |      |     |      |

| Peak sourcing output current                       | ISRC_PK                                        | $C_{VDD}$ = 10 $\mu$ F, $C_{LOAD}$ = 0.18 $\mu$ F, $F_{sw}$ = 1 kHz, bench measurement         |     | 4.0  |     | Α    |

| Peak sinking output current                        | I <sub>SNK_PK</sub>                            | $C_{VDD}$ = 10 $\mu$ F, $C_{LOAD}$ = 0.18 $\mu$ F, $F_{sw}$ = 1 kHz, bench measurement         |     | -6.0 |     | Α    |

| Output voltage at high state                       | V <sub>OHA_ERR</sub> /<br>V <sub>OHB_ERR</sub> | V <sub>VDDA</sub> , V <sub>VDDB</sub> = 12 V, I <sub>OUT</sub> = -10 mA, T <sub>A</sub> = 25°C |     | 13   | 24  | mV   |

DATA SHEET HP3600

| Parameter                                                                 | Symbol                             | Conditions                                                                                    | Min | Тур      | Max | Unit  |

|---------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------|-----|----------|-----|-------|

| Output voltage at low state                                               | V <sub>OLA</sub> /V <sub>OLB</sub> | V <sub>VDDA</sub> , V <sub>VDDB</sub> = 12 V, I <sub>OUT</sub> = 10 mA, T <sub>A</sub> = 25°C |     | 7        | 14  | mV    |

| Switching Characteristics                                                 |                                    |                                                                                               |     |          |     |       |

| Output rise time, 10% to 90% measured points                              | t <sub>RISE</sub>                  | С <sub>ОUТ</sub> = 1.0 nF, F <sub>sw</sub> = 1 kHz, 50%                                       |     | 6        | 15  | ns    |

| Output fall time, 90% to 10% measured points                              | t <sub>FALL</sub>                  | duty cycle                                                                                    |     | 4        | 10  | ns    |

| Minimum pulse width                                                       | t <sub>PWmin</sub>                 | Output off for less than minimum, Cout = 0 pF                                                 |     | V        | 15  | ns    |

| INx/DIS to OUTx turn-on / off propagation delay                           | t <sub>PD_OFF</sub>                |                                                                                               |     | 48       | 68  | ns    |

| Pulse width distortion  tpD_ON - tpD_OFF                                  | t <sub>PWD</sub>                   |                                                                                               | ×?  | <b>)</b> | 20  | ns    |

| Propagation delays matching between V <sub>OUTA</sub> , V <sub>OUTB</sub> | t <sub>DM</sub>                    | F <sub>sw</sub> = 100 kHz                                                                     | 3   |          | 18  | ns    |

| VDDI UVLO Recovery Delay                                                  | tuvlo_rec_v                        |                                                                                               |     | 15       | 100 | μs    |

| VDDA, VDDB UVLO Recovery<br>Delay                                         | tuvlo_rec_v<br>dda/b               |                                                                                               |     | 20       | 30  | μs    |

| High Level Static Common<br>Mode Transient Immunity                       | СМТІн                              | V <sub>CM</sub> =1000V, T <sub>A</sub> =25°C                                                  | 150 | 200      |     | kV/µs |

| Low Level Static Common Mode Transient Immunity                           | CMTI∟                              | V <sub>CM</sub> =1000V, T <sub>A</sub> =25°C                                                  | 150 | 200      |     | kV/µs |

Table 0-2 SAFETY RELATED CERTIFICATIONS (SOP16)

| VDE                          | UL                                          | CQC                                                       | TUV                                                               |

|------------------------------|---------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------|

| DIN VDE 0884-17: 2021-<br>10 | UL 1577 component recognition program       | Certified according to GB4943.1-2022                      | Certified according to IEC 61010-1: 2010+A1 and IEC 62368-1: 2018 |

| Reinforced Insulation        | Single protection, 3000<br>V <sub>RMS</sub> | Reinforced insulation, Altitude ≤ 5000m, ⊤ropical climate | 3000Vrms basic<br>insulation, 400Vrms<br>maximum working voltage  |

| Certification Pending        | Certification Pending                       | Certification Pending                                     | Certification Pending                                             |

### ABSOLUTE MAXIMUM RATINGS

### Table 0-1.

| Parameter                                    | Rating                             |

|----------------------------------------------|------------------------------------|

| Output supply voltage                        |                                    |

| VDDA, VDDB, continuous                       | -0.3 to 35 V                       |

| Output voltage                               |                                    |

| OUTA to GNDA, OUTB to GNDB, continuous       | -0.3 V to V <sub>DDx</sub> + 0.3 V |

| OUTA, OUTB, transient for 200 ns             | -3 V to V <sub>DDx</sub> + 1.5 V   |

| Input supply voltage                         |                                    |

| VDDI to GND                                  | -0.3 to 20 V                       |

| Input voltage                                |                                    |

| INA, INB, DIS, DTC                           | -7 to V <sub>DDI</sub> + 0.3 V     |

| Output Channel to Channel internal isolation | 1500 V                             |

| Junction temperature range                   | -40 °C to +150 °C                  |

| Storage Temperature                          | -65 °C to 150 °C                   |

| Soldering conditions                         | JEDEC J-STD-020                    |

| Electrostatic Discharge (ESD)                |                                    |

| Human body model                             | 3000 V                             |

| Changed device model                         | 2000 V                             |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

$\theta_{JC}$  is the junction to case thermal resistance.

Table 0-2. Thermal Resistance

| Package Type |  | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|--------------|--|-----------------|-----------------|------|

| SOP-16       |  | 150             | 38              | °C/W |

### **ESD CAUTION**

### Electrostatic Discharge Sensitive Device.

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

DATA SHEET HP3600

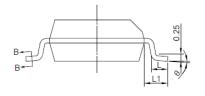

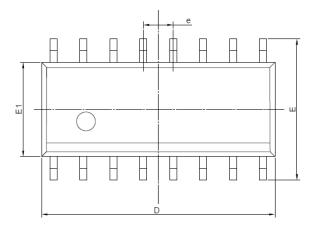

## PACKAGE OUTLINE DIMENSIONS

| Dimension | MIN  | NOM   | MAX  |  |  |  |

|-----------|------|-------|------|--|--|--|

| Α         | -    | -     | 1.75 |  |  |  |

| A1        | 0.1  | -     | 0.25 |  |  |  |

| A2        | 1.25 | -     | -    |  |  |  |

| L         | 0.4  | 0.835 | 1.27 |  |  |  |

| L1        | -    | 1.04  | -    |  |  |  |

| θ         | 0    | -     | 8    |  |  |  |

| b         | 0.31 | -     | 0.51 |  |  |  |

| b1        | 0.28 | -     | 0.48 |  |  |  |

| С         | 0.1  | -     | 0.25 |  |  |  |

| c1        | 0.1  | -     | 0.25 |  |  |  |

| D         | 9.8  | 9.9   | 10   |  |  |  |

| E         | 5.8  | 6     | 6.2  |  |  |  |

| E1        | 3.8  | 3.9   | 4    |  |  |  |

| е         | 1.02 | 1.27  | 1.52 |  |  |  |

| Unit : mm |      |       |      |  |  |  |

Figure 4. SOP-16 Package Outline Dimensions

### **ORDERING GUIDE**

| Device ID          | Package Type | Tj Temp (℃) | Package Option | Package Qty |

|--------------------|--------------|-------------|----------------|-------------|

| HP3600-AB001-SP16R | SOP-16       | -40 ~ 150   | T&R            | 3000ea      |

DATA SHEET HP3600

### **IMPORTANT NOTICE**

Hynetek Semiconductor Co., Ltd. and its subsidiaries (Hynetek) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to Hynetek's terms and conditions of sale supplied at the time of order acknowledgment.

Hynetek warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in Hynetek's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent Hynetek deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

Hynetek assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using Hynetek components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Hynetek does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which Hynetek components or services are used. Information published by Hynetek regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from Hynetek under the patents or other intellectual property of Hynetek.

Reproduction of significant portions of Hynetek information in Hynetek data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Hynetek is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of Hynetek components or services with statements different from or beyond the parameters stated by Hynetek for that component or service voids all express and any implied warranties for the associated Hynetek component or service and is an unfair and deceptive business practice.

Hynetek is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of Hynetek components in its applications, notwithstanding any applications-related information or support that may be provided by Hynetek. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify Hynetek and its representatives against any damages arising out of the use of any Hynetek components in safety-critical applications.

In some cases, Hynetek components may be promoted specifically to facilitate safety-related applications. With such components, Hynetek's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No Hynetek components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those Hynetek components which Hynetek has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of Hynetek components which have not been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

Hynetek has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, Hynetek will not be responsible for any failure to meet ISO/TS16949.

Please refer to below URL for other products and solutions of Hynetek Semiconductor Co., Ltd.

©2022 Hynetek Semiconductor Co., Ltd. All rights reserved.

Trademarks and registered trademarks are the property of their respective owners.

www.hynetek.com