# **GENERAL DESCRIPITION**

MX1210R is a highly integrated current mode PWM controller, optimized for high performance, low standby power consumption and wide output voltage range PD adapter solutions. The circuit is as well compatible with cost effective offline flyback converter applications covering a wide output range.

At full loading, the IC operates in fixed frequency mode. When the loading goes low, it operates in Green mode for high power conversion efficiency can be achieved in the whole loading range.

MX1210R offers complete protection coverage including cycle-by-cycle current limiting (OCP), over load protection (OLP), over temperature protection (OTP), VDD over voltage protection (VDD OVP). Excellent EMI performance is achieved with MAXIN proprietary frequency shuffling technique. The tone energy at below 22kHz is minimized to avoid audio noise during operation.

MX1210R is offered in SOT23-6 package.

# **Applications**

Battery chargers

PD adapters

Wide output range adapters

Set-Top Box power supply

# **FEATURES**

- ♦ Multi-Mode Operation

- •65kHz fixed frequency mode @ Full Load

- •Middle load and light load@ Green mode

- •Burst Mode @ Light Load and No Load

- ◆Adaptive loop gain compensation with Iovp current detection

- ♦Ultra low operation current at light and no load

- ♦Internal OCP compensation for universal line voltage

- ◆Extend burst mode control for improved efficiency and low standby power

- ♦Power on soft start reducing MOSFET VDS stress

- ♦Built in leading edge blanking function

- ♦Frequency shuffling for EMI

- ♦Audio noise free operation

- ♦Comprehensive protection coverage

- •VDD under voltage lockout with hysteresis (UVLO)

- •Cycle-by-cycle over current protection (OCP) with auto recovery

- •External over temperature protection (EXT\_OTP)

- Over load protection

- •VDD over voltage protection

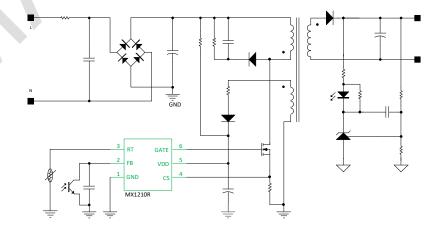

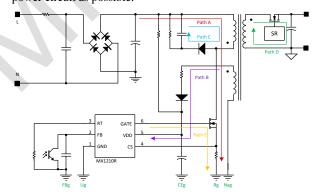

# **Typical Application**

# High Performance Multi-mode PWM Controller

# **General information**

## **Ordering information**

| Part Number | Description                 |

|-------------|-----------------------------|

| MX1210R     | SOT23-6, Halogen-free, RoHS |

## Package dissipation rating

| Package | RθJA (°C/W) |

|---------|-------------|

| SOT23-6 | 200         |

# **Absolute maximum ratings**

| Parameter                            | Value        |

|--------------------------------------|--------------|

| VDD DC supply voltage                | 60V          |

| FB input voltage                     | -0.3 to 7V   |

| CS input voltage                     | -0.3 to 7V   |

| RT input voltage                     | -0.3 to 7V   |

| Junction temperature T <sub>J</sub>  | -40 to 150°C |

| Ambient temperature T <sub>A</sub>   | -40 to 85℃   |

| Storage temperature T <sub>STG</sub> | -55 to 150°C |

| ESD(HBM)                             | ±2.0kV       |

| Leading temperature                  | 260°C        |

| (soldering, 10secs)                  | 200 C        |

Note: stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

## **Recommended operating condition**

| Symbol | Parameter                  | Range |  |

|--------|----------------------------|-------|--|

| VDD    | VDD voltage                |       |  |

| PD     | Power dissipation @TA=25°C | 0.59W |  |

# **Terminal assignments**

| PIN  | PIN  |                                                 |

|------|------|-------------------------------------------------|

| NO.  | name | Description                                     |

| 1    | GND  | Ground pin.                                     |

|      |      | Feedback input pin. The PWM duty cycle is       |

| 2    | FB   | determined by voltage level into this pin and   |

|      |      | current-sense signal CS pin.                    |

| 3 RT |      | Connect a NTC between this pin and ground to    |

|      |      | achieve OTP protection function. Let this pin   |

|      |      | float to disable the latch protection.          |

| 4    | CS   | Current sense pin, connect resistors to ground. |

| 5    | VDD  | Power supply.                                   |

| 6    | GATE | Gate driver for external MOSFET.                |

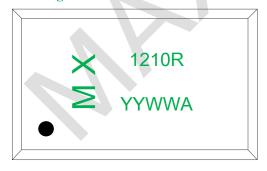

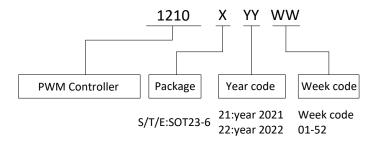

## **Marking information**

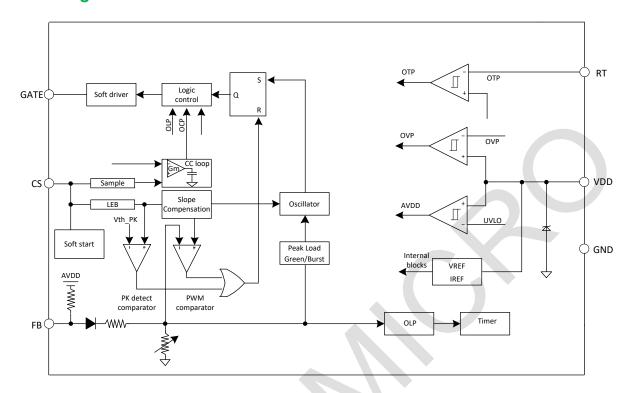

# **Block Diagram**

# **Electrical characteristics**

(TA=25°C, VDD=18V, unless otherwise noted)

| Symbol                   | Parameter                                                        | Test condition                                      | Min   | Тур.  | Max   | Unit |

|--------------------------|------------------------------------------------------------------|-----------------------------------------------------|-------|-------|-------|------|

| VDD supply v             | voltage                                                          |                                                     |       |       |       |      |

| I startup                | VDD startup current                                              | VDD=UVLO_OFF-1V                                     |       | 5.0   | 20.0  | μΑ   |

| I_VDD                    | VDD normal operation current                                     | V <sub>FB</sub> =3V                                 |       | 2.8   | 3.3   | mA   |

| I_ Burst                 | Burst mode operation current                                     | VFB=0.5V                                            |       | 0.45  | 0.48  | mA   |

| UVLO_ON                  | VDD under voltage lockout enter                                  |                                                     | 6.7   | 7.2   | 7.7   | V    |

| UVLO_OFF                 | VDD under voltage lockout exit                                   |                                                     | 15.5  | 16.5  | 17.5  | V    |

| V_Pull/up                | Pull-up PMOS active                                              |                                                     |       | 10    |       | V    |

| V <sub>DD_OVP</sub>      | Over voltage protection voltage                                  | FB=3V, VDD ramp up until gate clock is off          | 50.0  | 52.0  | 54.0  | V    |

| V_Latch                  | Latch release voltage                                            | External OTP/VDD_OVP                                |       | 4.8   |       | V    |

| T_recovery               | Restart time for auto-recovery protection                        | Other protection                                    |       | 1.4   |       | s    |

| FB pin – Feed            | back input section                                               |                                                     |       |       |       |      |

| V <sub>FB_Open</sub>     | FB open loop voltage                                             |                                                     |       | 5.1   |       | V    |

| Avcs                     | PWM input gain ΔVFB/ΔVCS                                         |                                                     |       | 3.3   |       | V/V  |

| D_MAX                    | Max duty cycle @ VDD=18V, VFB=3V, VCS=0.3V                       |                                                     | 70    |       | 90    | %    |

| I <sub>FB_short</sub>    | FB pin short circuit current                                     | Current for short FB to GND                         |       | 250   |       | μΑ   |

| V <sub>FB_green</sub>    | The threshold enters green mode                                  |                                                     |       | 2.05  |       | V    |

| V <sub>REF_burst_H</sub> | The threshold exits burst mode                                   |                                                     |       | 1.2   |       | V    |

| V <sub>REF_burst_L</sub> | The threshold enters burst mode                                  |                                                     |       | 1.1   |       | V    |

| V <sub>FB_OLP</sub>      | Over load protection                                             |                                                     | 4.0   | 4.4   | 4.8   | V    |

| T <sub>D_OLP</sub>       | Over load debounce time                                          |                                                     |       | 60    |       | ms   |

| R <sub>FB_IN</sub>       | Input impedance                                                  |                                                     |       | 20    |       | kΩ   |

| CS pin – Curr            | ent sense input                                                  |                                                     |       |       |       |      |

| T <sub>CS</sub> _SST     | Soft start time of CS threshold                                  |                                                     |       | 4.0   |       | ms   |

| T_blanking               | Leading edge blanking time                                       |                                                     |       | 300   |       | ns   |

| T <sub>D_</sub> oc       | Over current detection and delay                                 | From over current occurs till gate driver turns off |       | 90    |       | ns   |

| Vcs_pk                   | Internal current limiting threshold voltage with zero duty cycle |                                                     | 0.492 | 0.500 | 0.508 | V    |

| V <sub>CS_PKclamp</sub>  | CS voltage clamper                                               |                                                     |       | 0.715 |       | V    |

| V <sub>CS_SRST</sub>     | Secondary rectifier diode short protection threshold voltage     |                                                     | 1.1   | 1.2   | 1.3   | V    |

| Oscillator               |                                                                  |                                                     |       |       |       |      |

| Fosc_nom                 | Normal frequency of high output voltage                          | VDD=15V, FB=3V, CS=0V                               | 60    | 65    | 70    | kHz  |

| Fosc_jt                  | Frequency jittering                                              |                                                     | -7    |       | +7    | %    |

|                          |                                                                  |                                                     |       |       |       |      |

# High Performance Multi-mode PWM Controller

| Fosc_shuffling          | Shuffling frequency                                |      | 240  |      | Hz           |

|-------------------------|----------------------------------------------------|------|------|------|--------------|

| Fosc_temp               | Frequency temperature stability                    |      | 1.0  |      | %            |

| Fosc_vdd                | Frequency VDD voltage stability                    |      | 1.0  |      | %            |

| Fosc_burst              | Burst mode frequency                               |      | 22   |      | kHz          |

| Gate driver             |                                                    |      |      |      |              |

| $V_{GL}$                | Gate low voltage @ VDD=15V, Io=20mA                |      |      | 1.0  | V            |

| $V_{GH}$                | Gate high voltage @ VDD=15V, Io=20mA               | 8.0  |      |      | V            |

| V <sub>G_clamping</sub> | Gate clamp voltage                                 |      | 11.5 |      | V            |

| T_rise                  | Gate voltage rising time 1.2V ~ 10.8V @ CL=1000pF  |      | 200  |      | ns           |

| T_fall                  | Gate voltage falling time 10.8V ~ 1.2V @ CL=1000pF |      | 35   |      | ns           |

| RT pin – Exte           | rnal temperature protect                           |      |      |      |              |

| V <sub>RT_Open</sub>    | RT open loop voltage                               |      | 2    |      | V            |

| V <sub>RT_TH</sub>      | Threshold voltage for OTP                          | 0.95 | 1    | 1.05 | V            |

| $I_{RT}$                | Output current of RT pin                           | 39.5 | 40   | 40.5 | uA           |

| T <sub>D_OTP</sub>      | Thermal protect debounce time                      |      | 32   |      | Cycle        |

| Internal OTP            |                                                    |      |      |      |              |

| OTP_in                  |                                                    |      | 155  |      | $^{\circ}$ C |

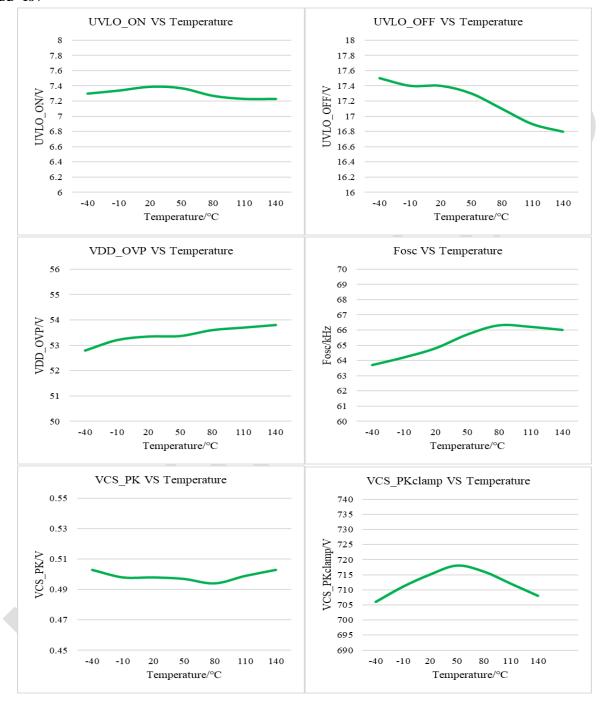

# **Characteristic plots**

## VDD=18V

# Operation description

MX1210R is a highly integrated current mode PWM controller, optimized for high performance, low standby power consumption and wide output voltage range PD adapter solutions. Together with PD secondary controller. The power circuit is as well compatible with cost effective offline flyback converter applications covering a wide output range. The extended burst mode control greatly reduces the standby power consumption and helps the design easily to meet the international power conservation requirements.

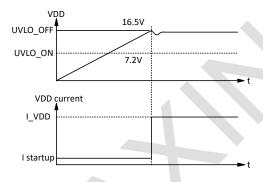

#### Startup and Internal under voltage lockout

Startup current of MX1210R is designed to be very low so that VDD could be charged up to UVLO\_OFF threshold level and device starts up quickly. A large value startup resistor can therefore be used to minimize the power loss yet achieve a reliable startup in application.

To optimize power efficiency, startup resistors can be added to the AC line, which not only can reduce power loss but can reset latched mode protections faster.

Fig1 startup current timing

## **Operation current**

The typical operating current of MX1210R is 2.8mA. Good efficiency is achieved with this low operating current together with the extended burst mode control features.

## Soft start

MX1210R features an internal 4ms soft start to soften the electrical stress occurring in the power supply during startup. It is activated during the power in sequence. As soon as VDD reaches UVLO\_OFF, the CS peak voltage is gradually increased from 0V to the maximum level. Every restart up begins with a soft start.

#### Adaptive loop gain compensation

With MAXIN proprietary technology, an adaptive loop

compensation is implemented to ensure the system loop stability for wide output voltage range according to I\_OVP current detection.

#### Frequency shuffling for EMI improvement

The frequency shuffling is implemented in MX1210R. The oscillation frequency is modulated so that the tone energy is spread out. The spread spectrum minimizes the system design.

#### **Extended burst mode operation**

At light load or no-load condition, most of the power dissipation in a switching mode power supply is from switching loss of the MOSFET, the core loss of the transformer and the loss of the snubber circuit. The magnitude of power loss is in proportion to the switching frequency. Lower switching frequency leads to the reduction on the power loss and thus conserves the energy.

The switching frequency is internally adjusted at light load or no-load condition. The switching frequency reduces at light load or no load to improve the conversion efficiency. At light load or no-load condition, the FB input drops below  $V_{REF\_burst\_L}$  and system enters burst mode. The gate drive output switches when FB input rise back to  $V_{REF\_burst\_H}$ . Otherwise the gate drive remains at off state to minimize the switching loss and reduces the standby power consumption to the greatest extend.

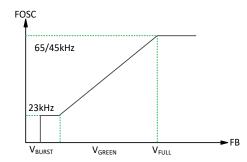

#### Oscillator operation

During the full load power operation, MX1210R operates at 65kHz fixed frequency of high output voltage  $(V_{FB}>2.05V$  typical). The efficiency and system cost are controlled at an optimal level. At light load, MX1210R enters the light load mode, where the output current is reduced. The switching losses are reduced by lowering the switching frequency.

Fig2 FB voltage vs frequency

#### Current sensing and leading-edge blanking

Cycle by cycle current limiting is offered in MX1210R

current mode PWM control. The switch current is detected by a sense resistor into CS pin. At internal leading-edge blanking circuit chops off the sensed voltage spike at initial internal power MOSFET on state due to snubber diode reverse recovery and surge gate current of power MOSFET. The current limiting comparator is disabled and cannot turn off the power MOSFET during the blanking period. The PWM duty cycle is determined by the current sense voltage and the FB voltage.

#### Internal synchronized slope compensation

Built-in slope compensation circuit adds voltage ramp into the current sense input voltage for PWM generation. This greatly improves the close loop stability at CCM and prevents the sub-harmonic oscillation and thus reduces the

#### **Protection controls**

Good power supply system reliability is achieved with auto recovery protection features including OCP, Under Voltage Lockout on VDD (UVLO), and latched shutdown features including external Over Temperature Protection, VDD Over Voltage Protection (VDD\_OVP).

With MAXIN proprietary technology, the OCP is line voltage compensated to achieve constant output OCP limit over the universal input voltage range and its dependency on primary inductance and frequency is removed.

At overload condition when FB pin input voltage exceeds power limit threshold value for more than Td\_OLP, control circuit reacts to shut down the converter. It restarts when VDD voltage drops below UVLO limit. For protection with latched shut down mode, control circuit shuts down (latch) the power MOSFET when an over temperature condition or over voltage condition is detected until VDD drops below 4.8V (Latch release voltage), and the device enters power on restart-up sequence thereafter.

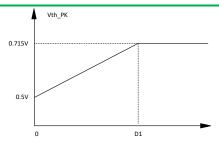

#### Over current protection

MX1210R provides an adaptive cycle-by-cycle OCP compensation method varying with gate on duty cycle in Figure 6. The maximum cycle-by-cycle OCP threshold voltage, Vth\_PK, is 0.715V.

At PWM off state, 100uA current flows out of CS pin to generate a voltage through R1 and Rsense. The final CS peak clamping voltage threshold is adjusted by the added voltage.

$$V_{_{CS\_PKclamp}} = V_{_{CS\_PK}} + R1 \cdot 100uA$$

Figure 5 cycle by cycle OCP compensation

#### Pin floating and short protection

MX1210R provides pin floating protection for all the pins and pin short protection for adjacent pins. In the cases when a pin is floating or two adjacent pins are shorted, Gate switching is disabled.

## **On-Chip OTP - Auto Recovery**

An internal OTP circuit is embedded inside the MX1210R to provide the worst-case protection for this controller. When the chip temperature rises higher than the trip OTP level, the output will be disabled until the chip is cooled down below the hysteresis window.

#### External over temperature latch mode protection

The OTP circuit is implemented to sense whether there is any hot-spot of power circuit like power MOSFET or output rectifier. Typically, an NTC is recommended to connect with OTP pin. The NTC resistance will decrease as the device or ambient is in high temperature. The relationship is described as below:

$$V_{OTP} = 40 \mu A \times R_{NTC}$$

When V<sub>OTP</sub><V<sub>OTP-TH</sub> (typical 1.05V), it will trigger the protection to shut down the gate output and latch off the power supply. The controller will remain latched unless the VCC drops below 7V (power down reset) and VCC stays on UVLO condition. Two conditions are required to restart the IC successfully, to cool down the circuit so that the NTC resistance will increase and to raise V<sub>OTP</sub> above 0.95V. Then, recycle the AC main power.

### Feedback resistors

To enhance efficiency at light load, the power loss caused by the feedback resistors, in parallel with the opto-coupler as shown in Figure7, must be reduced. Since the current through the feedback resistor is very small, a shunt regulator, especially with its minimum regulated current, should be carefully chosen to ensure that the shunt regulator can still regulate the output voltage at such a small cathode current.

Figure7 Feedback resistor

#### Driver

The power MOSFET is driven by a dedicated gate driver for power switch control. Too weak the gate driver strength results in higher conduction and switch loss of MOSFET while too strong gate driver strength results the compromise

A good tradeoff is achieved through the built-in totem pole gate design with right output strength and dead time control. The low idle loss and good EMI system design is easier to achieve with this dedicated control scheme.

#### **Layout considerations**

A proper PCB layout can alleviate unknown noise interference and EMI emission in a switch mode power supply. It is recommended to follow the following PCB layout guidelines when a switch mode power supply is to be designed:

- ♦The current path A, starting from the bulk capacitor, through the transformer, the MOSFET, the resistor Rcs and back to the bulk capacitor, is a high frequency and high current loop. This path should be kept as small as possible to decrease noise coupling and kept away from other low voltage traces, such as control paths.

- ♦The path B, starting from the auxiliary winding, through the resistor, the diode, and VDD capacitor to the VDD pin, is also recommended to be as short as possible. Besides, the VDD capacitor should place as close to the VDD pin as possible.

- ♦The path C, from the RCD snubber circuit to the MOSFET should also be kept short as it is also a loop with high frequency.

- ♦The path D, starting from the second winding, through the rectifier diode, the rectifier capacitor, back to second winding, is also recommended to be as short as possible. In

- High Performance Multi-mode PWM Controller

- addition, the copper areas at the anode and cathode of the diode must be large enough to ease sinking heat from the diode.

- ♦The path E which is from the GATE pin, through the MOSFET, the current sense resistor and back to the MX1210R ground should be kept as small as possible.

- ♦The ground traces of the bulk capacitor Cg, the current sense resistor Rg, the VDD capacitor CEg, the auxiliary winding Nag, and the power circuit Ug, should be separated to reduce noise, output ripple and EMI emission. The ground traces of the auxiliary winding Na and the MX1210R are connected together at the VDD capacitor ground. Then the connected ground trace goes through the VDD capacitor, the current sense ground, and to the bulk capacitor ground in turn. The area of the bulk capacitor ground trace should be large enough.

- ♦The bypass capacitor should be placed as closed to the power circuit as possible.

Figure8 PCB layout guide

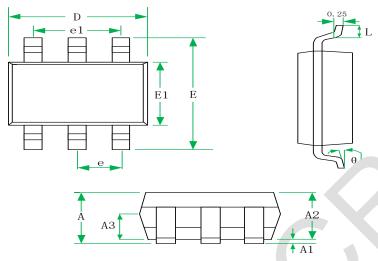

# **Package information**

| SYMBOL | MILLIMETERS |         |      | INCHES   |       |        |  |

|--------|-------------|---------|------|----------|-------|--------|--|

| SIMBOL | MIN         | NOM     | MAX  | MIN      | NOM   | MAX    |  |

| A      |             |         |      |          |       |        |  |

| A1     | 0.04        |         | 0.15 | 0.0016   |       | 0.0059 |  |

| A2     | 1.00        | 1.10    | 1.20 | 0.039    | 0.043 | 0.047  |  |

| A3     | 0.55        | 0.65    | 0.75 | 0.022    | 0.026 | 0.029  |  |

| D      | 2.72        | 2.92    | 3.12 | 0.107    | 0.115 | 0.123  |  |

| Е      | 2.60        | 2.80    | 3.00 | 0.102    | 0.110 | 0.118  |  |

| E1     | 1.40        | 1.60    | 1.80 | 0.055    | 0.063 | 0.071  |  |

| e      |             | 0.95BSC | 1    | 0.037BSC |       |        |  |

| e1     | 1.90BSC     |         |      | 0.074BSC |       |        |  |

| L      | 0.30        |         | 0.60 | 0.012    |       | 0.024  |  |

| θ      | 0           |         | 8°   | 0        |       | 8°     |  |

SOT23-6 for MX1210R

# **Restrictions on Product Use**

- MAXIN micro is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing MAXIN products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such MAXIN products could cause loss of human life, bodily injury or damage to property.

- ♦ In developing your designs, please ensure that MAXIN products are used within specified operating ranges as set forth in the most recent MAXIN products specifications.

- ◆ The information contained herein is subject to change without notice.