## CCi8332

## 隔离双通道栅极驱动器

## 特性

- ◆ 隔离驱动可配置为两个独立的单侧驱动器或半桥驱动器

- ◆ 输入侧  $V_{CC}$  的电源电压: 3V ~ 5.5V

- ◆ 输出驱动侧  $V_{DDA}/V_{DDB}$  电源电压: 可接受最大 30V

- ◆  $V_{CC}$ 、 $V_{DDA}$ 、 $V_{DDB}$  均带有 UVLO 控制

- ◆ 具有 4A 峰值拉电流和 6A 峰值灌电流

- ◆ 高共模瞬态抑制 (CMTI): 典型值 150V/ns

- ◆ 40ns 典型传播延迟

- ◆ 7ns 最大脉宽失真

- ◆ 死区时间可通过 DT 引脚配置

- ◆ 可接收最小 30ns 的窄脉冲

- ◆ 工作温度: -40°C ~ 125°C

- ◆ 封装: SOP16W、SOP14W 和 LGA 4x4 三种封装

- ◆ ESD ( HBM )  $\pm 3$  kV, ESD ( CDM )  $\pm 1.5$  kV, LU  $\pm 200$  mA

## 应用

- ◆ 电机驱动器

- ◆ 太阳能逆变器

- ◆ UPS 和电池充电器

- ◆ 隔离 IGBT、功率 MOSFET 栅极驱动

## 产品渲染图

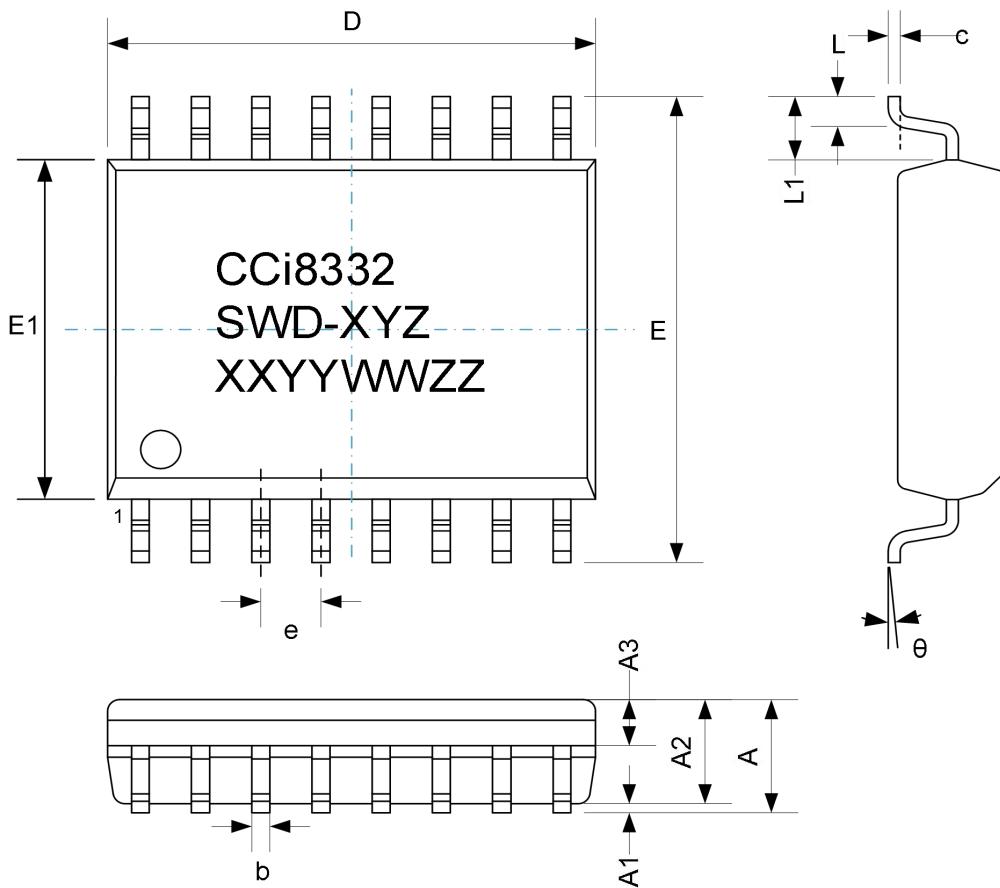

SOP16W 封装

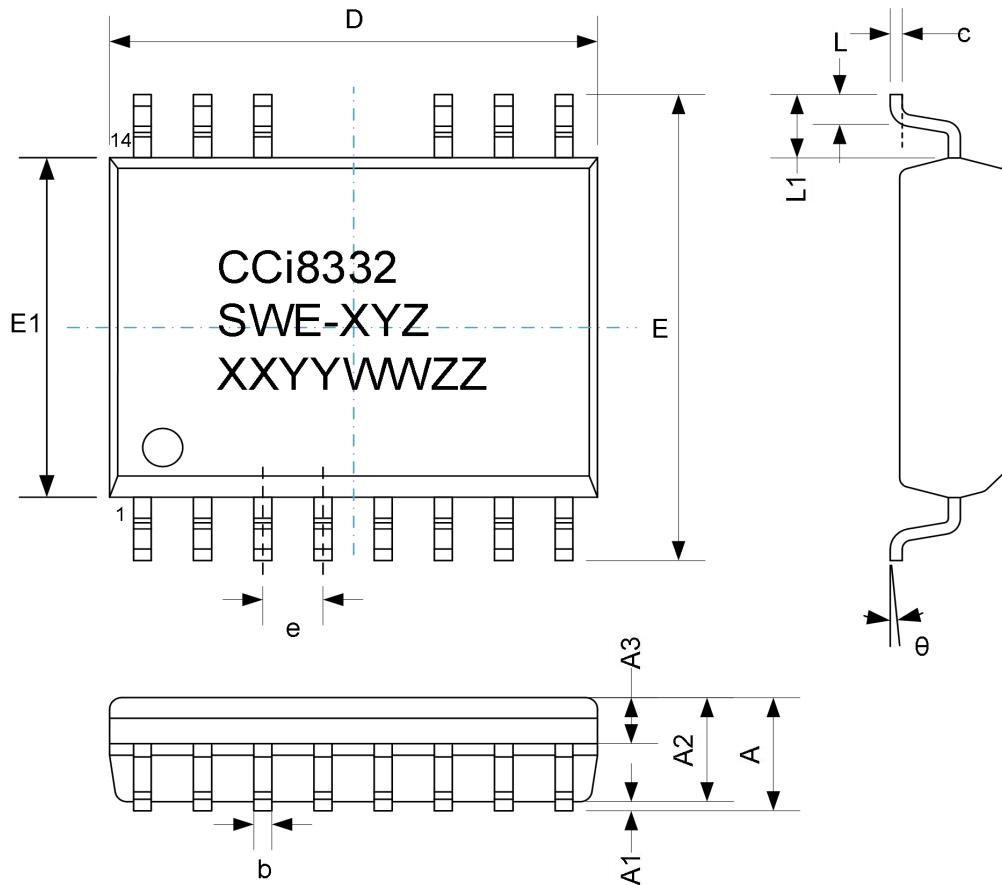

SOP14W 封装

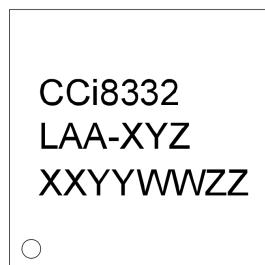

LGA 4x4 封装—正面

LGA 4x4 封装—背面

## 概述

CCi8332 是一款隔离双通道栅极驱动器，具有 4A 峰值拉电流和 6A 峰值灌电流。该驱动器可驱动 IGBT 和 SiC，具有 40ns 传播延迟和 7ns 最大脉宽失真。输入侧通过一个 5.7kV<sub>RMS</sub> 增强型隔离层与两个输出驱动器隔离，两侧之间的共模瞬态抑制 (CMTI) 的典型值为 150V/ns。两个次级侧驱动器之间的内部功能隔离高达 1500V (DC) 的工作电压。

CCi8332 可配置为两个独立的单侧驱动器或一个死区时间 (DT) 可编程的半桥驱动器。Disable 引脚拉高时，芯片不工作，输出被强拉低；Disable 引脚拉低或悬空时，芯片正常工作<sup>[1]</sup>。

输出驱动侧可接受最大 30V 的  $V_{DDA}/V_{DDB}$  电源电压。输入侧  $V_{CC}$  接受 3V ~ 5.5V 的电源电压。所有电源电压引脚都具有欠压锁定(UVLO)保护功能，在欠压保护状态下，输出引脚  $V_{OA}/V_{OB}$  为低电平。CCi8332 适用于高可靠性、高功率密度和高效率的电源应用系统。

CCi8332 提供 SOP16W、SOP14W 和 LGA 4x4 三种封装，工作温度范围为 -40 至 +125°C，符合 RoHS 相关规定要求。

## 安全认证

- ◆ 符合 UL 1577 标准且长达 1 分钟的 5.7kV<sub>RMS</sub> (SOP16W) 隔离

## 器件信息

| 器件型号       | 封装外形    | 封装尺寸 (典型值)     |

|------------|---------|----------------|

| CCi8332SWD | SOP16W  | 10.30mm×7.50mm |

| CCi8332SWE | SOP14W  | 10.30mm×7.50mm |

| CCi8332LAA | LGA 4x4 | 4.00mm×4.00mm  |

注: [1] 该逻辑状态定义仅适用于 CCi8332XXX-XXL 的版本。

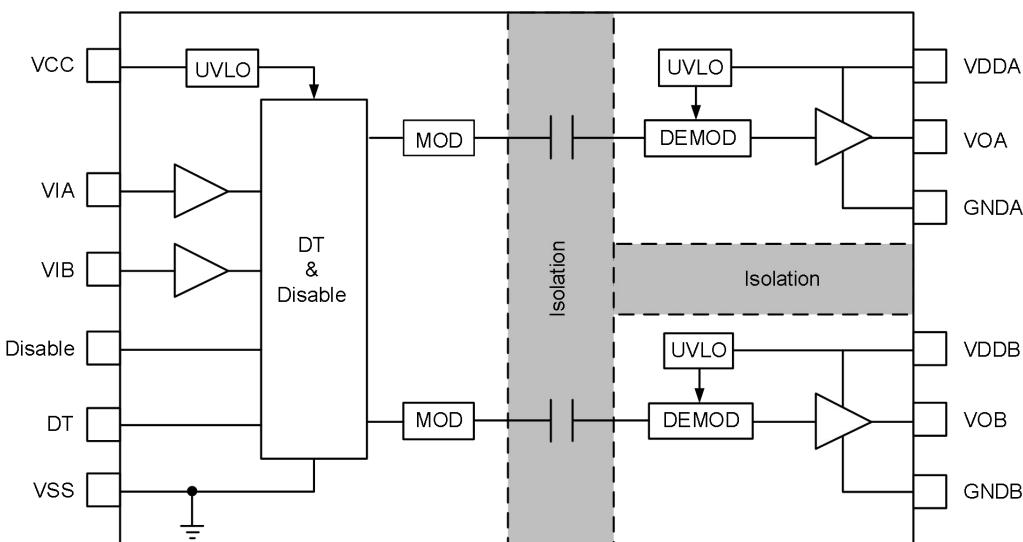

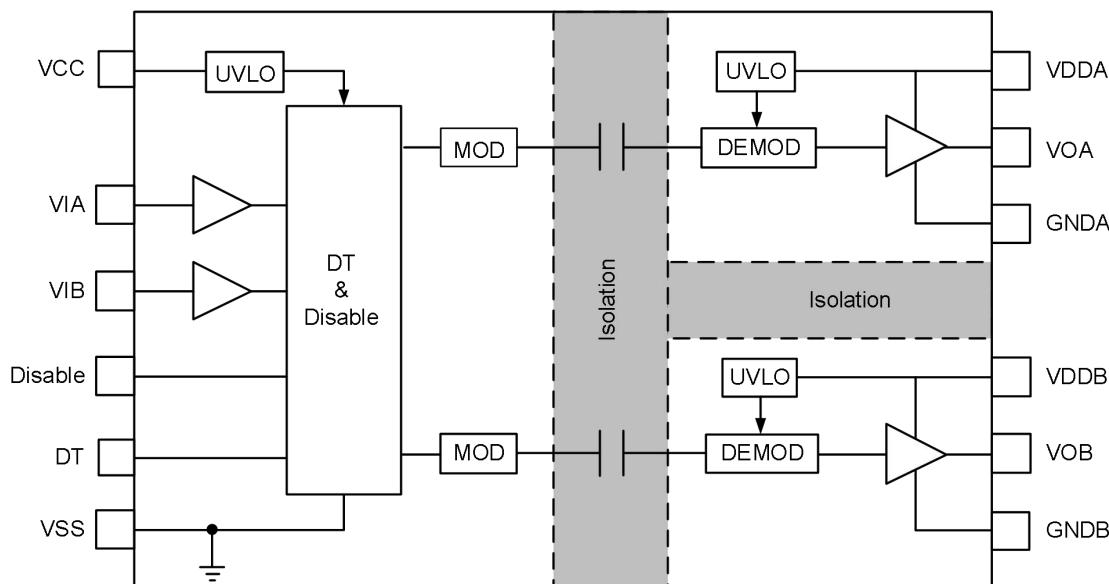

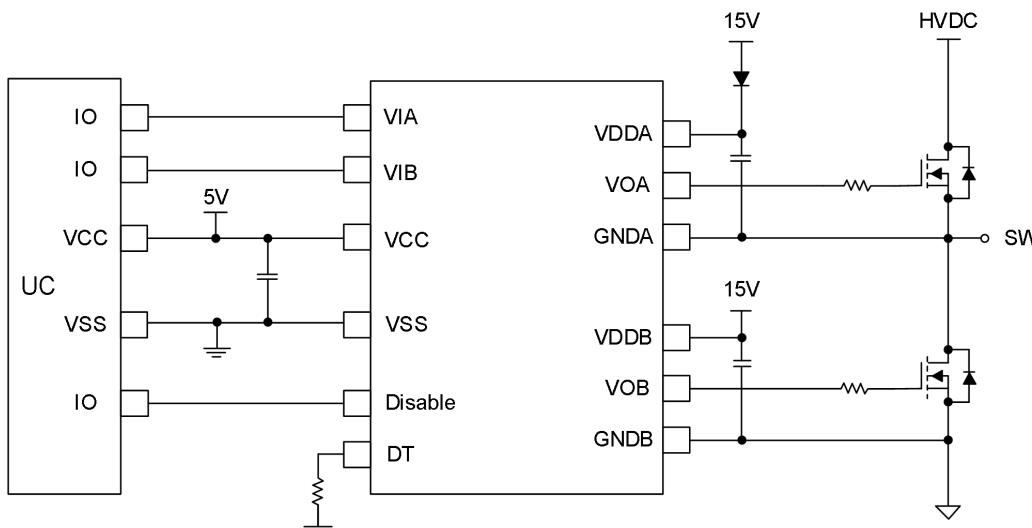

## 功能框图

## 1 产品信息

## 1.1 订购信息

| 产品名称           | 封装外形    | 包装           |

|----------------|---------|--------------|

| CCi8332SWD-2BL | SOP16W  | 编带, 1000 片/卷 |

| CCi8332SWD-2AL | SOP16W  | 编带, 1000 片/卷 |

| CCi8332SWE-2BL | SOP14W  | 编带, 1000 片/卷 |

| CCi8332LAA-2BL | LGA 4x4 | 编带, 5000 片/卷 |

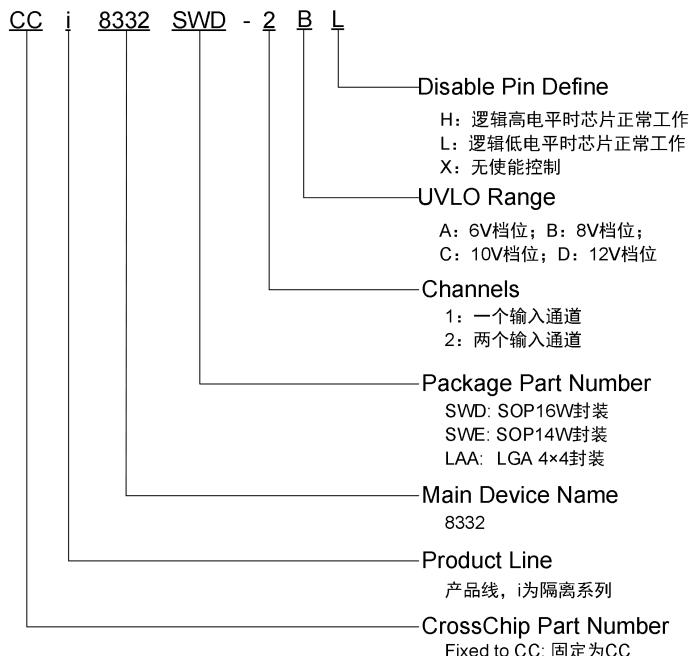

## 1.2 产品名称定义

表 1.1 显示了此系列中每个产品的配置和功能概述。

表 1.1.1 CCi8332 系列概述 (SOP16W 封装)

| 产品             | 配置                      | 防止重叠保护 | 可编程死区时间 | 输入                               | 使能有效电位 | UVLO 电压 |

|----------------|-------------------------|--------|---------|----------------------------------|--------|---------|

| CCi8332SWD-2AH | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 高有效    | 6V      |

| CCi8332SWD-2AL | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 低有效    | 6V      |

| CCi8332SWD-2BH | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 高有效    | 8V      |

| CCi8332SWD-1BH | 半桥驱动                    | -      | √       | PWM                              | 高有效    | 8V      |

| CCi8332SWD-2BL | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 低有效    | 8V      |

| CCi8332SWD-1BL | 半桥驱动                    | -      | √       | PWM                              | 低有效    | 8V      |

| CCi8332SWD-2CH | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 高有效    | 10V     |

| CCi8332SWD-2CL | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 低有效    | 10V     |

| CCi8332SWD-2DH | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 高有效    | 12V     |

| CCi8332SWD-2DL | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 低有效    | 12V     |

表 1.1.2 CCi8332 系列概述 (SOP14W 封装)

| 产品             | 配置                      | 防止重叠保护 | 可编程死区时间 | 输入                               | 使能有效电位 | UVLO 电压 |

|----------------|-------------------------|--------|---------|----------------------------------|--------|---------|

| CCi8332SWE-2AH | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 高有效    | 6V      |

| CCi8332SWE-2AL | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 低有效    | 6V      |

| CCi8332SWE-2BH | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 高有效    | 8V      |

| CCi8332SWE-1BH | 半桥驱动                    | -      | √       | PWM                              | 高有效    | 8V      |

| CCi8332SWE-2BL | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 低有效    | 8V      |

| CCi8332SWE-1BL | 半桥驱动                    | -      | √       | PWM                              | 低有效    | 8V      |

| CCi8332SWE-2CH | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 高有效    | 10V     |

| CCi8332SWE-2CL | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 低有效    | 10V     |

| CCi8332SWE-2DH | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 高有效    | 12V     |

| CCi8332SWE-2DL | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 低有效    | 12V     |

表 1.1.3 CCi8332 系列概述 (LGA 4×4 封装)

| 产品             | 配置                      | 防止重叠保护 | 可编程死区时间 | 输入                               | 使能有效电位 | UVLO 电压 |

|----------------|-------------------------|--------|---------|----------------------------------|--------|---------|

| CCi8332LAA-2BL | DT 可设置: 独立的 2 通道驱动或半桥驱动 | √      | √       | V <sub>IA</sub> 、V <sub>IB</sub> | 低有效    | 8V      |

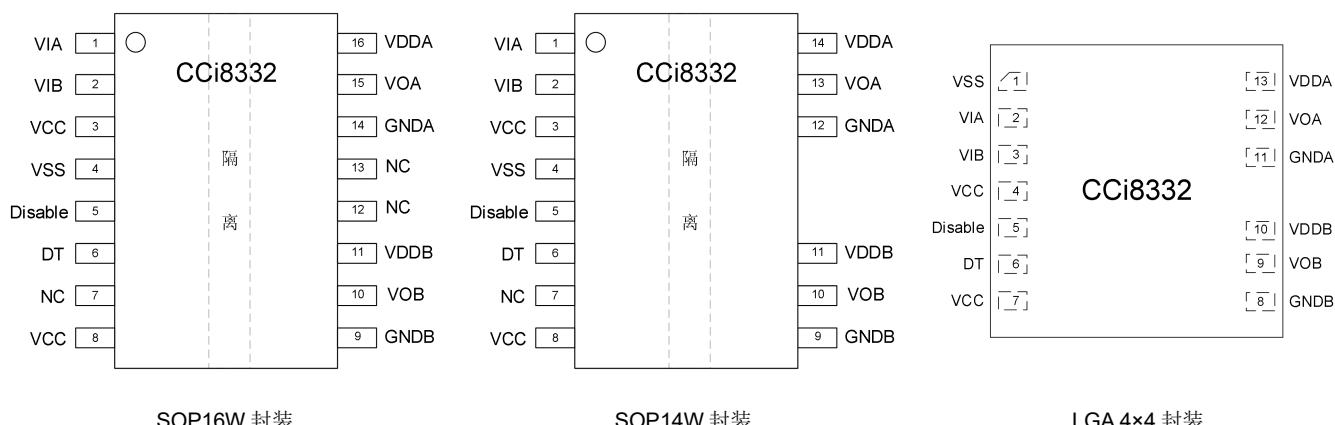

## 2 管脚定义

## 1) 两输入通道

| 名称      | 引脚编号   |        |         | 功能描述                                                                                                                     |

|---------|--------|--------|---------|--------------------------------------------------------------------------------------------------------------------------|

|         | SOP16W | SOP14W | LGA 4x4 |                                                                                                                          |

| VIA     | 1      | 1      | 2       | A 通道输入信号, 带有下拉到地。默认输出 L。                                                                                                 |

| VIB     | 2      | 2      | 3       | B 通道输入信号, 带有下拉到地。默认输出 L。                                                                                                 |

| VCC     | 3      | 3      | 4       | 输入侧电源电压                                                                                                                  |

| VSS     | 4      | 4      | 1       | 输入侧参考地                                                                                                                   |

| Disable | 5      | 5      | 5       | 使能信号, 默认使能状态为低时器件正常工作。<br>Disable 引脚输入高电平时器件不工作, 输出被强拉低; Disable 引脚输入低电平或悬空时器件恢复正常输出; 如果不使用, 建议将该引脚连接至接地。 <sup>[1]</sup> |

| DT      | 6      | 6      | 6       | 死区时间调制 PIN;<br>DT 接 VCC: A、B 通道独立工作;<br>DT 接电阻 (5kΩ~200kΩ) : DT(ns)=10×R <sub>DT</sub> (kΩ)的死区时间, 防止 VOA、VOB 重叠。         |

| NC      | 7      | 7      | -       | 悬空                                                                                                                       |

| VCC     | 8      | 8      | 7       | 输入侧电源电压                                                                                                                  |

| GNDB    | 9      | 9      | 8       | 输出驱动侧 B 通道参考地                                                                                                            |

| VOB     | 10     | 10     | 9       | 输出驱动侧 B 通道的输出                                                                                                            |

| VDBB    | 11     | 11     | 10      | 输出驱动侧 B 通道电源电压                                                                                                           |

| NC      | 12     | -      | -       | 悬空                                                                                                                       |

| NC      | 13     | -      | -       | 悬空                                                                                                                       |

| GNDA    | 14     | 12     | 11      | 输出驱动侧 A 通道参考地                                                                                                            |

| VOA     | 15     | 13     | 12      | 输出驱动侧 A 通道的输出                                                                                                            |

| VDDA    | 16     | 14     | 13      | 输出驱动侧 A 通道电源电压                                                                                                           |

注: [1] 该逻辑状态定义仅适用于 CCi8332XXX-XXL 的版本。

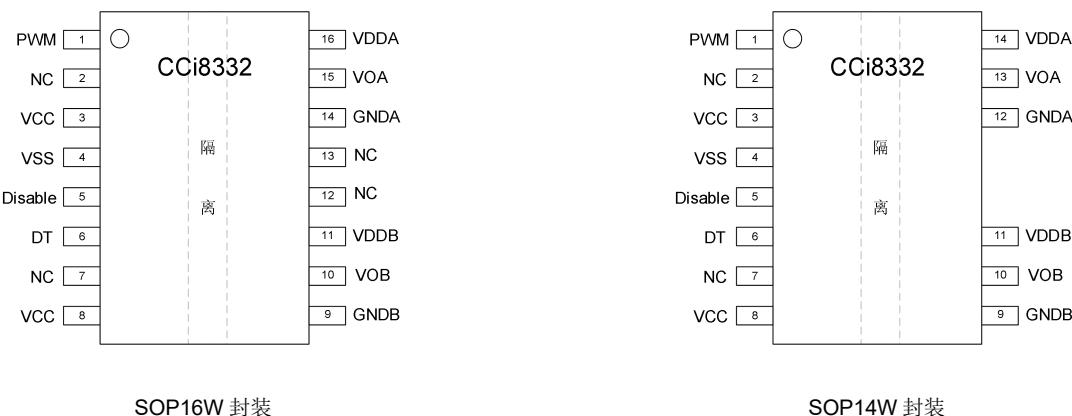

## 2) 单输入通道

| 名称      | 编号     |        | 功能描述                                                                                                                 |

|---------|--------|--------|----------------------------------------------------------------------------------------------------------------------|

|         | SOP16W | SOP14W |                                                                                                                      |

| PWM     | 1      | 1      | PWM 输入信号                                                                                                             |

| NC      | 2      | 2      | 悬空                                                                                                                   |

| VCC     | 3      | 3      | 输入侧电源电压                                                                                                              |

| VSS     | 4      | 4      | 输入侧参考地                                                                                                               |

| Disable | 5      | 5      | 使能信号， 默认使能状态为低时器件正常工作。<br>Disable 引脚输入高电平时器件不工作，输出被强拉低；Disable 引脚输入低电平或悬空时器件恢复正常输出；如果不使用，建议将该引脚连接至接地。 <sup>[1]</sup> |

| DT      | 6      | 6      | 死区时间调制 PIN；<br>DT 接电阻（5kΩ~200kΩ）：DT(ns)=10×R <sub>DT</sub> (kΩ)的死区时间。                                                |

| NC      | 7      | 7      | 悬空                                                                                                                   |

| VCC     | 8      | 8      | 输入侧电源电压                                                                                                              |

| GNDB    | 9      | 9      | 输出驱动侧 B 通道参考地                                                                                                        |

| VOB     | 10     | 10     | 输出驱动侧 B 通道的输出                                                                                                        |

| VDDB    | 11     | 11     | 输出驱动侧 B 通道电源电压                                                                                                       |

| NC      | 12     | -      | 悬空                                                                                                                   |

| NC      | 13     | -      | 悬空                                                                                                                   |

| GNDA    | 14     | 12     | 输出驱动侧 A 通道参考地                                                                                                        |

| VOA     | 15     | 13     | 输出驱动侧 A 通道的输出                                                                                                        |

| VDDA    | 16     | 14     | 输出驱动侧 A 通道电源电压                                                                                                       |

注：[1] 该逻辑状态定义仅适用于 CCi8332XXX-XXL 的版本。

### 3 极限参数

| 参数          | 符号                                                         | 最小值  | 最大值              | 单位 |

|-------------|------------------------------------------------------------|------|------------------|----|

| 输入侧电源电压     | $V_{CC} - V_{SS}$                                          | -0.3 | 6                | V  |

| 输出驱动侧电源电压   | $V_{DDA} - GNDA, V_{DDB} - GNDB$                           | -0.3 | 35               | V  |

| 输入信号        | $(V_{IA}, V_{IB}, Disable, DT) - V_{SS}$                   | -0.3 | $V_{CC} + 0.3$   | V  |

|             | $(V_{IA}, V_{IB}, Disable, DT) - V_{SS}, 200\text{ ns}$ 瞬态 | -2   | $V_{CC} + 0.3$   | V  |

| 输出信号        | $V_{DDA} - GNDA, V_{DDB} - GNDB$                           | -0.3 | $V_{DD^*} + 0.3$ | V  |

|             | $V_{DDA} - GNDA, V_{DDB} - GNDB, 200\text{ ns}$ 瞬态         | -2   | $V_{DD^*} + 0.3$ | V  |

| 通道 A、B 的电压差 | GNDA - GNDB                                                | -    | 1500             | V  |

| 最大结温        | $T_{J(max)}$                                               | -40  | 150              | °C |

| 存储环境温度      | $T_s$                                                      | -40  | 165              | °C |

| 静电保护 (ESD)  | HBM                                                        | -3   | 3                | kV |

|             | CDM                                                        | -1.5 | 1.5              | kV |

| 闩锁保护        | LU                                                         | -200 | 200              | mA |

注意：应用时不要超过最大额定值，以防止损坏。长时间工作在最大额定值的情况下可能影响器件的可靠性。

### 4 推荐工作环境

| 参数        | 符号                                       | 最小值 | 最大值      | 单位 |

|-----------|------------------------------------------|-----|----------|----|

| 输入侧电源电压   | $V_{CC} - V_{SS}$                        | 3   | 5.5      | V  |

| 输出驱动侧电源电压 | $V_{DDA} - GNDA, V_{DDB} - GNDB$         | 9   | 30       | V  |

| 输入信号      | $(V_{IA}, V_{IB}, Disable, DT) - V_{SS}$ | 0   | $V_{CC}$ | V  |

| 结温        | $T_J$                                    | -40 | 150      | °C |

| 工作环境温度    | $T_A$                                    | -40 | 125      | °C |

### 5 热阻信息

| 参数     | 符号       | 测试条件          | 数值    | 单位   |

|--------|----------|---------------|-------|------|

| 结与环境热阻 | $R_{JA}$ | SOP16W/SOP14W | 97    | °C/W |

|        |          | LGA 4×4       | 209.5 | °C/W |

| 结与外壳热阻 | $R_{JC}$ | SOP16W/SOP14W | 24    | °C/W |

|        |          | LGA 4×4       | 48.4  | °C/W |

## 6 工作特性

( $V_{CC} = 3.3V/5V$ ,  $V_{CC}$  至  $V_{SS}$  接  $0.1\mu F$  电容,  $V_{DDA} = V_{DDB} = 15V$ ,  $V_{DDA/B}$  至  $GND/A/B$  接  $1\mu F$  电容,  $T_A = -40^\circ C \sim 125^\circ C$ 。除非另有说明, 典型值为  $T_A=25^\circ C$ )

### 6.1 电气特性

| 参数               | 符号                               | 条件                                                       | 最小值  | 典型值  | 最大值  | 单位         |

|------------------|----------------------------------|----------------------------------------------------------|------|------|------|------------|

| <b>输入侧电源</b>     |                                  |                                                          |      |      |      |            |

| VCC 工作电压         | $V_{CC}$                         |                                                          | 3.0  | -    | 5.5  | V          |

| VCC 静态电流         | $I_{VCCQ}$                       | $V_{IA}=V_{IB}=0$                                        | -    | 1.5  | 2.0  | mA         |

| VCC 工作电流         | $I_{VCCI}$                       | $V_{IA}=V_{CC}, V_{IB}=0$<br>或 $V_{IA}=0, V_{IB}=V_{CC}$ | -    | 3.0  | 5.0  | mA         |

| VCC UVLO 释放阈值    | $V_{CC\_ON}$                     |                                                          | 2.55 | 2.70 | 2.95 | V          |

| VCC UVLO 复位阈值    | $V_{CC\_OFF}$                    |                                                          | 2.40 | 2.52 | 2.80 | V          |

| VCC UVLO 迟滞      | $V_{CC\_HYS}$                    |                                                          | -    | 0.18 | -    | V          |

| <b>输出驱动侧电源</b>   |                                  |                                                          |      |      |      |            |

| VDDA/B 工作电压      | $V_{DDA}, V_{DDB}$               | 8V UVLO 档位                                               | 9    | -    | 30   | V          |

|                  |                                  | 6V UVLO 档位                                               | 6.5  |      | 30   | V          |

| VDDA/B 静态电流      | $I_{VDD^*Q}$                     | $V_{IA}=V_{IB}=0$                                        | -    | 1.36 | 2.00 | mA         |

| VDDA/B 工作电流      | $I_{VDD^*I}$                     | 输入频率 500kHz, $C_{VOA}C_{VOB}=100pF$                      | -    | 3.3  | 4.5  | mA         |

| VDDA/B UVLO 释放阈值 | $V_{DD^*\_ON}$                   | 8V UVLO 档位                                               | 7.80 | 8.25 | 8.60 | V          |

| VDDA/B UVLO 复位阈值 | $V_{DD^*\_OFF}$                  | 8V UVLO 档位                                               | 7.20 | 7.60 | 7.90 | V          |

| VDDA/B UVLO 迟滞   | $V_{DD^*\_HYS}$                  | 8V UVLO 档位                                               | -    | 0.65 | -    | V          |

| VDDA/B UVLO 释放阈值 | $V_{DD^*\_ON}$                   | 6V UVLO 档位                                               | 5.50 | 5.90 | 6.30 | V          |

| VDDA/B UVLO 复位阈值 | $V_{DD^*\_OFF}$                  | 6V UVLO 档位                                               | 5.10 | 5.50 | 5.90 | V          |

| VDDA/B UVLO 迟滞   | $V_{DD^*\_HYS}$                  | 6V UVLO 档位                                               | -    | 0.40 | -    | V          |

| <b>输入侧特性</b>     |                                  |                                                          |      |      |      |            |

| 输入下拉电阻           | $R_{VI^*\_PD}$                   |                                                          | -    | 160  | -    | k $\Omega$ |

| 输入上拉电阻           | $R_{Disable\_PU}$                |                                                          | -    | 160  | -    | k $\Omega$ |

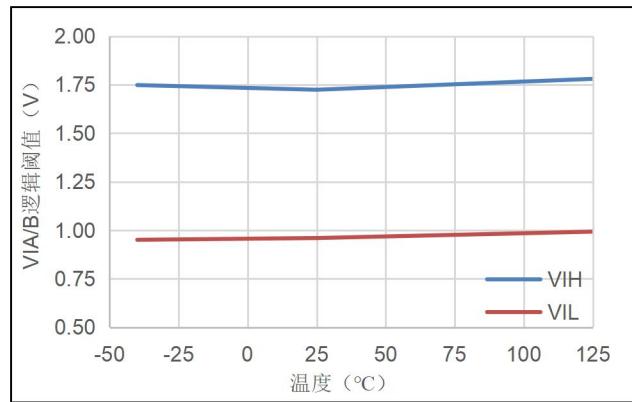

| 输入逻辑高阈值          | $V_{I^*\_H}, V_{Disable\_H}$     |                                                          | 1.6  | 1.8  | 2.0  | V          |

| 输入逻辑低阈值          | $V_{I^*\_L}, V_{Disable\_L}$     |                                                          | 0.9  | 1.1  | 1.3  | V          |

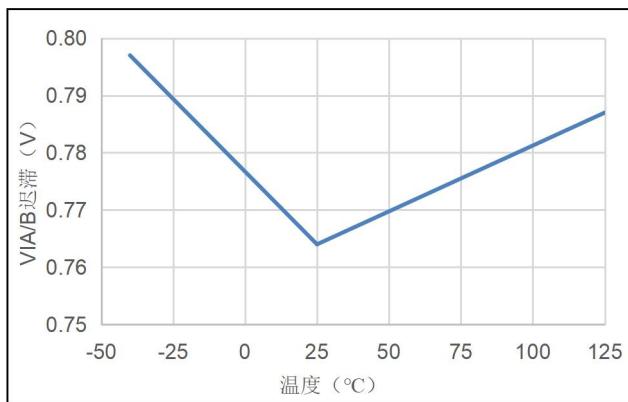

| 输入迟滞             | $V_{I^*\_HYS}, V_{Disable\_HYS}$ |                                                          | -    | 0.7  | -    | V          |

接上表:

| 参数             | 符号                 | 条件                                                                  | 最小值          | 典型值          | 最大值  | 单位       |

|----------------|--------------------|---------------------------------------------------------------------|--------------|--------------|------|----------|

| <b>输出驱动侧特性</b> |                    |                                                                     |              |              |      |          |

| 输出上管峰值电流       | $I_{OAP}, I_{OBP}$ | $C_{VDD} = 10 \mu F, C_{LOAD} = 0.18 \mu F,$<br>$f = 1 \text{ kHz}$ | -            | 4            | -    | A        |

| 输出下管峰值电流       | $I_{OAN}, I_{OBN}$ |                                                                     | -            | 6            | -    | A        |

| 输出上管电压         | $V_{OH}$           | 8V UVLO 档位, $V_{DD} = 15V, I_o = 100mA$                             | $V_{DD}-200$ | $V_{DD}-100$ | -    | mV       |

| 输出下管电压         | $V_{OL}$           | 8V UVLO 档位, $V_{DD} = 15V, I_o = -100mA$                            | -            | 50           | 75   | mV       |

| 输出上管电压         | $V_{OH}$           | 6V UVLO 档位, $V_{DD} = 7V, I_o = 100mA$                              | $V_{DD}-500$ | $V_{DD}-330$ | -    | mV       |

| 输出下管电压         | $V_{OL}$           | 6V UVLO 档位, $V_{DD} = 7V, I_o = -100mA$                             | -            | 40           | 80   | mV       |

| 输出上管电阻         | $R_{OH}$           | 8V UVLO 档位, $V_{DD} = 15V, I_o = 100mA$                             | -            | 1            | 2    | $\Omega$ |

| 输出下管电阻         | $R_{OL}$           | 8V UVLO 档位, $V_{DD} = 15V, I_o = -100mA$                            | -            | 0.50         | 0.75 | $\Omega$ |

| 输出上管电阻         | $R_{OH}$           | 6V UVLO 档位, $V_{DD} = 7V, I_o = 100mA$                              |              | 3.3          | 5.0  | $\Omega$ |

| 输出下管电阻         | $R_{OL}$           | 6V UVLO 档位, $V_{DD} = 7V, I_o = -100mA$                             |              | 0.4          | 0.8  | $\Omega$ |

## 6.2 开关特性

| 参数                   | 符号                           | 条件                                                                                                                                                     | 最小值                    | 典型值  | 最大值  | 单位   |

|----------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------|------|

| 传播延迟-高到低             | $t_{PHL}$                    |                                                                                                                                                        | 15                     | 40   | 55   | ns   |

| 传播延迟-低到高             | $t_{PLH}$                    |                                                                                                                                                        | 15                     | 40   | 55   | ns   |

| 脉冲宽度失真               | $PWD$                        |                                                                                                                                                        | -                      | -    | 10   | ns   |

| 传输延迟匹配               | $t_{DM}$                     | $f=100\text{kHz}$                                                                                                                                      | -                      | -    | 5    | ns   |

| 可编程死区时间              | $t_{DT}$                     | $t_{DT}(\text{ns})=10 \times R(\text{k}\Omega); \text{ test for } R=100\text{k}\Omega$<br>防止两通道同时输出高。 $R=5\text{k}\Omega \sim 200\text{k}\Omega^{[1]}$ | 800                    | 1000 | 1200 | ns   |

|                      |                              | DT no connect, 防止两通道同时输出高                                                                                                                              | -                      | 10   | -    | ns   |

|                      |                              | DT 接 $V_{CC}$                                                                                                                                          | 没有死区时间，<br>且允许两通道同时输出。 |      |      | -    |

| 输出上升时间 10% → 90%     | $t_r$                        | $C_L=1 \text{ nF}$                                                                                                                                     | -                      | 8.5  | 15   | ns   |

| 输出下降时间 90% → 10%     | $t_f$                        | $C_L=1 \text{ nF}$                                                                                                                                     | -                      | 5    | 10   | ns   |

| 最小脉宽                 | $t_{PWmin}$                  | $C_L=50 \text{ pF}$                                                                                                                                    | -                      | 22   | 30   | ns   |

| Enable: 禁用态 → 正常工作态  | $t_{en}$                     |                                                                                                                                                        | -                      | -    | 60   | ns   |

| Disable: 正常工作态 → 禁用态 | $t_{dis}$                    |                                                                                                                                                        | -                      | -    | 60   | ns   |

| VCC_UVLO 释放到 OUT 变高  | $t_{VCC\_ON} \text{ to OUT}$ |                                                                                                                                                        | -                      | 20   | 60   | us   |

| VDD*_UVLO 释放到 OUT 变高 | $t_{VDD\_ON} \text{ to OUT}$ |                                                                                                                                                        | -                      | 30   | 60   | us   |

| 共模瞬态抑制               | $CMTI$                       |                                                                                                                                                        | -                      | 150  | -    | V/ns |

注:  $R_{DT}$  的推荐值介于  $5\text{k}\Omega$  到  $200\text{k}\Omega$  之间,  $R_{DT} < 20\text{k}\Omega$  时, 死区时间典型值会有 0~20ns 的偏差。

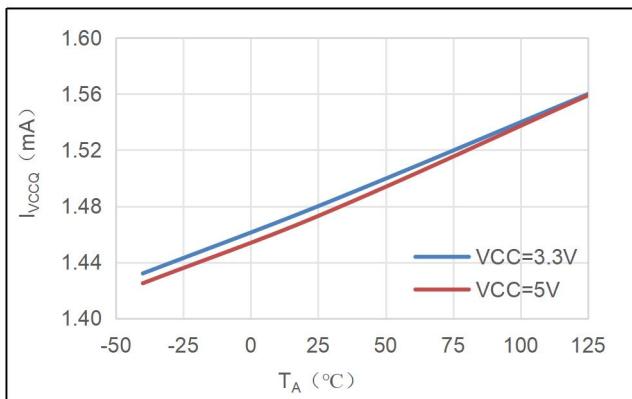

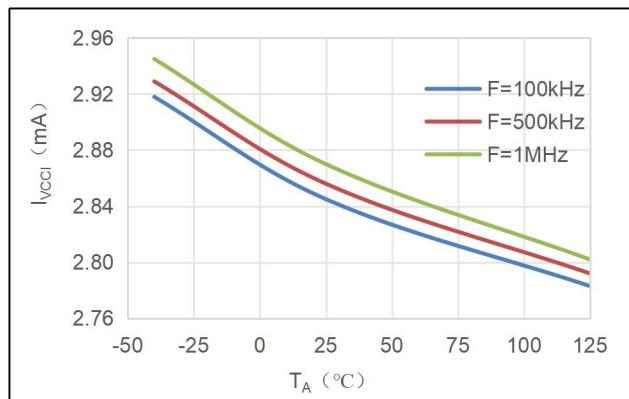

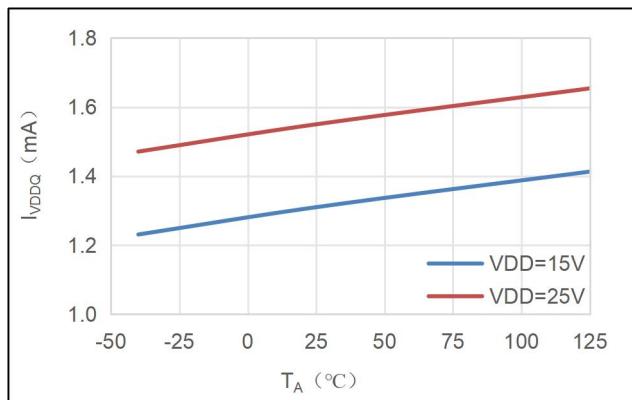

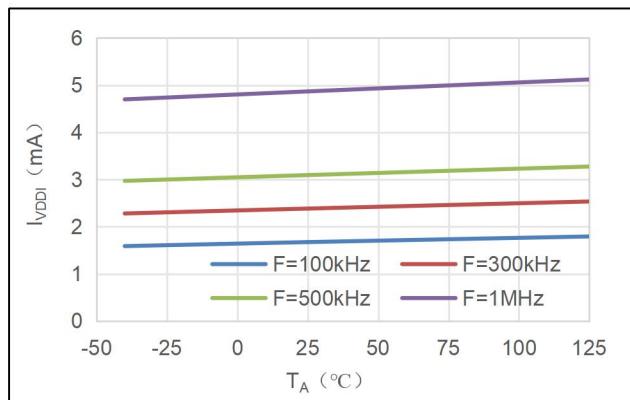

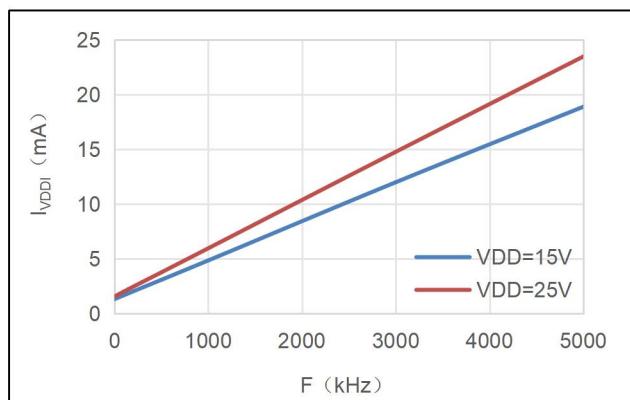

6.3 曲线&波形 (若无特别说明,  $T_A = 25^\circ\text{C}$ )图 6-1 V<sub>CC</sub> 静态电流  $I_{VCCQ}$  vs 工作环境温度图 6-2 V<sub>CC</sub> 工作电流  $I_{VCCI}$  vs 工作环境温度 (A、B 通道接反向方波)图 6-3 V<sub>DDA/B</sub> 静态电流  $I_{VDDQ}$  vs 工作环境温度 (30pF 负载)图 6-4 V<sub>DDA/B</sub> 工作电流  $I_{VDDI}$  vs 工作环境温度 (30pF 负载)图 6-5 输出峰值电流 vs V<sub>DDA/B</sub> 电源电压图 6-6 V<sub>DDA/B</sub> 工作态电流  $I_{VDDI}$  vs 频率

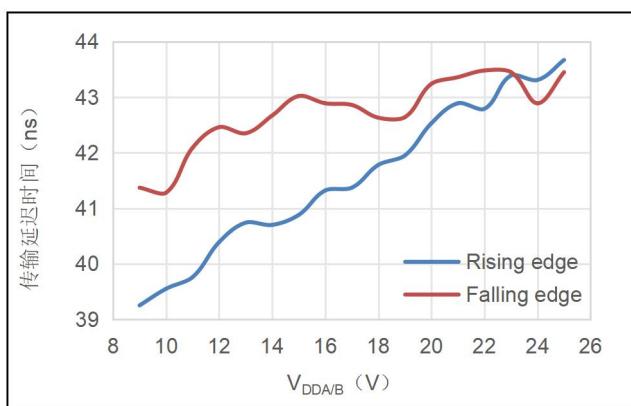

图 6-7 传输延迟时间 vs V<sub>DDA/B</sub>

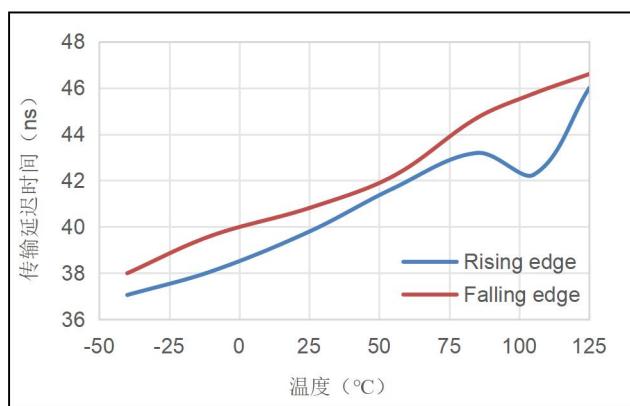

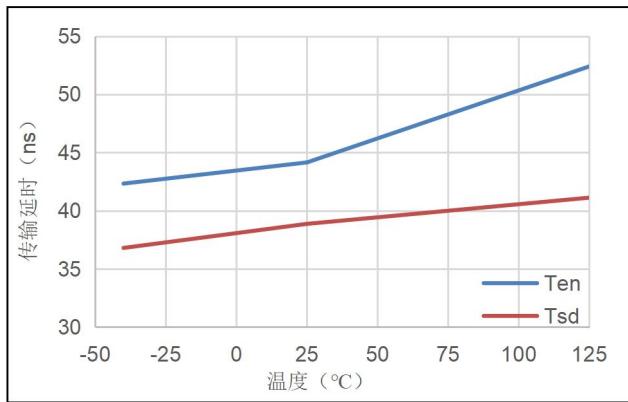

图 6-8 传输延迟时间 vs 工作环境温度

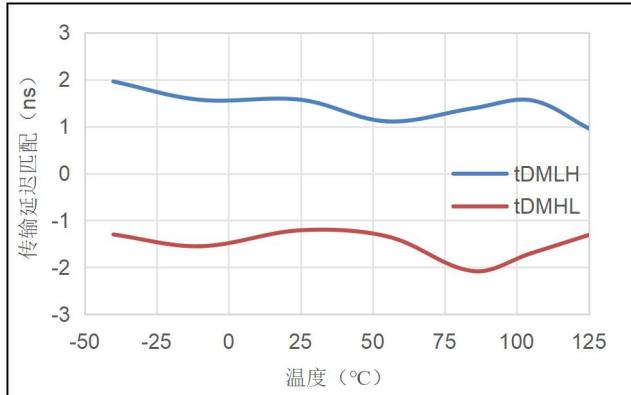

图 6-9 传输延迟匹配 vs 工作环境温度

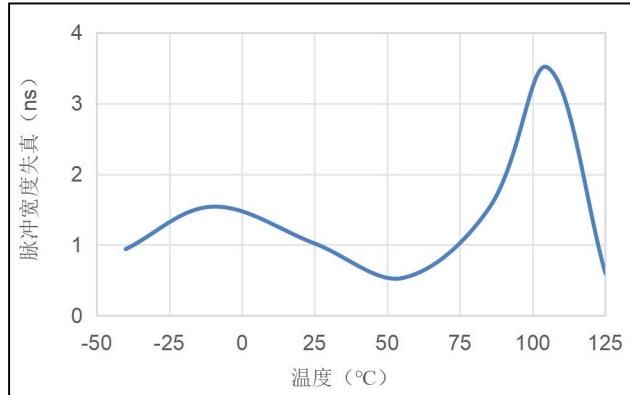

图 6-10 脉冲宽度失真 vs 工作环境温度

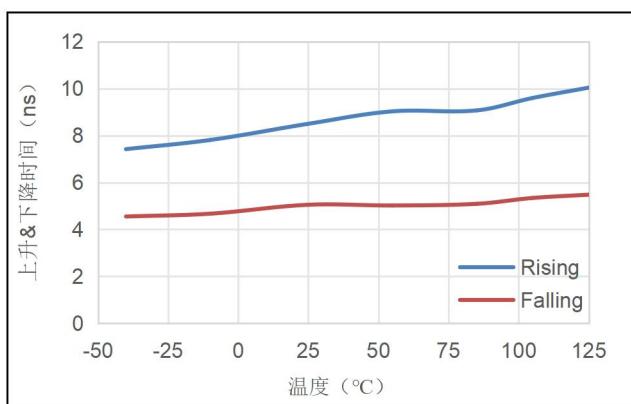

图 6-11 上升&amp;下降时间 vs 工作环境温度 (1nF 负载)

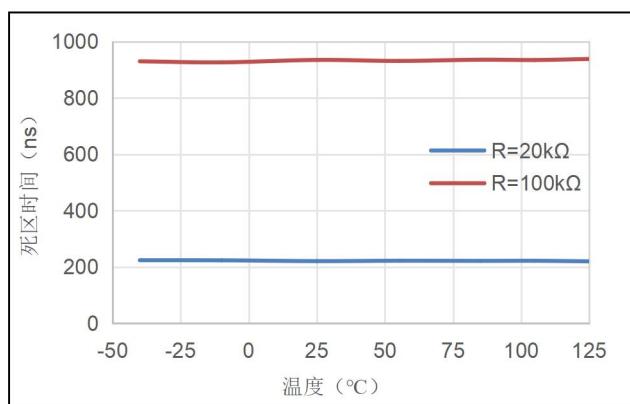

图 6-12 死区时间 vs 工作环境温度

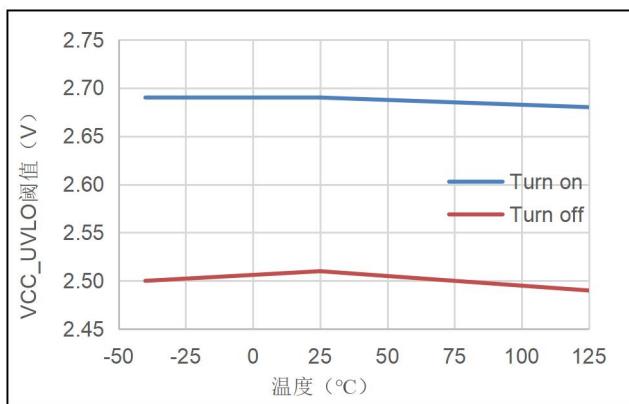

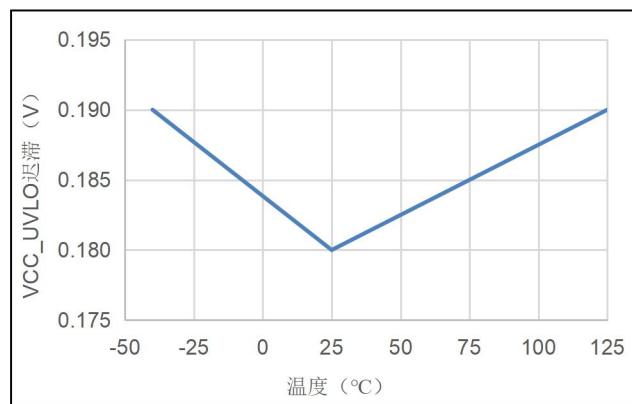

图 6-13 VCC\_UVLO 阈值 vs 工作环境温度

图 6-14 VCC\_UVLO 迟滞 vs 工作环境温度

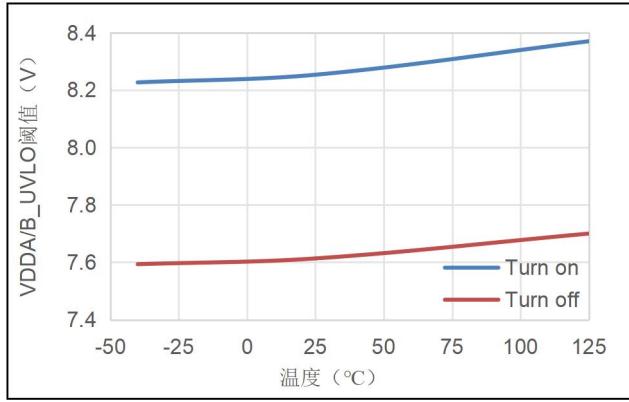

图 6-15 VDDA/B\_UVLO 阈值 vs 工作环境温度 (8V UVLO)

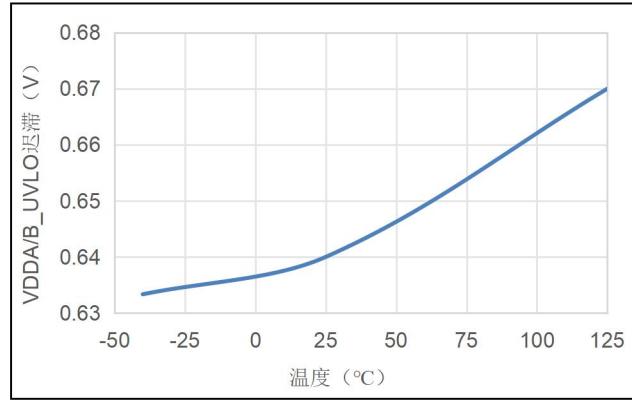

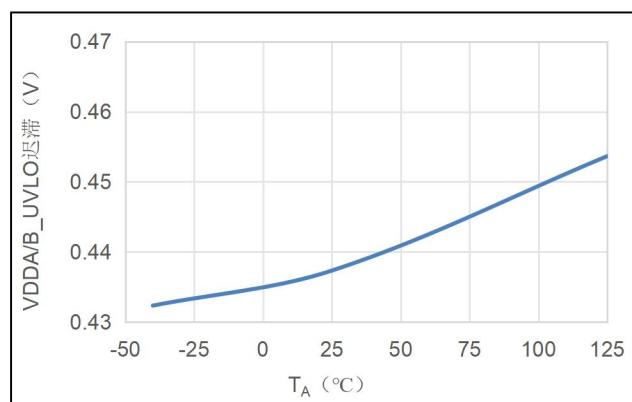

图 6-16 VDDA/B\_UVLO 迟滞 vs 工作环境温度 (8V UVLO)

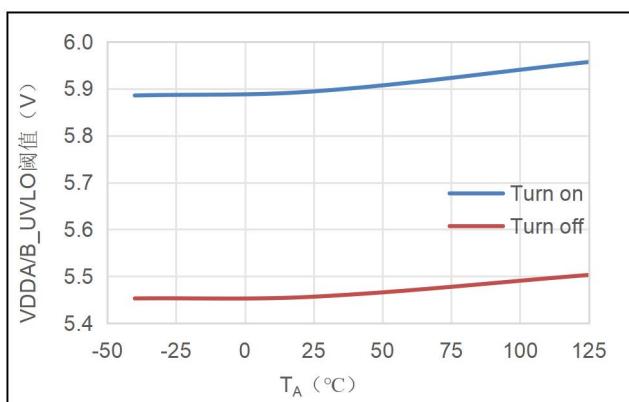

图 6-17 VDDA/B\_UVLO 阈值 vs 工作环境温度 (6V UVLO)

图 6-18 VDDA/B\_UVLO 迟滞 vs 工作环境温度 (6V UVLO)

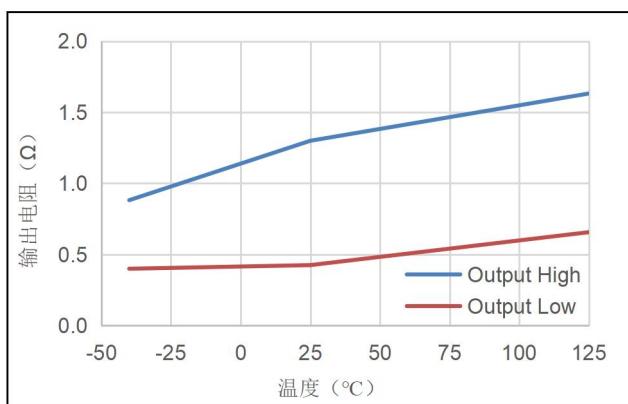

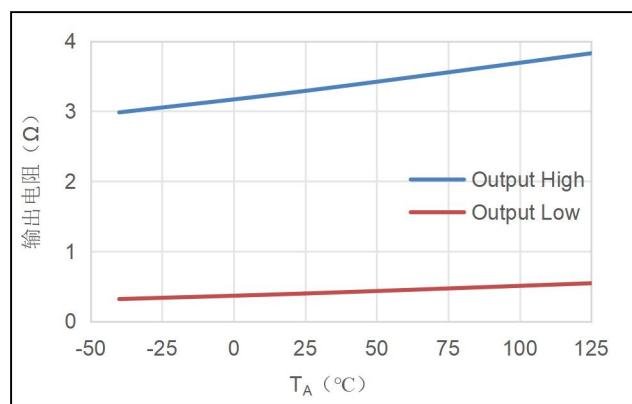

图 6-19 输出电阻 vs 工作环境温度 (8V UVLO, V<sub>DD</sub> = 15V)图 6-20 输出电阻 vs 工作环境温度 (6V UVLO, V<sub>DD</sub> = 7V)

图 6-21 Disable 传输延时 vs 工作环境温度

图 6-22 VIA/B 逻辑阈值 vs 工作环境温度

图 6-23 VIA/B 退滞 vs 工作环境温度

## 7 高压特性描述

## 7.1 绝缘特性

| 参数                                   | 符号                | 测试条件                                                                                                                                                             | 值                 |                   | 单位               |

|--------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------------|

|                                      |                   |                                                                                                                                                                  | SOP16W            | SOP14W            |                  |

| 外部间隙                                 | CLR               | 通过空气的最短距离                                                                                                                                                        | 8.3               | 3                 | mm               |

| 外部爬电                                 | CPG               | 穿过包装表面的最短距离                                                                                                                                                      | 8.3               | 3                 | mm               |

| 绝缘穿透距离                               | DTI               | 双绝缘层的最小内部间隙 (内部间隙)                                                                                                                                               | 150               | -                 | um               |

| 相对漏电起痕指数                             | CTI               | DIN EN 60112 (VDE 0303-11);                                                                                                                                      | >600              | >600              | V                |

| 物料组                                  |                   | 符合 IEC 60664-1 标准                                                                                                                                                | I                 | I                 |                  |

| 过电压类别符合<br>IEC 60664-1 标准            |                   | 额定电源电压≤600 V <sub>RMS</sub>                                                                                                                                      | I-IV              | I-IV              |                  |

|                                      |                   | 额定电源电压≤1000 V <sub>RMS</sub>                                                                                                                                     | I-III             | I-III             |                  |

| 绝缘规范 符合 DIN VDE V 0884-11:2017-01 标准 |                   |                                                                                                                                                                  |                   |                   |                  |

| 最大重复峰值隔离电压                           | V <sub>IORM</sub> |                                                                                                                                                                  | 2121              | 792               | V <sub>PK</sub>  |

| 最大工作隔离电压                             | V <sub>IOWM</sub> | 交流电压                                                                                                                                                             | 1500              | 560               | V <sub>RMS</sub> |

|                                      |                   | 直流电压                                                                                                                                                             | 2121              | 792               | V <sub>DC</sub>  |

| 最大瞬态隔离电压                             | V <sub>IOTM</sub> | V <sub>TEST</sub> = V <sub>IOTM</sub> , t = 60 s.<br>V <sub>TEST</sub> = 1.2 × V <sub>IOTM</sub> , t = 1 s.                                                      | 8000              | 3000              | V <sub>PK</sub>  |

| 最大浪涌隔离电压                             | V <sub>IOSM</sub> | 符合 IEC 62368-1 的测试方法, 1.2/50 us 波形,<br>V <sub>TEST</sub> = 1.6 × V <sub>IOSM</sub> , (在绝缘油中测试)                                                                   | 12500             | 12500             | V <sub>PK</sub>  |

| 视在电荷                                 | q <sub>pd</sub>   | 方法 a, 输入/输出安全测试子组 2/3 后<br>V <sub>ini</sub> = V <sub>IOTM</sub> , t <sub>ini</sub> = 60s;<br>V <sub>pd(m)</sub> = 1.2 × V <sub>IORM</sub> , t <sub>m</sub> = 10s | <5                | <5                | pC               |

|                                      |                   | 方法 a, 环境测试子组 1 后<br>V <sub>ini</sub> = V <sub>IOTM</sub> , t <sub>ini</sub> = 60s;<br>V <sub>pd(m)</sub> = 1.6 × V <sub>IORM</sub> , t <sub>m</sub> = 10s        | <5                | <5                | pC               |

|                                      |                   | 方法 b1, 常规测试和预调节<br>V <sub>ini</sub> = 1.2 × V <sub>IOTM</sub> ; t <sub>ini</sub> = 1s;<br>V <sub>pd(m)</sub> = 1.875 × V <sub>IORM</sub> , t <sub>m</sub> = 1s   | <5                | <5                | pC               |

| 势垒电容, 输入到输出                          | C <sub>IO</sub>   | V <sub>IO</sub> = 0.4 sin (2πft), f = 1 MHz                                                                                                                      | 1.2               | 1.2               | pF               |

| 隔离电阻, 输入到输出                          | R <sub>IO</sub>   | V <sub>IO</sub> = 500 V at T <sub>A</sub> = 25°C                                                                                                                 | >10 <sup>12</sup> | >10 <sup>12</sup> | Ω                |

|                                      |                   | V <sub>IO</sub> = 500 V at 100°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                        | >10 <sup>11</sup> | >10 <sup>11</sup> |                  |

|                                      |                   | V <sub>IO</sub> = 500 V at T <sub>S</sub> = 150°C                                                                                                                | >10 <sup>9</sup>  | >10 <sup>9</sup>  |                  |

| 污染程度                                 |                   |                                                                                                                                                                  | 2                 | 2                 |                  |

| 气候类别                                 |                   |                                                                                                                                                                  | 40/125/21         | 40/125/21         |                  |

| UL 1577                              |                   |                                                                                                                                                                  |                   |                   |                  |

| 耐受隔离电压                               | V <sub>ISO</sub>  | V <sub>TEST</sub> = V <sub>ISO</sub> = 5700 V <sub>RMS</sub> , t = 60s.<br>V <sub>TEST</sub> = 1.2 × V <sub>ISO</sub> , t = 1s.                                  | 5700              | 2121              | V <sub>RMS</sub> |

## 7.2 安全认证

| UL                     |                                                                                             |

|------------------------|---------------------------------------------------------------------------------------------|

| 根据 UL 1577 组件认证计划进行了认证 | 单一保护, 5700 V <sub>RMS</sub> , SOP16W<br>Certificate Number: UL-US-2442758-0、UL-CA-2432313-0 |

| 文件编号: E539511          |                                                                                             |

## 7.3 安全限制值

| 参数     | 符号, 测试条件                                                                                                                       | 数值        | 单位   |

|--------|--------------------------------------------------------------------------------------------------------------------------------|-----------|------|

| 安全电源功耗 | $R_{JA}=97^{\circ}\text{C}/\text{W}$ , $T_J=150^{\circ}\text{C}$ , $T_A=25^{\circ}\text{C}$                                    | 输入侧       | 14   |

|        |                                                                                                                                | 驱动 A、驱动 B | 637  |

|        |                                                                                                                                | 总功耗       | 1288 |

| 安全电源电流 | $R_{JA}=97^{\circ}\text{C}/\text{W}$ , $V_{DDA}$ 、 $V_{DDB}=12\text{V}$ , $T_J=150^{\circ}\text{C}$ , $T_A=25^{\circ}\text{C}$ | 驱动 A、驱动 B | 53   |

|        | $R_{JA}=97^{\circ}\text{C}/\text{W}$ , $V_{DDA}$ 、 $V_{DDB}=25\text{V}$ , $T_J=150^{\circ}\text{C}$ , $T_A=25^{\circ}\text{C}$ | 驱动 A、驱动 B | 25.4 |

| 安全温度   | -                                                                                                                              | 150       | °C   |

## 8 参数测量信息

### 8.1 传播延迟和脉冲宽度失真

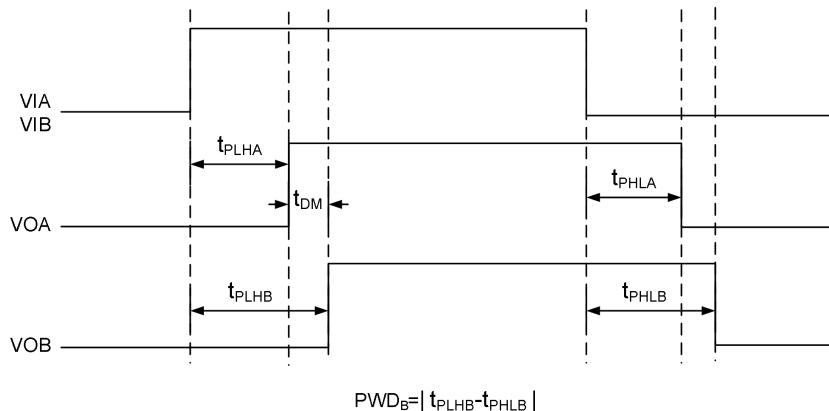

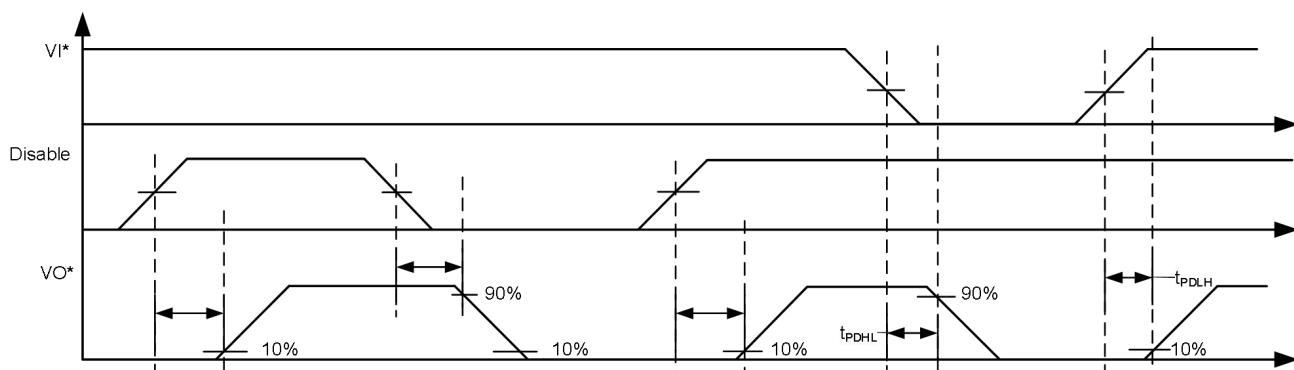

图 8-1 展示了如何从通道 A 和 B 的传播延迟计算脉冲宽度失真 (PWD) 和延迟匹配 ( $t_{DM}$ )。测量延迟匹配需要两个输入同相以及禁用死区时间。

图 8-1 传播延迟和脉冲宽度失真

### 8.2 上升和下降时间

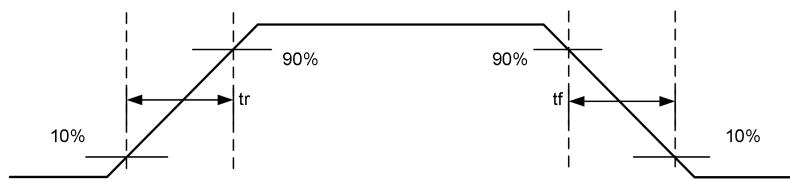

图 8-2 显示了测量上升时间 ( $tr$ ) 和下降时间 ( $tf$ ) 的标准。 $tr$  测量 OUT 电压从 10% 到 90% 的时间， $tf$  测量 OUT 电压从 90% 到 10% 的时间。

图 8-2 输出上升和下降时间

### 8.3 输入和使能响应时间

图 8-3 显示了输入  $VI^*$  的响应时间和 Disable 使能的响应时间。

图 8-3 输入  $VI^*/VIB$  电压和使能 Disable 响应时间

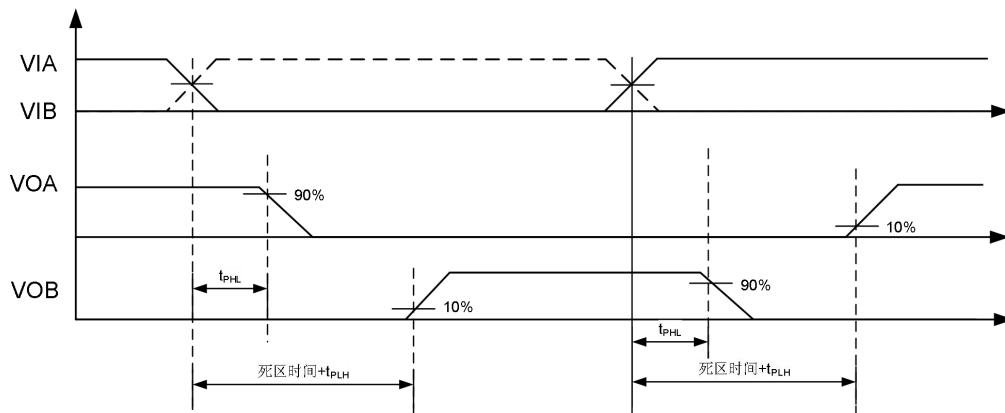

#### 8.4 可编程的死区时间

当 DT 引脚连接到 VCC 上, 禁用死区时间, A、B 是独立的 2 个通道, 允许输出重叠。当 DT 引脚和 GND 之间连接一个电阻器 ( $R_{DT}$ ), VOA 与 VOB 之间的死区时间可编程。

图 8-4 输出死区时间

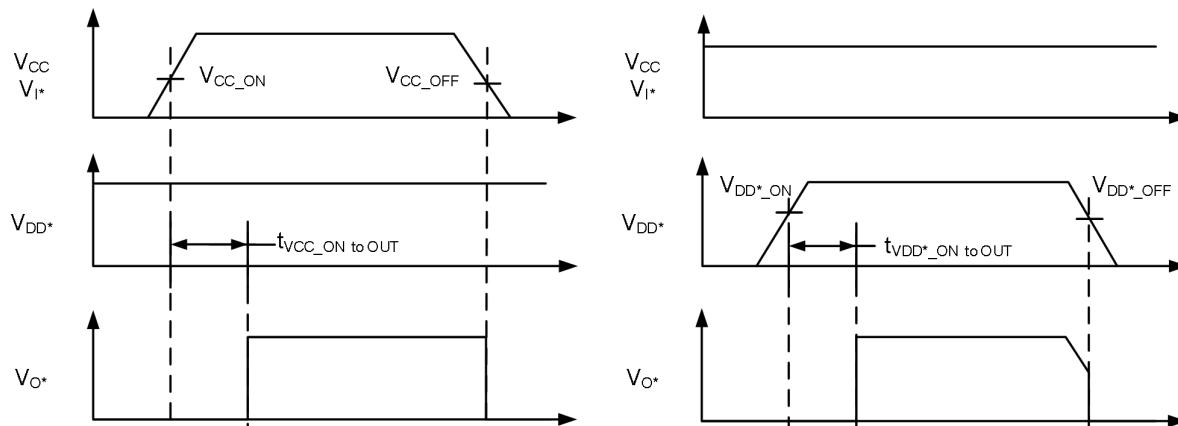

#### 8.5 电源 UVLO 延迟到输出高

当电源电压  $V_{CC}$  从低于复位阈值  $V_{CC\_OFF}$  变为高于释放阈值  $V_{CC\_ON}$  时, 以及当电源电压  $V_{DD^*}$  从低于复位阈值  $V_{DD^*\_OFF}$  变为高于释放阈值  $V_{DD^*\_ON}$  时, 输入到输出开始响应之间存在延迟。对于  $V_{CC\_UVLO}$ , 此延迟被定义为  $t_{VCC\_ON \text{ to } OUT}$ , 典型为 20 $\mu$ s。对于  $V_{DD^*\_UVLO}$ , 此延迟被定义为  $t_{VDD^*\_ON \text{ to } OUT}$ , 典型为 30 $\mu$ s。图 8-5 是  $V_{CC}$  和  $V_{DD^*}$  的 UVLO 输出时序图。

图 8-5 电源 UVLO 输出时序

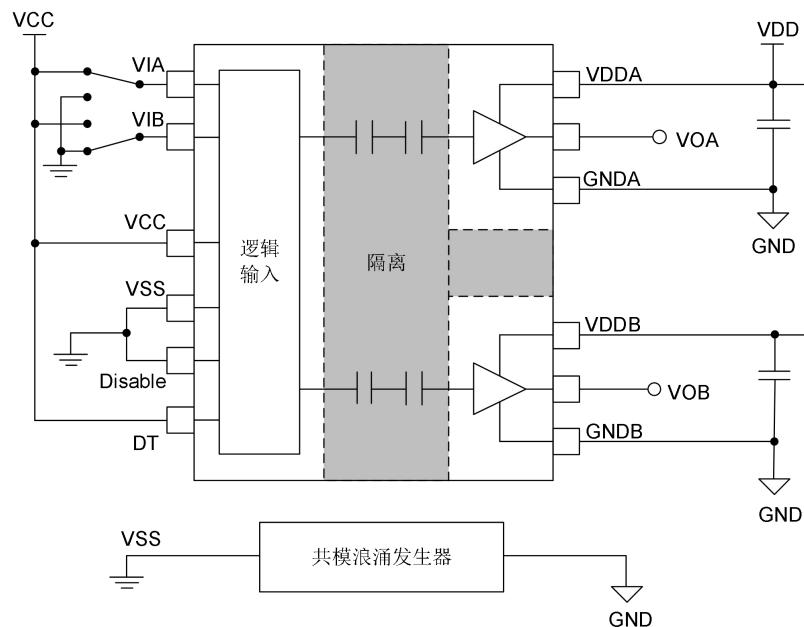

## 8.6 CMTI 测试

图 8-6 是 CMTI 测试配置的示意图。

图 8-6 CMTI 测试示意图

## 9 功能详细描述

### 9.1 概述

CCi8332 是一种高可靠的双通道隔离栅驱动器，可设计用于各种功率开关和电机驱动拓扑。CCi8332 有许多特性，允许它很好地集成控制电路，并保护它驱动的晶体管，此类特性包括输入和输出电源的欠电压锁定（UVLO）、使能引脚、死区时间控制和默认的输出低（输入浮空时）。驱动器输入端兼容 CMOS 和 TTL 接口。当 DT=VCC 时，输入引脚 VIA/VIB 独立控制 VOA/VOB，且允许 2 通道同时输出高；当 DT 接电阻时，在 VOA、VOB 间产生死区时间，可以防止 VOA、VOB 重叠。功能电路方框图如图 9-1 所示。

图 9-1 CCi8332 功能框图

### 9.2 欠压锁定 UVLO

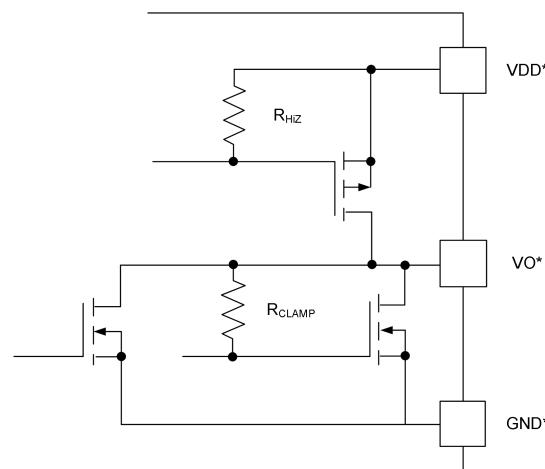

CCi8332 在输出端引脚 (VDD\* 和 GND\*) 的供电电路块上设计了欠电压锁定 (UVLO) 保护功能，主要体现于：当设备启动时，VDD\* 偏置电压低于 VDD\_ON；在设备启动后，若 VDD\* 偏置电压低于 VDD\_OFF 时，VDD\* 会处于 UVLO 保护下。所以无论输入引脚 (VIA / VIB) 的状态如何，上部 PMOS 栅极都会被 Hi-Z 电阻上拉，从而处于断开状态，下部 NMOS 栅极都会被 UVLO 控制，形成导通状态，驱动器电压输出低。

如图 9-2，当驱动器的输出级 VDD\* 处于无电源电压的浮空状态，如果输出被外围拉高，驱动器通过主动下拉功能，将输出电压引入到下部 NMOS 的栅极，输出被有效地钳位到下部 NMOS 器件的阈值电压，通常小于 1.5V。

图 9-2 主动下拉功能框图

VDD UVLO 保护具有迟滞特性 ( $V_{VDD\_HYS}$ )。当电源有接地噪声时，这种迟滞特性可以防止颤振，基于此可允许设备接受电源电压的微小下降，这种电源电压的微小下降现象在设备开始切换和工作电流消耗突然增加时，都会发生。

CCi8332 的输入侧也具有一个内部低电压锁定 (UVLO) 保护功能。除非启动时电压  $V_{CC}$  超过  $V_{CC\_ON}$ ，否则该设备不会工作。一旦引脚接收到小于  $V_{CC\_OFF}$  的电压，该信号将停止传递。与  $VDD$  UVLO 一样，也存在迟滞 ( $V_{CC\_HYS}$ )，以确保稳定运行。

### 9.3 输入输出逻辑状态

表 9.1 展示了输入信号  $V_{IA}$ 、 $V_{IB}$ 、**Disable**、**DT** 与输出信号  $V_{OA}$ 、 $V_{OB}$  的关系。

表 9.1 输入输出信号关系表 [1]

| 输入信号     |          | DT       | Disable | 输出信号     |          | 注释                      |

|----------|----------|----------|---------|----------|----------|-------------------------|

| $V_{IA}$ | $V_{IB}$ |          |         | $V_{OA}$ | $V_{OB}$ |                         |

| L/NC     | L/NC     | $V_{CC}$ | L/NC    | L        | L        |                         |

| L/NC     | H        |          | L/NC    | L        | H        |                         |

| H        | L/NC     |          | L/NC    | H        | L        |                         |

| H        | H        |          | L/NC    | H        | H        | 独立的 2 通道，且允许 2 通道同时输出高。 |

| X        | X        | X        | H       | L        | L        |                         |

| L/NC     | L/NC     | 电阻或 NC   | L/NC    | L        | L        |                         |

| L/NC     | H        |          | L/NC    | L        | H        |                         |

| H        | L/NC     |          | L/NC    | H        | L        |                         |

| H        | H        |          | L/NC    | L        | L        | 防止同时输出高。                |

注：[1] 该真值表仅适用于 CCi8332XXX-XXL 的版本。

## 9.4 可编程死区时间

CCi8332 允许用户通过以下方式调整死区时间。

## 1) DT 上拉 VCC

输入引脚 VIA/VIB 独立控制 VOA/VOB，且允许 2 通道同时输出高。

## 2) DT 接死区时间编程电阻，或 NC

当 DT 引脚保持 NC 时，死区时间 ( $t_{DT}$ ) 设置为  $<20\text{ns}$ ；当 DT 引脚与 GND 之间放置电阻器  $R_{DT}$  时，死区时间 ( $t_{DT}$ ) 可编程。 $R_{DT}$  值可以从下列公式中确定，其中  $R_{DT}$  在  $\text{k}\Omega$  中， $t_{DT}$  在  $\text{ns}$  中：

$$t_{DT} \approx 10 \times R_{DT} \quad (\text{式 9-1})$$

$R_{DT}$  的推荐值介于  $5\text{k}\Omega$  到  $200\text{k}\Omega$  之间， $R_{DT} < 20\text{k}\Omega$  时，死区时间典型值会有  $0\sim20\text{ns}$  的偏差。当  $R_{DT} > 500\text{k}\Omega$  时，CCi8332 会认为 DT 是 NC 状态。DT 引脚处的稳态电压约为  $1.25\text{V}$ 。

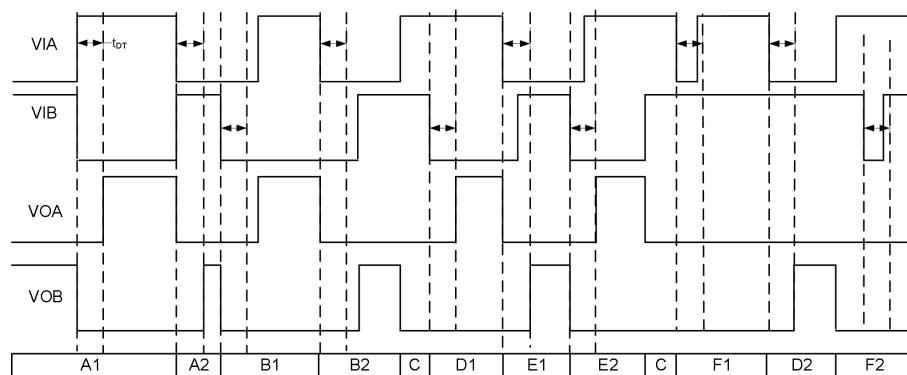

当应用于高侧和低侧驱动器时，死区时间可防止高侧和低侧驱动器穿通。死区时间由 VIA/VIB 下降沿与 VIB/VIA 上升沿的逻辑决定。死区时间输入输出逻辑细节如图 9-3 所示：

图 9-3 死区时间输入输出逻辑时序图

表 9.2 在  $R_{DT}$  设置下，输入和输出逻辑关系表

| 条件                                                              | 结果                                            |

|-----------------------------------------------------------------|-----------------------------------------------|

| A(A1\A2): VIA、VIB 同时切换，且高低互换。                                   | 经过 $t_{DT}$ 后，输入为高的通道，输出为高。                   |

| B(B1\B2): VIB 拉低后，经过 $t_{DT}$ 时间后，VIB/VIA 切换为高。                 | 在 VIB/VIA 上升沿后，VOB/VOA 立即输出高。                 |

| C: VIA、VIB 同时为高                                                 | VOA、VOB 立即输出低。                                |

| D(D1\D2): VIA、VIB 同时为高时，VIA 或 VIB 切换为低。                         | 经过 $t_{DT}$ 后，输入为高的通道，输出为高。                   |

| E(E1\E2): VIA 和 VIB 拉低后，在 $t_{DT}$ 时间内，VIB/VIA 切换为高。            | 在 VIA/VIB 下降沿后，经过 $t_{DT}$ 时间后，VOB/VOA 立即输出高。 |

| F(F1\F2): VIA、VIB 同时为高，VIA 或 VIB 切换为低，但在小于 $t_{DT}$ 时间内，重新切换为高。 | VOA、VOB 保持输出低。                                |

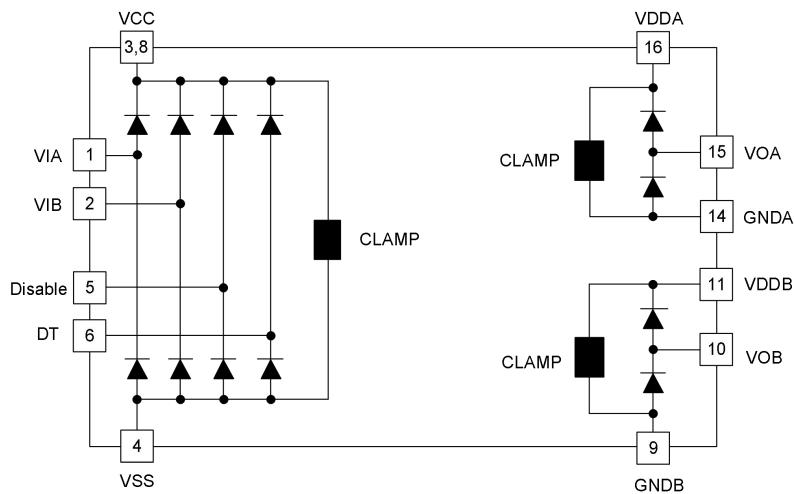

## 9.5 ESD 保护

如图 9-4 所示, CCi8332 的 ESD 保护组件中涉及多个二极管和电源钳位保护。

图 9-4 ESD 保护组件

## 10 应用说明

## 10.1 典型应用电路

CCi8332 有效地结合了隔离和缓冲区驱动器的功能，允许该设备用作功率转换器拓扑，如低侧、高侧、高侧/低侧或半桥驱动器应用。CCi8332 具有 UVLO 和死区时间保护功能，如图 10-1，是 CCi8332 的一个典型的半桥配置电路。

图 10-1 典型的半桥式应用示意图

## 10.2 PCB 布局

PCB 的布局对于获得最佳性能非常重要。一些关键准则如下：

- ❖ 低 ESR 和低 ESL 旁路电容器应放置在设备附近，位于 VCC~VSS 和 VDDA/B~GNDA/B 之间。

- ❖ 存在高频开关电流，对外部功率晶体管的栅极进行充电和放电，导致电磁干扰和振铃现象。栅极驱动器必须尽可能靠近晶体管来减少回路面积，将回路的寄生电感被最小化，并减少晶体管栅极端子的噪声。

- ❖ 在 VDDA/B~GNDA/B 处放置大量铜进行散热。

- ❖ 为确保原边和副边之间的隔离性能，避免在驱动设备下方放置任何 PCB 迹线或覆铜。建议采用 PCB 切口，以防止污染可能影响隔离性能。

## 11 外形尺寸

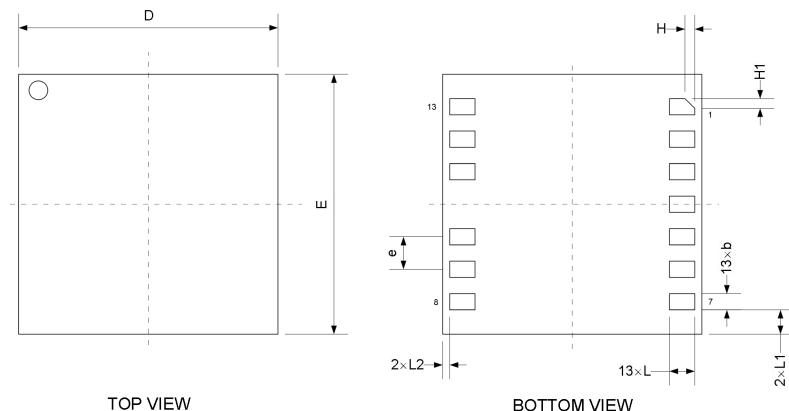

## (1) SOP16W 封装

| 符号 | 尺寸 (mm)  |       |       |

|----|----------|-------|-------|

|    | 最小值      | 典型值   | 最大值   |

| A  | -        | -     | 2.65  |

| A1 | 0.10     | -     | 0.30  |

| A2 | 2.25     | 2.30  | 2.35  |

| A3 | 0.97     | 1.02  | 1.07  |

| b  | 0.35     | -     | 0.43  |

| c  | 0.25     | -     | 0.29  |

| D  | 10.20    | 10.30 | 10.40 |

| E  | 10.10    | 10.30 | 10.50 |

| E1 | 7.40     | 7.50  | 7.60  |

| e  | 1.27 BSC |       |       |

| L  | 0.55     | -     | 0.85  |

| L1 | 1.40 REF |       |       |

| θ  | 0°       | -     | 8°    |

## 注意:

- 尺寸单位为毫米

- 详情参考产品名称定义

## 丝印:

第一行: CCi8332 – 产品名称

第二行: SWD-XYZ

- SWD – 产品的封装代码

- X – 输入通道数

- Y – UVLO档位

- Z – 使能控制位

第三行: XXYYWWZZ

- XX – 封装厂编码

- YYWW – 年周号

- ZZ – 订单序列流水号

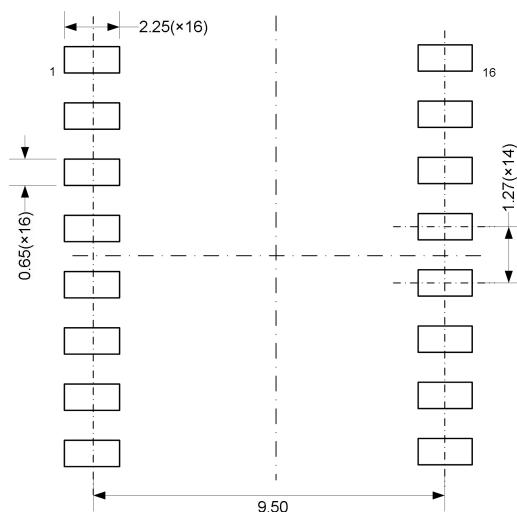

## (2) SOP14W 封装

| 符号 | 尺寸 (mm)  |       |       |

|----|----------|-------|-------|

|    | 最小值      | 典型值   | 最大值   |

| A  | -        | -     | 2.65  |

| A1 | 0.10     | -     | 0.30  |

| A2 | 2.25     | 2.30  | 2.35  |

| A3 | 0.97     | 1.02  | 1.07  |

| b  | 0.35     | -     | 0.43  |

| c  | 0.25     | -     | 0.29  |

| D  | 10.20    | 10.30 | 10.40 |

| E  | 10.10    | 10.30 | 10.50 |

| E1 | 7.40     | 7.50  | 7.60  |

| e  | 1.27 BSC |       |       |

| L  | 0.55     | -     | 0.85  |

| L1 | 1.40 REF |       |       |

| θ  | 0°       | -     | 8°    |

## 注意:

1. 尺寸单位为毫米

2. 详情参考产品名称定义

## 丝印:

第一行: CCi8332 – 产品名称

第二行: SWE-XYZ

- SWE – 产品的封装代码

- X – 输入通道数

- Y – UVLO档位

- Z – 使能控制位

- 第三行: XXYYWWZZ

- XX – 封装厂编码

- YYWW – 年周号

- ZZ – 订单序列流水号

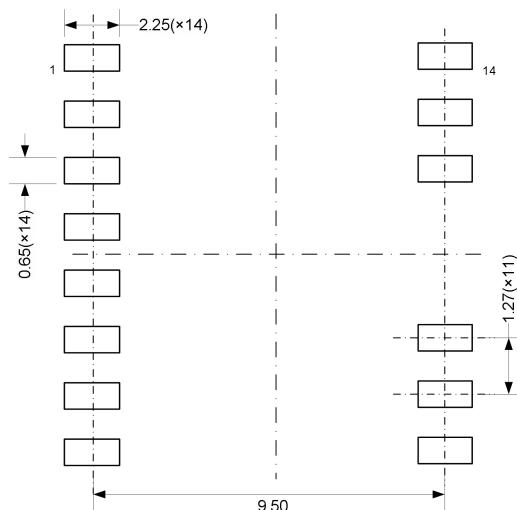

## (3) LGA 4x4 封装

| 符号 | 尺寸 (mm) |       |       |

|----|---------|-------|-------|

|    | 最小值     | 典型值   | 最大值   |

| A  | 0.750   | 0.850 | 0.950 |

| c  | 0.140   | 0.170 | 0.200 |

| D  | 3.900   | 4.000 | 4.100 |

| E  | 3.900   | 4.000 | 4.100 |

| H  | -       | 0.150 | -     |

| H1 | -       | 0.150 | -     |

| L  | 0.340   | 0.390 | 0.440 |

| L1 | 0.300   | 0.375 | 0.450 |

| L2 | 0.350   | 0.110 | 0.185 |

| e  |         | 0.500 |       |

| b  | 0.200   | 0.250 | 0.300 |

## 注意:

1. 尺寸单位为毫米

2. 详情参考产品名称定义

## 丝印:

第一行: CCi8332 – 产品名称

第二行: LAA-XYZ

- LAA – 产品的封装代码

- X – 输入通道数

- Y – UVLO档位

- Z – 使能控制位

第三行: XXYYWWZZ

- XX – 封装厂编码

- YYWW – 年周号

- ZZ – 订单序列流水号

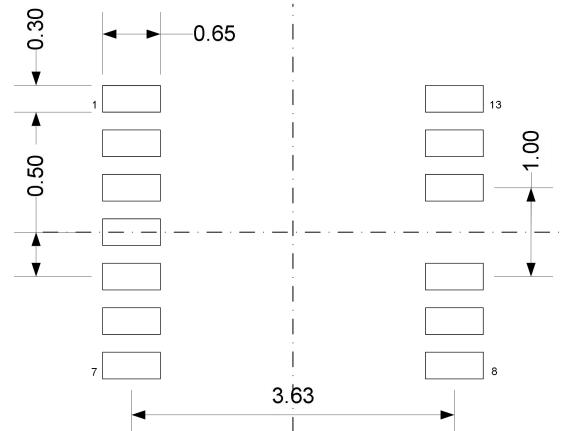

## 12 封装参考

## SOP16W 封装推荐焊盘

缩短焊盘长度增加爬电距离

## SOP14W 封装推荐焊盘

## LGA 4x4 封装推荐焊盘

注：所有尺寸单位为 mm。

## 13 包装信息

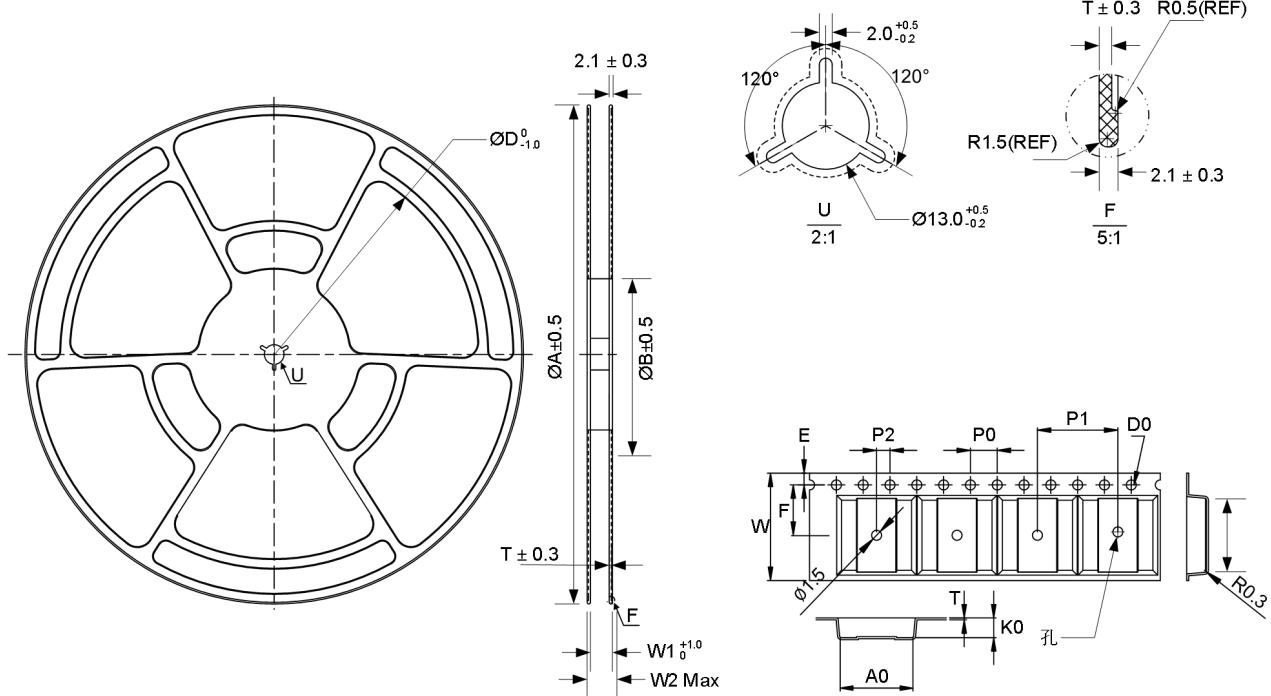

SOP16W 和 SOP14W 封装的卷盘尺寸和载带尺寸

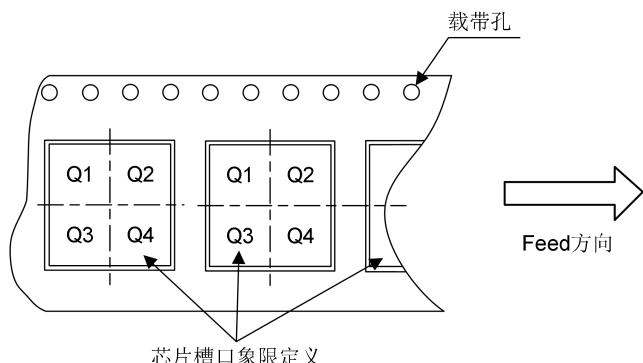

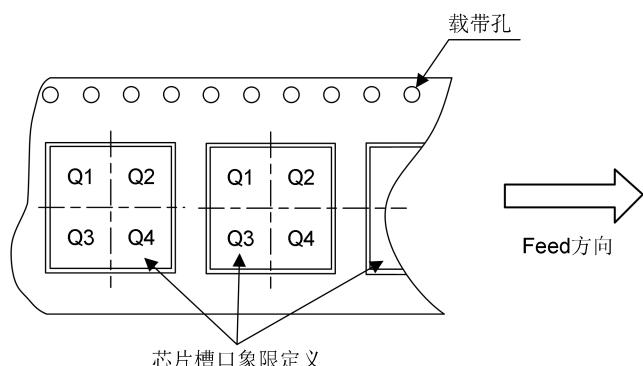

## 载带中芯片 PIN1 的定位

注:

丝印面朝上, PIN1 位置在 Q1

每盘载带前空 30±5 格, 后空 50±5 格。

芯片槽口象限定义

| 卷盘基本尺寸(mm) |            |            |            |                                     |             |

|------------|------------|------------|------------|-------------------------------------|-------------|

| A          | B          | W1         | W2 Max     | T                                   | D           |

| 330        | 100        | 16.4       | 22.4       | 1.5                                 | 270         |

| 载带基本尺寸(mm) |            |            |            |                                     |             |

| W          | A0         | B0         | K0         | P0                                  | P1          |

| 16 ± 0.30  | 10.7 ± 0.1 | 10.7 ± 0.1 | 3.00 ± 0.1 | 4.0 ± 0.1                           | 12.00 ± 0.1 |

| P2         | F          | S          | E          | D0                                  | T           |

| 2.0 ± 0.1  | 7.5 ± 0.1  | 0.0 ± 0.1  | 1.75 ± 0.1 | 1.5 <sup>+0.1</sup> <sub>-0.0</sub> | 0.3 ± 0.05  |

注: 未注明公差 ± 0.2mm

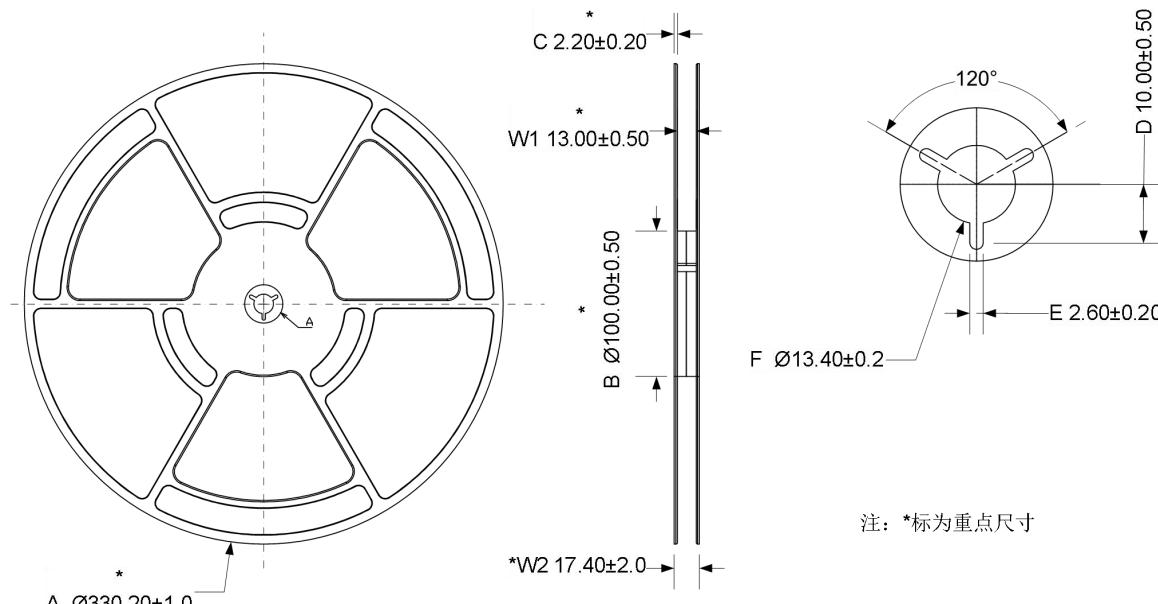

## LGA 4x4 封装的卷盘尺寸

## LGA 4x4 封装的载带尺寸

| 符号 | 尺寸 (mm)                 | 符号 | 尺寸 (mm)                            |

|----|-------------------------|----|------------------------------------|

| W  | $12.00^{+0.10}_{-0.15}$ | D0 | $\varnothing 1.50^{+0.10}_{-0.00}$ |

| E  | $1.75^{+0.10}_{-0.10}$  | D1 | $\varnothing 1.50^{+0.10}_{-0.00}$ |

| F  | $5.50^{+0.10}_{-0.10}$  | T  | $0.30^{+0.05}_{-0.05}$             |

| P0 | $4.00^{+0.10}_{-0.10}$  | A0 | $4.30^{+0.10}_{-0.10}$             |

| P1 | $8.00^{+0.10}_{-0.10}$  | B0 | $4.30^{+0.10}_{-0.10}$             |

| P2 | $2.00^{+0.10}_{-0.10}$  | K0 | $1.10^{+0.10}_{-0.10}$             |

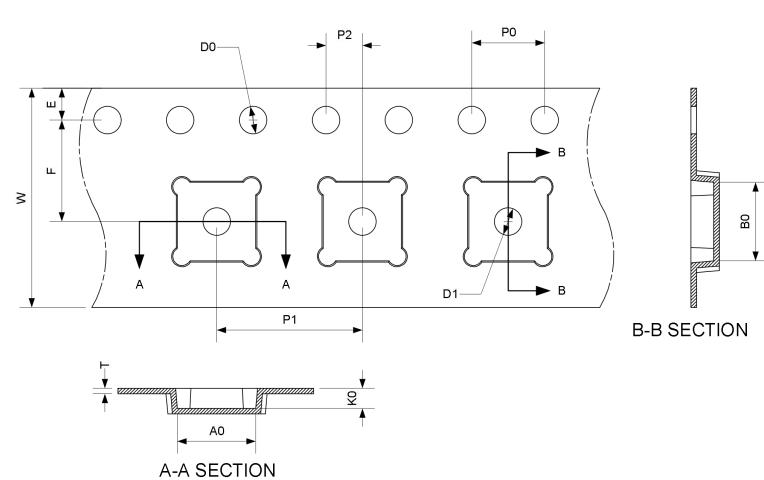

## 载带中芯片 PIN1 的定位

注: 丝印面朝上, PIN1 位置在 Q1。

## 关于芯进

成都芯进电子股份有限公司(CrossChip Microsystems Inc.)成立于 2013 年，是一家国家高新技术企业，从事集成电路设计与销售。公司技术实力雄厚，拥有 60 余项各类专利，主要应用于霍尔传感器信号处理，拥有下列产品线：

- ✓ 高精度线性霍尔传感器

- ✓ 各类霍尔开关

- ✓ 单相电机驱动器

- ✓ 单芯片电流传感器

- ✓ AMR 磁阻传感器

- ✓ 隔离驱动类芯片

## 联系我们

### 成都

地址：四川省成都市高新区天辰路 88 号 3 号楼 1 单元 1-5 楼

电话：+ 86 -028 - 87787685

邮箱：support@crosschipmicro.com

网址：<https://www.crosschipmicro.com>

### 深圳

地址：深圳市南山区科技园国信投资大厦 1005-1007

### 上海

地址：上海市浦东新区盛荣路 88 号盛大天地源创谷 1 号楼 602 室

### 苏州

地址：江苏省苏州市姑苏区西环路 1788 号中广核苏州科技大厦 B 座 1101