# **OSM7N65**

### **FEATURES**

- V<sub>DS</sub>=650V, I<sub>D</sub>=7A

- $R_{SS(on)type} \leq 1.7\Omega@V_{GS}=10V$

- Fast switching capability

- Avalanche energy specified

- Improved dv/dt capability, high ruggedness

- TO-220-FB 封装

### **APPLICATIONS**

- Power Management in Telecom, Industrial Automation

- Motor Driving in Power Tool, E-vehicle, Robotics

- Current Switching in DC/DC&AC/DC(SR) Sub-systems

## **GENERAL DESCRIPTION**

OSM7N65 是一款在栅源电压 10V 时可实现最大  $1.7\Omega$  导通阻抗,7A 持续电流的 650V N 沟道 MOS 器件。

OSM7N65 具有低栅极电荷,低栅极电压,和高电流导通能力。适用于负载开关、PWM 控制等应用场景。

OSM7N65采用 TO-220-FB 封装。

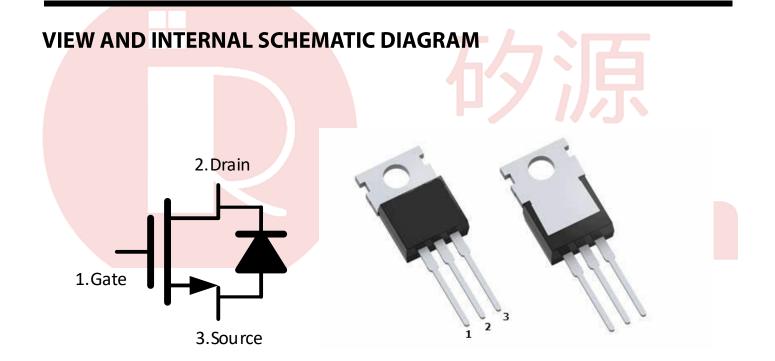

Figure 1. View and Internal Schematic Diagram

## **SPECIFICATIONS**

Table 1. Typical and limits appearing in normal type apply for  $T_A = 25$ °C, unless otherwise noted.

| Parameter                         | Symbol              | Conditions                                                            | Min | Тур  | Max  | Unit |

|-----------------------------------|---------------------|-----------------------------------------------------------------------|-----|------|------|------|

| Static Parameters                 | - 1                 |                                                                       | ı   | •    |      |      |

| Source-Source Breakdown Voltage   | BV <sub>DSS</sub>   | V <sub>GS</sub> =0V, I <sub>SS</sub> =250μA                           | 650 |      |      | V    |

| Zero Gate Voltage Drain Current   | I <sub>DSS</sub>    | V <sub>DSS</sub> =650V, V <sub>GS</sub> =0V                           |     |      | 1    | μΑ   |

| Gate-Body leakage current         |                     | $V_{DSS} = 0V, V_{GS} = +30V$                                         |     |      | 0.1  | μΑ   |

| Gate-body leakage current         | l <sub>GSS</sub>    | $V_{DSS} = 0V, V_{GS} = -30V$                                         |     |      | -0.1 | μΑ   |

| Gate Threshold Voltage            | $V_{GS(TH)}$        | $V_{DSS} = V_{GS}$ , $I_{SS} = 250 \mu A$                             | 2   |      | 4    | ٧    |

| Static Drain-Source On-Resistance | R <sub>DS(ON)</sub> | V <sub>GS</sub> =10V, I <sub>SS</sub> =3.5A                           |     | 1.2  | 1.4  | Ω    |

| Diode Forward Voltage             | V <sub>FSS</sub>    | V <sub>GS</sub> =0V, I <sub>F</sub> =7A                               |     |      | 1.2  | ٧    |

|                                   |                     |                                                                       |     | _    |      |      |

| Input Capacitance*1               | C <sub>ISS</sub>    |                                                                       |     | 1130 |      | рF   |

| Output Capacitance*1              | Coss                | V <sub>GS</sub> =0V, V <sub>DS</sub> =25V, f=1MHz                     |     | 93   |      | рF   |

| Reverse Transfer Capacitance*1    | C <sub>RSS</sub>    |                                                                       |     | 5.5  |      | рF   |

| Switching Parameters              |                     |                                                                       |     |      |      |      |

| Total Gate Charge*1               | Qg                  | TA                                                                    |     | 24   |      | nC   |

| Gate Source Charge*1              | $Q_{gs}$            | V <sub>GS</sub> =0 to 10V, V <sub>DS</sub> =520V, l <sub>SS</sub> =7A |     | 5.1  |      | nC   |

| Gate Drain Charge*1               | $Q_{\mathrm{gd}}$   |                                                                       | 11  | 9.5  |      | nC   |

| Turn-On Delay Time*1,2            | t <sub>D(ON)</sub>  |                                                                       | 17  | 19   |      | ns   |

| Turn-On Rise Time*1,2             | <b>t</b> r          | V <sub>DSS</sub> =350V, I <sub>D</sub> =7A,R <sub>G</sub> =25Ω        |     | 21   |      | ns   |

| Turn-Off Delay Time*1,2           | t <sub>D(OFF)</sub> | VDSS-330V, ID-7A,nG-2312                                              |     | 42   |      | ns   |

| Turn-Off Fall Time*1,2            | t <sub>f</sub>      |                                                                       |     | 19   |      | ns   |

| ote: 1. 参数由设计保证<br>2. 测量修正。       |                     |                                                                       |     |      |      |      |

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                            | Rating          |

|--------------------------------------|-----------------|

| VDSS(ON)                             | 650 <b>V</b>    |

| VGS                                  | ±30V            |

| ISS(DC)                              | 7A              |

| ISS(Pulse)                           | 28A             |

| Storage Temperature Range            | −65°C to +150°C |

| Operating Junction Temperature Range | −40°C to +125°C |

| Operating Ambient Temperature Range  | −40°C to +85°C  |

| Soldering Conditions                 | JEDEC J-STD-020 |

注意,超出上述绝对最大额定值可能会导致器件永久性损坏。 这只是额定应力值,不涉及器件在这些或任何其他条件下 超出本技术规格指标的功能性操作。长期在绝对最大额定 值条件下工作会影响器件的可靠性。

#### THERMAL DATA

绝对最大额定值仅适合单独应用,但不适合组合使用。结温高于限制值时,会损坏芯片。监控环境温度并不能保证 T<sub>1</sub> 不会超出额定温度限值。在功耗高、热阻差的应用中,可能必须降低最大环境温度。

在功耗适中、PCB 热阻较低的应用中,只要结温处于额定限值以内,最大环境温度可以超过最大限值。器件的结温( $T_{\rm J}$ )取决于环境温度( $T_{\rm A}$ )、器件的功耗( $P_{\rm D}$ )和封装的结到环境热阻( $\theta_{\rm JA}$ )。

最高结温(T」)由环境温度(TA)和功耗(Pb)通过下式计算:

$$T_J = T_A + (P_D \times \theta_{JA})$$

封装的结到环境热阻 (θ<sub>JA</sub>) 基于使用 4 层板的建模和计算方法,主要取决于应用和板布局。在功耗较高的应用中,需

要特别注意热板设计。 $\theta_{JA}$  的值可能随 PCB 材料、布局和环境条件不同而异。 $\theta_{JA}$  的额定值基于  $4" \times 3"$  的 4 层电路板。有关板结构的详细信息,请参考 JESD 51-7 和 JESD 51-9。

$\Psi_{IB}$  是结到板热特性参数,单位为 °C/W. 封装的  $\Psi_{IB}$  基于使用 4 层板的建模和计算方法。JESD51-12——"报告和使用电子封装热信息指南"中声明,热特性参数和热阻不是一回事。  $\Psi_{IB}$  衡量沿多条热路径流动的器件功率,而  $\theta_{IB}$  只涉及一条路径。因此,  $\Psi_{IB}$  热路径包括来自封装顶部的对流和封装的辐射,这些因素使得  $\Psi_{IB}$  在现实应用中更有用。最高结温  $(T_{IB})$  由板温度  $(T_{IB})$  和功耗  $(P_{O})$ 通过下式计算:

$$T_I = T_B + (P_D \times \Psi_{JB})$$

有关 Ψ<sub>B</sub> 的详细信息,请参考 JESD51-8 和 JESD51-12。

#### THERMAL RESISTANCE

$\theta_{JA}$ 和  $\Psi_{JB}$ 针对最差条件,即器件焊接在电路板上以实现表贴封装。

Table 3. Thermal Resistance

| Package Type | θ <sub>JA</sub> | θις  | Unit  |

|--------------|-----------------|------|-------|

| TO-220-FB    | 62.5            | 0.89 | °C /W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration (Bottom View)

| Table 4. Pir | n Function Desc   | riptions      | 五人》:"否   |

|--------------|-------------------|---------------|----------|

| Pin No.      | Mnemonic Mnemonic | Description   |          |

| 1            | G                 | MOSFET Gate   |          |

| 2            | D                 | MOSFET Drain  | , / W.J. |

| 3            | S                 | MOSFET Source |          |

- 1. = PIN1

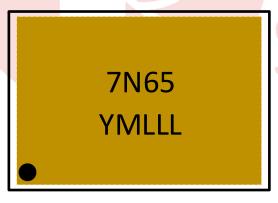

- 2. 7N65 = Device Name

- 3.Y = Year

- 4. M = Month

- 5. LLL = Trace No

Figure 3. Making View

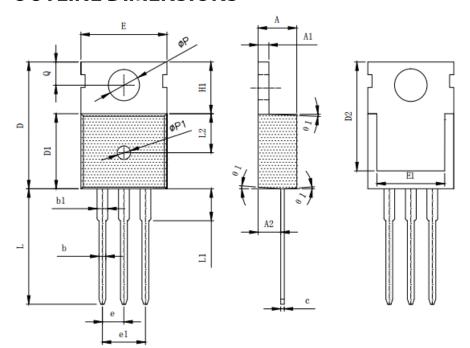

# **OUTLINE DIMENSIONS**

| SYMBOL | MILLIMETER  |        |        |  |

|--------|-------------|--------|--------|--|

| SIMBOL | MIN         | NOM    | MAX    |  |

| A      | 4. 40       | 4. 50  | 4. 60  |  |

| Al     | 1. 25       | 1. 30  | 1. 35  |  |

| A2     | 2. 30       | 2.40   | 2. 50  |  |

| b      | 0.70        | 0.80   | 0. 90  |  |

| bl     | 1. 25       | 1. 35  | 1. 45  |  |

| c      | 0. 40       | 0. 50  | 0. 60  |  |

| D      | 15. 50      | 15. 80 | 16. 10 |  |

| D1     | 9. 10       | 9. 20  | 9. 30  |  |

| D2     | 12. 73      | 12.83  | 12. 93 |  |

| E      | 9. 70       | 9. 90  | 10. 20 |  |

| E1     | 7. 60       | 8. 00  | 8. 40  |  |

| e      | 2. 54 (BSC) |        |        |  |

| el     | 5. 08 (BSC) |        |        |  |

| HI     | 6. 30       | 6. 50  | 6. 80  |  |

| L      | 12. 75      | 13.08  | 13. 50 |  |

| L1     |             |        | 3. 10  |  |

| L2     | 4. 30       | 4. 60  | 4. 90  |  |

| φP     | 3. 50       | 3. 60  | 3. 70  |  |

| øP1    | 1.40        | 1. 50  | 1. 60  |  |

| a      | 2. 70       |        | 2. 90  |  |

| 0 1    | 2*          | 4*     | 6*     |  |

Figure 4. TO-220-FB

## 版本说明

| 版本  | 改动页码 | 改动图片 | 改动内容 | 改动公式 | 备注      |

|-----|------|------|------|------|---------|

| 1.0 |      |      |      |      | initial |

|     |      |      |      |      |         |

|     |      |      |      |      |         |