#### 具有 2.5V 内部基准电压的 8 通道、16 位、电压输出的数模转换器

## 概述

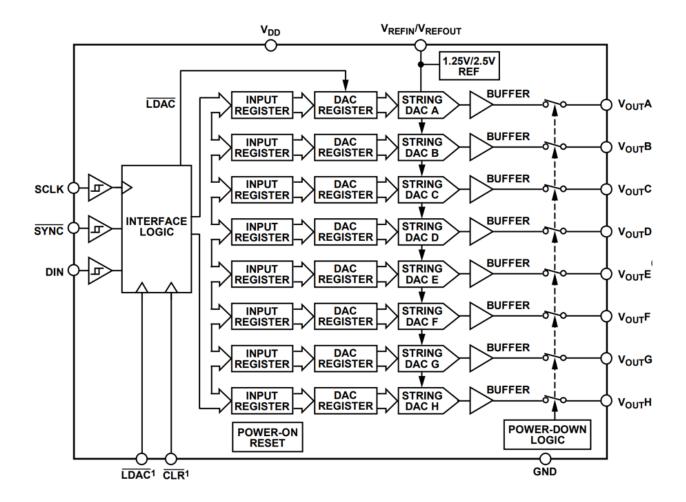

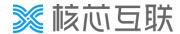

CL4658 是一款低功耗、8 通道、16 位缓冲电压输出 DAC(数模转换器),采用  $4.5\,\mathrm{V}$  至  $5.5\,\mathrm{V}$  单电源供电,通过设计保证单调性。CL4658 提供  $16\,\mathrm{J}$  脚 QFN 和 TSSOP 两种封装。

CL4658 内置一个 2.5V、5 ppm/°C 基准电压源,内部增益为 2,满量程输出范围可达到 5V。上电时片内基准电压源关闭,因而可以使用外部基准电压源。内部基准电压源通过软件写入使能。

CL4658 内置一个上电复位电路,确保 DAC 上电后输出中间电平并保持该电平,直到执行一次有效的写操作为止。此外还具有各通道独立关断特性,在关断模式下,器件在 5 V 时的功耗降至典型值 1.8uA,并提供软件可选输出负载。利用LDAC功能可以同时更新所有 DAC 的输出,用户也可以选择要同时更新的 DAC 通道。另外还有一个异步CLR功能,可以将所有 DAC 更新至一个用户可编程的编码:零电平、中间电平或满量程。

CL4658 采用多功能三线式串行接口,能够以最高 50MHz 的时钟速率工作,并与标准 SPI、QSPI、MICROWIRE、DSP 接口标准兼容。它内置片内精密输出放大器,能够实现轨到轨输出摆幅。

## 特性

- 低功耗、小尺寸、引脚兼容的 8 通道 DAC

- 4.5V 至 5.5V 供电

- 2.5V、5 ppm/°C 片内基准电压源

- 提供 16 引脚 TSSOP 和 QFN 封装

- 上电复位至中间电平/零电平

- 关断功能。关断模式下,功耗典型值为 1.8uA

- CLR功能,清零至可编程编码

- LDAC覆盖功能

- 轨到轨输出摆幅

- 通用三线 SPI 接口

## 应用

- 过程控制

- 数据采集系统

- 便携式电池供电仪表

- 数字增益和失调电压调整

- 可编程电压源和电流源

- 可编程衰减器

## 功能框图

图 1 功能框图

## 目录

| 概述        |    |

|-----------|----|

|           |    |

| 应用        |    |

| 力能框图      |    |

| 技术规格      |    |

| 交流特性      |    |

| 时序特性      |    |

| 绝对最大额定值   |    |

| 引脚配置和功能描述 |    |

| 工作原理与功能   |    |

| 寄存器列表     |    |

| 外形尺寸      | 17 |

| 订购信息      |    |

#### 版本历史

2023年5月31日星期三: Rev 1.0

## 技术规格

VDD=4.5V 至 5.5V,  $R_L$ =2KΩ 接 GND,  $C_L$ =200pF 接 GND,  $V_{REFIN}$ =2.5V。除非另有说明,所有规格均相对于 $T_{MIN}$ 至 $T_{MAX}$ 而言。

表格1

| 参数                          | 最小值   | 典型值 2 | 最大值                 | 单位     | 条件注释                         |

|-----------------------------|-------|-------|---------------------|--------|------------------------------|

| 静态性能                        |       |       |                     |        |                              |

| 分辨率                         | 16    |       |                     | 位      | 输入码范围: 0~65535               |

| 微分非线性(DNL)                  |       |       | ±1                  | LSB    |                              |

| 积分非线性(INL)                  |       | ±1    | ±4                  | LSB    |                              |

| 增益误差                        |       |       | $\pm 0.1$           | %FSR   | 1/4 到 3/4 输出量程               |

| 失调误差                        |       | ±1    | ±4                  | mV     | 输出电压为中间值                     |

| 直流电源抑制比1                    |       | -80   |                     | dB     | VDD±10%,输出电压为中间值             |

| 通道直流串扰1                     |       | 15    |                     | μV     | 外部基准模式                       |

|                             |       | 500   |                     | μV     | 内部基准模式                       |

| 输出特性1                       |       |       |                     |        |                              |

| 输出电压                        | 0     |       | ${ m V_{DD}}$       | V      | 输出范围: 0~2*V <sub>REFIN</sub> |

| 容性负载稳定性                     |       | 2     |                     | nF     | $R_L = \infty$               |

|                             |       | 10    |                     | nF     | $R_L=2k\Omega$               |

| 短路电流                        |       | 34    |                     | mA     | $V_{DD}=5V$                  |

| 上电时间                        |       | 5     |                     | μs     | 外部基准模式                       |

| (退出关断模式)                    |       | 1.25  |                     | ms     | 内部基准模式                       |

| 参考输入 <sup>1</sup>           |       |       |                     |        |                              |

| 基准电流                        |       |       | 100                 | nA     |                              |

| 基准输入范围                      | 0     |       | $V_{\mathrm{DD}}/2$ | V      |                              |

| 基准输入阻抗                      | 50    |       |                     | ΜΩ     |                              |

| 基准输出                        |       |       |                     |        |                              |

| 输出电压                        | 2.495 |       | 2.505               | V      | 环境温度                         |

| 基准电压温漂                      |       | 5     | 10                  | ppm/°C | 温度范围: -40°C 至+85°C           |

| 逻辑输入1                       |       |       |                     |        |                              |

| 输入电流                        |       |       | ±3                  | μΑ     | 所有数字输入                       |

| 输入低电压V <sub>INL</sub>       |       |       | 0.8                 | V      | $V_{DD}=5V$                  |

| 输入高电压V <sub>INH</sub>       | 2     |       |                     | V      | $V_{DD}=5V$                  |

| 引脚电容                        |       | 3     |                     | pF     |                              |

| 电源要求                        |       |       |                     |        |                              |

| $V_{ m DD}$                 | 4.5   |       | 5.5                 | V      | 所有数字输入为0或VDD                 |

| V DD                        | 4.5   |       | 5.5                 | v      | DAC 八通道启用输出 0V               |

| I <sub>DD</sub> (正常模式)      |       |       |                     |        | 不包括负载电流                      |

| V <sub>DD</sub> =4.5 至 5.5V |       | 3.2   |                     | mA     | 内部基准电压源关闭                    |

| V <sub>DD</sub> =4.5 至 5.5V |       | 4.0   |                     | mA     | 内部基准电压源开启                    |

| I <sub>DD</sub> (全关断模式)     |       |       |                     |        |                              |

| V <sub>DD</sub> =4.5 至 5.5V |       | 1.8   |                     | μΑ     | 所有8个DAC均关断                   |

<sup>1</sup> 通过设计和特性保证,但未经生产测试。

<sup>2</sup> 温度范围: -40℃ 至+85℃, 典型值 25℃。

#### 交流特性

VDD=4.5V 至 5.5V,  $R_L$ =2KΩ 接 GND,  $C_L$ =200pF 接 GND,  $V_{REFIN}$ =2.5V。除非另有说明,所有规格均相对于 $T_{MIN}$ 至 $T_{MAX}$ 而言。

表格 2

| 参数 1     | 最小值 | 典型值  | 最大值 | 单位             | 条件/注释                      |

|----------|-----|------|-----|----------------|----------------------------|

| 输出电压建立时间 |     | 3    |     | μs             | 1/4 到 3/4 输出量程 建立到±2LSB    |

| 压摆率      |     | 0.84 |     | V/µs           |                            |

| 总谐波失真    |     | -60  |     | dB             | VREF=2V±0.1Vp-p,频率=10kHz   |

| 输出噪声频谱密度 |     | 158  |     | $nV/\sqrt{Hz}$ | DAC 编码 = 0x8000,10kHz      |

|          |     | 128  |     | $nV/\sqrt{Hz}$ | DAC 编码 = 0x8000,1 kHz      |

| 输出噪声     |     | 12   |     | μVp-p          | 0.1Hz 至 10Hz,DAC 编码=0x0000 |

<sup>1</sup> 通过设计和特性保证,但未经生产测试。

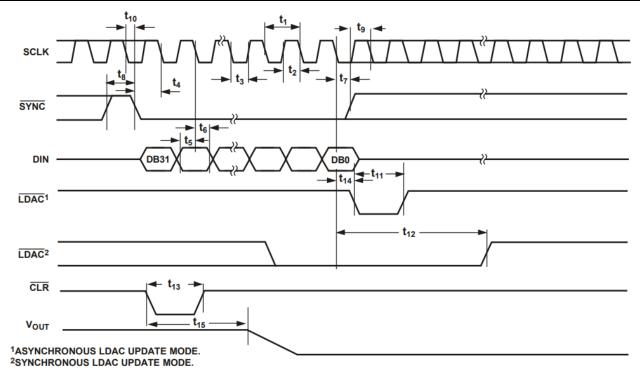

#### 时序特性

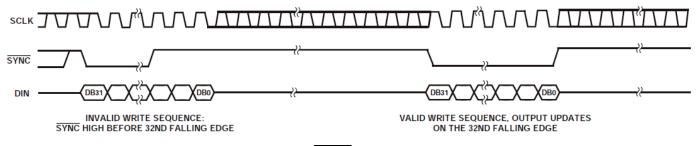

所有输入信号均指定 $t_R=t_F=1$ ns/V(10%至 90%的 VDD)并从( $V_{IL}+V_{IH}$ )/2 电平开始计时。参数在时序图中的标注见图 2。 $V_{DD}=4.5$ V 至 5.5V。所有规格均为 $T_{MIN}$ 至 $T_{MAX}$ ,除另有说明。

表格 3

| 参数 1     | 在T <sub>MIN</sub> 至T <sub>MAX</sub> 的限值<br>VDD=4.5V 至 5.5V | 单位      | 条件/注释               |  |  |  |  |  |

|----------|------------------------------------------------------------|---------|---------------------|--|--|--|--|--|

| $t_1$    | 20                                                         | ns(最小值) | SCLK 周期时间           |  |  |  |  |  |

| $t_2$    | 8                                                          | ns(最小值) | SCLK 高电平时间          |  |  |  |  |  |

| $t_3$    | 8                                                          | ns(最小值) | SCLK 低电平时间          |  |  |  |  |  |

| $t_4$    | 13                                                         | ns(最小值) | SYNC到 SCLK 下降沿建立时间  |  |  |  |  |  |

| $t_5$    | 4                                                          | ns(最小值) | 数据建立时间              |  |  |  |  |  |

| $t_6$    | 4                                                          | ns(最小值) | 数据保持时间              |  |  |  |  |  |

| $t_7$    | 0                                                          | ns(最小值) | SCLK 下降沿到SYNC上升沿    |  |  |  |  |  |

| $t_8$    | 15                                                         | ns(最小值) | 最小SYNC高电平时间         |  |  |  |  |  |

| $t_9$    | 13                                                         | ns(最小值) | SYNC上升沿到 SCLK 下降沿忽略 |  |  |  |  |  |

| $t_{10}$ | 0                                                          | ns(最小值) | SCLK 下降沿到SYNC下降沿忽略  |  |  |  |  |  |

| $t_{11}$ | 10                                                         | ns(最小值) | LDAC低电平脉冲宽度         |  |  |  |  |  |

| $t_{12}$ | 15                                                         | ns(最小值) | SCLK 下降沿到LDAC上升沿    |  |  |  |  |  |

| $t_{13}$ | 5                                                          | ns(最小值) | CLR低电平脉冲宽度          |  |  |  |  |  |

| $t_{14}$ | 0                                                          | ns(最小值) | SCLK 下降沿到LDAC下降沿    |  |  |  |  |  |

| $t_{15}$ | 300                                                        | ns(最小值) | CLR脉冲启动时间           |  |  |  |  |  |

<sup>1</sup> 通过设计和特性保证,但未经生产测试。

图 2 串行写入操作

## 绝对最大额定值

除非另有说明, T<sub>A</sub>=25℃。

表格 4

| 参数                                           | 额定值                           |  |  |  |  |  |  |

|----------------------------------------------|-------------------------------|--|--|--|--|--|--|

| V <sub>DD</sub> 至 GND                        | -0.3V 至 +7V                   |  |  |  |  |  |  |

| 数字输入电压至 GND                                  | -0.3V 至 V <sub>DD</sub> +0.3V |  |  |  |  |  |  |

| V <sub>OUT</sub> 至 GND                       | -0.3V 至 V <sub>DD</sub> +0.3V |  |  |  |  |  |  |

| V <sub>REFIN</sub> /V <sub>REFOUT</sub> 至GND | -0.3V 至 V <sub>DD</sub> +0.3V |  |  |  |  |  |  |

| 工作温度范围                                       | -40°C 至 +85°C                 |  |  |  |  |  |  |

| 存储温度范围                                       | -65°C 至 +150°C                |  |  |  |  |  |  |

| 结温                                           | 150°C                         |  |  |  |  |  |  |

| 热阻                                           | 150.4°C/W                     |  |  |  |  |  |  |

| 铅锡焊接温度 回流焊(10 秒至 30 秒)                       | 240°C                         |  |  |  |  |  |  |

| 无铅回流焊温度                                      | 260°C                         |  |  |  |  |  |  |

注意,超出上述绝对最大额定值可能会导致器件永久性损坏。这只是额定最值,并不能以这些条件或者在任何 其它超出本技术规范操作章节中所示规格的条件下,推断器件能否正常工作。长期在绝对最大额定值条件下工作会 影响器件的可靠性。

### ESD警告

#### ESD(静电放电)敏感器件。

带电器件和电路板可能会在没有察觉的情况下放电。尽管本产品具有专利或专有保护电路,但在遇到高能量ESD时,器件可能会损坏。因此,应当采取适当的ESD防范措施,以避免器件性能下降或功能丧失。

## 引脚配置和功能描述

Voute 4

Voute 5

Voute 6

Voute 7

Voute 8

Voute 7

Voute 8

Voute 7

Vou

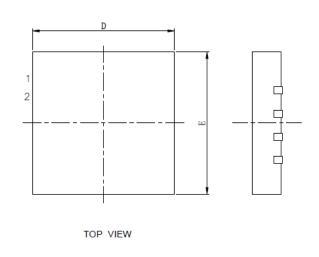

图 416 引脚 QFN

表 5 引脚功能描述

| 表 5 引脚切能描述 |       | 1                    |                                        |

|------------|-------|----------------------|----------------------------------------|

|            | P编号   |                      |                                        |

| 16 引脚      | 16 引脚 | £                    | THAN                                   |

| TSSOP      | QFN   | 名称                   | 描述                                     |

| 1          | 15    | LDAC                 | 发送脉冲使该引脚变为低电平后,当输入寄存器有新数据时,可以更         |

|            |       |                      | 新任意或全部 DAC 寄存器。因此,所有 DAC 输出可以同时更新。     |

|            |       |                      | 也可以将该引脚永久接为低电平。                        |

| 2          | 16    | SYNC                 | 低电平有效控制输入。这是输入数据的帧同步信号。当 SYNC 变为       |

|            |       |                      | 低电平时,SCLK 和 DIN 缓冲器上电,输入移位寄存器使能。数据     |

|            |       |                      | 在后续 32 个时钟的下降沿读入。如 果 SYNC 在第 32 个下降沿之前 |

|            |       |                      | 变为高电平,SYNC 的上升沿将用作中断,器件将忽略 写入序列。       |

| 3          | 1     | VDD                  | 电源输入引脚。这些器件可以采用 4.5V 至 5.5V 电源供电,电源应通  |

|            |       |                      | 过并联的 10μF 电容和 0.1μF 电容去耦至 GND。         |

| 4          | 2     | V <sub>out</sub> A   | DAC A 的模拟输出电压。输出放大器能以轨到轨方式工作。          |

| 13         | 11    | V <sub>out</sub> B   | DAC B 的模拟输出电压。输出放大器能以轨到轨方式工作。          |

| 5          | 3     | V <sub>out</sub> C   | DAC C 的模拟输出电压。输出放大器能以轨到轨方式工作。          |

| 12         | 10    | V <sub>out</sub> D   | DAC D 的模拟输出电压。输出放大器能以轨到轨方式工作。          |

| 8          | 6     | V <sub>REFIN</sub> / | CL4658 有一个用于基准输入和输出的公用引脚。使用内部基准电压      |

|            |       | V <sub>REFOUT</sub>  | 源时,此引脚为基准输出。使用外部基准电压源时,此引脚为基准输         |

|            |       |                      | 入。此引脚默认用作基准输入。作为基准输出引脚时,建议在基准电         |

|            |       |                      | 压输出与 GND 之间放置一个 100nF 电容, 使基准电压保持稳定。   |

| 9          | 7     | CLR                  | 异步清零输入。CLR输入对下降沿敏感。当CLR为低电平时,所有        |

|            |       |                      | LDAC脉冲都被忽略。当CLR有效时,输入寄存器和 DAC 寄存器更     |

|            |       |                      | 新为 CLR 编码寄存器内的数据:零电 平、中间电平或满量程。默认      |

|            |       |                      | 设置是输出清零至0V                             |

| 6          | 4     | V <sub>out</sub> E   | DACE的模拟输出电压。输出放大器能以轨到轨方式工作。            |

| 11         | 9     | V <sub>out</sub> F   | DAC F 的模拟输出电压。输出放大器能以轨到轨方式工作。          |

CL4658

| 7  | 5    | $V_{out}G$         | DAC G 的模拟输出电压。输出放大器能以轨到轨方式工作。  |

|----|------|--------------------|--------------------------------|

| 10 | 8    | V <sub>out</sub> H | DAC H 的模拟输出电压。输出放大器能以轨到轨方式工作。  |

| 14 | 12   | GND                | 器件上所有电路的接地基准点                  |

| 15 | 13   | DIN                | 串行数据输入。该器件有一个32位移位寄存器。数据在串行时钟输 |

|    |      |                    | 入的下降沿读入 寄存器。                   |

| 16 | 14   | SCLK               | 串行时钟输入。数据在串行时钟输入的下降沿读入移位寄存器。数据 |

|    |      |                    | 能够以最高 50 MHz 的速率传输。            |

|    | EPAD | EPAD               | 建议将裸露焊盘焊接到接地层。                 |

## 工作原理与功能

#### 数模转换部分

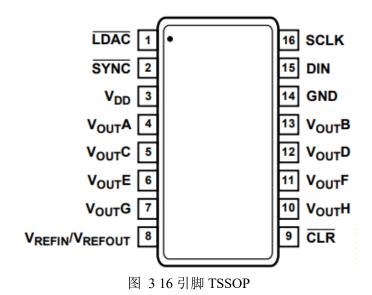

CL4658 DAC 采用 CMOS 工艺制造,由一串 DAC 和一个输出缓冲放大器构成。每个器件均内置一个 2.5V、5ppm/°C 基准电压源,其内部增益为 2。图 5 为 DAC 架构框图。

图 5 DAC 结构

DAC 的输入编码为直接二进制, 无论使用内部基准电压源还是外部基准电压源,模拟电压的理想输出公式均为:  $V_{\text{OUT}} = 2 * V_{\text{REFIN/OUT}} * (D / 2^{N})$

其中,D是载入DAC寄存器的二进制编码的十进制等效值,N是分辨率。CL4658是 16位 DAC,D的范围是 0至 65535,N是 16, $V_{REFIN/OUT}$ 是内部/外部基准电压值。

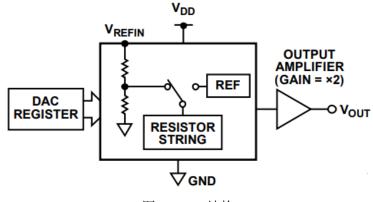

#### 电阻串

电阻串部分如图 6 所示。它由一串电阻和开关组成,各电阻的阻值为 R。载入 DAC 寄存器的编码决定抽取电阻串上哪一个节点的电压,以馈入输出放大器。抽取电压的方法是将连接电阻串与放大器的开关之一闭合。由于它是一串电阻,因此可以保证单调性。

图 6 电阻串

#### 内部基准电压

CL4658 内置一个 2.5 V、5 ppm/°C 片内基准电压源,内部增益为 2。上电时,片内基准电压源关闭,可以使用外部基准电压源。各器件的内部基准电压通过 $V_{REFOUT}$ 引脚输出。如果利用基准电压输出驱动外部负载,则需要使用缓冲器。使用内部基准电压源时,建议在基准电压输出与 GND 之间放置一个 100nF 电容,使基准电压保持稳定。

#### 输出放大器

输出缓冲放大器可以在其输出端产生轨到轨电压,输出范围为 0V 至 VDD。它能驱动连接至 GND 的一个与 200pF 电容 并联的 2kΩ 负载。

#### 串行接口

写序列通过将SYNC线置为低电平来启动。来自 DIN 线的数据在 SCLK 的下降沿进入 32 位移位寄存器。串行时钟频率最高可以达到 50MHz,因而 CL4658 能与高速 DSP 兼容。在第 32 个时钟下降沿,最后一位数据被读入,编程功能执行完毕,DAC 寄存器内容和/或工作模式会改变。在这个阶段,SYNC线可以保持在低电平或置为高电平。在任意一种情况下,必须在下一个写序列之前保持至少 15 ns 的高电平,这样才能用SYNC下降沿启动下一个写序列。SYNC在写序列之间空闲时应为低电平,以进一步降低器件功耗。如前所述,在下次写序列前,SYNC必须被置为高电平。

#### 输入移位寄存器

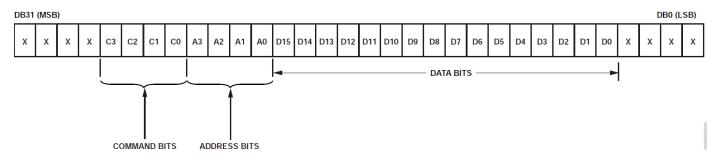

输入移位寄存器为 32 位宽。前 4 位是无关位,后续 4 位是命令位 C3 至 C0(参见表 6),然后是 4 位 DAC 地址 A3 至 A0(参见表 7),最后是 20 位数据字。CL4658 的数据字包括 16 位输入编码和 4 个无关位(参见图 7)。这些数据 位在 SCLK 的第 32 个下降沿被送入 DAC 寄存器。

表格 6 命今定 ₹

| 1CTH 0 | 叩令正义 | -  |    |                                       |

|--------|------|----|----|---------------------------------------|

| 命令     |      |    |    | 描述                                    |

| С3     | C2   | C1 | C0 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| 0      | 0    | 0  | 0  | 写入输入寄存器 n                             |

| 0      | 0    | 0  | 1  | 更新 DAC 寄存器 n                          |

| 0      | 0    | 1  | 0  | 写入输入寄存器 n, 更新全部                       |

| 0      | 0    | 1  | 1  | 写入并更新 DAC 通道 n                        |

| 0      | 1    | 0  | 0  | DAC 掉电/上电                             |

| 0      | 1    | 0  | 1  | 加载清零编码寄存器                             |

| 0      | 1    | 1  | 0  | 加载LDAC寄存器                             |

| 0      | 1    | 1  | 1  | 复位(上电复位)                              |

| 1      | 0    | 0  | 0  | 设置内部 REF 寄存器                          |

| 1      | 0    | 0  | 1  | 保留                                    |

| -      | -    | -  | -  | 保留                                    |

| 1      | 1    | 1  | 1  | 保留                                    |

表格 7 地址定义

| 命令 |    |    |    | <b>冰阜的 D 4 C 海</b> 类 |  |  |  |  |  |  |  |  |

|----|----|----|----|----------------------|--|--|--|--|--|--|--|--|

| A3 | A2 | A1 | A0 | · 选定的 DAC 通道         |  |  |  |  |  |  |  |  |

| 0  | 0  | 0  | 0  | DAC A                |  |  |  |  |  |  |  |  |

| 0  | 0  | 0  | 1  | DAC B                |  |  |  |  |  |  |  |  |

| 0  | 0  | 1  | 0  | DAC C                |  |  |  |  |  |  |  |  |

| 0  | 0  | 1  | 1  | DAC D                |  |  |  |  |  |  |  |  |

| 0  | 1  | 0  | 0  | DAC E                |  |  |  |  |  |  |  |  |

| 0  | 1  | 0  | 1  | DAC F                |  |  |  |  |  |  |  |  |

| 0  | 1  | 1  | 0  | DAC G                |  |  |  |  |  |  |  |  |

| 0  | 1  | 1  | 1  | DAC H                |  |  |  |  |  |  |  |  |

| 1  | 1  | 1  | 1  | 所有 DAC 通道            |  |  |  |  |  |  |  |  |

图 7 CL4658 输入寄存器内容

#### SYNC中断

在正常写序列中,SYNC在 32 个 SCLK 的下降沿保持为低电平,DAC 会在 SCLK 的第 32 个下降沿和SYNC的上升沿更新。如果在第 32 个下降沿之前SYNC被拉高,写序列就会被中断。移位寄存器会复位,写序列被认为是无效的。不会造成 DAC 寄存器内容的更新和工作模式的改变(参见图 8)。

图 8 SYNC中断设置

#### 内部基准电压源寄存器

片内基准电压源在上电时默认关闭。如果应用要求,可以使用外部基准电压源。将用户可编程的内部 REF 寄存器的位 DBO 设为高电平或低电平,可以开启或关闭片内基准电压源(参见寄存器列表)。命令 1000 用于内部 REF 寄存器的设置(参见表 6)。

#### 上电复位

CL4658 具有上电复位电路可以在上电时控制输出电压。在上电后输出 0 V 或者中间电平。输出一直保持该电平,直到对 DAC 执行有效的写序列。这对于在上电过程中需要了解 DAC 输出状态的应用来说很重要。还有一个软件可执行的复位功能,它可将 DAC 复位至上电复位代码。命令 0111 保留用于该复位功能(参见表 6)。上电复位期间,LDAC或CLR上的所有事件都会被忽略。

#### 掉电模式

CL4658 具有四种独立的工作模式。命令 0100 用于关断功能(参见表 6)。这些模式可通过软件编程,设置控制寄存器中的两位(DB9 和 DB8)进行选择。寄存器列表列出了这些位的状态与器件工作模式的对应关系和关断/上电期间输入移位寄存器的内容。将相应的 8 位(DB7 至 DB0)设为 1,任意或所有 DAC(DAC H 至 DAC A)都可以关断到选定的模式。

输出级也从放大器输出切换为已知值的电阻网络,这是有好处的,因为在掉电模式下器件的输出阻抗是已知的。有三种不同的选项:输出通过  $1 \, k \Omega$  电阻或  $100 \, k \Omega$  电阻内部连接到 GND,或者保持开路状态(三态)。

在关断模式有效时,选定 DAC 的偏置发生器、输出放大器、电阻串以及其它相关线性电路全部关闭。内部基准电压源仅在所有通道均关断时才关断。然而,掉电期间 DAC 寄存器的内容不受影响。将 PD1 和 PD0 设为 0(正常工作),可以使任意 DAC 组合上电。上电后,输出为输入寄存器中的值(LDAC为低电平),或者输出为关断前 DAC 寄存器中的值(LDAC为高电平)。

#### 清零编码寄存器

CL4658 具有一个硬件异步清零输入引脚CLR。CLR输入对下降沿敏感。通过将CLR引脚置为低电平,可以将输入寄存器和 DAC 寄存器的内容清零至用户可配置CLR寄存器中的数据,并相应地设置模拟输出。此功能在系统校准中可用于将零电平、中间电平或满量程同时载入所有通道。通过设置CLR控制寄存器中的两位 DB1 和 DB0,用户可以对这些清零编码值进行编程(详情参见寄存器列表)。默认设置是输出清零至 0 V。命令 0101 用于加载清零编码寄存器(参见表 6)。器件在下一次写操作的第 32 个下降沿退出清零编码模式。如果CLR在写序列期间有效,写操作将被中止。

#### LDAC功能

利用硬件LDAC引脚可以同时更新所有 DAC 的输出。

同步LDAC: 读入新数据后, DAC 寄存器在第 32 个 SCLK 脉冲的下降沿更新。LDAC可以永久接为低电平,或者为脉冲形式,如图 2 所示。

异步LDAC:输出不在写入输入寄存器的同时更新。当LDAC变为低电平时,DAC 寄存器更新为输入寄存器的内容。

利用软件 $\overline{LDAC}$ 功能,写入输入寄存器 n 并更新所有 DAC 寄存器,也可以同时更新所有 DAC 的输出。命令 0011 用于该软件 $\overline{LDAC}$ 功能。

利用LDAC寄存器,用户可以更加灵活地控制硬件LDAC引脚。该寄存器允许用户选择在执行硬件LDAC引脚时同时更新哪些通道。如果将LDAC位寄存器的某一 DAC 通道设为 0,则意味着该通道的更新受LDAC引脚的控制。如果该位设为 1,则该通道同步更新,即 DAC 寄存器在读入新数据后更新,与LDAC引脚的状态无关,此时LDAC引脚被视为接低电平。(有关LDAC寄存器的工作模式,请参见表 8。)在用户希望同时更新选定的通道,而其余通道同步更新的应用中,这种灵活性十分有用。

使用命令 0110 写入 DAC 将加载 8 位LDAC寄存器(DB7 至 DB0)。各通道的默认值为 0,即LDAC引脚正常工作。如果将某一位设为 1,则意味着无论LDAC引脚的状态如何,对应的 DAC 通道都会更新。寄存器列表中列出了加载LDAC寄存器工作模式期间输入移位寄存器的内容。

#### 表格 8 LDAC 寄存器

| 加载 DAC 寄存器       |         | TD to LE lle                        |  |  |  |  |  |  |  |

|------------------|---------|-------------------------------------|--|--|--|--|--|--|--|

| LDAC位(DB7 至 DB0) | LDAC 引脚 | LDAC 操作                             |  |  |  |  |  |  |  |

| 0                | 1/0     | 由LDAC引脚决定。                          |  |  |  |  |  |  |  |

| 1                | X (无关位) | DAC 通道更新,覆盖LDAC引脚。DAC 通道视 LDAC 为 0。 |  |  |  |  |  |  |  |

## 寄存器列表

| DB31<br>-<br>DB28 | DB27       | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20     | DB19 | DB18     | DB17 | DB16<br>-<br>DB10 | DB9      | DB8 | DB7      | DB6      | DB5      | DB4      | DB3      | DB2      | DB1      | DB0      | 描述                                                                                   |

|-------------------|------------|------|------|------|------|------|------|----------|------|----------|------|-------------------|----------|-----|----------|----------|----------|----------|----------|----------|----------|----------|--------------------------------------------------------------------------------------|

| 无关<br>位           | СЗ         | C2   | C1   | C0   | А3   | A2   | A1   | A0       | D15  | D14      | D13  | D12-<br>D6        | D5       | D4  | D3       | D2       | D1       | D0       | F3       | F2       | F1       | F0       | CL4658 寄存器配置                                                                         |

| DAC 寄             | 存器的写       | 写入   | •    |      | •    |      |      | •        |      |          |      |                   |          | •   | •        | •        | •        | •        | •        |          |          |          |                                                                                      |

| ×                 | ×          | ×    | ×    | ×    | ×    | ×    | ×    | ×        | ×    | ×        | ×    | ×                 | ×        | ×   | ×        | ×        | ×        | ×        | ×        | ×        | ×        | ×        | CL4658 无效                                                                            |

| ×                 | 0          | 0    | 0    | 0    | 0    | 0    | 0    | 0        |      | Data     |      |                   |          |     |          |          |          |          |          |          | ×        | ×        | 选择 DAC 通道 A 写入数据寄存器                                                                  |

| ×                 | 0          | 0    | 0    | 0    | 0    | 0    | 0    | 1        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 选择 DAC 通道 B 写入数据寄存器                                                                  |

| ×                 | 0          | 0    | 0    | 0    | 0    | 0    | 1    | 0        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 选择 DAC 通道 C 写入数据寄存器                                                                  |

| ×                 | 0          | 0    | 0    | 0    | 0    | 0    | 1    | 1        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 选择 DAC 通道 D 写入数据寄存器                                                                  |

| ×                 | 0          | 0    | 0    | 0    | 0    | 1    | 0    | 0        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 选择 DAC 通道 E 写入数据寄存器                                                                  |

| ×                 | 0          | 0    | 0    | 0    | 0    | 1    | 0    | 1        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 选择 DAC 通道 F 写入数据寄存器                                                                  |

| ×                 | 0          | 0    | 0    | 0    | 0    | 1    | 1    | 0        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 选择 DAC 通道 G 写入数据寄存器                                                                  |

| ×                 | 0          | 0    | 0    | 0    | 0    | 1    | 1    | 1        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 选择 DAC 通道 H 写入数据寄存器                                                                  |

| ×                 | 0          | 0    | 0    | 0    | 1    | ×    | ×    | ×        |      |          |      |                   |          | ×   |          |          |          |          | ×        | ×        | ×        | ×        | 无效码,没有选择 DAC 的通道                                                                     |

| ×                 | 0          | 0    | 0    | 0    | 1    | 1    | 1    | 1        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 向所有的 DAC 通路写入数据寄存器                                                                   |

| DAC 寄             | DAC 寄存器的更新 |      |      |      |      |      |      |          |      |          |      |                   |          |     |          |          |          |          |          |          |          |          |                                                                                      |

| ×                 | 0          | 0    | 0    | 1    | 0    | 0    | 0    | 0        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 更新通道 A 数据                                                                            |

| ×                 | 0          | 0    | 0    | 1    | 0    | 0    | 0    | 1        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 更新通道 B 数据                                                                            |

| ×                 | 0          | 0    | 0    | 1    | 0    | 0    | 1    | 0        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 更新通道 C 数据                                                                            |

| ×                 | 0          | 0    | 0    | 1    | 0    | 0    | 1    | 1        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 更新通道 D 数据                                                                            |

| ×                 | 0          | 0    | 0    | 1    | 0    | 1    | 0    | 0        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 更新通道 E 数据                                                                            |

| ×                 | 0          | 0    | 0    | 1    | 0    | 1    | 0    | 1        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 更新通道 F 数据                                                                            |

| ×                 | 0          | 0    | 0    | 1    | 0    | 1    | 1    | 0        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 更新通道 G 数据                                                                            |

| ×                 | 0          | 0    | 0    | 1    | 0    | 1    | 1    | 1        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 更新通道 H 数据                                                                            |

| ×                 | 0          | 0    | 0    | 1    | 1    | ×    | ×    | ×        |      |          |      |                   |          | ×   |          |          |          |          | ×        | ×        | ×        | ×        | 无效位                                                                                  |

| ×                 | 0          | 0    | 0    | 1    | 1    | 1    | 1    | 1        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 更新所有通道数据                                                                             |

| 清空寄               | 存器         |      |      |      |      |      |      |          |      |          |      |                   |          |     |          |          |          |          |          |          |          |          |                                                                                      |

| ×                 | 0          | 1    | 0    | 1    | ×    | ×    | ×    | ×        | ×    | ×        | ×    | ×                 | ×        | ×   | ×        | ×        | ×        | ×        | ×        | ×        | 0        | 0        | 寄存器清零; CL4658 输出置 0                                                                  |

| ×                 | 0          | 1    | 0    | 1    | ×    | ×    | ×    | ×        | ×    | ×        | ×    | ×                 | ×        | ×   | ×        | ×        | ×        | ×        | ×        | ×        | 0        | 1        | 寄存器清零; CL4658 输出置于中间位置                                                               |

| ×                 | 0          | 1    | 0    | 1    | ×    | ×    | ×    | ×        | ×    | ×        | ×    | ×                 | ×        | ×   | ×        | ×        | ×        | ×        | ×        | ×        | 1        | 0        | 寄存器清零; CL4658 输出置于满摆幅位置                                                              |

| ×                 | 0          | 1    | 0    | 1    | ×    | ×    | ×    | ×        | ×    | ×        | ×    | ×                 | ×        | ×   | ×        | ×        | ×        | ×        | ×        | ×        | 1        | 1        | 无操作                                                                                  |

| 写入 LI             | DAC 寄存     | 字器   |      |      |      |      |      |          |      |          |      |                   |          |     |          |          |          |          |          |          |          |          |                                                                                      |

| X                 | 0          | 1    | 1    | 0    | ×    | ×    | ×    | ×        | ×    | ×        | ×    | ×                 | ×        | ×   | DAC<br>H | DAC<br>G | DAC<br>F | DAC<br>E | DAC<br>D | DAC<br>C | DAC<br>B | DAC<br>A | 写入 LDAC 寄存器,默认 LDAC 寄存器为<br>0 ,如果将其中某一位设为 1,那么无论<br>LDAC的引脚状态如何,它的 DAC 通道都<br>会直接更新。 |

| 复位                | _          |      | Ι.   |      | 1    | Ι    | Ι    | <u> </u> |      | <u> </u> | I    |                   | <u> </u> | I   | T .      | Ī        | I        | I        | 1        | <u> </u> | I        | I        | F.0                                                                                  |

| X                 | 0          | 1    | 1    | 1 1  | X X  | X X  | ×    | X X      | ×    | ×        | ×    | ×                 | ×        | ×   | ×        | ×        | ×        | ×        | ×        | ×        | ×        | ×        | 复位                                                                                   |

|                   | l          | 1    | 输入寄存 | ı    | 1    | 1    | 1    | I        | l    |          |      |                   |          |     |          |          |          |          | 1        |          | l        | l        |                                                                                      |

| ×                 | 0          | 0    | 1    | 0    | 0    | 0    | 0    | 0        |      |          |      |                   | D        | ata |          |          |          |          | ×        | ×        | ×        | ×        | 写入通道 A 并更新所有 DAC 寄存器                                                                 |

| . — ~ | •                             |   |   |   |     |     |   |     |     |      |     |     |    |     |     |     |     |     |     |     |                      |                      |                                                    |

|-------|-------------------------------|---|---|---|-----|-----|---|-----|-----|------|-----|-----|----|-----|-----|-----|-----|-----|-----|-----|----------------------|----------------------|----------------------------------------------------|

| ×     | 0                             | 0 | 1 | 0 | 0   | 0   | 0 | 1   |     | Data |     |     |    |     |     |     |     |     |     |     | ×                    | ×                    | 写入通道 B 并更新所有 DAC 寄存器                               |

| ×     | 0                             | 0 | 1 | 0 | 0   | 0   | 1 | 0   |     | Data |     |     |    |     |     |     |     |     |     |     | ×                    | ×                    | 写入通道 C 并更新所有 DAC 寄存器                               |

| ×     | 0                             | 0 | 1 | 0 | 0   | 0   | 1 | 1   |     |      |     |     | Da | ata |     |     |     | ×   | ×   | ×   | ×                    | 写入通道 D 并更新所有 DAC 寄存器 |                                                    |

| ×     | 0                             | 0 | 1 | 0 | 0   | 1   | 0 | 0   |     |      |     |     | Da | nta |     |     | ×   | ×   | ×   | ×   | 写入通道 E 并更新所有 DAC 寄存器 |                      |                                                    |

| ×     | 0                             | 0 | 1 | 0 | 0   | 1   | 0 | 1   |     |      |     |     | Da | nta |     |     | ×   | ×   | ×   | ×   | 写入通道 F 并更新所有 DAC 寄存器 |                      |                                                    |

| ×     | 0                             | 0 | 1 | 0 | 0   | 1   | 1 | 0   |     |      |     |     | Da | nta |     |     |     |     | ×   | ×   | ×                    | ×                    | 写入通道 G 并更新所有 DAC 寄存器                               |

| ×     | 0                             | 0 | 1 | 0 | 0   | 1   | 1 | 1   |     |      |     |     | Da | nta |     |     |     |     | ×   | ×   | ×                    | ×                    | 写入通道 H 并更新所有 DAC 寄存器                               |

| ×     | 0                             | 0 | 1 | 0 | 1   | ×   | × | ×   |     |      |     |     | >  | <   |     |     |     |     | ×   | ×   | ×                    | ×                    | 无效码,没有 DAC 被更新和写入                                  |

| ×     | 0                             | 0 | 1 | 0 | 1   | 1   | 1 | 1   |     |      |     |     | Da | nta |     |     |     |     | ×   | ×   | ×                    | ×                    | 写入所有 DAC 输入寄存器并更新所有 DAC 通道的寄存器                     |

| 写入选   | 入选择的 DAC 输入寄存器以及更新选择的 DAC 寄存器 |   |   |   |     |     |   |     |     |      |     |     |    |     |     |     |     |     |     |     |                      |                      |                                                    |

| ×     | 0                             | 0 | 1 | 1 | 0   | 0   | 0 | 0   |     |      |     |     | Da | nta |     |     |     |     | ×   | ×   | ×                    | ×                    | 写入通道 A 并更新通道 A                                     |

| ×     | 0                             | 0 | 1 | 1 | 0   | 0   | 0 | 1   |     |      |     |     | Da | ıta |     |     |     |     | ×   | ×   | ×                    | ×                    | 写入通道 B 并更新通道 B                                     |

| ×     | 0                             | 0 | 1 | 1 | 0   | 0   | 1 | 0   |     |      |     |     | Da | nta |     |     |     |     | ×   | ×   | ×                    | ×                    | 写入通道 C 并更新通道 C                                     |

| ×     | 0                             | 0 | 1 | 1 | 0   | 0   | 1 | 1   |     |      |     |     | Da | ata |     |     |     |     | ×   | ×   | ×                    | ×                    | 写入通道 D 并更新通道 D                                     |

| ×     | 0                             | 0 | 1 | 1 | 0   | 1   | 0 | 0   |     |      |     |     | Da | nta |     |     |     |     | ×   | ×   | ×                    | ×                    | 写入通道 E 并更新通道 E                                     |

| ×     | 0                             | 0 | 1 | 1 | 0   | 1   | 0 | 1   |     |      |     |     | Da | nta |     |     |     |     | ×   | ×   | ×                    | ×                    | 写入通道 F 并更新通道 F                                     |

| ×     | 0                             | 0 | 1 | 1 | 0   | 1   | 1 | 0   |     |      |     |     | Da | nta |     |     |     |     | ×   | ×   | ×                    | ×                    | 写入通道 G 并更新通道 G                                     |

| ×     | 0                             | 0 | 1 | 1 | 0   | 1   | 1 | 1   |     |      |     |     | Da | nta |     |     |     |     | ×   | ×   | ×                    | ×                    | 写入通道 H 并更新通道 H                                     |

| ×     | 0                             | 0 | 1 | 1 | 1   | ×   | × | ×   |     |      |     |     | >  | <   |     |     |     |     | ×   | ×   | ×                    | ×                    | 无效码,没有 DAC 被更新和写入                                  |

| ×     | 0                             | 0 | 1 | 1 | 1   | 1   | 1 | 1   |     |      |     |     | Da | nta |     |     |     |     | ×   | ×   | ×                    | ×                    | 写入所有 DAC 输入寄存器并更新所有 DAC<br>寄存器                     |

| 掉电模   | 式指令                           |   |   |   |     |     |   |     |     |      |     |     |    |     |     |     |     |     |     |     |                      |                      |                                                    |

| ×     | 0                             | 1 | 0 | 0 | ×   | ×   | × | ×   | ×   | ×    | ×   | ×   | 0  | 0   | DAC                  | DAC                  | 打开 A,B,C,D,E,F,G,H 通道(退出掉电关断                       |

|       |                               |   |   |   |     |     |   |     |     |      |     |     |    |     | Н   | G   | F   | Е   | D   | С   | В                    | A                    | 模式),通过把对应通道的寄存器置 1<br>关断 A,B,C,D,E,F,G,H 通道,通过将对应通 |

| ×     | 0                             | 1 | 0 | 0 | ×   | ×   | × | ×   | ×   | ×    | ×   | ×   | 0  | 1   | DAC                  | DAC                  | 道的寄存器置 1,模拟输出引脚接至内部                                |

|       |                               |   |   |   |     |     |   |     |     |      |     |     |    |     | Н   | G   | F   | Е   | D   | С   | В                    | A                    | 1kΩ 到 GND                                          |

|       |                               | 1 |   |   |     |     |   |     |     |      |     |     |    | 0   | DAC                  | DAC                  | 关断 A,B,C,D,E,F,G,H 通道,通过把对应通                       |

| ×     | 0                             | 1 | 0 | 0 | ×   | ×   | × | ×   | ×   | ×    | ×   | ×   | 1  | 0   | Н   | G   | F   | Е   | D   | С   | В                    | A                    | 道的寄存器置 1,模拟输出引脚接至内部<br>100kΩ 到 GND                 |

| ×     | 0                             | 1 | 0 | 0 | ×   | ×   | × | ×   | ×   | ×    | ×   | ×   | 1  | 1   | DAC                  | DAC                  | 关断 A,B,C,D,E,F,G,H 通道,通过把对应通                       |

|       |                               | 1 | U | 0 | _ ^ | _ ^ | ^ | _ ^ | _ ^ | _ ^  | _ ^ | _ ^ | 1  | 1   | Н   | G   | F   | Е   | D   | С   | В                    | A                    | 道的寄存器置 1,模拟输出引脚接至高阻态                               |

| 内部参   | 考指令                           | 1 |   |   |     | 1   | 1 |     | 1   | 1    |     |     |    |     |     |     |     |     |     |     |                      |                      |                                                    |

| ×     | 1                             | 0 | 0 | 0 | 0   | ×   | × | ×   | ×   | ×    | ×   | ×   | ×  | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×                    | 0                    | 将内部参考断电,必须使用外部参考                                   |

| ×     | 1                             | 0 | 0 | 0 | 0   | ×   | × | ×   | ×   | ×    | ×   | ×   | ×  | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×                    | 1                    | 内部参考打开,外部参考电压必须断开与引<br>脚连接                         |

| 保留位   |                               |   |   |   |     |     | _ |     |     |      |     |     |    |     |     |     |     |     |     |     |                      |                      |                                                    |

| ×     | 1                             | 0 | 1 | 0 | ×   | ×   | × | ×   | ×   | ×    | ×   | ×   | ×  | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×                    | ×                    | 保留位-无效;设备不符合指定条件                                   |

| ×     | 1                             | 0 | 1 | 1 | ×   | ×   | × | ×   | ×   | ×    | ×   | ×   | ×  | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×                    | ×                    | 保留位-无效,设备不符合指定条件                                   |

| ×     | 1                             | 1 | 0 | 0 | ×   | ×   | × | ×   | ×   | ×    | ×   | ×   | ×  | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×                    | ×                    | 保留位-无效;设备不符合指定条件                                   |

| ×     | 1                             | 1 | 0 | 1 | ×   | ×   | × | ×   | ×   | ×    | ×   | ×   | ×  | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×                    | ×                    | 保留位-无效;设备不符合指定条件                                   |

| ×     | 1                             | 1 | 1 | 0 | ×   | ×   | × | ×   | ×   | ×    | ×   | ×   | ×  | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×                    | ×                    | 保留位-无效;设备不符合指定条件                                   |

| ×     | 1                             | 1 | 1 | 1 | ×   | ×   | × | ×   | ×   | ×    | ×   | ×   | ×  | ×   | ×   | ×   | ×   | ×   | ×   | ×   | ×                    | ×                    | 保留位-无效;设备不符合指定条件                                   |

| •     |                               |   | • | • | •   | •   |   | •   | •   | •    | •   | •   | •  |     | •   |     | •   |     | •   | •   |                      |                      |                                                    |

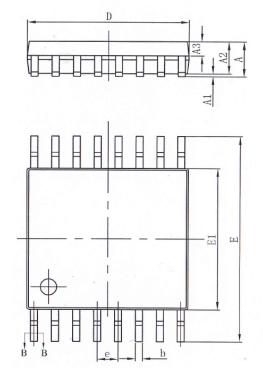

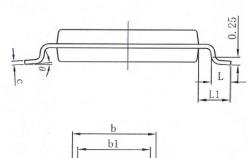

## 外形尺寸

| SYMBOL | MILLIMETER |      |      |

|--------|------------|------|------|

|        | MIN        | NOM  | MAX  |

| Α      | _          | _    | 1.20 |

| A1     | 0.05       |      | 0.15 |

| A2     | 0.90       | 1.00 | 1.05 |

| A3     | 0.39       | 0.44 | 0.49 |

| b      | 0.20       |      | 0.28 |

| b1     | 0.19       | 0.22 | 0.25 |

| С      | 0.13       | _    | 0.17 |

| cl     | 0.12       | 0.13 | 0.14 |

| D      | 4.90       | 5.00 | 5.10 |

| Е      | 6.20       | 6.40 | 6.60 |

| E1     | 4.30       | 4.40 | 4.50 |

| e      | 0.65BSC    |      |      |

| L      | 0.45       | 0.60 | 0.75 |

| LI     | 1.00BSC    |      |      |

| θ      | 0          | _    | 8°   |

|        |            |      |      |

图 916 引脚 TSSOP 封装

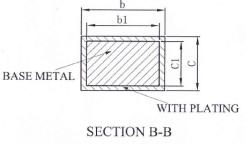

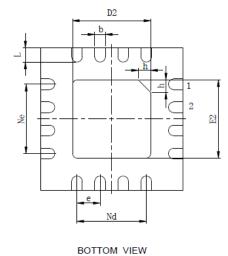

| SYMBOL  | MILLIMETER |       |       |  |

|---------|------------|-------|-------|--|

|         | MIN        | NOM   | MAX   |  |

| A       | 0.70       | 0.75  | 0.80  |  |

| A1      | _          | 0.02  | 0.05  |  |

| b       | 0. 25      | 0.30  | 0.35  |  |

| с       | 0. 18      | 0. 20 | 0. 25 |  |

| D       | 3. 90      | 4.00  | 4. 10 |  |

| D2      | 2.10       | 2. 20 | 2.30  |  |

| e       | 0. 65BSC   |       |       |  |

| Ne      | 1.95BSC    |       |       |  |

| Nd      | 1. 95BSC   |       |       |  |

| E       | 3. 90      | 4.00  | 4. 10 |  |

| E2      | 2.10       | 2. 20 | 2. 30 |  |

| L       | 0.35       | 0.40  | 0.45  |  |

| h       | 0.30       | 0. 35 | 0.40  |  |

| L/F载体尺寸 | 110*110    |       |       |  |

图 10 16 引脚 QFN 封装

# ※ 核芯互联 订购信息

| 型号          | 工作温度范围    | 封装描述                        |

|-------------|-----------|-----------------------------|

| CL4658Z-QG  | _40~+85°C | 16 引脚 QFN-16 封装,上电输出为零电平    |

| CL4658M-QG  | _40~+85°C | 16 引脚 QFN-16 封装,上电输出为中间电平   |

| CL4658Z-TSG | _40~+85°C | 16 引脚 TSSOP-16 封装,上电输出为零电平  |

| CL4658M-TSG | _40~+85°C | 10 引脚 TSSOP-16 封装,上电输出为中间电平 |