# FURUNO GNSS Receiver GT-100

# **Hardware Specifications**

(Document No. SE22-410-003-07)

www.furuno.com

### **IMPORTANT NOTICE**

No part of this manual may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose without the express written permission of the publisher, FURUNO ELECTRIC CO., LTD. FURUNO ELECTRIC CO., LTD. All rights reserved.

Any information of this documentation shall not be disclosed to any third party without permission of the publisher, FURUNO ELECTRIC CO., LTD.

FURUNO ELECTRIC CO., LTD. reserves the right to make changes to its products and specifications without notice.

All brand and product names are registered trademarks, trademarks or service marks of their respective holders.

The following satellite systems are operated and controlled by the authorities of each government.

- GPS(USA)

- GLONASS (Russia)

- Galileo(Europe)

- Beidou(China)

- QZSS(Japan)

- SBAS(USA: WAAS, Europe: EGNOS, Japan: MSAS)

Thus FURUNO is not liable for the degradation of the above systems so therefore FURUNO cannot guarantee specification based on their conditions. User is expected to be familiar with the System and make full use of it with their own responsibility.

We pay through attention about the software of this product. But, if perchance you found a bug or a trouble, please feel free to contact us directly. We will check it, and if it is a bug, we may send you a new version with a bug fix. If perchance we found a bug or a trouble, we may send you a new version after we contact you.

When we send you the new version software, we may ask you to update software. Therefore, we strongly recommended being able to access to serial port of this product from outside of your product to make software update easy. In addition, we also strongly recommend connecting between serial port of this product and network to remote access and update software.

This product must not be used for military and/or antisocial purposes such as terrorism, and shall not be supplied to any party Intending to use the products for such purposes.

This product has been designed for consumer equipment and devices. This product is not intended for use in, and must not be used for, any application of nuclear equipment, driving control equipment for aerospace or any other unauthorized use. With the exception of the above-mentioned banned applications, for applications involving highs of safety and liability such as medical equipment, burglar alarm equipment, disaster prevention equipment and undersea equipment, please contact an FURUNO sales representative and/or evaluate the total system on the applicability. Also, implement a fail-safe design, protection circuit, redundant circuit, malfunction protection and/or fire protection into the complete system for safety and reliability of the total system.

# **Revision History**

| Version | Changed contents                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Date       |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 0       | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2022.06.22 |

| 1       | Change the figure in section 4.1 Correct items in Table 4.2 Add items in Table 5.1 Add items in Table 5.2 Add section 5.4 Change the contents in section 5.5 Add items in Table 5.6.2 Change the figures in section 7.1 Add a note in section 7.1 Correct the weight in section 7.2 Add the storage conditions in section 8.3 Change the figure in section 8.4 Change the figure in section 8.5 Change the figure in section 8.6 Add the marking specifications in chapter 9 | 2022.12.19 |

| 2       | IMPORTANT NOTICE Change the figure in section 3 Change the contents in Table 4.2 Change the contents in Table 5.6.1 Change the contents in Table 5.6.2                                                                                                                                                                                                                                                                                                                       | 2023.05.12 |

| 3       | Add items in Table 5.2 Change the contents in section 5.6.2                                                                                                                                                                                                                                                                                                                                                                                                                  | 2023.07.13 |

| 4       | Change the contents in Table 5.6.1                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2023.10.11 |

| 5       | Correct chapter 9                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2024.03.18 |

| 6       | Add section 5.6 Change a note in section 7.1                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2024.06.20 |

| 7       | Add a supplement page                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2024.11.08 |

# **Table of Contents**

| 1      | l Outline ·····                                   |            |

|--------|---------------------------------------------------|------------|

| 2      |                                                   |            |

|        | 2.1 Product Overview                              |            |

| 3      |                                                   |            |

| 4      |                                                   |            |

|        | 4.1 Pin Layout                                    |            |

|        | 4.2 GT-100 Signal Description                     | 4          |

| 5      |                                                   |            |

|        | 5.1 Absolute Maximum Rating                       |            |

|        | 5.2 Power Supply                                  | 5          |

|        | 5.3 Digital Interface Signal                      | 6          |

|        | 5.4 Operation Sequence                            | 7          |

|        | 5.4.1 Rise Time for Power Supply                  |            |

|        | 5.4.2 Power-up / Power-down timing of VBK and VCC | 7          |

|        | 5.5 Reset                                         |            |

|        | 5.5.1 External Reset                              |            |

|        | 5.5.2 UART Wake-up Timing after Reset ······      | 8          |

|        | 5.5.2.1 Without External Reset                    |            |

|        |                                                   |            |

|        | 5.6 UART                                          | -          |

|        | 5.7.1 Recommended Antenna                         |            |

|        | 5.7.1 Recommended Antenna                         |            |

| 6      | •                                                 |            |

| Ծ<br>7 | • • • • • • • • • • • • • • • • • • •             |            |

| 1      | 7.1 Mechanical Description                        | 44         |

|        | 7.1 Mechanical Description                        |            |

| 8      |                                                   | دران<br>۱۸ |

| 0      | 8.1 Refollow times                                |            |

|        | 8.2 Reflow Heat Resistance                        |            |

|        | 8.3 Storage Conditions                            |            |

|        | 8.4 Copper Land Design ······                     |            |

|        | 8.5 Solder Stop Mask Design                       |            |

|        | 8.6 Solder Print Mask Design ······               | 18         |

| 9      | lacktriangle                                      |            |

|        | lo Special Instruction······                      |            |

|        | 10.1 Electronic Component                         | 20         |

|        | 10.2 RoHS                                         | 20         |

| 11     | 11 Reference Documents ······                     |            |

|        | Sunnlement: White Paner                           |            |

### 1 Outline

This document contains the specification pertinent to the GNSS module.

### 2 Features

### 2.1 Product Overview

GT-100 is Dual band, multi constellation GNSS receivers.

- ◆ GT-100 support L1 Band and L5 Band.

- ◆ GT-100 support GPS, GLONASS, BeiDou, Galileo, NavIC, SBAS and QZSS as multi constellation.

GT-100 output accurate time information.

◆ GT-100 support PPS (Pulse per Second) output synchronized with UTC time or GPS time and frequency output that can be set arbitrarily.

The products support the debug feature for GNSS application.

Internal Antenna Diagnostic function.

The products include an embedded NVM for firmware updates.

◆ Size: 16Mbit

Memory Structure: STT-MRAM

The products have an UART interface. And the following message format is supported.

♦ NMEA Message

Table 2.1 General Specifications<sup>1)</sup>

|                           | lable 2.1 General S       | Specification |                                |

|---------------------------|---------------------------|---------------|--------------------------------|

| Items                     | Description               |               | Notes                          |

|                           | GPS L1C/A                 | L1            |                                |

|                           | GLONASS L1OF              | L1            |                                |

|                           | Galileo E1                | L1            |                                |

|                           | Beidou B1I                | L1            | ─<br>─ 32 channels             |

|                           | Beidou B1C                | L1            |                                |

| GNSS reception            | QZSS L1C/A                | L1            |                                |

| capability                | SBAS L1                   | L1            |                                |

|                           | NavIC L5                  | L5            |                                |

|                           | GPS L5                    | L5            |                                |

|                           | Galileo E5a               | L5            | ─<br>─ 30 channels             |

|                           | Beidou B2a                | L5            |                                |

|                           | QZSS L5                   | L5            |                                |

|                           | Anti-Jamming              | •             | -                              |

| Facility                  | Anti-Spoofing             | •             | -                              |

| Environment<br>Robustness | Multipath mitigation      | •             | -                              |

| TODUSTITESS               | T-RAIM                    | •             | -                              |

|                           | Antenna current detection | •             | -                              |

| Serial data format        | NMEA <sup>2)</sup>        | •             | Default 115200bps              |

| Antenna                   | Active antenna            | •             |                                |

| Antenna                   | Passive antenna           | •             | External LNA required.         |

| Operational limits        | Altitude                  | 18,300m       | Based on Wassenaar arrangement |

| Operational limits        | Velocity                  | 515 m/s       | specification                  |

|                           |                           |               |                                |

### Notes:

- 1) See the function specifications for details.

- 2) See the protocol specifications for details.

### 3 Functional Overview

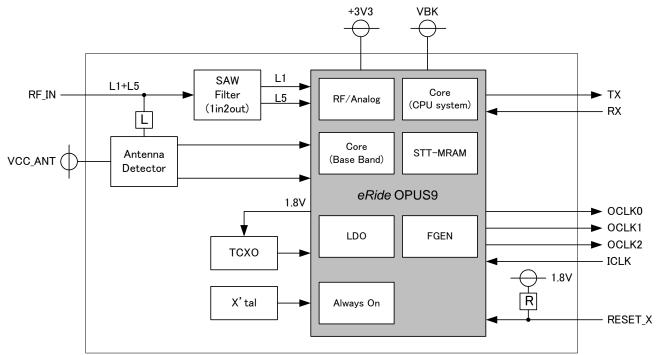

The internal key device for GT-100 is *eRide*OPUS 9. The latest Furuno monolithic GNSS receiver chip with an ARM-Cortex processor (for signal tracking and processing), PLL synthesizer, Down-converter, ADC, DSP and STT-MRAM (for firmware and data storage).

GT-100 also include a TCXO (for reference clock), RTC (for real-time clock) 32 kHz crystal, SAW filter, and antenna current detection circuit. The block diagram is shown in Figure 3.1.

GT-100 have a built-in function (FGEN) for generating high-precision clock pulses in the GNSS receiver chip. GT-100 output a PPS signal or a clock pulse of any frequency from its OCLK0, OCLK1 and OCLK2. The GT-100 have an input pin, ICLK, to allow time synchronization with an external PPS or clock. Refer to the function specifications and protocol specifications for usage.

RF\_IN is the signal line on which the GNSS signal input and the bias voltage for antenna power supply are superimposed. By applying a voltage to VCC\_ANT, the bias voltage is superimposed on RF\_IN. The antenna current detection circuit detects whether the current flowing from VCC\_ANT to RF\_IN is insufficient or excessive. This status can be known by serial communication.

Figure 3.1 Block Diagram

# 4 I/O Signal Description

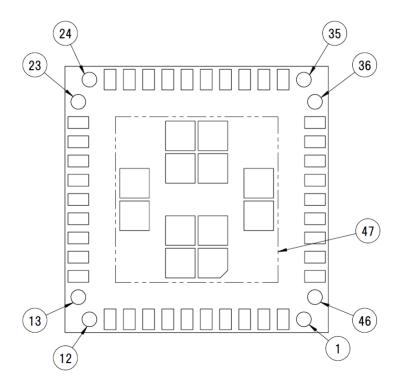

# 4.1 Pin Layout

**TOP View**

**BOTTOM View**

Note: GND pads of the center are put together as Pin No.47.

# 4.2 GT-100 Signal Description

### **Table 4.2 I/O Signal Description**

| #  | GT-100<br>Pin Name | I/O                  | I/O<br>Voltage | Built-in<br>PU/PD <sup>1)</sup> | Reset<br>State | Unused     | Description                                                              |

|----|--------------------|----------------------|----------------|---------------------------------|----------------|------------|--------------------------------------------------------------------------|

| 1  | NC                 | -                    | -              | -                               | -              | OPEN       | -                                                                        |

| 2  | GND                | -                    | -              | -                               | -              | -          | -                                                                        |

| 3  | RESERVE            | -                    | -              | -                               | -              | OPEN       | Don't connect to GND.                                                    |

| 4  | RESERVE            | -                    | -              | -                               | -              | OPEN       | -                                                                        |

| 5  | RESERVE            | -                    | -              | -                               | -              | OPEN       | -                                                                        |

| 6  | GND                | -                    | -              | -                               | -              | -          | -                                                                        |

| 7  | GND                | -                    | -              | -                               | -              | -          | -                                                                        |

| 8  | GND                | -                    | -              | -                               | -              | -          | -                                                                        |

| 9  | GND                | -                    | -              | -                               | -              | -          | -                                                                        |

| 10 | RF_IN              | INPUT                | -              | -                               | -              | OPEN       | L1 & L5 band RF signal input pin                                         |

| 11 | GND                | -                    | -              | -                               | -              | -          | -                                                                        |

| 12 | NC                 | -                    | -              | -                               | -              | OPEN       | -                                                                        |

| 13 | NC                 | -                    | -              | -                               | -              | OPEN       | -                                                                        |

| 14 | VCC_ANT            | Power Input          | -              | -                               | -              | OPEN       | Antenna Detector power supply / Antenna power supply input pin           |

| 15 | GPIO2              | OUTPUT 2)            | 3.3V           | -                               | Hi-Z           | OPEN       | Refer to Protocol Specifications                                         |

| 16 | OCLK1              | OUTPUT               | 3.3V           |                                 | Hi-Z           | OPEN       | PPS/clock output pin                                                     |

| 17 | GND                | -                    | -              | -                               | -              | -          | -                                                                        |

| 18 | NC                 | -                    | -              | -                               | -              | OPEN       | Don't connect to GND.                                                    |

| 19 | GND                | -                    | -              | -                               | -              | -          | -                                                                        |

| 20 | VBK                | Power Input          | -              | -                               | -              | OPEN       | Backup power supply input pin                                            |

| 21 | GND                | -                    | -              | -                               | -              | -          | -                                                                        |

| 22 | GND                | -                    | -              | -                               | -              | -          | -                                                                        |

| 23 | NC                 | -                    | -              | -                               | -              | OPEN       | -                                                                        |

| 24 | NC                 | -                    | -              | -                               | -              | OPEN       | -                                                                        |

| 25 | GND                | -                    | -              | -                               | -              | -          | -                                                                        |

| 26 | GND                | -                    | -              | -                               | -              | -          | -                                                                        |

| 27 | RESERVE            | -                    | -              | -                               | Hi-Z           | OPEN       | -                                                                        |

| 28 | RESERVE            | -                    | _              | _                               | Hi-Z           | OPEN       | -                                                                        |

| 29 | RX                 | INPUT                | 3.3V           | PU                              | Hi-Z           | OPEN or PU | UART reception input pin                                                 |

| 30 | TX                 | OUTPUT               | 3.3V           | -                               | Hi-Z           | OPEN       | UART transmission output pin                                             |

| 31 | GND                | -                    | -              | _                               | -              | -          | -                                                                        |

| 32 | ICLK               | INPUT                | 3.3V           | PD                              | Hi-Z           | GND or PD  | PPS/clock input pin                                                      |

| 33 | OCLK2              | OUTPUT               | 3.3V           | -                               | Hi-Z           | OPEN       | PPS/clock output pin                                                     |

| 34 | GND                | -                    | -              | _                               | -              | -          | -                                                                        |

| 35 | NC                 | -                    | _              | _                               | _              | OPEN       | •                                                                        |

| 36 | NC                 | -                    |                | _                               | _              | OPEN       |                                                                          |

| 37 | GND                | -                    |                | _                               |                | -          |                                                                          |

| 38 | OCLK0              | OUTPUT               | 3.3V           | -                               | Hi-Z           | OPEN       | PPS/clock output pin                                                     |

| 39 | GPIO0              | OUTPUT <sup>2)</sup> | 3.3V           | _                               | Hi-Z           | OPEN       | Refer to Protocol Specifications                                         |

| 40 | GPIO1              | OUTPUT <sup>2)</sup> | 3.3V           |                                 | Hi-Z           | OPEN       | Refer to Protocol Specifications                                         |

|    |                    | OUTFUT 7             | 3.3 V          | -                               | ПІ-Д           |            | Refer to Protocol Specifications                                         |

| 41 | RESERVE<br>GND     | -                    | -              | -                               | -              | OPEN       | <del>-</del>                                                             |

| 42 |                    | Power Innut          | -              | -                               | -              | -          | Main nawar aunah inaut ain                                               |

| 43 | VCC                | Power Input          | -              | -                               | -              | -          | Main power supply input pin                                              |

| 44 | Reset_X            | INPUT                | 1.8V           | PU                              | -              | OPEN or PU | External reset signal input pin Logic L: Reset Logic H: Normal operation |

| 45 | GND                | _                    | -              | -                               | -              | -          | -                                                                        |

| 46 | NC                 | -                    | -              | -                               | -              | OPEN       | -                                                                        |

| 47 | GND                | -                    | -              | -                               | -              | -          | -                                                                        |

|    |                    |                      |                |                                 |                |            |                                                                          |

### Notes:

- 1) Pull-up and pull-down resistor values are shown in Table 5.3.

- 2) Hi-Z when command is not set.

# 5 Electrical Characteristics

# 5.1 Absolute Maximum Rating

The lists of absolute maximum ratings are specified over operating case temperature shown in Table 6.1. Stresses beyond those listed under those ranges may cause permanent damage to the module.

**Table 5.1 Absolute Maximum Rating**

| Items                      | Symbol               | Min. | Max. | Unit | Notes                 |

|----------------------------|----------------------|------|------|------|-----------------------|

| Supply voltage to VCC      | V <sub>CC_ABS</sub>  | -0.3 | 4.0  | V    | -                     |

| Supply voltage to VBK      | $V_{BK\_ABS}$        | -0.3 | 2.5  | V    | -                     |

| Supply voltage to VCC_ANT  | $V_{ANT\_ABS}$       | -    | 7.0  | V    | -                     |

| Digital input (DI) voltage | -                    | -0.3 | 3.7  | V    | -                     |

| Digital input (DI) voltage | -                    | -0.3 | 2.2  | V    | Apply to Reset_X pin. |

| RF_IN input power          | P_RF_ABS             | -    | 0    | dBm  | -                     |

| Magnetic field strength    | T <sub>MFS_ABS</sub> | -    | 1000 | mT   | -                     |

# 5.2 Power Supply

# **Table 5.2 Power Supply Characteristics**

T<sub>A</sub>=25°C, unless otherwise stated

|                                              |                     |      |      |      | • • • • • • • • • • • • • • • • • • • • | =25°C, unless otherwise stated                     |

|----------------------------------------------|---------------------|------|------|------|-----------------------------------------|----------------------------------------------------|

| Items                                        | Symbol              | Min. | Тур. | Max. | Unit                                    | Notes                                              |

| Supply voltage to VCC                        | $V_{CC0}$           | 3.0  | 3.3  | 3.60 | V                                       | -                                                  |

| Supply voltage to VBK                        | $V_{BK}$            | 1.40 | 1.80 | 1.98 | V                                       | -                                                  |

| Supply voltage to VCC_ANT                    | $V_{ANT}$           | 3.0  |      | 5.0  | V                                       | -                                                  |

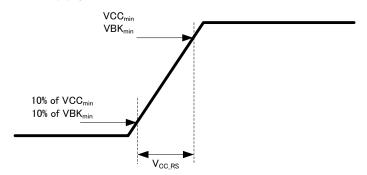

| VCC rising slew rate                         | $V_{\text{CC\_RS}}$ | 0.2  | -    | 20   | ms                                      | Figure 5.4.1                                       |

|                                              | I <sub>CCAL</sub>   | -    | 55   | 200  | mΑ                                      | Full search @T <sub>A</sub> =85°C                  |

| VCC current consumption                      | ICCTL               | -    | 50   | -    | mA                                      | Tracking satellite outdoor @T <sub>A</sub> =85°C   |

| VBK current consumption at                   | 1                   | -    | 40   | -    | μA                                      | V <sub>CC</sub> =0V                                |

| back up                                      | I <sub>BKN</sub> -  | -    | -    | 1.5  | mΑ                                      | V <sub>CC</sub> =0V @T <sub>A</sub> =85°C          |

| VBK current consumption at normal operation) | I <sub>BKB</sub>    | -    | -    | 0.1  | μA                                      | V <sub>CC</sub> =3.3V                              |

| VCC_ANT current consumption                  | I <sub>CC_ANT</sub> | -    | 13   | 21   | mA                                      | The current of the active antenna is not included. |

# 5.3 Digital Interface Signal

# **Table 5.3 Interface Signal**

T<sub>A</sub>=25°C, unless otherwise stated

| Items                                                       | Symbol              | Min.         | Тур. | Max.         | Unit | Notes                     |

|-------------------------------------------------------------|---------------------|--------------|------|--------------|------|---------------------------|

| Logic L input voltage for 3.3V power domain Inputs          | VIL                 | 0            | -    | 0.3 x<br>VCC | V    | -                         |

| Logic H input voltage for 3.3V power domain Inputs          | V <sub>IH</sub>     | 0.7 x<br>VCC | -    | VCC          | V    | -                         |

| Logic L input voltage for 1.8V power domain Input (Reset_X) | $V_{IL\_RST}$       | 0            | -    | 0.5          | V    | Apply to Reset_X pin      |

| Logic H input voltage for 1.8V power domain Input (Reset_X) | V <sub>IH_RST</sub> | 1.36         | 1.8  | -            | V    | Apply to Reset_X pin      |

| Logic L output voltage                                      | $V_{OL}$            | 0            | -    | 0.2 x<br>VCC | V    | @ loL  = 2mA              |

| Logic H output voltage                                      | $V_{OH}$            | 0.8 x<br>VCC | -    | VCC          | V    | @ I <sub>OH</sub>   = 2mA |

| Pull-up resistor for 3.3V power domain I/O                  | $R_{PU}$            | 33           | -    | 330          | kΩ   | -                         |

| Pull-up resistor for 1.8V power domain Input (Reset_X)      | R <sub>PU_RST</sub> | -            | 10   | -            | kΩ   | Apply to Reset_X pin      |

| Pull-down resistor                                          | $R_{PD}$            | 33           | -    | 330          | kΩ   | -                         |

### 5.4 Operation Sequence

### 5.4.1 Rise Time for Power Supply

Figure 5.4.1 Rise Time for Power Supply Sequence

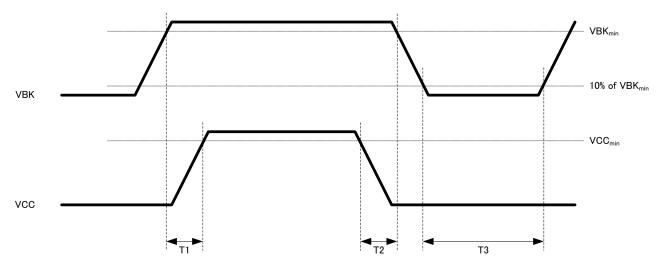

# 5.4.2 Power-up / Power-down timing of VBK and VCC

Figure 5.4.2 Power-up / Power-down timing of VBK and VCC Sequence

Table 5.4.2 Power-up / Power-down timing of VBK and VCC Sequence

| Table 5.4.2 I ower up / I ower down tilling of VBR and VOO bequence |        |      |      |      |      |                                                                     |  |  |  |

|---------------------------------------------------------------------|--------|------|------|------|------|---------------------------------------------------------------------|--|--|--|

| Items                                                               | Symbol | Min. | Тур. | Max. | Unit | Notes                                                               |  |  |  |

| VBK rise to VCC rise time                                           | T1     | 0    | -    | -    | ms   | The VBK should rise at earlier than or VCC rising.                  |  |  |  |

| VCC fall to VBK fall time                                           | T2     | 0    | -    | -    | ms   | The VCC should fall earlier than or same timing as the VBK falling. |  |  |  |

| Minimum VBK inactive time                                           | T3     | 500  | -    | -    | ms   | The VBK should be kept low more than 500ms.                         |  |  |  |

### 5.5 Reset

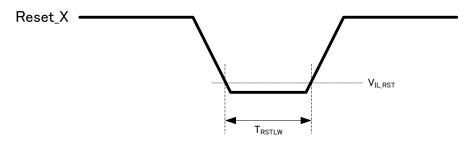

### 5.5.1 External Reset

In most cases, it is not required to drive external reset input (Reset\_X) pin. However, if it is needed to force the reset state externally for e.g. synchronizing the reset state with the application circuitry, Reset\_X can be used for this purpose. The H voltage level of the Reset\_X signal should be 1.8V. The Reset\_X has an internal pull-up. (Pull-up resistor is  $10k\Omega$ .) An open-drain or open-collectors is recommended to prevent collisions with internal pull-up voltages.

Figure 5.5.1 Reset Sequence

**Table 5.5.1 Reset Sequence**

| Items                       | Symbol             | Min. | Max. | Unit | Notes                                           |

|-----------------------------|--------------------|------|------|------|-------------------------------------------------|

| Minimum reset activate time | T <sub>RSTLW</sub> | 500  | -    | ms   | The Reset_X should be kept low more than 500ms. |

### 5.5.2 UART Wake-up Timing after Reset

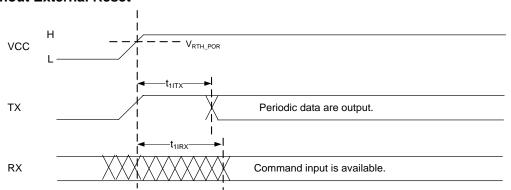

### 5.5.2.1 Without External Reset

Figure 5.5.2.1 UART Wake-up Timing after V<sub>RTH POR</sub>

Table 5.4.2.1 UART Wake-up Timing after VRTH\_POR

| Items                                                        | Symbol            | Min. | Max. | Unit | Notes |

|--------------------------------------------------------------|-------------------|------|------|------|-------|

| Time delay from VCC reaches V <sub>RTH_POR</sub> to TX valid | t <sub>1ITX</sub> | -    | 6    | S    |       |

| Time delay from VCC reaches V <sub>RTH_POR</sub> to RX ready | t <sub>1IRX</sub> | -    | 6    | S    |       |

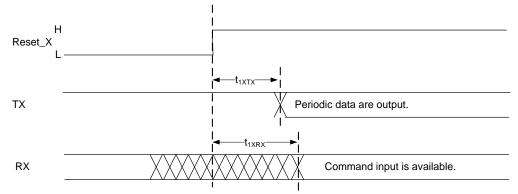

### 5.5.2.2 With External Reset

Figure 5.1.2.2 UART Wake-up Timing after Reset\_X

Table 5.5.2.2 UART Wake-up Timing after Reset\_X

| Items                                        | Symbol            | Min. | Max. | Unit | Notes |

|----------------------------------------------|-------------------|------|------|------|-------|

| Time delay from Reset_X set to H to TX valid | t <sub>1XTX</sub> | -    | 6    | S    |       |

| Time delay from Reset_X set to H to RX ready | t <sub>1XRX</sub> | -    | 6    | S    |       |

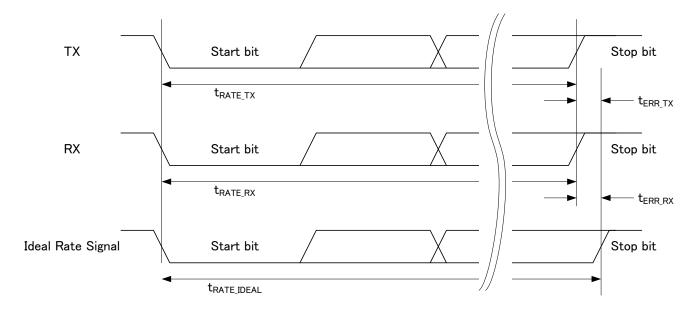

### **5.6 UART**

| Items           | Symbol                | Min. | Max.   | Unit | Notes                                        |

|-----------------|-----------------------|------|--------|------|----------------------------------------------|

| Baud Rate       | R <sub>BRT_RATE</sub> | 9600 | 460800 | bps  |                                              |

| UART Error Rate | R <sub>BRT_ERR</sub>  | -2   | 2      | %    | terr_tx/ trate_ideal<br>terr_rx/ trate_ideal |

### 5.7 Antenna

### 5.7.1 Recommended Antenna

**Table 5.6.1 Recommended Active Antenna**

| Item                 | Min. | Тур. | Max. | Unit | Remarks                                                                  |

|----------------------|------|------|------|------|--------------------------------------------------------------------------|

| L1 Bandwidth         | 1559 | -    | 1606 | MHz  |                                                                          |

| L5 Bandwidth         | 1166 | -    | 1187 | MHz  |                                                                          |

| Antenna element gain | 0    | -    | -    | dBi  |                                                                          |

| Amplifier gain       | 15   | -    | 40   | dB   | Including cable loss. 15 dB to 25 dB is recommended for noise robustness |

| Amplifier NF         | -    | -    | 3    | dB   | Including cable loss                                                     |

| Impedance            | -    | 50   | -    | Ω    |                                                                          |

### 5.7.2 Antenna Amplifier Power

Power for antenna pre-amplifier input on pin #14 (VCC\_ANT) is superimposed (biased) on pin #10 (RF\_IN).

GT-100 have the function of supplying voltage to the active antenna and diagnosing the connection state (open, short) of the antenna. The diagnostic results are output by the proprietary NMEA message. In addition, it also has a protection function (OFF Mode) when the antenna is shorted. When the antenna output voltage is 0.5V(TYP) or less, it enters OFF Mode. To return to Normal Mode from OFF Mode, please solve the short-circuit problem first. After that, it will work as Normal Mode when the antenna output voltage is 1.0V(TYP) or higher. The diagnostic result is SHORT during OFF Mode.

**Table 5.6.2 Recommended Antenna Power**

T<sub>A</sub>=25°C, VCC\_ANT=5V unless otherwise stated

| Items                          | Symbol           | Min                   | Тур | Max | Unit | Notes                    |

|--------------------------------|------------------|-----------------------|-----|-----|------|--------------------------|

| Output voltage                 | $V_{APO}$        | V <sub>ANT</sub> -0.5 | -   | -   | V    | @ I <sub>APO</sub> =50mA |

| Output current                 | I <sub>APO</sub> | -                     | -   | 55  | mA   | -                        |

| Open Detect Threshold Current  | I <sub>AOD</sub> | -                     | 1.3 | 2.5 | mA   | -                        |

| Short Detect Threshold Current | I <sub>ASD</sub> | 60                    | 82  | -   | mA   | -                        |

| Short Protection               | I <sub>ASP</sub> | 68                    | -   | 130 | mA   | -                        |

| Load Capacity                  | C <sub>ALC</sub> | -                     | -   | 50  | μF   |                          |

# 6 Environmental Specifications

Table 6.1 Environmental Specifications

| Items                   |                        | Specification | Unit | Notes |  |

|-------------------------|------------------------|---------------|------|-------|--|

| Operating temperature   |                        | -40 to +85    | °C   | -     |  |

| Storage temperature     |                        | -40 to +105   | °C   | -     |  |

| Magnetic field immunity | 10-year data retention | Max 100       | mT   | @25°C |  |

|                         |                        | Max 90        | mT   | @55°C |  |

|                         |                        | Max 55        | mT   | @85°C |  |

|                         | Active Read / Write    | Max 25        | mT   | -     |  |

# 7 Mechanical Specifications

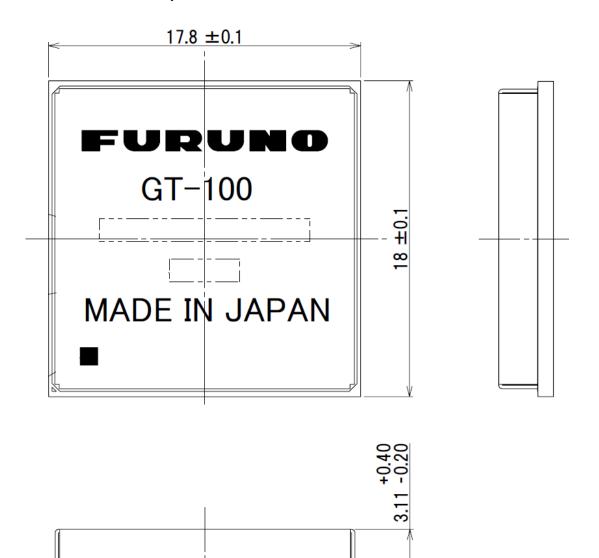

# 7.1 Mechanical Description

units: [mm]

Note: Tolerances are ±0.3mm, unless otherwise specified.

Dimensions in ( ): It is reference dimension.

The terminal coplanarity of product assumes the state of room temperature.

units: [mm]

0.1

Tolerances are ±0.3mm, unless otherwise specified. Note:

Dimensions in (): It is reference dimension.

The terminal coplanarity of product assumes the state of room temperature. Surface treatment specifications for module bottom terminal.

Material : Cu

Surface finish: Ni-Au

Ni 3µm - 8µm

Au 0.05μm – 0.15μm

# 7.2 Weight

1.7g (TYP)

### 8 MECHANICAL DESIGN INFORMATION

Recommended Copper Land and Solder Stop Mask (Resist) on Customer's Mother Board and Solder Print Mask (Metal Mask) Dimensions for better soldering with GT-100. The following drawings have been verified based on FURUNO recommended reflow soldering conditions and reference PCB. The reflow solderability should vary in accordance to the thickness of the PCB, reflow condition and pattern layout etc. If the customer will apply these conditions (Cupper Land, Solder Stop Mask, Solder Print Mask, etc.), further verification or modification of these parameters may be necessary. Please solder the NC pins to NC footprint patterns of the Main Board.

### 8.1 Refollow times

1 time

Note: This Module is exclusive use of reflow

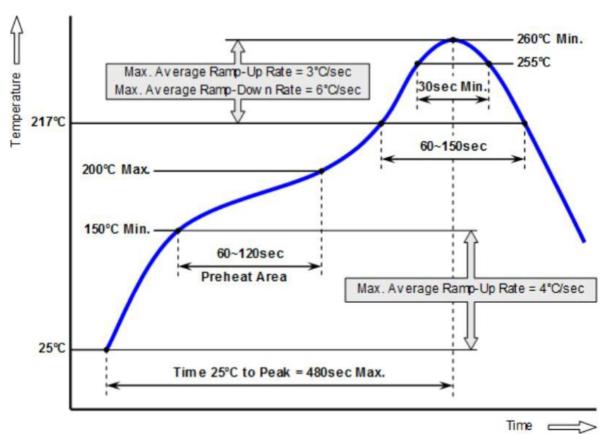

### 8.2 Reflow Heat Resistance

Allowable reflow number of times: 1 time Max.

### Note:

- 1. The measurement point is at the center of the upper surface of the module.

- 2. Please execute the reflow soldering on the following conditions according to JEDEC J-STD-020D. Peak Temperature: Max. 260[°C]

Peak Time (≥ 255[°C]): Max. 30[s]

### 8.3 Storage Conditions

The following conditions shall be kept for soldering and keeping in storage this product.

- 1. Shelf life in dry bag: 12 months at 5 ~ 40 °C and < 85 % RH.

- 2. After dry bag is opened, module that will be subjected to soldering reflow or equivalent processing must be:

- a) Mounted within 168 hours at factory condition of < 30 °C / 60 % RH, or

- b) Stored at  $< 30 \,^{\circ}\text{C} / 10 \,^{\circ}\text{K}$  RH.

- 3. Modules require baking, before mounting, if:

- a) Humidity Indicator Card is >10 % when read at 23 °C ± 5 °C, or

- b) Item 2.a) or 2.b) are not met.

- 4. If baking is required, device may be baked for 216 hours at  $40 \sim 45$  °C and < 5 % RH for low-temperature device containers.

- a) Allowable baking number of times: 1time.

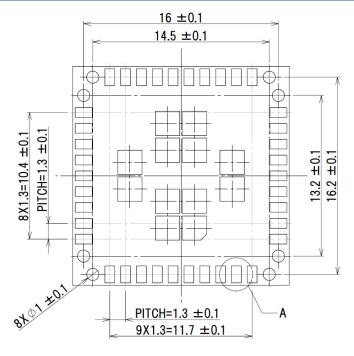

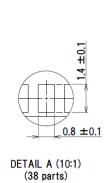

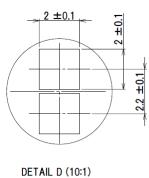

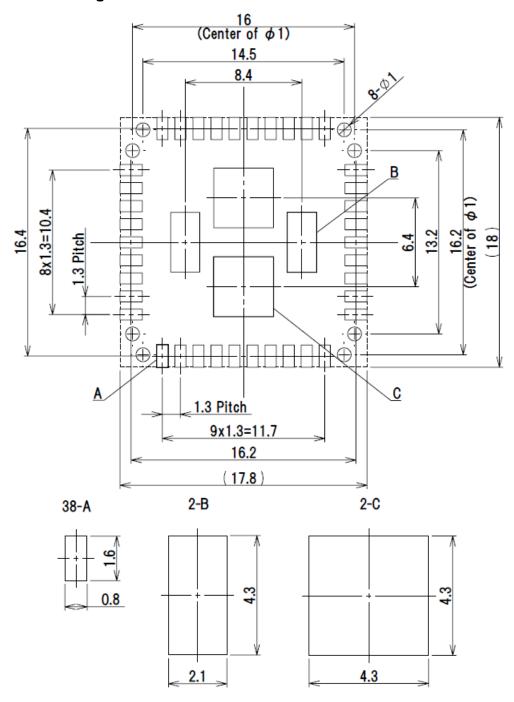

# 8.4 Copper Land Design

units: [mm]

### Note

- 1. All are Top View.

- 2. Recommended Pattern and Solder stop mask on Customer's board and Metal mask dimensions for better soldering with GT-100.

- 3. Tolerances are ±0.1mm, unless otherwise specified.

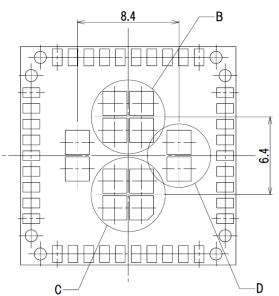

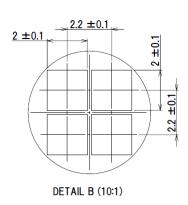

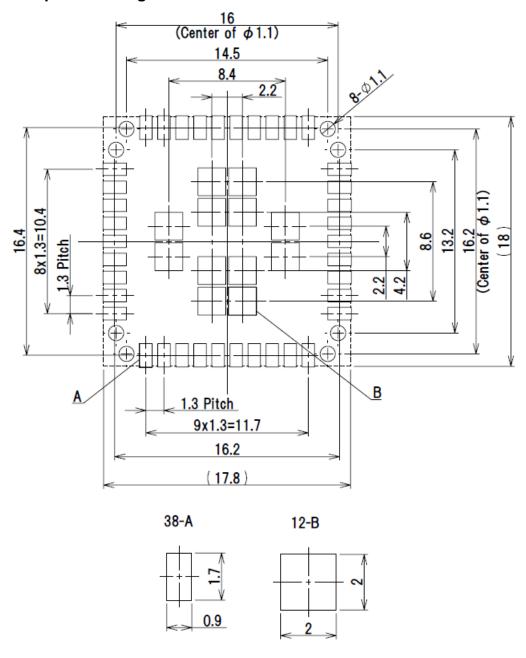

# 8.5 Solder Stop Mask Design

units: [mm]

### Note

- 1. All are Top View.

- 2. Recommended Pattern and Solder stop mask on Customer's board and Metal mask dimensions for better soldering with GT-100.

- 3. Tolerances are ±0.1mm, unless otherwise specified.

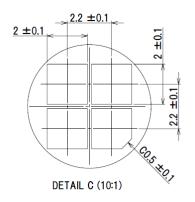

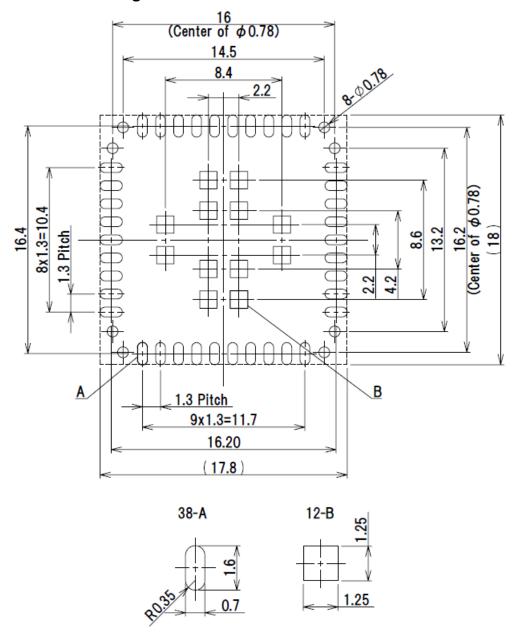

# 8.6 Solder Print Mask Design

units: [mm]

### Note

- 1. All are Top View.

- 2. Recommended Pattern and Solder stop mask on Customer's board and Metal mask dimensions for better soldering with GT-100.

- 3. Tolerances are ±0.1mm, unless otherwise specified.

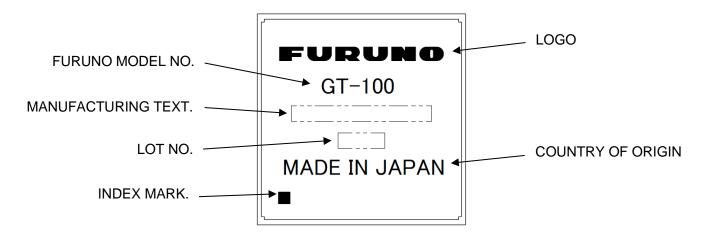

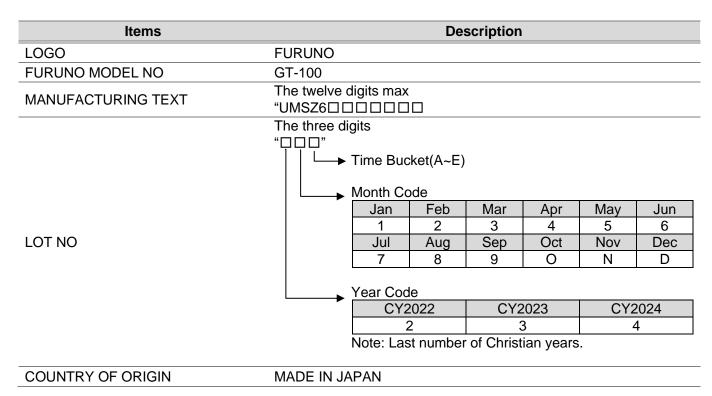

# 9 Marking

# 10 Special Instruction

### **10.1 Electronic Component**

Components in GT-100 module such as chip resistors, capacitors and TCXO's are planned to be purchased from multiple manufacturers/vendors according to FURUNO's procurement policy. So it is possible that multiple components from multiple manufacturers/vendors could be used even in the same production lot.

### **10.2 RoHS**

GT-100 comply with RoHS directives.

### 11 Reference Documents

- FURUNO SE22-600-013 GT-100 Function Specifications

- FURUNO SE22-600-007 GT-100 PFEC Protocol Specifications

# **Supplement: White Paper**

If you would like to understand the specifications in depth, please check the technical white paper from the URL below.

Our engineers specializing in time synchronization provide explanations with test results of our anti-jamming and multipath technologies.

- Dual Band GNSS Receivers: Safeguarding Critical Infrastructure <a href="https://pages.furuno.com/en-gt100-dualband-robustness-downloadform.html">https://pages.furuno.com/en-gt100-dualband-robustness-downloadform.html</a>

- White Papers (GNSS Receivers for Time Synchronization) https://pages.furuno.com/en-gnsstiming-whitepaper-downloadform.html