### 5.0kV<sub>RMS</sub> Reinforced Isolated Amplifier

#### **Features**

- -0.1V to 2V, high-impedance input voltage range optimized for voltage measurement

- Low offset error and drift: ±2.5mV (max), ±10μV/°C (max)

- Fixed gain: 1

- Low gain error and drift: ±0.3% (max), ±30ppm/°C (max)

- Low nonlinearity and drift: 0.04%, ±1ppm/°C (typical)

- 3.3V to 5V operation on high side

- Missing high-side supply indication

- Safety-related certifications: 7071V<sub>PK</sub> reinforced isolation per DIN VDE V 0884-17: 2021-10

5.0kV<sub>RMS</sub> isolation for 1 minute per UL1577

• High CMTI: 150 kV/µs (typical)

## **Applications**

- Isolated voltage sensing in:

- Motor drives

- Frequency inverters

- Uninterruptible power supplies

| PART NUMBER | PACKAGE   | BODY SIZE    |

|-------------|-----------|--------------|

| CH1311BDWVR | WB SOIC-8 | 5.85mm*7.5mm |

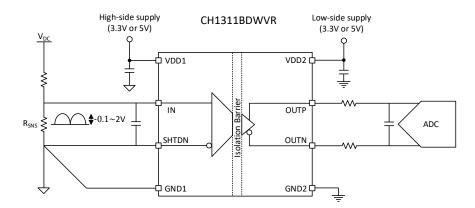

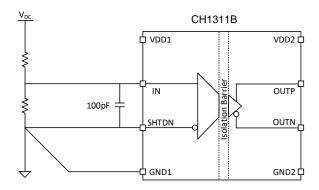

#### **Simplified Schematic**

# 1 Pin Configurations and Functions

Figure 1. Pin Configuration, Top View

**Pin Functions and Descriptions**

| PIN NO. | PIN NAME                                                                 | ТҮРЕ             | DESCRIPTION                                                 |

|---------|--------------------------------------------------------------------------|------------------|-------------------------------------------------------------|

| 1       | VDD1                                                                     | High-side power  | High-side power supply, 3.0 V to 5.5 V relative to GND1.    |

| 2       | IN                                                                       | Analog input     | Analog input.                                               |

| 3       | SHTDN Digital input Shutdown input, active high, with internal pullup re |                  | Shutdown input, active high, with internal pullup resistor. |

| 4       | GND1                                                                     | High-side ground | High-side analog ground.                                    |

| 5       | GND2                                                                     | Low-side ground  | Low-side analog ground.                                     |

| 6       | OUTN                                                                     | Analog output    | Inverting analog output.                                    |

| 7       | OUTP                                                                     | Analog output    | Noninverting analog output.                                 |

| 8       | VDD2                                                                     | Low-side power   | Low-side power supply, 3.0V to 5.5V relative to GND2.       |

## 2 Specifications

## 2.1 Absolute Maximum Ratings (1)

| Parameter Description                 |                                              | MIN      | MAX      | UNIT |  |

|---------------------------------------|----------------------------------------------|----------|----------|------|--|

| Damaranah                             | VDD1 to GND1                                 | -0.3     | 6.5      | V    |  |

| Power supply                          | VDD2 to GND2                                 | -0.3     | 6.5      | V    |  |

| Innut valtage                         | IN                                           | GND1-6   | VDD1+0.5 | V    |  |

| Input voltage                         | SHTDN                                        | GND1-0.5 | VDD1+0.5 | V    |  |

| Output voltage                        | OUTP, OUTN                                   | GND2-0.5 | VDD2+0.5 | V    |  |

| Input current                         | Continuous, any pin except power-supply pins | -10      | 10       | mA   |  |

| Junction temperature, T <sub>J</sub>  | T <sub>J</sub>                               | -40      | 150      | °C   |  |

| Storage temperature, T <sub>stg</sub> | T <sub>stg</sub>                             | -65      | 150      | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 2.2 ESD Ratings

| Parameter               |                                                                       | VALUE | UNIT |

|-------------------------|-----------------------------------------------------------------------|-------|------|

|                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±4000 | W    |

| Electrostatic discharge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±2000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 2.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

| Parameter                           | Description             | MIN  | MAX  | UNIT |

|-------------------------------------|-------------------------|------|------|------|

| High side power supply              | VDD1 to GND1            | 3.0  | 5.5  | V    |

| Low side power supply               | VDD2 to GND2            | 3.0  | 5.5  | V    |

| Specified linear full-scale voltage | IN-GND1                 | -0.1 | 2    | V    |

| Conscisive load                     | On OUTP or OUTN to GND2 |      | 500  | [    |

| Capacitive load                     | OUTP to OUTN            |      | 250  | pF   |

| Resistive load                      | On OUTP or OUTN to GND2 |      | 1    | kΩ   |

| Input voltage                       | SHTDN to GND1           | 0    | VDD1 |      |

| T <sub>A</sub>                      | Ambient Temperature     | -40  | 125  | °C   |

### 2.4 Thermal Information

| Parameter              | Description                               | VALUE | UNIT |

|------------------------|-------------------------------------------|-------|------|

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance    | 85    | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance | 26    | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance      | 43    | °C/W |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 2.5 Insulation Specifications

| Parameter                      | Description        | Test Condition                                          | VALUE | UNIT |

|--------------------------------|--------------------|---------------------------------------------------------|-------|------|

| CLR                            | External clearance | Shortest pin-to-pin distance through air                | ≥8    | mm   |

| CPG External creepage          |                    | Shortest pin-to-pin distance across the package surface | ≥ 8   | mm   |

| CTI Comparative tracking index |                    | DIN EN 60112 (VDE 0303-11); IEC 60112                   | ≥ 600 | V    |

| Material gro                   | oup                | According to IEC 60664-1                                | I     |      |

| Overvoltage category           |                    | Rated mains voltage ≤ 600 V <sub>RMS</sub>              | I-IV  |      |

|                                |                    | Rated mains voltage ≤ 1000 V <sub>RMS</sub>             | 1-111 |      |

#### DIN V VDE V 0884-17 (VDE V 0884-17): 2021-10(2)

| Parameter         | Description                                                                      | Test Condition                                                                                                                                     | VALUE              | UNIT            |

|-------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage                                        | AC voltage                                                                                                                                         | 2121               | $V_{PK}$        |

| V                 | Maximum working isolation                                                        | AC voltage                                                                                                                                         | 1500               | $V_{RMS}$       |

| $V_{IOWM}$        | voltage                                                                          | DC voltage                                                                                                                                         | 2121               | $V_{DC}$        |

| V <sub>IOTM</sub> | Maximum transient isolation voltage                                              | $V_{TEST} = V_{IOTM}$ , t = 60s (qualification)<br>$V_{TEST} = 1.2 \times V_{IOTM}$ , t = 1s (100% production)                                     | 7071               | $V_{PK}$        |

| V <sub>IOSM</sub> | Maximum surge isolation voltage (3)                                              | 1.2/50 μs waveform per IEC 62368-1<br>$V_{TEST} = 1.6 \times V_{IOSM}$ (qualification)                                                             | 6250               | $V_{PK}$        |

|                   | Method a, after Input-Output safety test subgroup 2/3                            | $\begin{split} &V_{ini} = V_{IOTM},  t_{ini} = 60s \\ &V_{pd(m)} = 1.2  x  V_{IORM},  t_m = 10s \\ &partial \; discharge \leq 5 \; pC \end{split}$ | 2545               | $V_{PK}$        |

| $V_{pd(m)}$       | Method a, after Input-Output safety test subgroup 1                              | $V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$<br>$V_{pd(m)} = 1.6 \times V_{IORM}$ , $t_m = 10s$<br>partial discharge $\leq 5 \text{ pC}$                 | 3394               | $V_{PK}$        |

|                   | Method b1, at routine test (100% production) and preconditioning (type test) (4) | Method b1: $V_{ini} = 1.2 \times V_{IOTM}, t_{ini} = 1s$ $V_{pd(m)} = 1.875 \times V_{IORM}, t_m = 1s$ partial discharge $\leq$ 5pC                | 3977               | V <sub>PK</sub> |

| C <sub>IO</sub>   | Barrier capacitance, input to output (5)                                         | V <sub>IO</sub> = 0.4*sin(2πft), f =1MHz                                                                                                           | ~1.2               | pF              |

|                   | Isolation resistance incut to                                                    | V <sub>IO</sub> = 500V at T <sub>A</sub> = 25°C                                                                                                    | > 10 <sup>12</sup> | Ω               |

| $R_{IO}$          | Isolation resistance, input to output (5)                                        | V <sub>IO</sub> = 500V at 100°C ≤ T <sub>A</sub> ≤ 125°C                                                                                           | > 10 <sup>11</sup> | Ω               |

|                   | Output                                                                           | $V_{IO} = 500V \text{ at } T_S = 150^{\circ}C$                                                                                                     | > 109              | Ω               |

| Pollution de      | egree                                                                            |                                                                                                                                                    | 2                  |                 |

| Climatic cat      | egory                                                                            |                                                                                                                                                    | 40/12              | 5/21            |

<sup>(1)</sup> Apply creepage and clearance requirements according to the specific equipment isolation standards of an application. Care must be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed circuit board (PCB) do not reduce this distance. Creepage and clearance on a PCB become equal in certain cases. Techniques such as inserting grooves, ribs, or both on a PCB are used to help increase these specifications.

<sup>(2)</sup> This coupler is suitable for safe electrical insulation only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

<sup>(3)</sup> Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

<sup>(4)</sup> Apparent charge is electrical discharge caused by a partial discharge (pd).

<sup>(5)</sup> All pins on each side of the barrier are tied together, creating a two-pin device.

#### **UL 1577**

| Parameter | Description                 | Test Condition                                                                                                                            |      | UNIT      |

|-----------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|

| $V_{ISO}$ | Withstand isolation voltage | $V_{TEST} = V_{ISO} = 5000V_{RMS}$ , t = 60s (qualification),<br>$V_{TEST} = 1.2 \times V_{ISO} = 6000V_{RMS}$ , t = 1s (100% production) | 5000 | $V_{RMS}$ |

# 2.7 Safety-Limiting Values

Safety limiting intends to minimize potential damage to the isolation barrier upon circuit failure.

| Parameter      | Description                          | Test Condition                                                                           | MIN | TYP | MAX  | UNIT |

|----------------|--------------------------------------|------------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>S</sub> | Safety input, output or              | R <sub>θJA</sub> =85°C/W, T <sub>J</sub> =150°C,<br>T <sub>A</sub> =25°C, VDD1=VDD2=5.5V |     |     | 294  | mA   |

|                | supply current                       | R <sub>0JA</sub> =85°C/W, T <sub>J</sub> =150°C,<br>T <sub>A</sub> =25°C, VDD1=VDD2=3.3V |     |     | 445  | mA   |

| Ps             | Safety input, output or supply power | $R_{\theta JA}=85$ °C/W, $T_{J}=150$ °C, $T_{A}=25$ °C                                   |     |     | 1470 | mW   |

| Ts             | Maximum Safety temperature           |                                                                                          |     |     | 150  | °C   |

### 2.8 Electrical Characteristics

Minimum and maximum specifications of the CH1311B apply from  $T_A$ =-40°C to +125°C, VDD1=3.0V to 5.5V, VDD2 =3.0V to 5.5V, IN=0V to 2V, and SHTDN=GND1=0V, typical specifications are at  $T_A$ =25°C, VDD1=5V, and VDD2=3.3V (unless otherwise noted).

| Parameter             |                                      | Test Condition                                                  | MIN           | TYP        | MAX    | UNIT       |

|-----------------------|--------------------------------------|-----------------------------------------------------------------|---------------|------------|--------|------------|

| INPUT and (           | OUTPUT                               |                                                                 |               |            | 1      |            |

| Vos                   | Input offset voltage (1)             | T <sub>A</sub> = 25°C                                           | -2.5          | ±0.5       | 2.5    | mV         |

| TCV <sub>OS</sub>     | Input offset drift (1)               | - A                                                             | -10           | ±3         | 10     | μV/°C      |

| R <sub>IN</sub>       | Input resistance                     |                                                                 |               | 1          |        | GΩ         |

| I <sub>IB</sub>       | Input bias current                   | T <sub>A</sub> = 25°C                                           | -15           |            | 15     | nA         |

| C <sub>IN</sub>       | Input capacitance                    | f <sub>IN</sub> = 275 kHz                                       |               | 25         |        | pF         |

| GAIN                  | Normal gain                          | 11N 273 1112                                                    |               | 1          |        | V/V        |

| E <sub>G</sub>        | Gain error <sup>(1)</sup>            | T <sub>A</sub> = 25°C                                           | -0.3%         | ±0.05%     | 0.3%   | -,,,       |

| TCE <sub>G</sub>      | Gain error drift (1)                 | 14 15 5                                                         | -30           | ±5         | 30     | ppm/°C     |

| NL                    | Nonlinearity (1)                     |                                                                 | -0.04%        | ±0.01%     | 0.04%  | ррину с    |

| TC <sub>NL</sub>      | Nonlinearity drift                   |                                                                 | 0.0 170       | ±1         | 0.0170 | ppm/°C     |

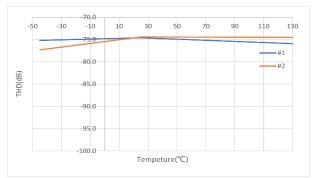

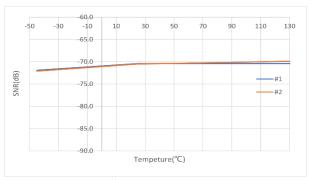

| THD                   | Total harmonic distortion            | V <sub>IN</sub> = 2V,<br>f <sub>IN</sub> = 10 kHz, BW = 100 kHz |               | -83        |        | dB         |

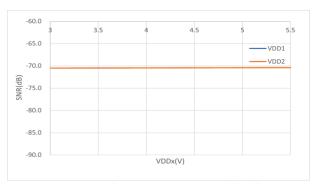

| SNR                   | Signal to noise ratio                | $V_{IN} = 2V,$<br>$f_{IN} = 1 \text{ kHz}, BW = 10 \text{ kHz}$ |               | 81         |        | dB         |

| SINK                  | Signal to hoise ratio                | $V_{IN} = 2V$ ,<br>$f_{IN} = 10 \text{ kHz}$ , BW = 100 kHz     |               | 71         |        | dB         |

| NOISE <sub>OUT</sub>  | Output noise                         | V <sub>IN</sub> = GND1, BW =100kHz                              |               | 250        |        | $uV_{RMS}$ |

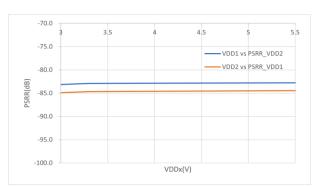

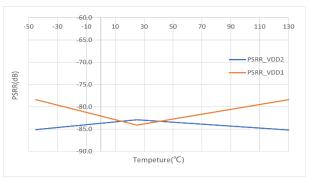

|                       | Power-supply rejection ratio         | PSRR vs VDD1, at DC PSRR vs VDD1, 100mV and 10kHz ripple        |               | -95<br>-85 |        |            |

| PSRR                  |                                      | PSRR vs VDD2, at DC                                             |               | -95        |        | dB         |

|                       |                                      | PSRR vs VDD2,<br>100mV and 10kHz ripple                         |               | -85        |        |            |

| $V_{CMout}$           | Common-mode output voltage           |                                                                 | 1.39          | 1.44       | 1.49   | V          |

| $V_{Clipping}$        | Input Voltage before clipping output | IN to GND1                                                      |               | 2.516      |        | V          |

| $V_{CLIPout}$         | Clipping differential output voltage | $V_{IN} > V_{Clipping}$                                         |               | 2.5        |        | V          |

| V <sub>FAILSAFE</sub> | Failsafe differential output voltage |                                                                 |               | -2.6       | -2.5   | V          |

| BW                    | Output bandwidth                     |                                                                 | 250           | 310        |        | kHz        |

| R <sub>OUT</sub>      | Output resistance                    | OUTP or OUTN                                                    |               | 0.2        |        | Ω          |

| I <sub>SC</sub>       | Output short-circuit current         | VDD2 or GND2                                                    |               | ±13        |        | mA         |

| CMTI                  | Common-mode transient immunity       | GND1 – GND2  = 1 kV                                             | 100           | 150        |        | kV/us      |

| I <sub>IN</sub>       | SHTDN pin,<br>GND1 ≤ SHTDN ≤ VDD1    |                                                                 | -70           |            | 1      | uA         |

| V <sub>IH</sub>       | High level of input voltage          |                                                                 | 0.77*<br>VDD1 |            |        | V          |

| Parameter            |                                       | Test Condition     | MIN | TYP  | MAX           | UNIT |

|----------------------|---------------------------------------|--------------------|-----|------|---------------|------|

| V <sub>IL</sub>      | Low level of input volage             |                    |     |      | 0.28*<br>VDD1 | V    |

| POWER SUP            | PLY                                   |                    |     |      |               |      |

| VDD1                 | VDD1 undervoltage detection threshold | VDD1 Rising        | 2.3 | 2.5  | 2.7           | V    |

| VDD1 <sub>UVLO</sub> | VDD1 undervoltage hysteresis          | Hysteresis         |     | 0.15 |               | V    |

| VDD2 <sub>UVLO</sub> | VDD2 undervoltage detection threshold | VDD2 Rising        | 2.2 | 2.4  | 2.6           | V    |

|                      | VDD2 undervoltage hysteresis          | Hysteresis         |     | 0.35 |               | V    |

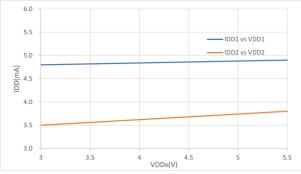

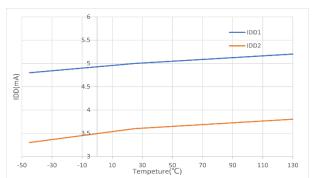

| IDD1                 | High-side supply current              | 3.0V ≤ VDD1 ≤ 5.5V |     | 4    | 6             | mA   |

| IDD2                 | Low-side supply current               | 3.0V ≤ VDD2 ≤ 5.5V |     | 3    | 5             | mA   |

<sup>(1)</sup> The typical value includes one sigma statistical variation.

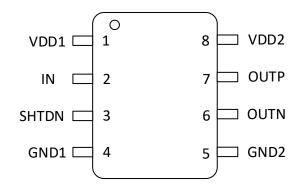

## 2.9 Switching Characteristics

over operating ambient temperature range (unless otherwise noted)

| Parameter          |                                 | Test Conditions                                                               | MIN | TYP | MAX | UNIT |

|--------------------|---------------------------------|-------------------------------------------------------------------------------|-----|-----|-----|------|

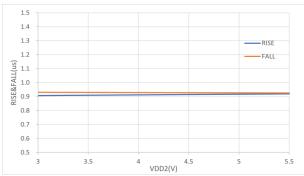

| t <sub>r</sub>     | Rise time of OUTP,<br>OUTN      |                                                                               |     | 1.0 |     | us   |

| t <sub>f</sub>     | Fall time of OUTP,<br>OUTN      |                                                                               |     | 1.0 |     | us   |

|                    | IN to OUTP, OUTN<br>(50% – 10%) | Unfiltered output, see Fig2                                                   |     | 0.7 | 1   | us   |

| $t_{\text{PD}}$    | IN to OUTP, OUTN<br>(50% – 50%) | Unfiltered output, see Fig2                                                   |     | 1.2 | 1.5 | us   |

|                    | IN to OUTP, OUTN<br>(50% – 90%) | Unfiltered output, see Fig2                                                   |     | 1.7 | 2   | us   |

| t <sub>AS</sub>    | Analog settling time            | VDD1 step to 3.0 V with VDD2<br>≥ 3.0V, to OUTP, OUTN valid,<br>0.1% settling |     | 350 |     | us   |

| t <sub>EN</sub>    | Device enable time              | SHTDN high to low                                                             |     | 350 |     | us   |

| t <sub>SHTDN</sub> | Device shut down time           | SHTDN low to high                                                             |     | 3   | 10  | us   |

Figure 2. Rise, Fall, and Delay Time Waveforms

<sup>(2)</sup> This parameter is output referred.

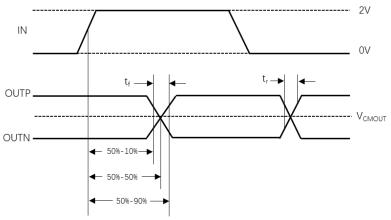

# 2.10 Typical Characteristics

VDD1 = 5V, VDD2 = 3.3V,  $V_{IN} = 2V$ , SHTDN = 0V,  $f_{IN} = 10$ kHz, and BW = 100kHz (unless otherwise noted)

Figure 3. Input Offset Voltage vs Supply Voltage

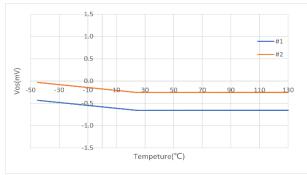

Figure 4. Input Offset Voltage vs Temperature

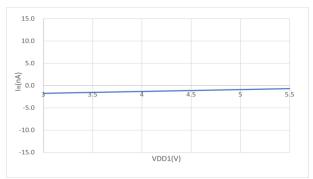

Figure 5. Input Bias Current vs High-Side Supply Voltage

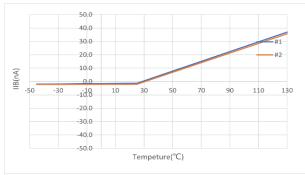

Figure 6. Input Bias Current vs Temperature

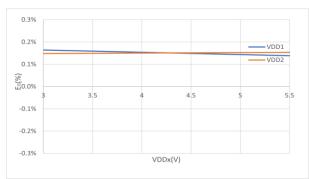

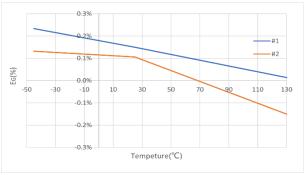

Figure 7. Gain Error vs Supply Voltage

Figure 8. Gain Error vs Temperature

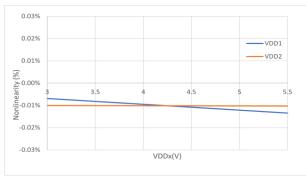

Figure 9. Nonlinearity vs Supply Voltage

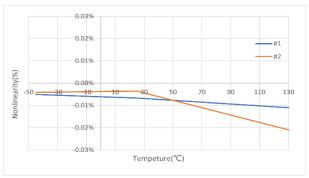

Figure 10. Nonlinearity vs Temperature

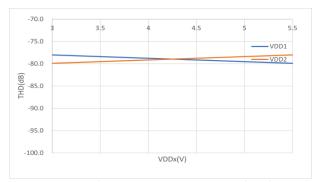

Figure 11. Total Harmonic Distortion vs Supply Voltage

Figure 13. Signal-to-Noise Ratio vs Supply Voltage

Figure 15. Power-Supply Rejection Ratio vs Supply Voltage

Figure 17. Supply Current vs Supply Voltage

Figure 12. Total Harmonic Distortion vs Temperature

Figure 14. Signal-to-Noise Ratio vs Temperature

Figure 16. Power-Supply Rejection Ratio vs Temperature

Figure 18. Supply Current vs Temperature

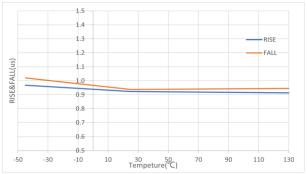

Figure 19. Output Rise and Fall Time vs Low-Side Supply

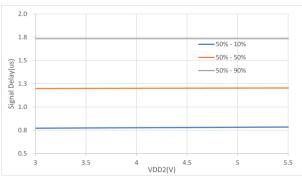

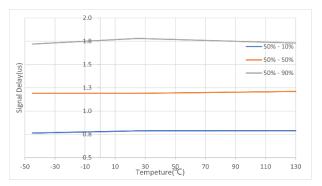

Figure 21. VIN to VOUT Signal Delay vs Low-Side Supply Voltage

Figure 20. Output Rise and Fall Time vs Temperature

Figure 22. VIN to VOUT Signal Delay vs Temperature

## 3 Detailed Description

#### 3.1 Overview

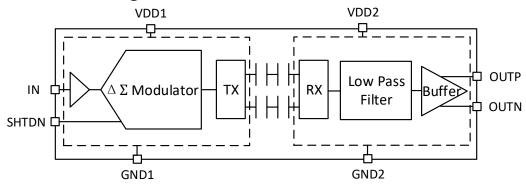

The CH1311B single is a -ended input, precision, isolated amplifier with a high input impedance and wide input voltage range. The input stage drives a second-order, delta-sigma ( $\Delta\Sigma$ ) modulator. The modulator generates data pulse. The drivers (called TX in the Functional Block Diagram) transfer the data pulse of the modulator across the isolation barrier. The received data pulse is synchronized and processed, as shown in the Functional Block Diagram, by a low pass filter and out buffer on the low-side and presented as a differential output of the device.

CH1311B adopts single channel transfer architecture and saves one clock channel, compared with current other amplifiers products, CH1311B has the lowest power consumption. CH1311B also uses Intelligent voltage divider technology (iDivider® technology) which is a new generation digital isolator technology invented by Tokmas to support a high level of magnetic field immunity.

#### 3.2 Function block diagram

## 3.3 Feature Description

## 3.3.1 Analog Input

The single-ended, high-impedance input stage of the CH1311B feeds a second-order, switched-capacitor, feed-forward  $\Delta\Sigma$  modulator. The modulator converts the analog signal into data pulse that is transferred across the isolation barrier, as described in patented iDivider® technology.

There are two restrictions on the analog input signals (IN). First, if the input voltage exceeds the range GND1-6V to VDD1+0.5V, the input current must be limited to 10mA because the device input electrostatic discharge (ESD) diodes turn on. In addition, the linearity and noise performance of the device are ensured only when the analog input voltage remains within the specified linear full-scale range (FSR).

### 3.3.2 Isolation Channel Signal Transmission

The CIH1311B uses the patentediDivider® technology to transmit the modulator output data pulse across the SiO<sub>2</sub> - based isolation barrier. The CH1311B also uses special circuit techniques to maximize the CMTI performance and minimize the radiated emissions caused by the high-frequency carrier and IO buffer switching.

#### 3.3.3 Failsafe Output

The CH1311B offers a fail-safe output that simplifies diagnostics on a system level. The fail-safe output is active when the high-side supply VDD1 of the CH1311B is missing.

The fail-safe outputs a negative differential output voltage value that does not occur under normal device operation which is marked as  $V_{\text{FAILSAFE}}$  and specified in the electrical characteristics table as a reference value for the fail-safe detection on a system level.

## **4 Application and Implementation**

## 4.1 Application Information

The high input impedance, low input bias current, low AC and DC errors, and low temperature drift make the CH1311B a high-performance solution for automotive applications where voltage sensing in the presence of high common-mode voltage levels is required.

### 4.2 Input Filter Design

Placing an RC filter in front of the isolated amplifier improves signal-to-noise performance of the signal path. In practice, however, the impedance of the resistor divider is high and only a small-value filter capacitor can be used to not limit the signal bandwidth to an unacceptable low value. Design the input filter such that:

- The cutoff frequency of the filter is at least one order of magnitude lower than the sampling frequency (20 MHz) of the internal  $\Delta\Sigma$  modulator.

- The input bias current does not generate significant voltage drop across the DC impedance of the input filter Most voltage-sensing applications use high-impedance resistor dividers in front of the isolated amplifier to scale down the input voltage. In this case, a single capacitor (as shown in Figure 23) is sufficient to filter the input signal.

Figure 23. Input Filter Design

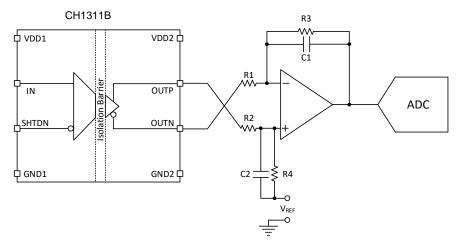

#### 4.3 Differential to Single-Ended Output Conversion

Figure 24 shows an example of an amplifier-based signal conversion and filter circuit for systems using single-ended input ADCs to convert the analog output voltage into digital. With R1 = R2 = R3 = R4, the output voltage equals (VOUTP – VOUTN) + VREF. Tailor the bandwidth of this filter stage to the bandwidth requirement of the system and use NPO-type capacitors for best performance. For most applications, R1 = R2 = R3 = R4 = 3.3 k $\Omega$  and C1 = C2 = 330 pF yields good performance.

Figure 24. Connecting the CH1311B Output to a Single-Ended Input ADC

## 4.4 Power Supply Recommendations

In a typical frequency inverter application, the high-side power supply (VDD1) for the device is directly derived from the floating power supply of the upper gate driver. For lowest system-level cost, a Zener diode can be used to limit the voltage to 5V or  $3.3V \pm 10\%$ . Alternatively, a low-cost low-dropout (LDO) regulator may be used to minimize noise on the power supply. A low-ESR decoupling capacitor of  $0.1\mu F$  to filter this power-supply path is recommended. Place this capacitor as close as possible to the VDD1 pin of the CH1311B for best performance.

If better filtering is required, an additional 2.2 $\mu$ F capacitor may be used. The floating ground reference (GND1) is derived from the end of the sensing resistor, which is connected to the shut-down pin of the device. To decouple the low-side power supply on the controller side, use a 0.1 $\mu$ F capacitor placed as close to the VDD2 pin of the CH1311B as possible, followed by an additional capacitor from 1  $\mu$ F to 10  $\mu$ F.

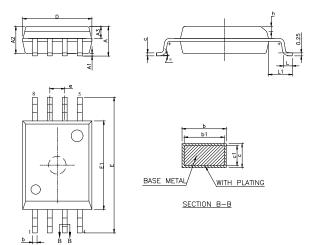

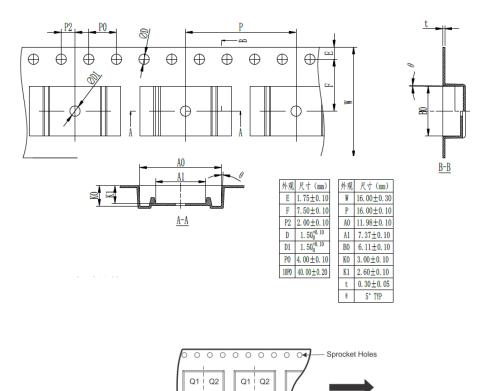

## **5 Outline Dimensions**

| avn mov | MILLIMETER |       |       |  |

|---------|------------|-------|-------|--|

| SYMBOL  | MIN        | NOM   | MAX   |  |

| A       | _          | _     | 2.65  |  |

| A1      | 0.10       | _     | 0.30  |  |

| A2      | 2.25       | 2.30  | 2.35  |  |

| A3      | 0.97       | 1.02  | 1.07  |  |

| b       | 0.39       |       | 0.47  |  |

| b1      | 0.38       | 0.41  | 0.44  |  |

| c       | 0.25       | _     | 0.29  |  |

| c1      | 0.24       | 0.25  | 0.26  |  |

| D       | 5.75       | 5.85  | 5.95  |  |

| Е       | 11.30      | 11.50 | 11.70 |  |

| E1      | 7.40       | 7.50  | 7.60  |  |

| e       | 1.27BSC    |       |       |  |

| h       | 0.25       |       | 0.50  |  |

| L       | 0.50       |       | 1.00  |  |

| L1      | 2.00REF    |       |       |  |

| θ       | 0          | _     | 8°    |  |

Figure 25. Outline Package

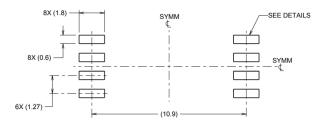

### **6 Land Patterns**

The Fig.26 illustrates the recommended land pattern details for the CH1311B in an 8-pin wide-body SOIC package.

Figure 26. WB-SOIC-8 Land Pattern

#### Note:

- (1) This land pattern design is based on IPC -7351

- (2) All feature sizes shown are at maximum material condition and a card fabrication tolerance of 0.05 mm is assumed.

## **8 Reel Information**

Pocket Quadrants

Figure 28. Reel Information

Note: The Pin 1 of the chip is in the quadrant Q1.

Q3

# 9 Ordering Guide

| Model Name  | Temperature Range | Withstand Voltage<br>Rating (kV <sub>RMS</sub> ) | Package   | MSL Peak Temp <sup>1</sup> | Quantity per Reel |

|-------------|-------------------|--------------------------------------------------|-----------|----------------------------|-------------------|

| CH1311BDWVR | -40~125°C         | 5.0                                              | WB SOIC-8 | Level-3-260C-168 HR        | 1000              |

<sup>(1)</sup> The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.