# 1. 特性

低噪声可编程增益放大器 (PGA) 和高分辨率 24 位模数转换器 (ADC)

- 可编程增益: 1/2/3/4/6/8/12/24/48

- 4路差分输入或者8路单端输入

- 支持增益误差、失调误差自校准

- 最大积分非线性: 13 PPM/FS

- 可编程输出速率: 2.5SPS-30kSPS

连续采样模式: 525μA待机电流: 0.2 μA

• 12 位电压输出型数模转换器(DAC)

- 输出范围: 0~2.5V

- 支持最大电阻负载 1kΩ,电容负载 200pF

• 集成温度传感器

• TIA 跨阻放大器

集成两路可编程激励电流源:

100nA/50μA/100μA/250μA/500μA/750μA/1mA

内置低温漂参考源: 25ppm/℃

• 内置振荡器

电源

- 模拟: 2.4V 至 3.6V - 数字: 1.7V 至 3.6V

4线SPI接口

工作温度范围: -40°C ~+125°C封装: 5mm x5mm QFN40

# 2. 应用

• 电桥变送器

• 便携式设备

• 电池监测

• 工业测温

• 工厂自动化过程控制

# 3. 功能描述

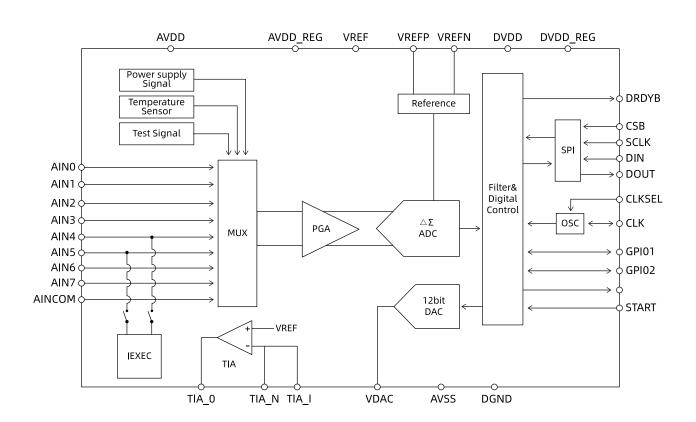

LH001-55 是一款低噪声 24 位 ΣΔADC, 提供完整的高分辨率测量解决方案。集成多路选择 MUX 和增益可调 PGA, 可灵活处理差分或单端信号。可编程滤波器允许用户在分辨率和输出速率之间做最优的选择。芯片内部集成了可编程激励电流源以及温度传感器。同时集成了 12 位电压输出型 DAC。4-线 SPI 接口,支持菊花链扩展多路 ADC 实现同时采样

## 4. 结构框图

# 目录

| 1. | 特性                    | 1  |

|----|-----------------------|----|

| 2. | 应用                    | 1  |

| 3. | 功能描述                  | 1  |

| 4. | 结构框图                  | 1  |

| 5. | 版本历史                  | 4  |

|    | 管脚定义和功能描述             |    |

| Ο. | 6.1. 绝对最大额定值          |    |

|    | 6.2. ESD 额定值          |    |

|    | 6.3. 建议工作条件           |    |

|    | 6.4. 热性能信息            |    |

|    | 6.5. 电气特性             |    |

|    | 6.6. 典型特性             |    |

|    |                       |    |

| 7. | 噪声特性                  | 13 |

| 8. | 模拟功能模块详细介绍            | 15 |

|    | 8.1. 输入选择器 (MUX)      | 15 |

|    | 8.2. PGA 及 ADC        | 16 |

|    | 8.3. 激励电流源            | 17 |

|    | 8.4. 温度传感器            | 17 |

|    | 8.5. 参考电压             | 18 |

| 9. | 数字功能模块介绍              | 19 |

|    | 9.1. 时钟               | 19 |

|    | 9.2. SPI              | 20 |

|    | 9.2.1. 时序需求           |    |

|    | 9.2.2. SPI 接口         |    |

|    | 9.2.3. 数据检索           |    |

|    | 9.2.4. 数据就绪引脚 (DRDYn) |    |

|    | 9.2.5. 启动模式           |    |

|    | 9.2.6. 建立时间           |    |

|    | 9.2.7. 单次转换模式        | . 25       |

|----|----------------------|------------|

|    | 9.2.8. 多器件配置         | . 25       |

|    | 9.2.9. SPI 命令定义      | . 28       |

| Ć  | 9.3. SINC3           | . 32       |

| Ć  | 9.4. 中断              | . 33       |

|    | 9.4.1. 寄存器列表         | . 34       |

| Ć  | 9.5. FIFO            | . 35       |

| Ć  | 9.6. GPIO            | . 36       |

|    | 9.6.1. 结构图           | . 36       |

|    | 9.6.2. Power down 模式 | . 36       |

| 10 | . 寄存器描述              | . 37       |

| 11 | . 封装丝印信息             | . 45       |

| 12 | . 订购信息               | . 45       |

| -  | 12.1. 编带规格           | <b>交</b> 。 |

| ,  | 12.2                 | 15         |

# 5. 版本历史

| 版本号   | 日期          | 变更说明                                  |

|-------|-------------|---------------------------------------|

| PreA  | 2022年3月5日   | 初版                                    |

| PreB  | 2022年6月20日  | 更新信息                                  |

| PreC  | 2022年7月12日  | 增加封装丝印信息                              |

| Rev.A | 2023年3月23日  | 量产                                    |

| Rev.B | 2023年10月24日 | 首页增加 PGA=3,                           |

| Rev.C | 2023年11月10日 | 1. 纠正表 14,表 15,INT_OEN, FIFO_STA 偏移地址 |

| Nev.C |             | 2. 更新功耗测试数据,更新恒流源精度 Spec              |

| Rev.D | 2024年6月12日  | 增加 PLTFMPD 寄存器                        |

| Rev.E | 2024年8月23日  | 管脚描述中增加上下拉说明,增加 GPIO 寄存器描述            |

# 6. 管脚定义和功能描述

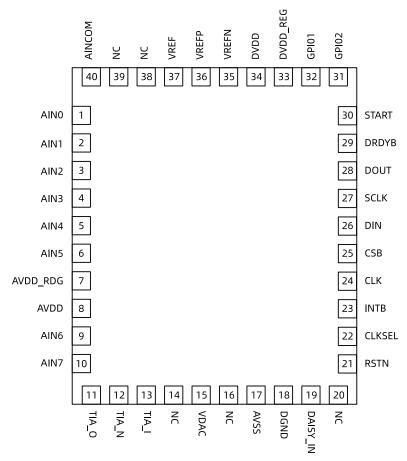

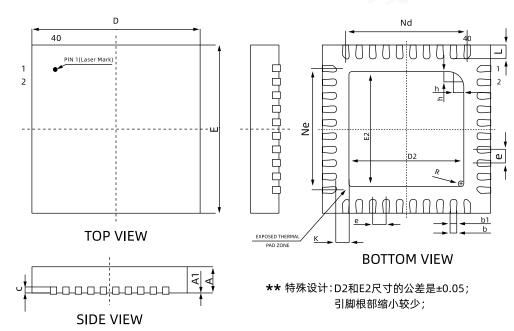

图1.40 脚 QFN 管脚

表1. 管脚描述

| QFN40 | 名称       | 类型   | 说明                              |

|-------|----------|------|---------------------------------|

| 1     | AIN0     | 模拟输入 | ADC 模拟输入 AIN0                   |

| 2     | AIN1     | 模拟输入 | ADC 模拟输入 AIN1                   |

| 3     | AIN2     | 模拟输入 | ADC 模拟输入 AIN2                   |

| 4     | AIN3     | 模拟输入 | ADC 模拟输入 AIN3                   |

| 5     | AIN4     | 模拟输入 | ADC 模拟输入 AIN4                   |

| 6     | AIN5     | 模拟输入 | ADC 模拟输入 AIN5                   |

| 7     | AVDD_REG | 模拟输出 | 模拟 1.8V LDO 输出,外接对地 AVSS 1μF 电容 |

| 8     | AVDD     | 电源   | 模拟电源                            |

| 9     | AIN6     | 模拟输入 | ADC 模拟输入 AIN6                   |

| 10    | AIN7     | 模拟输入 | ADC 模拟输入 AIN7                   |

| 11    | TIA_O    | 模拟输出 | TIA 输出端                         |

| 12    | TIA_N    | 模拟输入 | TIA 负输入端                        |

| 13    | TIA_I    | 模拟输入 | TIA 输入                          |

| 14    | NC       |      | 建议浮空                            |

| 15    | VDAC0    | 模拟输出 | VDAC 通道 0 输出                    |

| 16    | NC       |      | 建议浮空                            |

| 17    | AVSS     | 电源   | 模拟地                             |

| 18    | DGND     | 电源   | 数字地                             |

| 19    | DAISY_IN | 数字输入 | 菊花链输入;内部有弱上拉,不使用时悬空。            |

| 20    | NC       | 电源   | 建议接地                            |

| 21    | RSTN     | 数字输入 | 系统复位;低电平有效,内部有弱上拉。              |

| QFN40 | 名称       | 类型      | 说明                             |

|-------|----------|---------|--------------------------------|

| 22    | CLKSEL   | 数字输入    | 选择主时钟,内部有弱上拉                   |

| 23    | INTB     | 数字输出    | 数字中断指示信号;低电平有效,内部有弱上拉          |

| 24    | CLK      | 数字输入/输出 | 外部主时钟输入或内部时钟输出                 |

| 25    | CSB      | 数字输入    | SPI 片选; 低电平有效                  |

| 26    | DIN      | 数字输入    | SPI 数据输入                       |

| 27    | SCLK     | 数字输入    | SPI 时钟                         |

| 28    | DOUT     | 数字输出    | SPI 数据输出                       |

| 29    | DRDYB    | 数字输出    | 数据准备好指示;低电平有效,内部有弱上拉           |

| 30    | START    | 数字输入    | 控制 ADC 开始转换                    |

| 31    | GPIO0    | 数字输入/输出 | 通用输入输出引脚 0                     |

| 32    | GPIO1    | 数字输入/输出 | 通用输入输出引脚1                      |

| 33    | DVDD_REG | 数字输出    | 数字 1.8V LDO 输出,外接对 DGND 1μF 电容 |

| 34    | DVDD     | 电源      | 数字电源                           |

| 35    | VREFN    | 模拟输入    | ADC 模拟参考地,必须接 AVSS             |

| 36    | VREFP    | 模拟输入/输出 | ADC 正端参考电压,外接 10µF 电容到 VREFN   |

| 37    | VREF     | 模拟输出    | 内置参考电压,外接 1μF 电容到 AVSS         |

| 38    | NC       |         | 建议浮空                           |

| 39    | NC       |         | 建议浮空                           |

| 40    | AINCOM   |         | 单端共模输入                         |

## 6.1. 绝对最大额定值

在自然通风温度范围内测得 (除非另有说明)

# 表2. 额定电压值

|                 | 最小值      | 最大值      | 单位 |

|-----------------|----------|----------|----|

| AVDD 至 AVSS     | -0.3     | 3.9      | V  |

| DVDD 至 DGND     | -0.3     | 3.9      | V  |

| AVSS 至 DGND     | -0.3     | 0.3      | V  |

| AVSS 的 VREFP 输入 | AVSS-0.3 | AVDD+0.3 | V  |

| 模拟输入电压          | AVSS-0.3 | AVDD+0.3 | V  |

| 数字输入电压          | DGND-0.3 | DVDD+0.3 | V  |

| 数字输出电压 DGND     | DGND-0.3 | DVDD+0.3 | V  |

| 输入电流 (瞬时)       |          | 100      | mA |

# 6.2. ESD 额定值

# 表3. 表 3. ESD 额定值

| V(ESD) 静电释放 | 人体放电模式(HBM),符合 ANSI/ESDA/JEDEC JS-001,所有引脚 | ±2000 | V |

|-------------|--------------------------------------------|-------|---|

| V(ESD) 静电释放 | 充电器件模型(CDM),符合 JEDEC 规范 JESD22-C101,所有引脚   | ±500  | V |

# 6.3. 建议工作条件

# 表4. 工作条件

|                 | 最小值 | 典型值 | 最大值 | 单位 |

|-----------------|-----|-----|-----|----|

| 电源              |     |     |     |    |

| 模拟电源(AVDD-AVSS) | 2.4 | 3.3 | 3.6 | V  |

| 数字电源(DVDD)      | 1.7 | 1.8 | 3.6 | V  |

| 模拟输入            |     |     |     |    |

## LH001-55: 集成 PGA 功能和内部基准的 24-位模数转换器

| 满标量程差分转    | 满标量程差分输入电压范围                                  |          | ±VREF/增益 |      | V   |  |  |

|------------|-----------------------------------------------|----------|----------|------|-----|--|--|

| 绝对输入电压     |                                               | AVSS-0.1 |          | AVDD | V   |  |  |

| 电压基准输入     |                                               |          | 2.5      | AVDD | V   |  |  |

| 差分基准       | AVDD $\geq$ 2.4V, $V_{REF} = (VREFP - VREFN)$ |          | 2        |      | V   |  |  |

| 电压         | AVDD $\geq$ 2.7V, $V_{REF} = (VREFP - VREFN)$ |          | 2.5      |      | V   |  |  |

| 负输入(VREFN) | 负输入(VREFN)                                    |          | AVSS     |      | V   |  |  |

| 正输入(VREFP) |                                               |          | AVSS+2.5 |      | V   |  |  |

| 时钟输入       |                                               |          |          |      |     |  |  |

| 外部时钟输入     | 频率 CLKSEL 引脚=0                                | 1.94     | 2.048    | 2.25 | MHz |  |  |

| 数字输入       |                                               |          |          |      |     |  |  |

| 输入电压       |                                               | DGND     |          | DVDD | V   |  |  |

| 工作温度范围     |                                               | -40      |          | 125  | °C  |  |  |

|            |                                               |          |          |      |     |  |  |

# 6.4. 热性能信息

# 表5. 热性能

| R <sub>e,A</sub> 结至环境热阻  | 35 °C/W  |

|--------------------------|----------|

| Rex(top) 结至外壳(顶部)热阻      | 31 °C/W  |

| R <sub>0.6</sub> 结至电路板热阻 | 26 °C/W  |

| ψπ 结至顶部特征参数              | 0.1 °C/W |

# 6.5. 电气特性

所有规格的适用条件为: DVDD = 3.3V, AVDD – AVSS = 3.3V, VREF = 2.5V, 工作温度范围-40℃~125℃外部 Fcik = 2.048MHz, Modclk=512KHz,数据速率(Foik) = 500SPS, 以及增益= 6(除非另有说明)。 表6. 由气特性

| 表6. 电气特性    |                                 |                       |           |          |              |

|-------------|---------------------------------|-----------------------|-----------|----------|--------------|

| 参数          | 测试条件                            | 最小值                   | 典型值       | 最大值      | 单位           |

| 模拟输入        |                                 |                       |           |          |              |

| 差分输入电压      |                                 |                       | ±VREF/PGA |          | V            |

| 绝对输入电压      |                                 | AVSS-0.1              |           | AVDD-0.1 | V            |

| 输入电容        |                                 |                       | 20        |          | pF           |

|             | T <sub>A</sub> = -40°C 至 125°C, |                       |           | ±300     | рА           |

| 输入电流        | 输入= 2.5V                        |                       |           |          |              |

| (chop=8,pga | 其他 gain,输入电压条件                  |                       |           | 参考典型特性   |              |

| gain=12)    |                                 |                       |           |          |              |

| PGA 性能      |                                 |                       |           |          |              |

| 增益设置        |                                 | 1,2,4,6,8,12,24,32,48 |           |          |              |

| ADC 性能      |                                 |                       |           |          |              |

| 分辨率         | 无丢失码 24 位                       | 24                    |           |          | Bits         |

| 数据速率        | F <sub>CLK</sub> =2.048MHz      | 2.5                   |           | 30K      | SPS          |

| 输入参考噪声      | 增益= 24, 4096 点, 32              |                       |           | 1        | $\mu V_{PP}$ |

|             | 秒的数据(125SPS)                    |                       |           |          |              |

|             | 增益= 6, 4096 点, 32 秒             |                       | 1.25      |          |              |

|             | 的数据(125SPS)                     |                       |           |          |              |

|             | 增益= 24, 4096 点, 8 秒             |                       | 2.18      |          |              |

|             | 的数据(500SPS)                     |                       |           |          |              |

|             | 增益= 6, 4096 点, 8 秒              |                       | 2.85      | 7        |              |

| l           | 的数据(500SPS)                     |                       |           |          |              |

| legendsemi.co |                                           |              |                  | GA 功能和内部基准的 |         |

|---------------|-------------------------------------------|--------------|------------------|-------------|---------|

| 参数            | 测试条件                                      | 最小值          | 典型值              | 最大值         | 单位      |

|               | 增益设置≠ 24 and ≠<br>6,数据速率≠ 250SPS<br>等其他条件 | 参考 Noise 典型特 | 特性章节<br>         |             |         |

| 积分非线性         | 满标量程,最佳拟合                                 |              | ±8               |             | ppm     |

| 失调误差          | 校正前, PGA gain=1                           |              | 15               |             | μV      |

|               | 校正后, PGA gain=1                           |              | noise level      |             | μV      |

| 失调误差漂移        |                                           |              | 30               |             | nV/°C   |

| 增益误差          | 不包括电压基准误差,                                |              | 0.1              | ±0.5        | % of FS |

|               | PGA gain= 1                               |              |                  |             |         |

|               | 校正后,PGA gain= 1                           |              | ±0.005           |             | % of FS |

| 增益漂移          | 不包括电压基准漂移                                 |              | 3                |             | ppm/°C  |

| 外部基准          |                                           |              |                  |             |         |

| 输入阻抗          |                                           |              | 5.6              |             | kΩ      |

| 参考输入电压        |                                           | 0.5          | 2.5              | AVDD        | V       |

| (VREFP)       |                                           |              |                  |             |         |

| 内部基准          |                                           |              |                  |             |         |

| 输出电压          | 寄存器位 BUFCON[5]=                           |              | 2                |             | V       |

|               | 0,                                        |              |                  |             |         |

|               | AVDD ≥ 2.4V                               |              |                  |             |         |

|               | 寄存器位 BUFCON[1] =                          |              | 2.5              |             | V       |

|               | 1,                                        |              |                  |             |         |

|               | AVDD ≥ 2.7V                               |              |                  |             |         |

| VREF 精度       |                                           |              | ±0.2             |             | %       |

| 内部基准漂移        |                                           |              | 10               | 25          | ppm/°C  |

| 启动时间          |                                           |              | 150              |             | mS      |

| 激励电流源(AIN4、A  | AIN5)                                     |              |                  |             |         |

| 输出电流          |                                           |              | 0.1/50/100/250/5 | 500/        | μΑ      |

|               |                                           |              | 750/1000         |             |         |

|               |                                           |              |                  |             |         |

| 电流精度          |                                           |              | ±10              |             | %       |

| 温漂            |                                           |              | 50               |             | ppm/°C  |

| 输出范围          |                                           | AVSS-0.05    |                  | AVDD-0.4    | V       |

| VDAC          |                                           |              |                  | ·           |         |

| 分辨率           |                                           | 12           |                  |             | Bit     |

| 积分非线性 (INL)   |                                           |              | ±2               |             | LSB     |

| 差分非线性(DNL)    |                                           | -0.5         |                  | +0.5        | LSB     |

| 失调电压          |                                           |              | ±3               |             | mV      |

| 增益误差          |                                           |              | ±0.3             |             | %       |

| 输出电压范围        |                                           | 0            |                  | 2.5         | V       |

|               |                                           | 0            |                  | AVDD-0.15   | V       |

| 建立时间          |                                           |              | 5                |             | μS      |

| 毛刺能量          |                                           |              | ±20              |             |         |

| 系统监控          | ı                                         | 1            | l                |             | 1       |

| 模拟电源读数误差      |                                           |              | 2                |             | %       |

| 数字电源读数误差      |                                           |              | 2                |             | %       |

| 器件唤醒          | 从上电到 DRDY 为低电                             |              | 150              |             | mS      |

|               | 平                                         |              |                  |             |         |

|               | ı                                         | I.           | l                | 1           |         |

# LH001-55: 集成 PGA 功能和内部基准的 24-位模数转换器

|             |                                                       |                                                                         | 11001-331 来风10 | A 切能和内部基准的 24 | - 区长数程 大 |

|-------------|-------------------------------------------------------|-------------------------------------------------------------------------|----------------|---------------|----------|

| 参数          | 测试条件                                                  | 最小值                                                                     | 典型值            | 最大值           | 单位       |

|             | 待机模式                                                  |                                                                         | 31.25          |               | μS       |

| 温度传感器读数,电   | 温度传感器读数,电压                                            |                                                                         | 145300         |               | μV       |

| 压           | TA = 25°C                                             |                                                                         |                |               |          |

| 温度传感器读数,系   |                                                       |                                                                         | 490            |               | μV/°C    |

| 数           |                                                       |                                                                         |                |               |          |

| 测试信号频率      |                                                       | F <sub>CLK</sub> / 2 <sup>21</sup> , F <sub>CLK</sub> / 2 <sup>20</sup> |                |               | Hz       |

| 测试信号电压      |                                                       | ±2.5                                                                    |                |               | mV       |

| 测试信号精度      |                                                       |                                                                         | ±2             |               | %        |

| 时钟          |                                                       |                                                                         | 1              |               | 1        |

| 内部振荡器时钟频率   | 标称频率                                                  |                                                                         |                |               | MHz      |

|             |                                                       |                                                                         | 2.048/16.384   |               |          |

| 内部时钟频率      | TA = 25°C                                             |                                                                         |                | ±0.5          | %        |

|             | -40°C ≤TA ≤ 125°C                                     |                                                                         |                | ±3            | %        |

| 内部振荡器启动时间   |                                                       |                                                                         | 20             |               | μs       |

| 内部振荡器功耗     |                                                       |                                                                         | 120            |               | μW       |

| 数字输入/输出(DVD | D = 1.7V 至 3.6V)                                      |                                                                         |                | •             | •        |

| VIH 高电平输入电压 |                                                       | 0.8 DVDD                                                                |                | DVDD + 0.1    | V        |

| VIL 低电平输入电压 |                                                       | -0.1                                                                    |                | 0.2 DVDD      | V        |

| VOH 高电平输出电  | I <sub>OH</sub> = -500 μA                             | 0.9 DVDD                                                                |                |               | V        |

| 压           |                                                       |                                                                         |                |               |          |

| VOL 低电平输出电  | Ι <sub>οι</sub> = +500 μΑ                             |                                                                         |                | 0.1 DVDD      | V        |

| 压           |                                                       |                                                                         |                |               |          |

| IIN 输入电流    | $0 \text{ V} < V_{\text{DigitalInput}} < \text{DVDD}$ | -10                                                                     |                | 10            | μΑ       |

| 功耗          |                                                       |                                                                         | 1              |               | 1        |

| AVDD 电流     | AVDD = 3.3V                                           |                                                                         | 205            |               | μΑ       |

| DVDD 电流     | DVDD = 3V                                             |                                                                         | 320            |               | μΑ       |

| 工作功耗        | AVDD = 3.3V                                           |                                                                         | 1.8            |               | mW       |

|             | DVDD = 3.3V                                           |                                                                         |                |               |          |

| Standby     |                                                       |                                                                         | 0.2            |               | μA       |

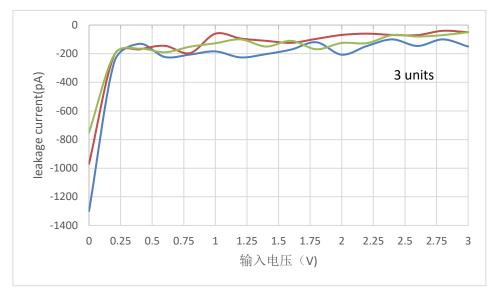

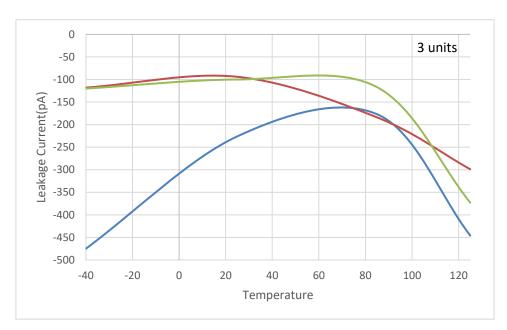

## 6.6. 典型特性

图2. Leakage current Vs 输入电压, Fmodclk=512KHz, chop=8KHz

图3. Leakage Vs Temperature, Fmodclk=512KHz, chop=8KHz, 输入电压 1.2V

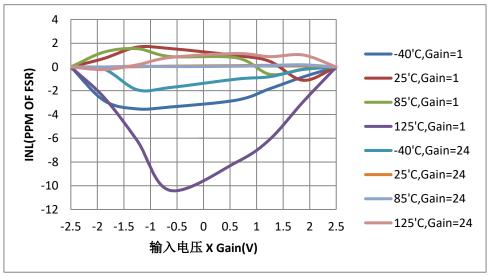

图4. INL Vs 不同输入电压, Fmodclk=512K,内部 2.5V Reference

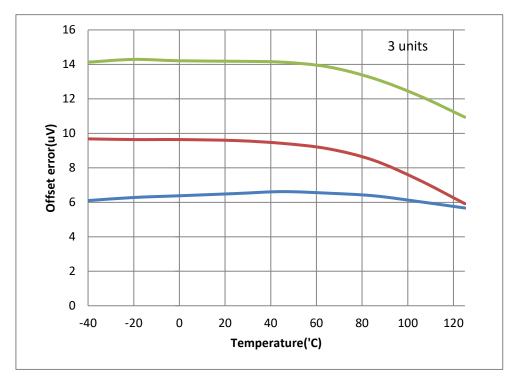

图5. Offset error drift

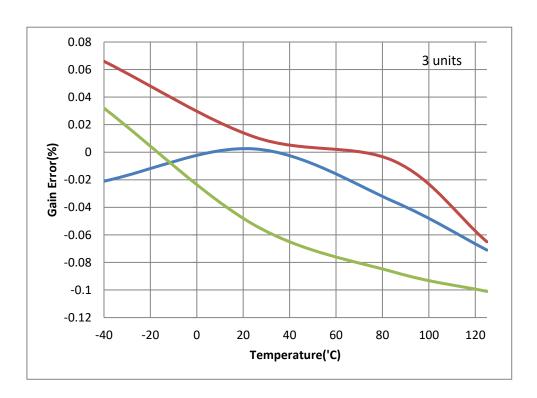

图6. Gain error drift

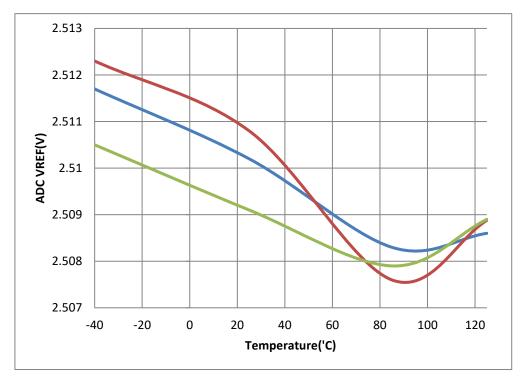

图7. 内部 2.5v Reference 温度漂移

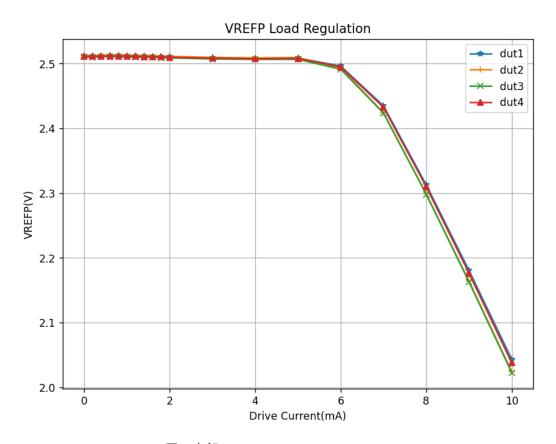

图8. 内部 2.5v Reference Load Regulation

# 7. 噪声特性

本节表格显示了不同输出速率,增益条件下的等效输入噪声特性。所有数据基于 2.5V 参考电压和 3.3V 模拟电源,采用全差分测量 0V 输入电压, ADC Fmodclk=512KHz。

表7. 等效输入噪声有效值(uRMS)、峰峰值(uVpp)与增益,输出数据速率的关系

|               |                   |                         | 曾益=1  | G (PP) J-H III     | PGA 增益=2             |                      |       |                    |

|---------------|-------------------|-------------------------|-------|--------------------|----------------------|----------------------|-------|--------------------|

| 数据速率<br>(SPS) | μV <sub>RMS</sub> | $\mu V_{	ext{	iny PP}}$ | ENOB  | Noise-Free<br>BITS | $\mu V_{\text{RMS}}$ | $\mu V_{	extsf{PP}}$ | ENOB  | Noise-Free<br>BITS |

| 30000         | 261.41            | 2374.35                 | 14.22 | 11.04              | 130.96               | 1208.48              | 14.22 | 11.01              |

| 15000         | 108.77            | 964.4                   | 15.49 | 12.34              | 54.86                | 471.77               | 15.48 | 12.37              |

| 7500          | 54.97             | 476.84                  | 16.47 | 13.36              | 27.66                | 225.15               | 16.46 | 13.44              |

| 3750          | 27.62             | 214.58                  | 17.47 | 14.51              | 13.91                | 125.91               | 17.46 | 14.28              |

| 2000          | 14.86             | 114.44                  | 18.36 | 15.42              | 7.59                 | 60.65                | 18.33 | 15.33              |

| 1000          | 7.78              | 56.32                   | 19.29 | 16.44              | 3.89                 | 27.86                | 19.29 | 16.45              |

| 500           | 4.02              | 29.5                    | 20.25 | 17.37              | 1.99                 | 13.56                | 20.26 | 17.49              |

| 100           | 1.09              | 6.56                    | 22.13 | 19.54              | 0.56                 | 3.57                 | 22.09 | 19.42              |

| 60            | 0.76              | 4.47                    | 22.65 | 20.09              | 0.39                 | 2.38                 | 22.61 | 20.00              |

| 50            | 0.66              | 3.87                    | 22.85 | 20.30              | 0.33                 | 2.09                 | 22.85 | 20.19              |

| 30            | 0.51              | 3.27                    | 23.22 | 20.54              | 0.25                 | 1.64                 | 23.25 | 20.54              |

| 25            | 0.49              | 2.68                    | 23.28 | 20.83              | 0.23                 | 1.34                 | 23.37 | 20.83              |

| 15            | 0.35              | 2.08                    | 23.77 | 21.20              | 0.17                 | 1.09                 | 23.81 | 21.13              |

| 10            | 0.28              | 1.19                    | 24.09 | 22.00              | 0.14                 | 0.89                 | 24.09 | 21.42              |

| 5             | 0.18              | 0.59                    | 24.73 | 23.01              | 0.1                  | 0.45                 | 24.58 | 22.41              |

| 2.5           | 0.15              | 0.3                     | 24.99 | 23.99              | 0.08                 | 0.29                 | 24.90 | 23.04              |

| <b>松</b> 中 '  |                   | PGA ‡                    | 曾益=3  |                    |                      | PGA ±        | 曾益=4  |                    |

|---------------|-------------------|--------------------------|-------|--------------------|----------------------|--------------|-------|--------------------|

| 数据速率<br>(SPS) | μV <sub>RMS</sub> | $\mu V_{	ext{\tiny PP}}$ | ENOB  | Noise-Free<br>BITS | $\mu V_{\text{RMS}}$ | $\mu V_{PP}$ | ENOB  | Noise-Free<br>BITS |

| 30000         | 89.63             | 812.71                   | 14.18 | 11.00              | 69.54                | 641.35       | 14.13 | 10.93              |

| 15000         | 38.16             | 356.83                   | 15.41 | 12.19              | 30.52                | 265.01       | 15.32 | 12.20              |

| 7500          | 19.16             | 176.62                   | 16.41 | 13.20              | 15.26                | 132.47       | 16.32 | 13.20              |

| 3750          | 9.8               | 82.05                    | 17.38 | 14.31              | 7.79                 | 66.23        | 17.29 | 14.20              |

| 2000          | 5.31              | 40.03                    | 18.26 | 15.35              | 4.19                 | 36.35        | 18.19 | 15.07              |

| 1000          | 2.71              | 22.35                    | 19.23 | 16.19              | 2.17                 | 17.43        | 19.14 | 16.13              |

| 500           | 1.44              | 10.33                    | 20.14 | 17.30              | 1.13                 | 8.42         | 20.08 | 17.18              |

| 100           | 0.4               | 2.48                     | 21.99 | 19.36              | 0.32                 | 2.23         | 21.90 | 19.10              |

| 60            | 0.28              | 1.78                     | 22.51 | 19.84              | 0.22                 | 1.41         | 22.44 | 19.76              |

| 50            | 0.27              | 1.68                     | 22.56 | 19.92              | 0.2                  | 1.19         | 22.58 | 20.00              |

| 30            | 0.19              | 1.19                     | 23.06 | 20.42              | 0.15                 | 0.82         | 22.99 | 20.54              |

| 25            | 0.16              | 0.99                     | 23.31 | 20.68              | 0.12                 | 0.59         | 23.31 | 21.01              |

| 15            | 0.13              | 0.59                     | 23.61 | 21.43              | 0.1                  | 0.52         | 23.58 | 21.20              |

| 10            | 0.1               | 0.49                     | 23.99 | 21.70              | 0.07                 | 0.37         | 24.09 | 21.69              |

| 5             | 0.07              | 0.29                     | 24.51 | 22.45              | 0.05                 | 0.22         | 24.58 | 22.44              |

| 2.5           | 0.05              | 0.19                     | 24.99 | 23.06              | 0.05                 | 0.14         | 24.58 | 23.09              |

| ** 10 4 4     |                       | PGA:         | 增益=3  |                    |                   | PGA:             | 增益=4  |                    |

|---------------|-----------------------|--------------|-------|--------------------|-------------------|------------------|-------|--------------------|

| 数据速率<br>(SPS) | $\mu V_{	extsf{RMS}}$ | $\mu V_{PP}$ | ENOB  | Noise-Free<br>BITS | μV <sub>RMS</sub> | μV <sub>РР</sub> | ENOB  | Noise-Free<br>BITS |

| 30000         | 50.25                 | 469.98       | 14.02 | 10.79              | 41.31             | 394.88           | 13.89 | 10.63              |

| 15000         | 23.03                 | 220.84       | 15.14 | 11.88              | 19.77             | 202.73           | 14.95 | 11.59              |

| 7500          | 11.74                 | 110.42       | 16.12 | 12.88              | 10.1              | 94.06            | 15.92 | 12.70              |

| 3750          | 6.01                  | 49.47        | 17.08 | 14.04              | 5.27              | 41.72            | 16.86 | 13.87              |

| 2000          | 3.19                  | 24.74        | 17.99 | 15.04              | 2.75              | 22.99            | 17.79 | 14.73              |

| 1000          | 1.65                  | 13.06        | 18.95 | 15.96              | 1.43              | 11.85            | 18.74 | 15.69              |

| 500           | 0.89                  | 7.8          | 19.84 | 16.71              | 0.77              | 5.36             | 19.63 | 16.83              |

| 100           | 0.24                  | 1.54         | 21.73 | 19.05              | 0.24              | 1.42             | 21.31 | 18.75              |

| 60            | 0.19                  | 0.99         | 22.06 | 19.68              | 0.16              | 0.93             | 21.90 | 19.36              |

| 50            | 0.16                  | 0.99         | 22.31 | 19.68              | 0.15              | 0.89             | 21.99 | 19.42              |

| 30            | 0.12                  | 0.64         | 22.73 | 20.31              | 0.11              | 0.71             | 22.44 | 19.75              |

| 25            | 0.11                  | 0.6          | 22.85 | 20.41              | 0.08              | 0.41             | 22.90 | 20.54              |

| 15            | 0.08                  | 0.4          | 23.31 | 20.99              | 0.06              | 0.37             | 23.31 | 20.69              |

| 10            | 0.06                  | 0.3          | 23.73 | 21.41              | 0.06              | 0.3              | 23.31 | 20.99              |

| 5             | 0.04                  | 0.14         | 24.31 | 22.51              | 0.04              | 0.18             | 23.90 | 21.73              |

| 2.5           | 0.02                  | 0.09         | 25.31 | 23.14              | 0.03              | 0.11             | 24.31 | 22.44              |

| <b>料</b> 把 '  |                   | PGA 增        | 益=12  |                    |               | PGA 增                           | 益=24  |                    |

|---------------|-------------------|--------------|-------|--------------------|---------------|---------------------------------|-------|--------------------|

| 数据速率<br>(SPS) | μV <sub>RMS</sub> | $\mu V_{PP}$ | ENOB  | Noise-Free<br>BITS | $\mu V_{RMS}$ | $\mu V_{\scriptscriptstyle PP}$ | ENOB  | Noise-Free<br>BITS |

| 30000         | 33.5              | 314.51       | 13.60 | 10.37              | 27.37         | 266.79                          | 12.89 | 9.61               |

| 15000         | 16.92             | 180.23       | 14.59 | 11.17              | 14.8          | 165.64                          | 13.78 | 10.30              |

| 7500          | 8.8               | 79.94        | 15.53 | 12.35              | 7.72          | 78.18                           | 14.72 | 11.38              |

| 3750          | 4.62              | 40.63        | 16.46 | 13.32              | 4.14          | 37.1                            | 15.62 | 12.46              |

| 2000          | 2.41              | 25.18        | 17.40 | 14.01              | 2.12          | 19.55                           | 16.58 | 13.38              |

| 1000          | 1.26              | 10.6         | 18.34 | 15.26              | 1.08          | 8.33                            | 17.56 | 14.61              |

| 500           | 0.68              | 5.09         | 19.22 | 16.32              | 0.6           | 4.86                            | 18.41 | 15.39              |

| 100           | 0.2               | 1.39         | 20.99 | 18.19              | 0.19          | 1.18                            | 20.06 | 17.43              |

| 60            | 0.15              | 0.84         | 21.41 | 18.92              | 0.13          | 0.76                            | 20.61 | 18.06              |

| 50            | 0.13              | 0.72         | 21.61 | 19.14              | 0.11          | 0.7                             | 20.85 | 18.18              |

| 30            | 0.09              | 0.52         | 22.14 | 19.61              | 0.09          | 0.5                             | 21.14 | 18.67              |

| 25            | 0.09              | 0.47         | 22.14 | 19.76              | 0.08          | 0.37                            | 21.31 | 19.10              |

| 15            | 0.06              | 0.4          | 22.73 | 19.99              | 0.06          | 0.27                            | 21.73 | 19.56              |

| 10            | 0.06              | 0.27         | 22.73 | 20.56              | 0.05          | 0.22                            | 21.99 | 19.85              |

| 5             | 0.03              | 0.15         | 23.73 | 21.41              | 0.03          | 0.14                            | 22.73 | 20.51              |

| 2.5           | 0.03              | 0.1          | 23.73 | 21.99              | 0.02          | 0.09                            | 23.31 | 21.14              |

| 数据速率                      | PGA 增益=48         |                      |       |                    |  |  |  |  |

|---------------------------|-------------------|----------------------|-------|--------------------|--|--|--|--|

| 致循述 <del>学</del><br>(SPS) | μV <sub>RMS</sub> | $\mu V_{	extsf{PP}}$ | ENOB  | Noise-Free<br>BITS |  |  |  |  |

| 30000                     | 25.44             | 250.89               | 12.00 | 8.70               |  |  |  |  |

| 15000                     | 14.14             | 140.9                | 12.85 | 9.53               |  |  |  |  |

| 7500                      | 7.42              | 77.85                | 13.78 | 10.39              |  |  |  |  |

| 3750                      | 3.97              | 33.29                | 14.68 | 11.61              |  |  |  |  |

| 2000                      | 2.01              | 20.43                | 15.66 | 12.32              |  |  |  |  |

| 1000 | 1.06 | 8.76 | 16.58 | 13.54 |

|------|------|------|-------|-------|

| 500  | 0.58 | 5.12 | 17.45 | 14.31 |

| 100  | 0.18 | 1.29 | 19.14 | 16.30 |

| 60   | 0.12 | 0.7  | 19.73 | 17.18 |

| 50   | 0.11 | 0.69 | 19.85 | 17.20 |

| 30   | 0.08 | 0.48 | 20.31 | 17.73 |

| 25   | 0.08 | 0.43 | 20.31 | 17.89 |

| 15   | 0.06 | 0.26 | 20.73 | 18.61 |

| 10   | 0.05 | 0.23 | 20.99 | 18.79 |

| 5    | 0.03 | 0.12 | 21.73 | 19.73 |

| 2.5  | 0.03 | 0.09 | 21.73 | 20.14 |

## 8. 模拟功能模块详细介绍

## 8.1. 输入选择器 (MUX)

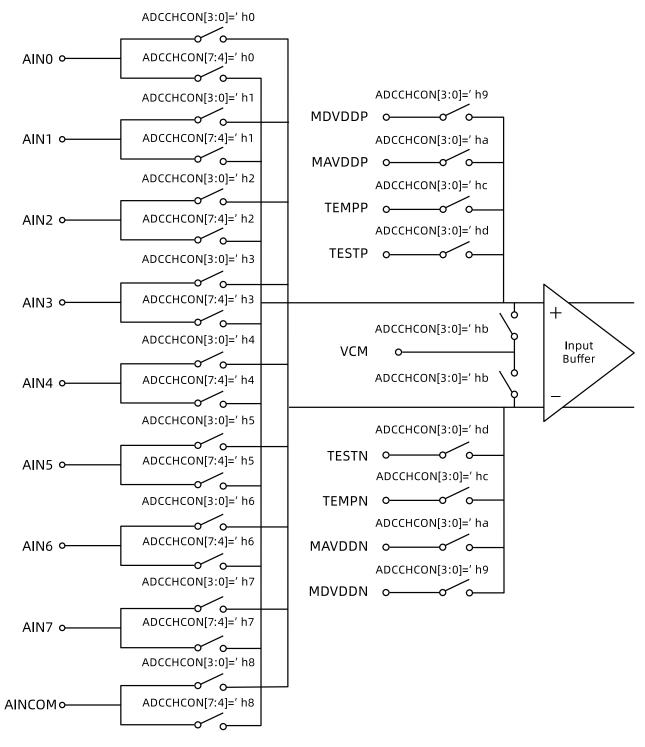

外部输入通道既可以配置成差分,也可以配置成单端,既可以配置与 ADC 的正输入端,也可以配置到 ADC 的负输入端,由寄存器 ADCCHCON 控制实现上述功能。

LH001-55 提供了8个输入,可以配置成4对差分输入和可以配成8路单端输入。差分通道建议配置相邻通道,比如AIN0/AIN1。单端配置建议将AINCOM配置成共模输入,AIN0~7位单端输入通道。不使用的通道建议浮空,从而减少输入漏电,AINCOM可以连接到地或者VREFP。

如果测量 ADC 信号链的噪声,可以通过配置寄存器 ADCCHCON.PSEL=0xb, ADCCHCON.NSEL=0xf 将输入 短接到共模电平。

如果上电做子系统验证,可以设置 ADCCHCON.PSEL=0xd, ADCCHCON.NSEL=0xf 提供内部生成的测试信号利用该功能测试整个信号链。该信号幅度固定为±2.5mV。

如果测试片内电压源,可以设置 ADCCHCON.PSEL= 0x9 或者 0xa, ADCCHCON.NSEL=0xf,选择 AVDD, 但实际测量的电压值为: (MAVDDP – MAVDDN) = 0.5 × (AVDD – AVSS)。同理测量 DVDD, 实际测量的电压值为: (MDVDDP – MDVDDN) = 0.5 x (DVDD-DVSS)。为避免在测量电源时使 PGA 饱和,请将增益 PGA\_GAIN.GAIN 设置为 1。

图9. 输入选择结构框图

#### 8.2. PGA 及 ADC

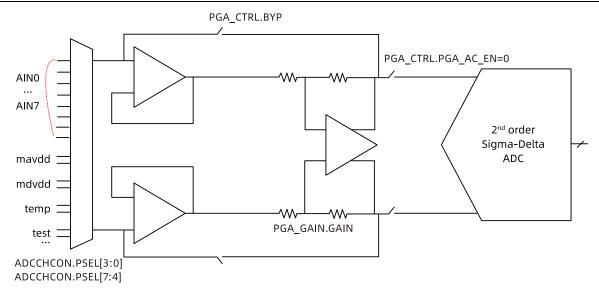

外部模拟输入 AIN0~AIN7 通过 MUX 选通,参考寄存器 ADCCHCON。PGA 对于全差分输入,输入电压的范围是 +/-VREF/Gain。 增益可以配置为 1,2,3,4,6,8,12,24,48,参考寄存器 PGA\_GAIN。PGA 的输入如系统图所示包含两个输入缓冲器,输入缓冲器的输出驱动主 PGA 增益放大部分。因为输入 Buffer 的使用,平均输入电流可以限制在 300pA 范围,适合外部阻抗比较大的应用。基于图中的电路结构,输入电压的绝对值可以在{AVSS-100mV, AVDD-100mV}范围,共模电压灵活变化,差分电压不超过满幅电压。

图10. ADC 信号链结构图

上图 ADC 信号链路 24 位 Sigma-Delta ADC,为 2 阶开关电容结构。其采样时钟频率在高精度模式下最高 FMODCLK= 512kHz。与任何  $\Delta$ - $\Sigma$  调制器的情况一样,此 ADC 噪声会整形到  $F_{MOD}/2$ 。可使用数字抽取滤波器部分中介绍的片上数字抽取滤波器来滤除较高频率的噪声。这些片上抽取滤波器还提供抗混叠滤波。

$\Delta$ - $\Sigma$  转换器的这一特性可极大地降低奈奎斯特 ADC 通常所需的抗混叠滤波器的复杂性。

## 8.3. 激励电流源

芯片上集成了低噪声可编程激励电流源,通过设置寄存器 IEXECON 可以开启激励电流源并且配置电流到 AIN4、AIN5 管脚上,IEXC\_MAG 可以设置电流的为 100nA,50uA,100uA,250uA,500uA,750uA 和 1mA。 这些电流源可以用来激励外部阻性电桥或 RTD 传感器。两个电流源均从 AVDD 获得电流。

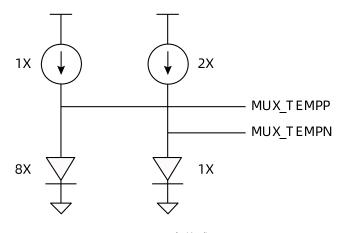

## 8.4. 温度传感器

LH001-55 包含一个片上温度传感器, 该传感器使用两个内部二极管, 其中一个二极管的电流密度是另一个二极管的 16 倍。二极管的电流密度的差异可产生与绝对温度成比例的电压差。

图11. 温度传感器

由于封装到印刷电路板(PCB) 的低热阻,内部传感器可密切跟踪 PCB 温度。LH001-55 的自发热会导致读数高于周围 PCB 的温度。等式的比例因子可将温度读数转换为 $^\circ$ C。在使用该公式之前,应将温度读数代码转换 $\mu$ V。

Temperature (°C) =

$$\left[ \frac{\text{Temperature Reading } (\mu V) - 145,300 \ \mu V}{490 \ \mu V/^{\circ}C} \right] + 25^{\circ}C$$

## 8.5. 参考电压

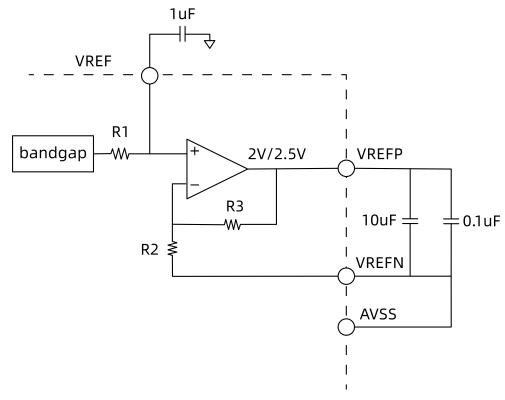

图 12 显示了 LH001-55 内部基准的简化方框图。该基准电压是相对于 AVSS 生成的。在使用内部电压基准时,需要将 VREFN 连接到 AVSS。

图12. 内部基准

# 9. 数字功能模块介绍

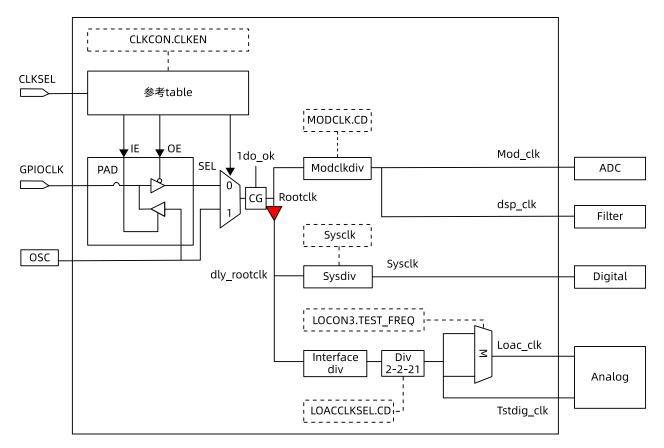

## 9.1. 时钟

图13. 时钟架构

- 1) 时钟源来自内部的 OSC 和外部输入 CLK

- 2) OSC 频率 2.048MHz

- 3) 外部输入 CLK 如不使用 PAD 时钟,PAD 时钟源必须接低,如果使用外部输入 CLK,确保上电期间时钟为固定电平

- 4) CLKSEL 和 CLKCON.CLKEN 配合实现选择(表格 8) 内部 OSC 作为系统主时钟 外部输入 CLK 时钟作为主时钟

表8. clock 配置

| CLKSEL PAD | CLKCON.CLKEN | CLOCK SOURCE | CLK PAD status | IE | OE |

|------------|--------------|--------------|----------------|----|----|

| 0          | ×            | 外部时钟         | 输入外部时钟         | 1  | 0  |

| 1          | 0            | 内部时钟         | 三态 (default)   | 0  | 0  |

| 1          | 1            | 内部时钟         | 输出内部时钟         | 0  | 1  |

#### 9.2. SPI

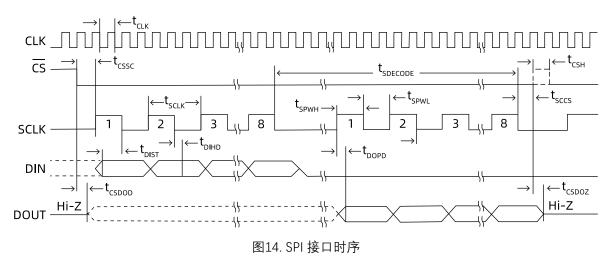

## 9.2.1. 时序需求

注意: SPI 设置为 CPOL = 0 且 CPHA = 1。

表9. 时序要求

| 参数       | 说明                        | 最小值  | 典型值 | 最大值 | 单位    |

|----------|---------------------------|------|-----|-----|-------|

| tclk     | 主时钟周期                     | 62.5 |     | 500 | ns    |

| tcssc    | <br>CS 低电平至第一个 SCLK, 建立时间 | 6    |     |     | ns    |

| tsclk    | SCLK 周期                   | 50   |     |     | ns    |

| tspwh, L | SCLK 脉冲宽度,高电平和低电平         | 15   |     |     | ns    |

| tdist    | DIN 有效至 SCLK 下降沿: 建立时间    | 10   |     |     | ns    |

| tDIHD    | SCLK 下降沿之后的有效 DIN: 保持时间   | 10   |     |     | ns    |

| tDOPD    | SCLK 上升沿至 DOUT 有效: 建立时间   |      |     | 12  | ns    |

| tCSH     | <br>CS 高电平脉冲              | 2    |     |     | †CLKs |

| tcsdod   | <br>CS 低电平至 DOUT 驱动       | 10   |     |     | ns    |

| tsccs    | 第八个 SCLK 下降沿至 CS 高电平      | 3    |     |     | †CLKs |

| tsdecode | 命令解码时间                    | 4    |     |     | tCLKs |

| tCSDOZ   | <br>CS 高电平至 DOUT Hi-Z     |      |     | 10  | ns    |

规格适用于  $T_A = -40^{\circ}C$  至  $+85^{\circ}C$  (除非另外说明)。Dout 上的负载 =  $20pF \parallel 100k\Omega$ 。

## 9.2.2. SPI 接口

# (1) 片选引脚 (CSn)

片选 (CSn) 可选择用于 SPI 通信的 LH001-55 器件。当 CSn 处于低电平时,串行接口处于活动状态。在

整个串行通信过程中, CSn 必须保持低电平。串行通信完成后, 始终等待四个或更多 tax 周期, 然后再将 CSn 置于高电平。当 CSn 置于高电平时, 串行接口复位, SCLK 和 DIN 被忽略, DOUT 进入高阻抗状态。无论 CSn

处于高电平还是低电平,当数据转换完成时,DRDY都会变为有效。选择LH001-55后,器件会尝试每八个串行时钟解码并执行一次命令。如果器件停止执行串行命令,则可能出现了额外的时钟脉冲,使串行接口进入未知状态。要将串行接口重置为已知状态,请将CSn置为高电平,然后再次置为低电平。

## (2) 串行时钟 (SCLK)

SCLK 是串行外设接口 (SPI) 串行时钟。它用于移入命令并从器件中移出数据。串行时钟 (SCLK) 在 DIN 和 DOUT 引脚上按照时钟脉冲将数据移入和移出 LH001-55。尽管输入存在迟滞, 仍应尽可能保持 SCLK 的纯净, 以防因干扰而意外强制执行时钟事件。时序要求: 串行接口表中指定了 SCLK 的绝对最大限制。

选择 LH001-55(CSn = low) 后,器件会尝试每八个串行时钟解码并执行一次命令。因此,在每次串行传输时提供八个 SCLK 的倍数,以使接口保持正常工作模式。如果接口由于额外的串行时钟而停止工作,则通过将

CS 切换为高电平并重新切换为低电平进行复位。

对于单个器件, SCLK 所需的最低速度取决于通道数、分辨率位数和输出数据速率。有关多个级联器件, 请参阅级联配置部分。Equation 1, 2 显示了最低 SCLK 速度的计算方法。

DC mode = 0 :  $t_{SCLK} < (t_{DR} - 4t_{CLK})/(NBITS \times NCHANNELS + 24)$  (1) DC mode = 1 :  $t_{SCLK} < (t_{DR} - 4t_{CLK})/(NBITS \times NCHANNELS)$  (2)

例如,在直流模式关闭情况下,根据公式 1 如果以 500SPS 的数据速率使用 LH001-55 (一个通道, 24 位分辨率,系统时钟 16.384MHZ),则最小 SCLK 速度为 41.66kHz。

#### (3) 数据输入引脚 (DIN)

数据输入引脚 (DIN) 与 SCLK 一起用于与 LH001-55 通信(操作码命令和寄存器数据)。该器件在 SCLK 的下降沿锁存 DIN 中的数据。

#### (4) 数据输出引脚 (DOUT)

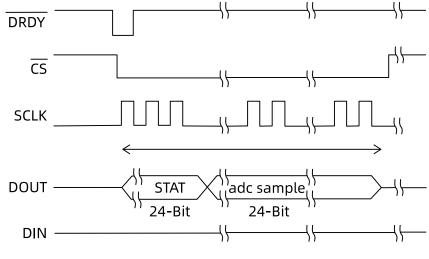

数据输出引脚 (DOUT) 与 SCLK 一起用于从LH001-55中读取转换和寄存器数据。DOUT 中的数据在 SCLK —— 的上升沿移出。DOUT 在 CS 处于高电平时进入高阻抗状态。下图中表示 LH001-55 的 DOUT 时序, 如果是 DC mode 打开的情况下没有图中的 24bit 的 STAT, 只输出 24bits 的 ADC 数据。

图15. SPI 总线数据输出

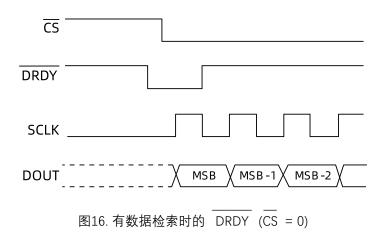

#### 9.2.3. 数据检索

可通过以下两种方法之一完成数据检索:

- 1. RDATAC: 连续读取数据命令设置在不发送操作码的情况下连续读取数据的器件模式。有关更多详细信息,请参阅 RDATAC: 连续读取数据 部分。

- 2. RDATA: 读取数据命令仅从器件中读取一个数据输出。有关更多详细信息, 请参阅 RDATA: 读取数据 部分。

有关更多详细信息,请参阅 SPI 命令定义部分。

可通过在 DOUT 上移出数据来读取转换数据。DOUT 上数据的 MSB 在第一个 SCLK 上升沿随时钟输出。

DRDY 会在第一个 SCLK 下降沿返回至高电平。在整个读取操作期间将 DIN 保持为低电平。

LH001-55 还提供多回读功能。将寄存器中的 DAISY\_EN 位设置为 0(即关闭菊花链功能)可实现多回读功能。 只需提供额外的 SCLK 即可多次读取数据;读取最后一个字节后 MSB 数据字节会重复。

## 通道数据格式:

LH001-55 会以二进制补码格式在输出一个通道的 24 位的数据, MSB 在前。LSB 具有 VREF/(2\*\*23 - 1) 的权重。正满标量程输入可生成输出代码 7FFFFFh, 负满标量程输入可生成输出代码 800000h。输出在这些代码处针对超出满标量程的信号进行削波。下表总结了不同输入信号的理想输出代码。

表10. 通道数据格式

理想输出代码与输入信号间的关系

| 输入信号,V <sub>IN</sub> (IN <sub>x</sub> P-IN <sub>x</sub> N)  | 理想输出代码  |

|-------------------------------------------------------------|---------|

| ≥V <sub>REF</sub>                                           | 7FFFFFh |

| V <sub>REF</sub> /(2 <sup>23</sup> -1)                      | 000001h |

| 0                                                           | 000000h |

| -V <sub>REF</sub> /(2 <sup>23</sup> -1)                     | FFFFFFh |

| <-V <sub>REF</sub> /(2 <sup>23</sup> /(2 <sup>23</sup> -1)) | 800000h |

#### 9.2.4. 数据就绪引脚 (DRDYn)

DRDYn 是输出。当 DRDYn 转换为低电平时,新转换数据就绪。CSn 信号对数据就绪信号没有任何影响。 无论 CSn 信号的状态如何, SCLK 上的上升沿都会将 DRDYn 拉至高电平。因此,在 SPI 总线中使用多个器件时,使用 CSn 来选通 SCLK。DRDYn 的行为取决于器件是否处于 RDATAC 模式或是否使用 RDATA 命令按需读取数据。有关更多详细信息,请参阅 RDATAC:连续读取数据 和 RDATA:读取数据 部分。

使用 RDATA 命令读取数据时,读取操作可能与出现的下一个 DRDY 重叠,但不会导致数据损坏。

使用 START 引脚或 START 命令将器件置于正常数据捕获模式或脉冲数据捕获模式。 下图显示了数据检索期间 DRDY、DOUT 和 SCLK 之间的关系。DOUT 在 SCLK 的上升沿锁存。无论是从器件检索数据还是通过 DIN 引脚发送命令,器件都会在 SCLK 的第一个下降沿将 DRDYn 拉为高电平。数据从状态字的 MSB 开始,然后再读取 ADC 通道数据。断电的通道仍然在数据流中有一个位置;但是数据无效,可以将其忽略。

无论 CSn 的状态如何,都会在第一个 SCLK 下降沿清除 DRDYn 信号。即使没有数据随时钟输出,也仍然会清除 DRDYn 信号。如果使用 SPI 总线与同一总线上的其他器件进行通信,请考虑此情况。

## 9.2.5. 启动模式

将 START 引脚拉为高电平并至少持续 2 个 tCLK 周期,或者发送 START 命令以开始转换。当 START 引 \_\_\_\_\_ 脚为低电平或未发送 START 命令时,器件不会发出 DRDY 信号(转换停止)。

使用 START 操作码开始转换时,将 START 引脚保持为低电平。LH001-55 具有两种控制转换的模式:连续和单冲。可通过 SINGLE\_SHOT (CONFIG1 寄存器的位 3)选择模式。在多器件配置中,START 引脚用于同步器件(有关更多详细信息,请参阅多器件配置部分)。

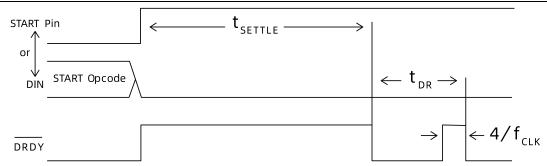

#### 9.2.6. 建立时间

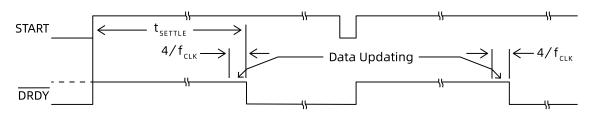

建立时间(tsettle) 是当 START 信号被拉为高电平时转换器输出完全稳定的数据所需的时间。

当 START 引脚被拉为高电平或发送 START 命令时, 器件 ADC 会转换输入信号并且 DRDY 被拉为高电

平。 DRDY 的下一个下降沿指示数据是可读的。下图显示了时序图,数据建立时间显示了不同数据速率下作为 tCLK 的 函数的建立时间。建立时间取决于 FCLK 和抽取率(由 CONFIG1 寄存器中的 DR[2:0] 位进行控制)。

图17. 转换建立时间

表11. 数据建立时间

| DR[2:0] | SETTLING TIME <sup>(1)</sup> | UNIT <sup>(2)</sup> |

|---------|------------------------------|---------------------|

| 000     | 4100                         | t <sub>MOD</sub>    |

| 001     | 2052                         | t <sub>MOD</sub>    |

| 010     | 1028                         | t <sub>MOD</sub>    |

| 011     | 516                          | t <sub>MOD</sub>    |

| 100     | 260                          | t <sub>MOD</sub>    |

| 101     | 132                          | t <sub>MOD</sub>    |

| 110     | 68                           | t <sub>MOD</sub>    |

| 111     | _                            | _                   |

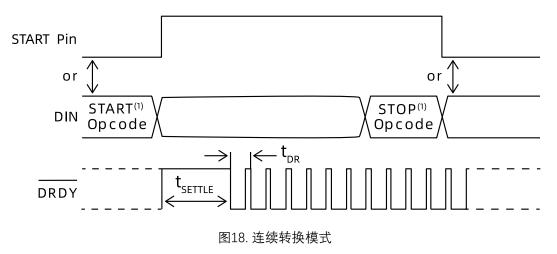

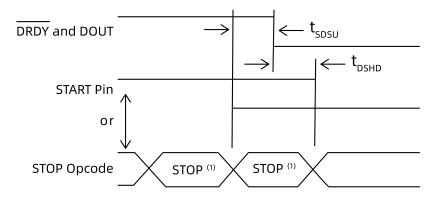

## 连续转换模式

当 START 引脚被置于高电平并至少保持两个 tclk 或发送 START 操作码命令时,将开始进行转换。如 18 所示,DRDYn 会在转换开始后变为高电平,并在数据就绪后变为低电平。转换会无限期地持续下去,直到 START 引脚被置为低电平或发送 STOP 操作码命令。当 START 引脚被拉为低电平或发出停止命令时,允许完成正在进行的转换。下图显示了在该模式下控制转换时 START 引脚以及 START 和 STOP 操作码命令所需的 DRDYn 时序。要使转换器保持连续运行,应将 START 引脚永久固定在高电平。从单冲模式切换到连续转换模式时,发送 START 脉冲信号,或发出 STOP 命令并后跟 START 命令。该转换模式非常适用于需要连续转换结果流的应用。

图19. START 至 DRDYn 时序

表12. 的时序要求

|                   |                                               | 最小值 | 最大值 | 单位               |

|-------------------|-----------------------------------------------|-----|-----|------------------|

| tsosu             | START 引脚置于低电平或向 DRDY 发送 STOP 操作码以中止进一步转换的设置时间 | 16  |     | t <sub>clk</sub> |

| t <sub>DSHD</sub> | START 引脚置于低电平或发送 STOP 操作码以完成当前转换              | 16  |     | t <sub>CLK</sub> |

#### 9.2.7. 单次转换模式

为需要非标准或非连续数据速率的应用提供了单冲转换模式。发出 START 命令或将 START 引脚切换为高电平可重置数字滤波器,从而有效地将数据速率降低为原来的四分之一。该模式使系统更容易受到混叠效应的影响,因此需要更复杂的模拟或数字滤波。主机处理器上的负载会增加,因为它必须切换 START 引脚或发送 START 命令以启动新的转换周期。

图20.1 无数据检索时的 DRDYn (单冲模式)

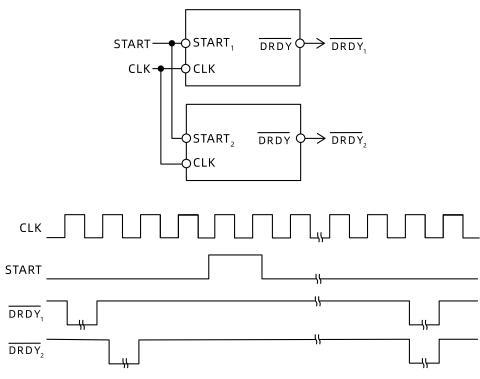

#### 9.2.8. 多器件配置

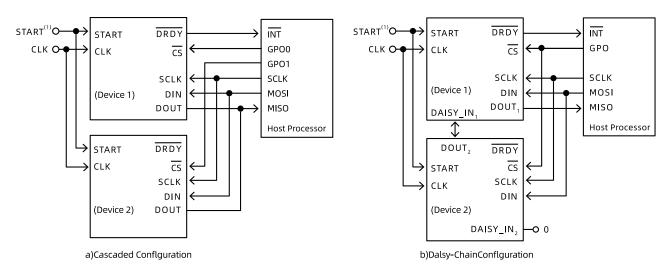

当系统中连接多个器件时,LH001-55 可提供配置灵活性。串行接口通常需要四个信号:DIN、DOUT、SCLK \_\_ 和CS。通过在每个器件上添加一个额外的片选信号,可以将多个器件连接在一起。连接 n 个器件所需的信号数量为 3+n。

如以菊花链方式连接多个器件。要以菊花链配置使用内部振荡器,请将其中一个器件设置为时钟源的主器件并启用内部振荡器 (CLKSEL 引脚 = 1),并通过将 CLK\_EN 寄存器位设置为 1 从器件获取内部振荡器时钟。使用该主器件时钟作为其他器件的外部时钟源。在使用多个器件时,将这些器件与 START 信号同步。从 START

信号到 DRDY 信号的延迟对于固定数据速率是固定的(有关建立时间的更多详细信息,请参阅启动模式部分)。 作为一个示例,下图显示了两个器件与 START 信号同步时的行为。 可使用两种配置以最佳接口引脚数来连接 多个器件:级联或菊花链。

#### 图21. 同步多个转换器

#### (1) 级联配置:

图 21 显示了两个器件级联在一起的配置。DOUT、SCLK 和 DIN 是共享的。每个器件都具有其自己的片选引脚。如果没有选择某个器件(通过将相应的 CSn 驱动为逻辑 1),则该器件的 DOUT 处于高阻抗。该结构允许其他器件控制 DOUT 总线。该配置方法适用于大多数应用。

#### (2) 菊花链配置:

可通过设置 SPI\_CTRL 寄存器中的 DAISY\_EN 位来启用菊花链模式;并且将第一个器件的 CLKSEL PAD 上拉为 1,配置寄存器 CLKCON的 CLKEN位为 1以便输出内部时钟;其他器件的 CLKSEL PAD 下拉为 0以便把第一个器件的输出时钟作为时钟源(详见如下表)。

| Bit-Name Bit CLKEN Description ena |              | 8<br>Width   | RW                | 0x6           | Yes       |                                       |          |      |    |            |        |            |

|------------------------------------|--------------|--------------|-------------------|---------------|-----------|---------------------------------------|----------|------|----|------------|--------|------------|

| CLKEN                              |              | Width        |                   |               |           | clock control register                |          |      |    |            |        |            |

|                                    | [0.0]        | PT AGEGRA    | Acess             | Default Value | Which Key | Description                           | Document | From | To | Scan Value | Retain | Visibility |

| Description ena                    | [0:0]        | 1            | RW                | 0x0           | USERKEYH  | enable osc or external clock          |          |      |    |            |        |            |

|                                    |              |              |                   |               |           |                                       |          |      |    |            |        |            |

| 0x0 osc                            | clock        |              |                   |               |           |                                       |          |      |    |            |        |            |

| 0x1 bas                            | sed clksel p | in select cl |                   |               |           |                                       |          |      |    |            |        |            |

| F2M                                | [1:1]        | 1            | RW                | 0x1           | USEKEY    | configure OSC frequency               |          |      |    |            |        |            |

| Description sele                   | ect OSC out  | put, 2Mh     | z or 16Mhz with 0 | x58 userkey   |           |                                       |          |      |    |            |        |            |

| 0x0 2M                             | 1hz          |              |                   |               |           |                                       |          |      |    |            |        |            |

| 0x1 16N                            | Mhz          |              |                   |               |           |                                       |          |      |    |            |        |            |

| CLKSEL_PU_EN                       | [2:2]        | 1            | RW                | 0x1           | USEKEY    | Enable clk sel pin pull-up resistor   |          |      |    |            |        |            |

|                                    |              |              | er for CLKSEL pin |               |           |                                       |          |      |    |            |        |            |

| 0x0 ena                            |              |              |                   |               |           |                                       |          |      |    |            |        |            |

| 0x1 disa                           | abel pull-u  | p register   |                   |               |           |                                       |          |      |    |            |        |            |

| PICTRL                             | 0x17         | 8            | RW                | 0x0           | No        | spi interface control                 |          |      |    |            |        |            |

| Bit-Name Bit                       | t-Position   | Width        | Acess             | Default Value | Which Key | Description                           | Document | From | To | Scan Value | Retain | Visibility |

| DAISY_EN                           | [0:0]        | 1            | RW                | 0x0           | NONE      | Enable daisy chain                    |          |      |    |            |        |            |

| Description Ena                    | able daisy c | hain         |                   | ·             |           | · · · · · · · · · · · · · · · · · · · |          |      |    |            |        |            |

| 0x0 disr                           | able daisy o |              |                   |               |           |                                       |          |      |    |            |        |            |

| 0x1 ena                            | able daisy c | hain         |                   |               |           |                                       |          |      |    |            |        |            |

| FIFO_SEL                           | [1:1]        | 1            | RW                | 0x0           | NONE      | Enable FIFO mode                      |          |      |    |            |        |            |

| Description Ena                    | able FIFO m  | ode          |                   |               |           |                                       |          |      |    |            |        |            |

|                                    | able FIFO n  |              |                   |               |           |                                       |          |      |    |            |        |            |

| 0x1 ena                            | able FIFO m  |              |                   |               |           |                                       |          |      |    |            |        |            |

| DC_MODE                            | [2:2]        | 1            | RW                | 0x0           | NONE      | Enable dc mode                        |          |      |    |            |        |            |

| Description Ena                    | able dc mod  | de           |                   |               |           |                                       |          |      |    |            |        |            |

| 0x0 disa                           | able dc mo   | de           |                   |               |           |                                       |          |      |    |            |        |            |

|                                    | able dc mod  |              |                   |               |           |                                       |          |      |    |            |        |            |

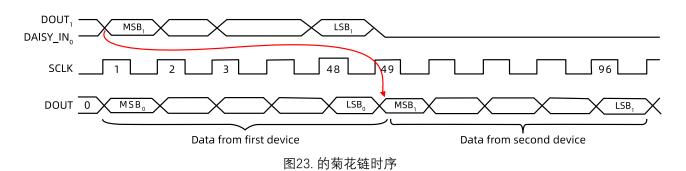

下图显示了菊花链配置。在该配置中, SCLK、DIN 和 CS 在多个器件之间共享。将第一个器件的 DOUT 引脚连接到下一个器件的 DAISY\_IN 引脚,从而创建一个链。在每个数据集之间发出一个额外的 SCLK。请注意,

在使用菊花链模式时、多读回功能不可用。

如果未使用 DAISY\_IN 引脚,则将其与数字地短接。图 23 介绍了图 22 所示的 LH001-55 所需的时序。来自 LH001-55 器件 1 的状态字和数据字首先出现在 DOUT 上,最后是来自 LH001-55 器件 2 的状态字和数据字。该时序图是针对 DC 模式关闭时,如果打开 DC 模式,时序图中只包含数据字而没有状态字。

(1) 要减少引脚数,请将 START 引脚设置为低电平并使用 START 操作码命令来同步和启动转换。

图22. 多器件配置

使用菊花链模式时的重要提醒:

- 1. 所有器件都配置为相同的寄存器值, 因为 CSn 是共享的。

- 2. 器件寄存器读回 (RREG) 仅对菊花链中的器件 0 有效。只能从器件 1 到器件 N 读取转换数据,其中 N 是链中的最后一个器件;无法读取寄存器数据。

如果链中的所有器件都在相同的寄存器设置下运行,则可以共享 DIN,从而将 SPI 通信信号数量减少为 4, 无论器件数量如何都是如此。不过,无法对单个器件进行编程;因此,无法在多个器件之间共享 RLD 驱动程序。 此外,所有器件需要共享一个 CLK 时钟。

SCLK 上升沿会在 DOUT 上将数据从 LH001-55 移出。SCLK 下降沿还用于将数据锁存到链中的器件 DAISY\_IN 引脚。此外请注意,菊花链模式需要一些软件开销来重新组合跨字节边界的数据位。

菊花链器件的最大数量取决于器件运行的数据速率。可以使用 Equation 3 来估算 DC 模式关闭时最大器件数,使用 Equation 4 来估算 DC 模式打开时最大器件数:

$$N_{DEVICES} = \frac{f_{SCLK}}{f_{DR} * N_{BITS} * N_{CHANNELS} + 24}$$

(3)

$$N_{DEVICES} = \frac{f_{SCLK}}{f_{DR} * N_{RITS} * N_{CHANNELS}} \tag{4}$$

其中

- NBITS = 器件分辨率, LH001-55 取 24

- NCHANNELS = 器件中的通道数, LH001-55 取 1

例如, 当 LH001-55 在 DC 模式关闭时以 2kSPS 数据速率和 4MHz fSCLK 运行时, 最多能够以菊花链方式连接 83 个器件。

#### 9.2.9. SPI 命令定义

LH001-55 可提供灵活的配置控制。表 13 中总结的操作码命令可控制和配置 LH001-55 的运行。操作码命令是独立的,但需要第二个命令字节加数据的寄存器读取和寄存器写入操作除外。可以将 CSn 在操作码命令之间置于高电平或保持在低电平,但在整个命令操作期间必须保持低电平(尤其是对于多字节命令)。所有操作码在第八个 SCLK 下降沿进行解码。发出命令后,将 CSn 拉为高电平时,确保遵循 SPI 时序要求。

表13. 操作码命令定义

| 命令       | 说明                    | 第一个字节           | 第二个字节     | 第三个字节                   |

|----------|-----------------------|-----------------|-----------|-------------------------|

| 系统命令     |                       |                 | •         |                         |

| RESET    | 复位器件                  | 0000 0110 (06h) |           |                         |

| START    | 启动/重新启动(同步)转换         | 0000 1000 (08h) |           |                         |

| STOP     | 停止转换                  | 0000 1010 (0Ah) |           |                         |

| RST_FIFO | 复位 FIFO               | 0000 1100 (0Ch) |           |                         |

| 数据读取命令   | ·                     |                 | •         |                         |

| RDATAC   | 启用连续读取数据模式。该模         | 0001 0000 (10h) |           |                         |

|          | 式是上电时的默认模式。           |                 |           |                         |

| SDATAC   | 停止连续读取数据模式            | 0001 0001 (11h) |           |                         |

|          |                       |                 |           |                         |

| RDATA    | 通过命令读取数据;支持多个         | 0001 0010 (12h) |           |                         |

|          | 读回。                   |                 |           |                         |

| 寄存器读写命令  |                       |                 | •         | ·                       |

| RREG     | 从地址 rrrrr 开始读取 n nnnn | 001r rrrr (2xh) | 000n nnnn |                         |

|          | 个寄存器                  |                 |           |                         |

| WREG     | 从地址 rrrrr 开始写入 n nnnn | 010r rrrr (4xh) | 000n nnnn |                         |

|          | 个寄存器                  |                 |           |                         |

| RREG_BK1 | 从地址 rrrrr+32 开始读取 n   | 101r rrrr (2xh) | 000n nnnn | 如果 r rrrr+32 等于 63,该字节需 |

|          | nnnn 个寄存器             |                 |           | 要输入 72h。否则无该字节。         |

| WREG_BK1 | 从地址 rrrrr+32 开始写入 n   | 110r rrrr (4xh) | 000n nnnn | 如果 r rrrr+32 等于 63,该字节需 |

|          | nnnn 个寄存器             |                 |           | 要输入 72h。否则无该字节。         |

n nnnn = 要读取/写入的寄存器数量 <math>-1。例如,要读取/写入三个寄存器,请设置 n nnnn = 0 0010。r rrrr = 读取/写入操作码的起始寄存器地址。

#### (1) RESET: 将寄存器重置为默认值

RESET 命令可重置数字滤波器周期并将所有寄存器设置恢复至相应的默认值。有关更多详细信息,请参阅复位(RESET 引脚和复位命令) 部分。对于该命令,SCLK 速率没有限制;可以随时发出该命令。执行 RESET 命令需要 18 个 tCLK 周期。请勿在此期间发送任何命令。

#### (2) START: 开始转换

该操作码可启动数据转换。将 START 引脚保持在低电平可通过命令控制转换。如果转换正在进行,那么该命令无效。STOP 操作码命令用于停止转换。如果 START 命令后紧跟 STOP 命令,那么这两个命令之间必须有 4 个 tCLK 周期的间隔。将 START 操作码发送到器件时,将 START 引脚保持为低电平,直到发出 STOP

命令。(有关更多详细信息,请参阅 SPI 接口部分的启动模式小节。)对于该命令, SCLK 速率没有限制,可以随时发出该命令。

#### (3) STOP: 停止转换

STOP 操作码可停止转换。将 START 引脚保持在低电平可通过命令控制转换。发送 STOP 命令后,正在进行的转换将完成,并且进一步的转换也会停止。如果转换已经停止,那么该命令无效。对于该命令,SCLK 速率没有限制;可以随时发出该命令。

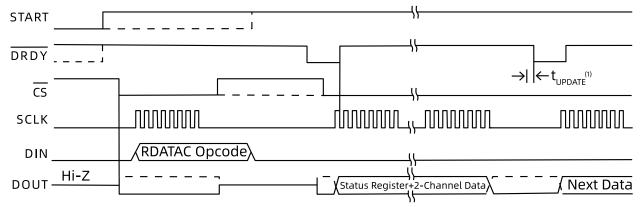

#### (4) RDATAC: 连续读取数据

RDATAC 操作码可以在每个 DRDY 上实现转换数据输出,而无需发出后续读取数据操作码。该操作码可将转换数据放置在输出寄存器中,可以直接将其移出。连续读取数据模式是该器件的默认模式,该器件在上电和复位时默认采用该模式。

停止连续读取数据命令 (SDATAC) 可取消 RDATAC 模式。如果器件处于 RDATAC 模式,则必须先发出 SDATAC 命令,然后才能将任何其他命令发送到器件中。对于该命令,SCLK 速率没有限制。不过,后续数据检

索 SCLK 或 SDATAC 操作码命令必须至少等待 4 个 tclk 周期。如下图所示,RDATAC 的时序说明了 DRDY 周围 4 个 tclk 周期的阻止区域,此时无法发出该命令。要在发出 RDATAC 命令后从器件检索数据,请确保 START 引脚处于高电平或发出 START 命令。 下图显示了使用 RDATAC 命令的建议方法。RDATAC 非常适合数据记录器等应用,其中只需设置寄存器一次,无需重新配置。

(1) t<sub>UPDATE</sub> = 4 x t<sub>CLK</sub> Do not read data during this time.

图24. RDATAC 用法

#### (5) SDATAC: 停止连续读取数据

该 SDATAC 操作码命令可取消连续读取数据 (RDATAC) 模式。对于该命令, SCLK 速率没有限制, 但下一条命令必须等待 4 个 tCLK 周期。

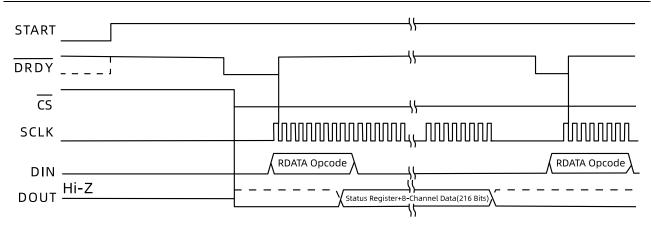

#### (6) RDATA: 读取数据

在 DRDY 变为低电平后发出 RDATA 命令,以读取转换结果(在 SDATAC 模式下)。对于该命令,SCLK 速率没有限制,后续命令或数据检索 SCLK 不需要等待时间。要在发出 RDATA 命令后从器件检索数据,请确保 START 引脚处于高电平或发出 START 命令。使用 RDATA 命令读取数据时,读取操作可能与出现的下一个

DRDY 重叠,但不会导致数据损坏。下图显示了使用 RDATA 命令的建议方法。

图25. RDATA 用法

#### (7) 发送多字节命令

LH001-55 串行接口以字节为单位对命令进行解码,需要 4 个 tclk 周期进行解码和执行。因此,在发送多字节命令时,4 个 tclk 周期必须将一个字节(或操作码)的末尾与下一个字节(或操作码)分开。

例如,如果 CLK 为 2.048MHz,那么  $t_{\text{DECODE}}$  (4 ×  $t_{\text{CLK}}$ )为  $1.96\mu$ S。当 SCLK 为 16.384MHz 时,一个字节的最大传输速度为 500nS。该字节传输时间不符合 tSDECODE 规格;因此,必须插入一个延迟,以便第二个字节的末尾在  $1.46\mu$ S 后到达。不过,如果 SCLK 为 4MHz,那么将在  $2\mu$ S 后传输一个字节。由于该传输时间超出了  $t_{\text{DECODE}}$  规格,因此处理器可以无延迟地发送后续字节。在第二种情形下,可以将串行端口编程为使用多字节传输,而不是满足第一种情形的时序所需的单字节传输。

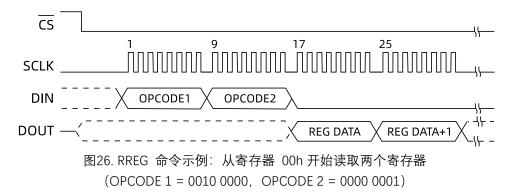

#### (8) RREG: 从地址 0 到 31 的寄存器进行读取

RREG 操作码命令可读取寄存器数据。RREG 命令是两字节操作码,后跟寄存器数据输出。第一个字节包含命令操作码和寄存器地址。操作码的第二个字节指定要读取的寄存器数量 -1。

第一个操作码字节: 001r rrrr, 其中 r rrrr 是起始寄存器地址。

第二个操作码字节: 000n nnnn, 其中 n nnnn 是要读取的寄存器数量 - 1。

运行的第 17 个 SCLK 上升沿输出第一个寄存器的 MSB, 如下图所示。当器件处于连续读数据模式时, 必须首先发出 SDATAC 命令, 然后才能发出 RREG 命令。可以随时发出 RREG 命令。不过, 由于该命令是多字节命令, 因此 SCLK 速率受到限制, 具体取决于发出 SCLK 的方式。有关更多详细信息, 请参阅串行时钟 (SCLK)

部分。CS 必须在整个命令操作期间处于低电平。

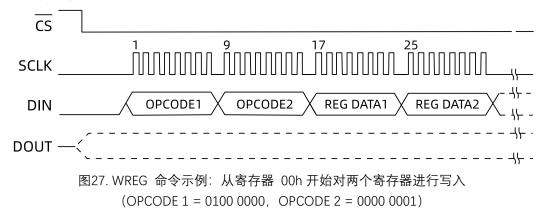

## (9) WREG: 对地址 0 到 31 的寄存器进行写入

WREG 操作码命令可写入寄存器数据。WREG 命令是两字节操作码,后跟寄存器数据输入。第一个字节包含命令操作码和寄存器地址。操作码的第二个字节指定要写入的寄存器数量 -1。

第一个操作码字节: 010r rrrr, 其中 r rrrr 是起始寄存器地址。

第二个操作码字节: 000n nnnn,其中 n nnnn 是要写入的寄存器数量 - 1。

操作码字节后跟寄存器数据(采用 MSB 在前的格式),如下图所示。可以随时发出 WREG 命令。不过,由于该命令是多字节命令,因此 SCLK 速率受到限制,具体取决于发出 SCLK 的方式。有关更多详细信息,请参阅串行时钟 (SCLK) 部分。CS 必须在整个命令操作期间处于低电平。

#### (10) RREG\_BK1: 从地址 32 到 63 的寄存器进行读取

RREG\_BK1 用来读地址 32 到 63 的寄存器,RREG\_BK1 的格式如下,第一个字节表示寄存器的起始地址为 rrrrr+32,第二个字节的  $n_n$ nnnn 表示要读的寄存器数目减一(可配从 0 到 31),只有当起始地址为 63 即 rrrrr 等于 31 时才需要输入第三个字节的码字 72h:

1st byte----101r rrrr 2nd byte---000n nnnn 3rd byte---72h

当起始地址在 32 到 62 之间,时序图和图 26 相同。当起始地址为 63 时,时序图需要在第 17 个周期到第 24 个周期给 DIN 输入第三个字节 72h,而后从第 25 个周期再开始从 DOUT 输出寄存器的值。

WREG\_BK1: 对地址 32 到 63 的寄存器进行写入

WREG\_BK1 用来写地址 32 到 63 的寄存器,WREG\_BK1 的格式如下,第一个字节表示寄存器的起始地址为 rrrrr+32,第二个字节的 n\_nnnn 表示要写的寄存器数目减一(可配从 0 到 31),只有当起始地址为 63 即 rrrrr 等于 31 时才需要输入第三个字节的码字 72h:

1st byte----110r rrrr 2nd byte---000n nnnn 3rd byte---72h

当起始地址在 32 到 62 之间,时序图和图 27 相同。当起始地址为 63 时,时序图需要在第 17 个周期到第 24 个周期给 DIN 输入第三个字节 72h,而后从第 25 个周期再开始给 DIN 输入要写入的寄存器值。

#### (11) 对地址大于 63 的寄存器进行读写的方法

如果需要访问地址为 64~127 的寄存器,这个地址范围的寄存器必须用地址为 63 的寄存器 bit0 来进行地址总 线 的 扩 充 , 所 以 必 须 先 用 WREG\_BK1 命 令 来 给 地 址 63 的 bit0 写 1 ,以 后 如 果 执 行 WREG/RREG/WREG\_BK1/WREG\_BK1 命令,读写地址都是和地址 63 的 bit0 拼接的,地址 63 的 bit0 相当于地址的 bit6,即最终 WREG/RREG 的读写地址为[bit0,0rrrr],最终 WREG\_BK1/RREG\_BK1 的读写地址为[bit0,1rrrrr]。这样后续的寄存器读写访问都是在地址 63 以后。想读地址 63 去查看扩展地址的具体值,就用 RREG\_BK1 命令,推荐固定 nnnnn 为 1,相当于只读地址 63。如要再次改写地址 63 的 bit0 为 0,就用 WREG\_BK1 再次写地址 63 为 0,这样以后的寄存器读写就是在地址 0 到 63 之间。

#### (12) RST\_FIFO:复位 FIFO

该命令用来在 FIFO 被使能时复位 FIFO 的读写指针以及内容。具体参考 FIFO 模式 部分.

#### (13) 编程步骤举例

- 1) 保持 START 引脚是拉低的状态

- 2) 如果使用外部时钟, 保持 CLKSEL=0 并从管脚 CLK 输入外部 2.048M 时钟; 如果使用内部晶振则保持

CLKSEL=1

- 3) 等待 2.5mS 使得上电过程完成, 上电过程中保持 PDEXTRST 引脚为 1.

- 4) 发送 RESET 命令或者 toggle PDEXTRST 引脚复位器件, 等待 10μS 使得复位过程完成

cmd\_drv(INSTR\_RESET, 0, data\_array);

5) 发送 SRATAC 命令退出 RDATAC 状态

cmd\_drv(INSTR\_SDATAC, 0, data\_array);

6) 根据应用需求配置时钟、系统、ADC、PGA 等相关寄存器,例如:

write\_reg(ADDR\_CLKCON, 7);

write\_reg(ADDR\_SPI\_CTRL, 1);

write\_reg(ADDR\_ADCCTRL, 'h3);

write\_reg(ADDR\_PGAGAIN, 'h1);

write\_reg(ADDR\_PGACTRL, 'h8);

7) 发送 START 命令或者拉高 START 引脚, ADC 采样开始转换

set\_digout(PIN\_START, 1, 1); 或者 cmd\_drv(INSTR\_START, 0, data\_array);

8) 发送 RDATAC 命令进入连续读取数据模式

cmd\_drv(INSTR\_RDATAC, 0, data\_array);

9) 每等待一次 DRDYn 变低电平,可使用 SCLK 的下降沿捕获一个 ADC 采样和状态字

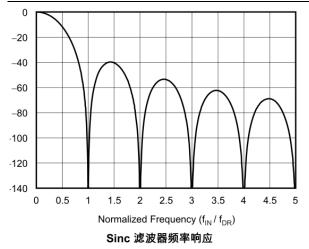

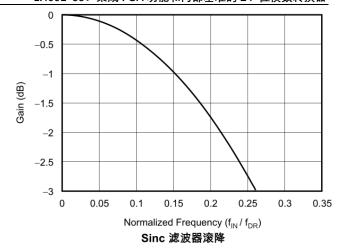

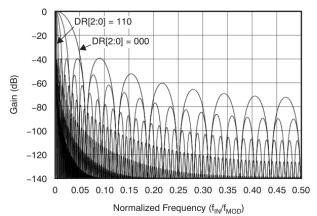

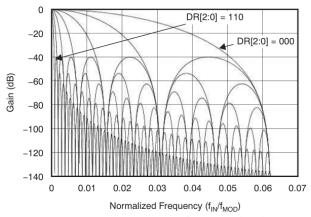

#### 9.3. SINC3

3 阶 SINC 滤波器,可变抽取率三阶低通滤波器:

$$|H(z)| = \left| \frac{1 - Z^{-N}}{1 - Z^{-1}} \right|^{3}$$

作用:

调制器的高频噪声衰减,然后将数据流抽取为并行数据。

SINC 的输入数据以 MODCLK(参考时钟架构) 的频率 (参考 MODCLK.CD) 更新。

滤波器的抽取率由 CONFIG1.DR 定义。

通过调整滤波器抽取率,可以在分辨率和数据速率之间进行折衷:

增大滤波抽取率,可实现更高的分辨率;

减小滤波过采样可实现更高的数据速率;

抽取率会影响转换器的整体数据速率,参考抽取系数 CONFIG1.DR 获得详细信息。

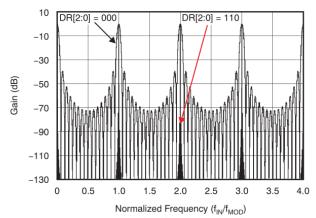

## 滤波器频率响应:

f<sub>MOD</sub>/2 下片上抽取滤波器的传递函数

f<sub>MOD</sub>/16 下片上抽取滤波器的传递函数

4 × f<sub>MOD</sub> 下片上抽取滤波器的传递函数 (DR[2:0] = 000 且 DR[2:0] = 110)

图28. 频率响应图

$F_{DR} = f_{MODCLK}/OSR$

# fin 是输入信号的频率

Sinc 滤波器具有以输出数据速率倍数出现的陷波(或零点)。在这些频率下,滤波器具有无限衰减。 输入端出现阶跃变化时,滤波器需要 3 \*MODCLK\*OSR 个转换周期才能稳定,tsettle = 3 \*MODCLK\*OSR。 在 START 引脚的上升沿或 START 命令完成后,滤波器需要多个 tsettle 周期来提供第一个数据输出,滤波器在各种数据速率下的建立时间见 SPI 部分。

#### 9.4. 中断

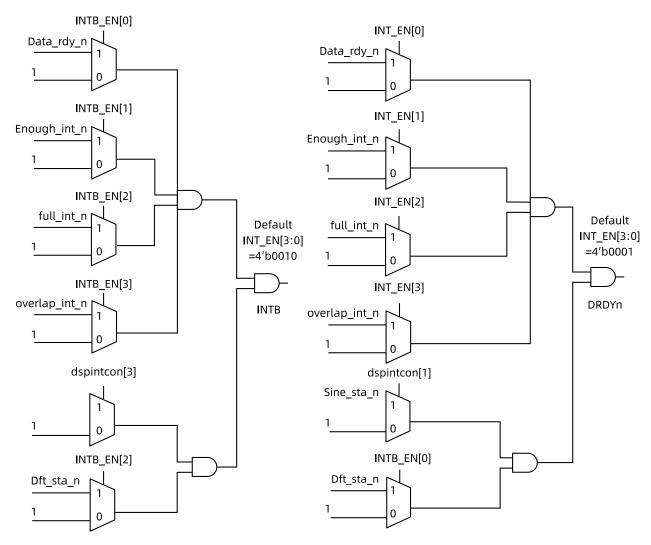

芯片内部共有5个中断源:

data\_rdy\_n: 表示 adc 每成功转换完一次数据就拉低一次,拉低之后遇到第一个 sclk 下降沿就立刻拉高,详细信息见数据就绪引脚 (DRDYn) 部分

enough\_int\_n, full\_int\_n, overflow\_int\_n: 只有在 FIFO 模式下才会使用, 详细信息参考 FIFO 模式部分。

5个中断源可以通过中断使能寄存器引出到两个中断引脚 DRDYn 和 INTB 输出具体如下图所示。

DRDYn 使用寄存器 INTB\_EN 的 bit3~0 来配置,INTB 使用寄存器 INTB\_EN 的 bit7~4 来配。

图29. 中断结构图

#### 9.4.1. 寄存器列表

INT\_OEN\_REG(用户可访问,无需输入 key)中断输出使能寄存器

偏移地址: 8'h18 复位值: 8'h21

表14. 中断使能

| Bit 位 | 名称       | r/w | 说明                           |

|-------|----------|-----|------------------------------|

| 7     | INTB_EN3 | RW  | INTB 管脚的 Overflow_int_n 中断使能 |

| 6     | INTB_EN2 | RW  | INTB 管脚的 full_int_n 中断使能     |

| 5     | INTB_EN1 | RW  | INTB 管脚的 enough_int_n 中断使能   |

| 4     | INTB_EN0 | RW  | INTB 管脚的 data_rdy_n 中断使能     |

| 3     | INT_EN3  | RW  | INT 管脚的 Overflow_int_n 中断使能  |

| 2     | INT_EN2  | RW  | INT 管脚的 full_int_n 中断使能      |

| 1 | INT_EN1 | RW | INT 管脚的 enough_int_n 中断使能 |

|---|---------|----|---------------------------|

| 0 | INT_EN0 | RW | INT 管脚的 data_rdy_n 中断使能   |

每个中断的状态也可以通过寄存器 FIFO\_STA\_REG 读出,具体见下表。

FIFO STA REG(用户可访问,无需输入 key) Fifo 状态寄存器

偏移地址: 8'h19 复位值: 8'hF

#### 表15. 中断标记

| Bit 位 | 名称                   | r/w | 说明                                                           |

|-------|----------------------|-----|--------------------------------------------------------------|

| 7     | Overflow_int_flag    | RO  | Fifo 溢出中断标记                                                  |

| 6     | Full_int_flag        | RO  | Fifo 满中断标记                                                   |

| 5     | Enough_int_flag      | RO  | Fifo 有足够的数中断标记                                               |

| 4:0   | Enough_Int_threshold | RW  | 当 fifo 未读的数据达到数目 Enough_Int_threshold+1 时就产生 Enough_int_flag |

#### 9.5. FIFO

如果寄存器位 FIFO\_SEL=1 则自动使用连续转换模式(SINGLE\_SHOT 被硬件强制置为 0),且 ADC 数据先要进入深度为 32 的异步 FIFO 缓存起来。当 DRDYn 每拉低一次就向 FIFO 写入一个 ADC 数据,当 FIFO 中未读的数据数目到达预先设定的值 (由寄存器位 Enough\_Int\_threshold 设置,可设置为 1~32) 时可产生 enough\_int\_n 的低电平中断。SPI 就可以通过 RDATA 或者 RDATAC 命令来读取数据,若 FIFO 写满了则会产生一个 full\_int\_n 的低电平中断,写满后如果继续写则会产生一个 overflow int n 的低电平中断。中断清除的条件如下表:

#### 表16. FIFO 中断清除的方法

| 中断名            | 清除方法                                                         |

|----------------|--------------------------------------------------------------|

| enough_int_n   | 读 FIFO 只要未读数据的数目小于设定值就自动清除。或者发送 RST_FIFO 命令,或者将 START 管脚拉低再拉 |

|                | 高,或者先发送 STOP 命令再发送 START 命令                                  |

| full_int_n     | 发送 RST_FIFO 命令,或者将 START 管脚拉低再拉高,或者先发送 STOP 命令再发送 START 命令   |

| overflow_int_n | 发送 RST_FIFO 命令,或者将 START 管脚拉低再拉高,或者先发送 STOP 命令再发送 START 命令   |

RST\_FIFO 命令只复位 FIFO, 而 START 管脚跳变或者 START/STOP 命令不仅复位 FIFO 还会复位数字滤波器。 所以 RST\_FIFO 命令能更快地使 FIFO 从异常情况恢复,在使用单器件或者单通道时比较适用。在使用多器件或者多通道情况下 FIFO 发生的异常,推荐使用 START 管脚跳变或者 START/STOP 命令重新同步多器件多通道。

FIFO 模式下数据检索的格式如下,和非 FIFO 模式的区别是多了 2bits 的 tail bits 域:

## 表17. FIFO 模式数据检索格式

| Bit47 |          |           |         |        | Bit0           |

|-------|----------|-----------|---------|--------|----------------|

| 1100  | RESERVED | GPIO[1:0] | 11 '0's | ADC 数据 | Tail Bits[1:0] |

#### 表18. 非 FIFO 模式数据检索格式

| Bit47 |          |           |         |        | Bit0 |

|-------|----------|-----------|---------|--------|------|

| 1100  | RESERVED | GPIO[1:0] | 13 '0's | ADC 数据 |      |

每个 adc sample 都对应 2bits 的 tail bits, tail bits 反映了当前 FIFO 的状态。对应关系如下表所示。

#### 表19. tail bits 说明

| 2'b00 | 正常数据                    |

|-------|-------------------------|

| 2'b01 | 当前读出的数据是 FIFO 的最后一个正常数据 |

| 2'b10 | FIFO 读空,当前读出的数据无效  |

|-------|--------------------|

| 2'b11 | FIFO 写满,adc 采样数据丢失 |

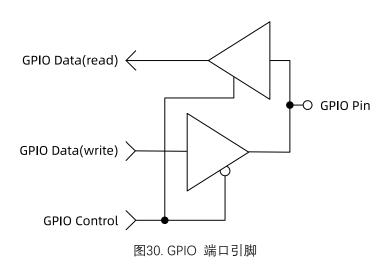

#### 9.6. GPIO

LH001-55 在正常工作时总共有 2 个通用数字输入/输出 (GPIO) 引脚。数字 I/O 引脚可通过 GPIO 寄存器的 GPIOC 位单独配置为输入、输出、上拉或下拉。GPIO 寄存器中的 GPIOD 位控制引脚的电平。在读取 GPIOD 位时,返回的数据是引脚的逻辑电平,无论它们是编程为输入还是输出都是如此。当 GPIO 引脚配置为输入时,对相应 GPIOD 位的写入无效。当配置为输出时,对 GPIOD 位的写入会设置输出值。

如果配置为输入,如果没有设置为上拉或者下拉则必须驱动这些引脚;请勿将这些引脚悬空。在上电或复位之后,GPIO 引脚会设置为输入。下图显示了 GPIO 端口结构。如果未使用这些引脚,则将其与 DGND 短接。

#### 9.6.1. 结构图

#### 9.6.2. Power down 模式

参考 PLTFMPD, 当 PLTFMPD.ALL 为 1 时, 芯片进入低功耗模式, 待机功耗 0.2μA。

# 10. 寄存器描述

CHIPID 寄存器

Address: 0x40,复位值: 0x12

## 表20.

| 位   | 名称 | 描述   | 读/写 |

|-----|----|------|-----|

| 5:0 | ID | 芯片ID | 只读  |

CONFIG1 寄存器

Address: 0x01,复位值: 0x36, 配置数据输出速率

## 表21.

| 位   | 名称          | 描述                                                   | 读/写 |

|-----|-------------|------------------------------------------------------|-----|

| 2:0 | RESERVED    |                                                      | 读写  |

| 3   | SINGLE_SHOT | ADC 转换模式                                             | 读写  |

|     |             | _                                                    |     |

|     |             | 0: 连续转换。停止条件:SPI Stop 命令或者CS为高                       |     |

|     |             | 1: 单次转换。转换完成即停止                                      |     |

| 7:4 | AVG         | 将 SINC3 滤波器的输出做平均,只有当 MODCFG.MD=0 时有效,SINC3 本身的过采样率为 | 读写  |

|     |             | Fmodclk/17,参考 DR 位                                   |     |

|     |             | 0: 输出数据速率=30K SPS                                    |     |

|     |             | 1: 输出数据速率=15K SPS                                    |     |

|     |             | 2: 输出数据速率=7.5K SPS                                   |     |

|     |             | 3: 输出数据速率=3.75K SPS                                  |     |

|     |             | 4: 输出数据速率=2K SPS                                     |     |

|     |             | 5: 输出数据速率=1K SPS                                     |     |

|     |             | 6: 输出数据速率=500 SPS                                    |     |

|     |             | 7: 输出数据速率=100 SPS                                    |     |

|     |             | 8: 输出数据速率=60 SPS                                     |     |

| Ì   |             | 9: 输出数据速率=50 SPS                                     |     |

|     |             | A: 输出数据速率=30 SPS                                     |     |

|     |             | B: 输出数据速率=25 SPS                                     |     |

|     |             | C: 输出数据速率=15 SPS                                     |     |

|     |             | D: 输出数据速率=10 SPS                                     |     |

|     |             | E: 输出数据速率=5 SPS                                      |     |

|     |             | F: 输出数据速率=2.5 SPS                                    |     |

|     |             | 注:该输出速率的计算条件:TBC                                     |     |

IEXECON 寄存器

Address: 0x08,复位值: 0x0, 激励电流源控制寄存器

#### 表22.

| 位 | 名称       | 描述               | 读/写 |

|---|----------|------------------|-----|

| 0 | EN       | 激励电流源使能控制        | 读写  |

|   |          | 0: 关闭            |     |

|   |          | 1: 使能            |     |

| 1 | SEL_AIN4 | AIN4 的激励电流源连接    |     |

|   |          | 0: 不连接           |     |

|   |          | 1: 激励电流源连接至 AIN4 |     |

| 2 | SEL_AIN5 | AIN5 的激励电流源连接    |  |

|---|----------|------------------|--|

|   |          | 0: 不连接           |  |

|   |          | 1: 激励电流源连接至 AIN5 |  |

| 3 | EN_100N  | 100nA 激励电流源使能    |  |

|   |          | 0: 不使能 100nA 电流源 |  |

|   |          | 1: 使能 100nA 电流源  |  |

# IEXEMAG 寄存器

Address: 0x09,复位值: 0x0, 激励电流源幅度控制寄存器

# 表23.

| 位   | 名称    | 描述                                                | 读/写 |

|-----|-------|---------------------------------------------------|-----|

| 2:0 | MAG_A | AIN4 的激励电流源幅度                                     | 读写  |

|     |       | 0: 当 EN_100NA 为 0 时输出 0,当 EN_100NA 为 1 时输出 100nA. |     |

|     |       | 1: 50uA                                           |     |

|     |       | 2: 100uA                                          |     |

|     |       | 3: 250uA                                          |     |

|     |       | 4: 500uA                                          |     |

|     |       | 5: 750uA                                          |     |

|     |       | 6: 1mA                                            |     |

|     |       |                                                   |     |

| 5:3 | MAG_B | AIN5 的激励电流源幅度                                     | 读写  |

|     |       | 0: 当 EN_100NA 为 0 时输出 0,当 EN_100NA 为 1 时输出 100nA. |     |

|     |       | 1: 50uA                                           |     |

|     |       | 2: 100uA                                          |     |

|     |       | 3: 250uA                                          |     |

|     |       | 4: 500uA                                          |     |

|     |       | 5: 750uA                                          |     |

|     |       | 6: 1mA                                            |     |

|     |       |                                                   |     |

# BUFCON 寄存器

Address: 0x0A,复位值: 0x11, 内部 Buffer 控制寄存器

# 表24.

| 位 | 名称          | 描述                                | 读/写 |

|---|-------------|-----------------------------------|-----|

| 0 | ENB_TEMP    | 温度传感器控制                           | 读写  |

|   |             | 0: 使能                             |     |

|   |             | 1: 关闭                             |     |

| 1 | 保留          | 保留                                |     |

| 2 | EN_HALFAVDD | AVDD/2 Buffer                     |     |

|   |             | 0: 关闭                             |     |

|   |             | 1: 使能                             |     |

| 3 | 保留          | 保留                                |     |

| 4 | EN_REFBUF   | ADC 参考 Buffer                     |     |

|   |             | 0: 关闭 ADC 参考 Buffer               |     |

|   |             | 1: 使能 ADC 参考 Buffer               |     |

| 5 | EN_2P5MOD   | ADC 参考选择                          |     |

|   |             | 0: 2V 内部参考源,AVDD 低于 2.7V 时只能使用该选项 |     |

|   |             | 1: 2.5V 内部参考源                     |     |

ADCCHCON 寄存器

Address: 0x0B,复位值: 0x10, ADC 通道选择寄存器

表25.

| 位    | 名称   | 描述                                 | 读/写 |

|------|------|------------------------------------|-----|

| 3:0  | PSEL | ADC 正输入通道选择                        | 读写  |

|      |      | 0x0: AIN0                          |     |

|      |      | 0x1: AIN1                          |     |

|      |      | 0x2: AIN2                          |     |

|      |      | 0x3: AIN3                          |     |

|      |      | 0x4: AIN4                          |     |

|      |      | 0x5: AIN5                          |     |

|      |      | 0x6: AIN6                          |     |

|      |      | 0x7: AIN7                          |     |

|      |      | 0x8: AINCOM                        |     |

|      |      | 0x9: DVDD/2, NSEL 设为 0xF           |     |

|      |      | 0xA: AVDD/2, NSEL 设为 0xF           |     |

|      |      | 0xB: VCM, 正负输入短路到 VCM, NSEL 设为 0xF |     |

|      |      | 0xC: 片内温度传感器, NSEL 设为 0xF          |     |

|      |      | 0xD: 测试信号,NSEL 设为 0xF              |     |

| 7: 4 | NSEL | ADC 负输入通道选择                        |     |

|      |      | 0x0: AIN0                          |     |

|      |      | 0x1: AIN1                          |     |

|      |      | 0x2: AIN2                          |     |

|      |      | 0x3: AIN3                          |     |

|      |      | 0x4: AIN4                          |     |

|      |      | 0x5: AIN5                          |     |

|      |      | 0x6: AIN6                          |     |

|      |      | 0x7: AIN7                          |     |

|      |      | 0x8: AIN8                          |     |

ADCCTRL 寄存器

Address: 0x0C,复位值: 0x0, ADC 控制寄存器

表26.

| 位 | 名称          | 描述           | 读/写 |

|---|-------------|--------------|-----|

| 0 | MOD_PDB     | 0: 关闭 ADC    | 读写  |

|   |             | 1: 使能 ADC    |     |

| 1 | MOD_PDB_AMP | 0: 关闭 ADC 运放 |     |

|   |             | 1: 使能 ADC 运放 |     |

PGAGAIN 寄存器

Address: 0x0D,复位值: 0x0, PGA 增益选择寄存器

表27.

| - |   |    |    |     |

|---|---|----|----|-----|

|   | 位 | 名称 | 描述 | 读/写 |

## LH001-55: 集成 PGA 功能和内部基准的 24-位模数转换器

| 5:0 | GAIN | PGA 增益选项 | 读写 |