# 802.3af/at Power over Ethernet PoE Powered Device (PD) Controller

#### **Features**

- Meets IEEE 802.3af/at Specifications

- Support 25W PoE Power Application

- 100V, 0.48Ω Integrated Pass Switch

- 180mA Inrush Current Limit

- Current Limit During Normal Operation

Between 720mA and 920mA

- Simplified Wall Adapter Interface

- Open Drain Type-2 PSE Indicator

- Current Limit and Fold-back

- Self-Driving Power Good Indicator

- Over Temperature Protection (OTP)

- DFN3x3-10 Package

## **Application**

- VoIP Telephones

- Security Camera Systems

- Remote Internet Power

- Safety Backup Power

### **Description**

The TMI7303B provides a complete interface for a Powered Device (PD) with the IEEE 802.3af/at standard in PoE system. The TMI7303B include detection signature, classification signature and an integrated isolation power switch with inrush current control mode. It supports a 2-event classification method as specified provide a signal to indicate when probed by Type 2 power-sourcing equipment (PSE). The devices detect the presence of a wall adapter power-source connection and allow a smooth switchover from the PoE power source to the wall adapter. Thermal protection is built in to accommodate both transient and/or overload conditions, shutting the part down and protecting the input source as well as the output load depending on the particular fault conditions. Inrush current limiting is included to slowly charge the input capacitor without interruption due to die heating, a problem encountered without the current limit fold back feature.

The TMI7303B is available in a DFN3x3-10 package with exposed pad for low thermal resistance.

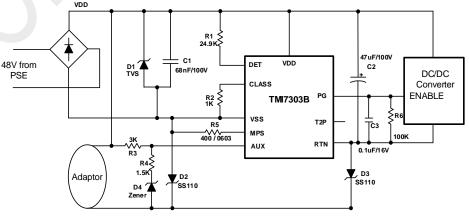

# **Typical Application**

Figure 1. TMI7303B Typical Application Circuit

# Absolute Maximum Ratings (Note 1)

| Items                                                         | Min  | Max | Unit |

|---------------------------------------------------------------|------|-----|------|

| VDD, RTN, DET, T2P, AUX to VSS                                | -0.3 | 100 | V    |

| CLASS, MPS to VSS                                             | -0.3 | 5.5 | V    |

| PG to RTN                                                     | -0.3 | 5.5 | V    |

| T2P sink current                                              |      | 10  | mA   |

| Continuous Power Dissipation (T <sub>A</sub> = +25°C) (Note2) |      | 2.5 | W    |

| Junction Temperature                                          | -40  | 150 | °C   |

| Lead Temperature                                              |      | 260 | °C   |

| Storage Temperature                                           | -50  | 150 | °C   |

## **Recommended Operating Conditions** (Note 3)

| Items                   | Min | Max | Unit |

|-------------------------|-----|-----|------|

| Supply Voltage VDD      | 0   | 57  | V    |

| Maximum T2P Current     |     | 5   | mA   |

| Operating Junction Temp | -40 | 125 | °C   |

#### **Thermal Resistance**

| Items         | Description                              | Value | Unit |

|---------------|------------------------------------------|-------|------|

| $\theta_{JA}$ | Junction-to-ambient thermal resistance   | 50    | °C/W |

| $\theta_{JC}$ | Junction-to-case(top) thermal resistance | 12    | °C/W |

## **ESD Ratings**

| Items                  | Description                                                                         | Value | Unit |

|------------------------|-------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD-HBM)</sub> | Human Body Model (HBM) ANSI/ESDA/JEDEC JS-001-2017 Classification, Class: 2         | ±2000 | V    |

| V <sub>(ESD-CDM)</sub> | Charged Device Mode (CDM) ANSI/ESDA/JEDEC JS-<br>002-2018 Classification, Class: C3 | ±1000 | V    |

| ILATCH-UP              | JEDEC STANDARD NO.78E APRIL 2016 Temperature Classification, Class: I               | ±200  | mA   |

Note 1: Exceeding these ratings may damage the device.

Note 2: The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_{D(MAX)}=(T_{J (MAX)}-T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

Note 3: The device is not guaranteed to function outside of its operating conditions.

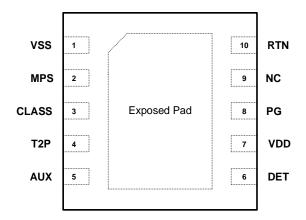

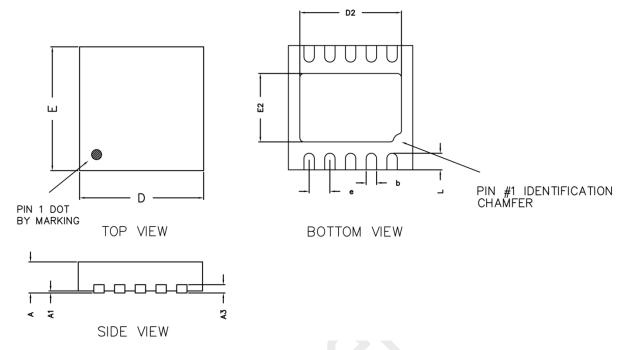

# **Package**

DFN3x3-10

Top Marking: T7303B/XXXXX (T7303B: Device Code, XXXXX: Inside Code)

## **Order Information**

| Part Number | Package   | Top Marking     | Quantity/ Reel |

|-------------|-----------|-----------------|----------------|

| TMI7303B    | DFN3x3-10 | T7303B<br>XXXXX | 5000           |

TMI7303B devices are Pb-free and RoHS compliant.

# **Pin Functions**

| Pin | Name           | Function                                                                                                                                                                                                                                                                  |

|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VSS            | Negative Power Supply Terminal from PoE input power rail.                                                                                                                                                                                                                 |

| 2   | MPS            | Open drain output. work as MPS switch to generate current pulses by connecting a resistor between MPS and VSS. The high level of MPS pulse is 5V.                                                                                                                         |

| 3   | CLASS          | Connect resistor from CLASS to VSS to program classification current.                                                                                                                                                                                                     |

| 4   | T2P            | Type 2 PSE indicator, open-drain output. Pull low to VSS indicates the presence of a Type 2 PSE or AUX is enabled.                                                                                                                                                        |

| 5   | AUX            | Auxiliary power input detector. Use this pin for adaptor power supply application. Drive VDD-AUX higher than 2.3V to disable hot-swap MOSFET and CLASS pin function, and force T2P and PG active.                                                                         |

| 6   | DET            | Detection Resistor. Connect a 24.9k $\Omega$ Detection Resistor from DET to VDD.                                                                                                                                                                                          |

| 7   | VDD            | Positive Power Supply.                                                                                                                                                                                                                                                    |

| 8   | PG             | PD supply power good indicator. This signal will enable the DCDC converter. It is pulled up by internal current source in output high condition, Connect PG to RTN through a resistor.                                                                                    |

| 9   | NC             | Not connected internally.                                                                                                                                                                                                                                                 |

| 10  | RTN            | Drain of Isolation MOSFET. RTN connects to the drain of the integrated isolation n-channel power MOSFET. Connect RTN to the downstream DC/DC converter ground as shown in the Typical Application Circuit.                                                                |

| 11  | Exposed<br>Pad | Exposed Pad. Do not use exposed pad as an electrical connection to VSS. Exposed pad is internally connected to VSS through a resistive path and must be connected to VSS externally. To optimize power dissipation, solder the exposed pad to a large copper power plane. |

## **Electrical Characteristics**

$V_{DD}$ - $V_{SS}$ =48V, all voltages with respect to  $V_{SS}$ ,  $R_{DET}$ =24.9 $k\Omega$ ,  $R_{CLASS}$ =1000 $\Omega$ ,  $T_{A}$ =25 °C, unless otherwise noted.

| Parameter                               | Symbol                  | Conditions                                                                             | Min  | Тур  | Max  | Units |  |

|-----------------------------------------|-------------------------|----------------------------------------------------------------------------------------|------|------|------|-------|--|

| Detection                               |                         |                                                                                        |      |      |      |       |  |

| Detection on                            | V <sub>DET_ON</sub>     | VDD Rising                                                                             |      | 1.4  |      | V     |  |

| Detection off                           | V <sub>DET_OFF</sub>    | VDD Rising                                                                             |      | 12   |      | V     |  |

| DET Leakage Current                     | V <sub>DET_LK</sub>     | V <sub>DET</sub> =V <sub>VDD</sub> =57V, Measure I <sub>DET</sub>                      |      | 0.1  | 5    | μA    |  |

| Bias Current                            |                         | V <sub>VDD</sub> =10.1V, float DET pin, not in Mark event, Measure I <sub>SUPPLY</sub> |      |      | 12   | μA    |  |

| Data ation Commant                      |                         | V <sub>VDD</sub> =2.5V, Measure I <sub>SUPPLY</sub>                                    | 96   | 99   | 102  | μΑ    |  |

| Detection Current                       | I <sub>DET</sub>        | V <sub>VDD</sub> =10.1V, Measure I <sub>SUPPLY</sub>                                   | 395  | 410  | 425  | μA    |  |

| Classification                          |                         |                                                                                        |      |      | l    |       |  |

| Classification Stability<br>Time        |                         |                                                                                        |      | 120  |      | μs    |  |

| VCLASS Output Voltage                   | V <sub>CLASS</sub>      | 13V <v<sub>VDD&lt;21V,1mA<i<sub>CLASS&lt;42mA</i<sub></v<sub>                          | 1.12 | 1.18 | 1.24 | V     |  |

|                                         |                         | 13≤V <sub>VDD</sub> ≤21V, Guaranteed by V <sub>CLASS</sub>                             |      |      |      |       |  |

| Classification Current                  | I <sub>CLASS</sub>      | R <sub>CLASS</sub> =1000Ω, 13≤VDD≤21V                                                  | 1    | 1.2  | 2.8  |       |  |

|                                         |                         | R <sub>CLASS</sub> =113Ω, 13≤VDD≤21V                                                   | 10.3 | 10.5 | 11.3 | mA    |  |

|                                         |                         | R <sub>CLASS</sub> =64.9Ω, 13≤VDD≤21V                                                  | 17.7 | 18.2 | 19.5 |       |  |

|                                         |                         | R <sub>CLASS</sub> =42.2Ω, 13≤VDD≤21V                                                  | 27.1 | 28   | 29.5 |       |  |

|                                         |                         | R <sub>CLASS</sub> =30Ω, 13≤VDD≤21V                                                    | 36.4 | 39.4 | 43.6 |       |  |

| Classification Lower<br>Threshold       | V <sub>CL_ON</sub>      | Class Regulator Turns on, VDD Rising                                                   | 11   | 12   | 13   | V     |  |

| Classification Upper<br>Threshold       | V <sub>CL_OFF</sub>     | Class Regulator Turns off, VDD Rising                                                  | 21   | 22   | 23   | V     |  |

| Classification Hystorosis               | .,,                     | Low side Hysteresis                                                                    |      | 1    |      | \/    |  |

| Classification Hysteresis               | V <sub>CL_HYS</sub>     | High side Hysteresis                                                                   |      | 8.0  |      | V     |  |

| Mark Event Rest<br>Threshold            | V <sub>MARK-L</sub>     |                                                                                        | 2.8  | 4    | 5.2  | V     |  |

| Max Mark Event Voltage                  | V <sub>MARK-H</sub>     |                                                                                        | 10.1 | 11   | 12   | V     |  |

| Mark Event Current                      | I <sub>MARK</sub>       |                                                                                        | 0.25 |      | 0.85 | mA    |  |

| IC Supply Current during Classification | I <sub>IN_CLASS</sub>   | V <sub>VDD</sub> =17.5V, CLASS Floating                                                |      | 200  | 300  | μA    |  |

| PD UVLO                                 |                         |                                                                                        |      |      |      |       |  |

| VDD Turn on Threshold                   | $V_{DD\_VSS\_R}$        | VDD Rising                                                                             | 36   | 37.8 | 39.6 | V     |  |

| VDD Turn off Threshold                  | V <sub>DD_VSS_F</sub>   | VDD Falling                                                                            | 30   | 31   | 32   | V     |  |

| VDD UVLO Hysteresis                     | V <sub>DD_VSS_HYS</sub> |                                                                                        |      | 7.6  |      | V     |  |

| IC Supply Current during<br>Operation   | I <sub>IN</sub>         |                                                                                        |      | 300  | 450  | μΑ    |  |

www.toll-semi.com

TMI7303B V1.2 2024.01 5

## **Electrical Characteristics**

$V_{DD}$ - $V_{SS}$ =48V, all voltages with respect to  $V_{SS}$ ,  $R_{DET}$ =24.9 $k\Omega$ ,  $R_{CLASS}$ =1000 $\Omega$ ,  $T_{A}$ =25 °C, unless otherwise noted.

| uniess otherwise note                     |                       |                                                                        |       |      |       |    |

|-------------------------------------------|-----------------------|------------------------------------------------------------------------|-------|------|-------|----|

| Pass Device and Current                   | Limit                 |                                                                        |       |      |       |    |

| On Resistance                             | R <sub>DS(ON)</sub>   | I <sub>RTN</sub> =600mA                                                |       | 0.48 |       | Ω  |

| Leakage Current                           | $I_{RTN\_LK}$         | V <sub>VDD</sub> =V <sub>RTN</sub> =57V                                |       | 1    | 15    | μΑ |

| Current Limit                             | I <sub>LIMIT</sub>    | V <sub>RTN</sub> =1V                                                   | 720   | 840  | 920   | mA |

| Inrush Limit                              | I <sub>INRUSH</sub>   | V <sub>RTN</sub> =2V                                                   |       | 180  |       | mA |

| Inrush Termination<br>Current             |                       | IRTN Falling Percentage of inrush current                              |       | 88%  |       |    |

| Inrush to Operation Mode<br>Delay         | , idelay              |                                                                        | 80    | 96   |       | ms |

| Current Fold-back Fhreshold  VRTN Rising  |                       |                                                                        | 12    |      | V     |    |

| MPS                                       |                       |                                                                        |       |      |       |    |

| Intelligent MPS falling                   | I <sub>MPS_TH</sub>   | Startup has completed, IRTN falling threshold to generate MPS pulses   |       | 22   |       | mA |

| current threshold                         | $I_{\text{MPS\_HYS}}$ | Hysteresis on RTN current                                              |       | 3    |       | mA |

| The high level of MPS pulse               | $V_{\text{MPS}}$      | Irtn <imsth< td=""><td>4</td><td>4.5</td><td>5</td><td>٧</td></imsth<> | 4     | 4.5  | 5     | ٧  |

|                                           |                       | MPS pulsed current ON time                                             | 75    | 80   | 85    | ms |

| MPS pulsed mode duty cycle                |                       | MPS pulsed current OFF time                                            | 225   | 240  | 255   | ms |

| - Sydio                                   |                       | MPS pulsed current duty cycle                                          | 24.7% | 25%  | 25.3% |    |

| T2P                                       |                       |                                                                        | -     |      |       |    |

| T2P Output Low Voltage                    |                       | I <sub>T2P</sub> =2mA, respect to VSS                                  |       | 0.1  | 0.3   | V  |

| T2P Output High<br>Leakage Current        |                       | V <sub>T2P</sub> =48V                                                  |       |      | 1     | μΑ |

| AUX                                       |                       |                                                                        |       |      |       |    |

| AUX High Threshold<br>Voltage             |                       | Respect to VDD                                                         |       | -1.5 | -2.3  | V  |

| AUX Low Threshold<br>Voltage              |                       | Respect to VDD                                                         | -0.6  | -1   |       | ٧  |

| AUX Leakage Current                       |                       | V <sub>VDD</sub> - V <sub>AUX</sub> =6V                                |       |      | 2     | μΑ |

| PG                                        |                       |                                                                        |       |      |       |    |

| Source Current<br>Capability              |                       | PG is logic high, pull PG pin to 0V                                    |       | 30   |       | μΑ |

| PG Pull Down<br>Resistance                |                       | PG is logic low, pull up PG pin to 1V                                  |       | 1000 |       | kΩ |

| PD Thermal Shutdown                       |                       |                                                                        |       |      |       |    |

| Thermal Shut down<br>Temperature (Note 1) | T <sub>PD-SD</sub>    |                                                                        |       | 150  |       | °C |

| Thermal Shut down<br>Hysteresis (Note 1)  | T <sub>PD-HYS</sub>   |                                                                        |       | 20   |       | °C |

Note 1: Guaranteed by design.

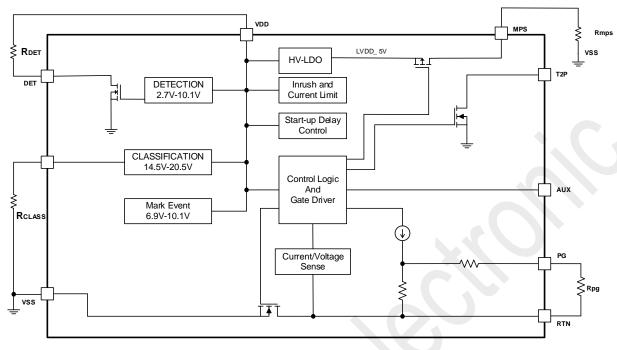

## **Block Diagram**

Figure 2 TMI7303B Block Diagram

## **Operation Description**

#### Overview

The TMI7303B provides a complete interface for a Powered Device (PD) with the IEEE 802.3af/at standard in PoE system. The TMI7303B includes detection signature, classification signature and an integrated isolation power switch with inrush current control mode. TMI7303B (along with the power sourcing element (PSE)) operates as a safety device to supply potentially lethal voltages only when the power sourcing element recognizes a unique, tightly specified resistance at the end of an unknown length of Ethernet cable. During the inrush period, the PD limit the current to less than 180mA before switching to high current limit, 720mA to 920mA, when the isolation power MOSFET is fully enhanced. The TMI7303B has an input UVLO with wide hysteresis and long deglitch time to compensate for twisted pair cable resistive drop and to assure glitch free transition during power on/off condition. The device can withstand up to 100V at the input. A PG signal pull high when the output is fully charged and pull low when the output drops under overload condition.

#### Operation

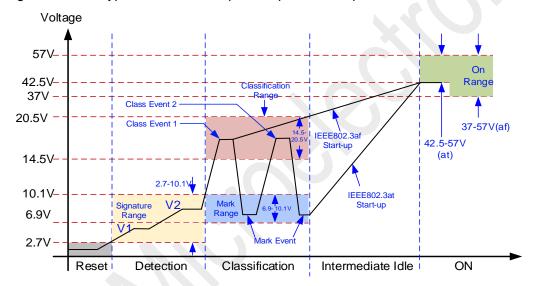

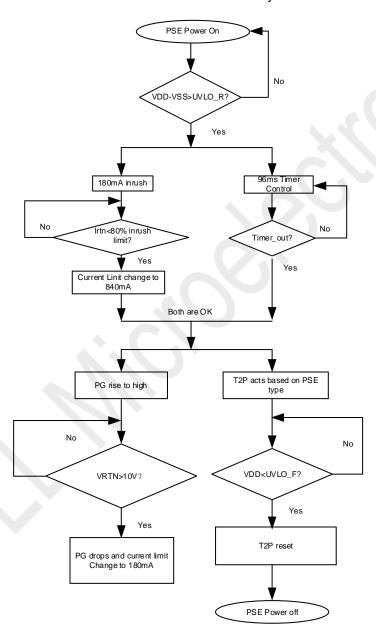

Compared with IEEE802.3af, the IEE802.3at standard establishes a higher power allocation for Power-over-Ethernet while maintaining backwards compatibility with the existing IEEE802.3af systems. Power Sourcing Equipment (PSE) and Powered Devices (PD) are distinguished as Type-1 complying with the IEEE 802.3af power levels, or Type-2 complying with the IEEE 802.3at power levels. IEEE802.3af/at standard establishes a method of communication between PD and PSE with detection, classification and event mark. TMI7303B provides a complete interface for a powered device (PD) to comply with IEEE 802.3af/at standard in a PoE system. Along with the PSE it operates as a safety device to supply voltage only when the power sourcing equipment recognizes a unique, tightly specified resistance at the end of an unknown length of Ethernet cable. After powered from PSE, the PD will regulate the output voltage based on application with isolated or non-isolated topology. Figure 1 shows the function diagram of this device, and Figure 3 shows typical PD interface power operation sequence.

**Figure 3 PD Interface Operation Description**

#### **Detection Mode(1.4V≤VDD≤10.1V)**

In detection mode, the PSE applies two voltages on VDD in the range of 1.4V to 10.1V (1V step minimum) and then records the current measurements at the two points. The PSE then computes  $\Delta V/\Delta I$  to ensure the presence of the 24.9k $\Omega$  signature resistor. Connect the signature resistor (RDET) from VDD to DET for proper signature detection. The TMI7303B pull DET low in detection mode. DET goes high impedance when the input voltage exceeds 12.5V. In detection mode, most of the TMI7303B internal circuitry is off and the offset current is less than 10µA.

If the voltage applied to the PD is reversed, install protection diodes at the input terminal to prevent internal damage to the TMI7303B (see the Typical Application Circuit). Since the PSE uses a slope technique ( $\Delta V/\Delta I$ ) to calculate the signature resistance, the DC offset due to the protection diodes is ubtracted and does not affect the detection process.

#### Classification Mode(12.6V≤VDD≤20V)

In the classification mode, the PSE classifies the PD based on the power consumption required by the PD. This allows the PSE to efficiently manage power distribution. Class 0 to 4 is defined as shown in Table 1. An external resistor (R<sub>CLS</sub>) connected from CLS to VSS sets the classification current. The PSE determines the class of a PD by applying a voltage at the PD input and measuring the current sourced out of the PSE. When the PSE applies a voltage between 12.1V and 20V, the TMI7303B exhibit a current characteristic with a value shown in Table 1. The PSE uses the classification current information to classify the power requirement of the PD. The classification current includes the current drawn by RCLS and the supply current of the TMI7303B so the total current drawn by the PD is within the IEEE 802.3af/at standard figures. The classification current is turned off whenever the device is in power mode.

|       | Table 1. OLAGO Resistor Gelection                          |      |      |  |  |  |  |  |  |

|-------|------------------------------------------------------------|------|------|--|--|--|--|--|--|

| Class | Class Max. Input Power to PD(W) Classification Current(mA) |      |      |  |  |  |  |  |  |

| 0     | 12.95                                                      | 2.4  | 1000 |  |  |  |  |  |  |

| 1     | 3.84                                                       | 10.6 | 113  |  |  |  |  |  |  |

| 2     | 6.49                                                       | 18.3 | 64.9 |  |  |  |  |  |  |

| 3     | 12.95                                                      | 28   | 42.2 |  |  |  |  |  |  |

| 4     | 25.5                                                       | 40   | 30   |  |  |  |  |  |  |

**Table 1. CLASS Resistor Selection**

#### 2-Event Classification and Detection

During 2-event classification, a Type 2 PSE probes PD for classification event, the PSE presents an input voltage between 12.6V and 20V, and the TMI7303B presents the programmed load  $I_{CLASS}$ . Then, the PSE drops the probing voltage below the mark event threshold of 10.1V and the devices present the mark current. This sequence is repeated one more time. When the TMI7303B is powered by a Type 2 PSE, the 2-event identification output T2P asserts low after the internal isolation n-channel MOSFET is fully turned on. T2P is turned off when VDD goes below the UVLO threshold ( $V_{OFF}$ ) and turns on when VDD goes above the UVLO threshold ( $V_{ON}$ ), unless VDD goes below  $V_{THR}$  to reset the latched output of the Type 2 PSE detection flag.

#### PD Interface UVLO and Current Limit

When PD is powered by PSE and VDD is higher than turn on threshold, the hot-swap switch will start pass a limited current I<sub>INRUSH</sub> to charge the downstream DC/DC converter's input capacitor C<sub>BULK</sub>. The startup charging current is around 180mA. Once the inrush current falls about 20% below the inrush current limit, the hot-swap current limit will change to 840mA. After the t<sub>DELAY</sub> from UVLO starting, TMI7303B will assert PG signal and go from the startup mode to the running mode if inrush period elapse, the PG signal can enable down-stream DCDC converter internally.

Figure 4: Startup Sequence

If VDD-VSS drops below falling UVLO, the hot-swap MOSFET and DC/DC converter both are disabled. If output current overloads on the internal pass MOSFET, current limit works and VRTN-VSS rises. If  $V_{RTN}$  rises above 10V the current limit reverts to the inrush value, and PG is pulled down internally to disable DCDC regulator at the same time. Figure 4 shows the current limit, PG and T2P work logic during startup from PSE power supply.

#### **Power Good Indicator (PG)**

The PG signal is driven by internal current source. After t<sub>DELAY</sub> from UVLO starting and the inrush current falls about 20% below the inrush current limit, or a wall power adapter is detected, the PG signal will be pulled high to indicate power condition and enable the downstream DCDC converter. Figure 4 shows the PG logic when powering from PSE, PG will be high if adaptor is detected.

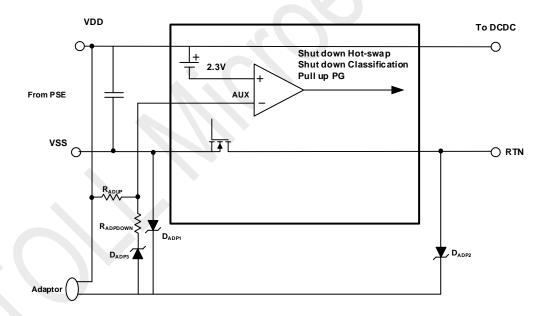

#### **Wall Power Adaptor Detection and Operation**

For applications where an auxiliary power source such as a wall adapter is used to power the device, the TMI7303B features wall power adapter detection as showing in figure 5 Once the input voltage ( $V_{DD}$ - $V_{SS}$ ) exceeds about 12.5V, the TMI7303B enables wall adapter detection. The wall power adapter detection resistor divider is connected from  $V_{DD}$  to negative terminal of adaptor, and  $D_{ADP3}$  is added for more accurate hysteresis. There is a -2.3V reference voltage from AUX to  $V_{DD}$  for adaptor detection. The adaptor is detected when AUX voltage triggers:

$$V_{DD} - V_{AUX} = (V_{ADP} - V_{DADP3}) \times \frac{R_{ADPUP}}{R_{ADPUP} + R_{ADPDOWN}} \rangle 2.3V$$

Where,  $V_{ADP}$  is adaptor voltage,  $V_{DADP3}$  is the zener voltage,  $R_{ADPUP}$  and  $R_{ADPDOWN}$  are the AUX divider resistors from adaptor power.

**Figure 5 Adaptor Power Detection**

To make TMI7303B work stable with adaptor power, one schottky diode  $D_{APD1}$  (D2 in schematic on page 1) is required between negative terminal of adaptor and VSS.  $D_{APD2}$  (D3 in schematic on page 1) is used to block reverse current between adaptor and PSE power source. When a wall adapter is detected, the internal MOSFET between RTN and  $V_{SS}$  turns off, classification current is disabled and T2P becomes active. The PG signal is active when adaptor power is detected, so that it can enable the downstream DC/DC converter even input hot-swap MOSFET is disabled.

#### **Maintain Power Signature (MPS)**

The MPS is an electrical signature presented by the PD to assure the PSE that it is still present after operating voltage is applied. For IEEE802.3af/at PD, a valid MPS consists of a minimum dc current of 10mA, or a 10mA pulsed current for at least 75ms every 325ms, and an AC impedance lower than  $26.3k\Omega$  in parallel with  $0.05\mu F$ . If the current through the RTN-to-VSS path is below ~22mA, the TMI7303B automatically generates the MPS pulsed current through the MPS output pin, the current amplitude being adjustable with an external resistor. The high level MPS pulse is 5V.

#### **Thermal Shutdown**

The TMI7303B has a temperature protection circuit. When the junction temperature exceeds 150°C the device shuts down. The device recovers with limited inrush current if the junction temperature drops below 130°C.

# **Package Information**

## DFN3x3-10

Unit: mm

| Symbol | Dimens | ions In Millin | neters | Symbol | Dimen    | sions In Milli | meters |

|--------|--------|----------------|--------|--------|----------|----------------|--------|

| Symbol | Min    | Nom            | Max    | Symbol | Min      | Nom            | Max    |

| Α      | 0.70   | 0.75           | 0.80   | b      | 0.20     | 0.25           | 0.30   |

| A1     | 0.00   | -              | 0.05   | L      | 0.30     | 0.40           | 0.50   |

| А3     |        | 0.2 REF        |        | D2     | 2.30     | 2.40           | 2.50   |

| D      | 2.95   | 3.00           | 3.05   | E2     | 1.50     | 1.65           | 1.75   |

| E      | 2.95   | 3.00           | 3.05   | е      | 0.50 BSC |                |        |

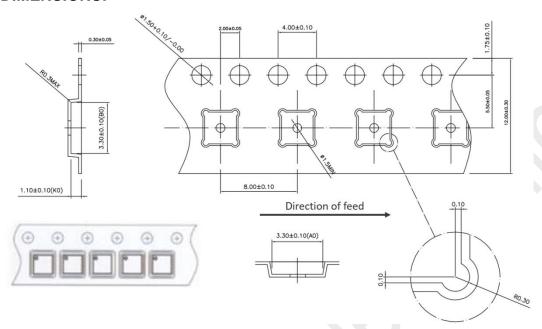

# **Tape And Reel Information**

## **TAPE DIMENSIONS:**

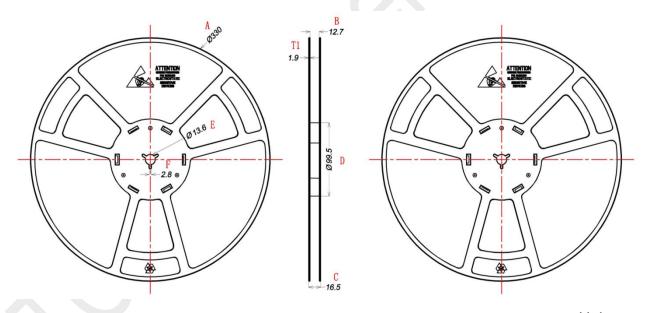

#### **REEL DIMENSIONS:**

Unit: mm

| Α       | В        | С        | D          | E          | F       | T1      |

|---------|----------|----------|------------|------------|---------|---------|

| Ø 330±1 | 12.7±0.5 | 16.5±0.3 | Ø 99.5±0.5 | Ø 13.6±0.2 | 2.8±0.2 | 1.9±0.2 |

#### Note:

- 1) All Dimensions are in Millimeter

- 2) Quantity of Units per Reel is 5000

- 3) MSL level is level 3.

# **Important Notification**

This document only provides product information. TOLL Microelectronic Inc. reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time.

TOLL Microelectronic Inc. cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a TMI product. No circuit patent licenses are implied.

All rights are reserved by TOLL Microelectronic Inc. http://www.toll-semi.com