# MQ6825/MQ6815 中文产品规格书 V1.9

No.: TDDS01-M6825 -CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

#### 目录

| 1.  | 修改i      | 修改记录10            |    |  |  |  |

|-----|----------|-------------------|----|--|--|--|

| 2.  | 产品简介14   |                   |    |  |  |  |

|     | 2.1      | 功能特性14            |    |  |  |  |

|     | 2.2      | 重点说明              | 15 |  |  |  |

|     | 2.3      | 系统模块图             | 17 |  |  |  |

|     | 2.4      | 引脚配置/说明           | 18 |  |  |  |

| 3.  | 电气特      | <b>特性</b>         | 25 |  |  |  |

|     | 3.1      | 极限参数              | 25 |  |  |  |

|     | 3.2      | 工作条件              | 26 |  |  |  |

|     | 3.3      | 直流(DC)电气特性        | 27 |  |  |  |

|     | 3.4      | AD 转换电气特性         | 29 |  |  |  |

|     | 3.5      | Flash 电气特性        | 30 |  |  |  |

|     | 3.6      | MTP 电气特性          | 31 |  |  |  |

|     | 3.7      | LCD 电气特性          | 32 |  |  |  |

|     | 3.8      | 比较器电气特性           | 33 |  |  |  |

|     | 3.9      | 上电复位特性            | 34 |  |  |  |

|     | 3.10     | LVD 电气特性          | 35 |  |  |  |

| ا.4 | 中央处:     | 理器(CPU)           | 36 |  |  |  |

|     | 4.1 概述36 |                   |    |  |  |  |

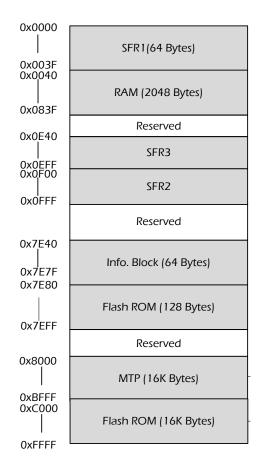

|     | 4.2      | 寻址区域              | 36 |  |  |  |

|     |          | 4.2.1 程序存储器 Flash | 37 |  |  |  |

|     |          | 4.2.2 数据存储器 RAM   | 39 |  |  |  |

|     |          | 4.2.3 特殊功能寄存器 SFR | 39 |  |  |  |

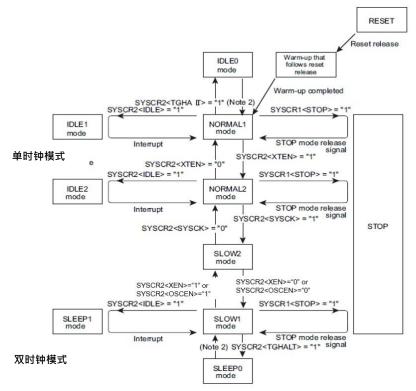

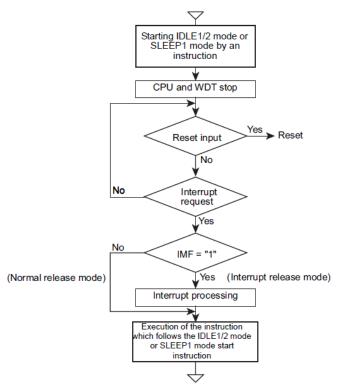

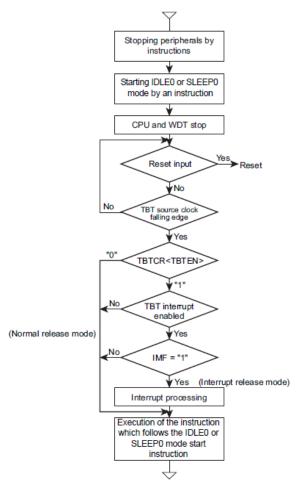

|     | 4.3      | 工作模式              | 41 |  |  |  |

|     |          | 4.3.1 工作模式控制线路    | 41 |  |  |  |

|     |          | 4.3.2 工作模式控制      | 45 |  |  |  |

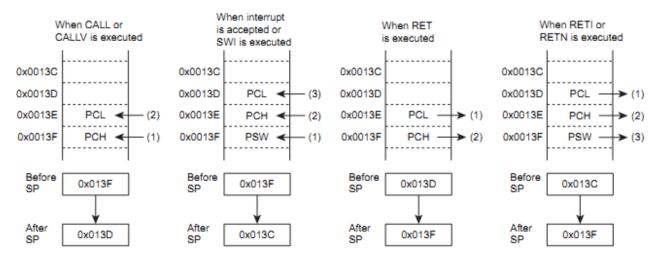

|     | 4.4      | 堆栈与堆栈指针           | 50 |  |  |  |

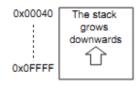

|     |          | 4.4.1 堆栈          | 50 |  |  |  |

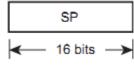

|     |          | 4.4.2 堆栈指针        | 50 |  |  |  |

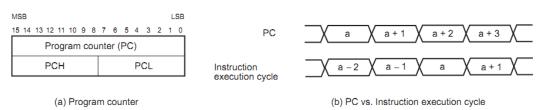

|     | 4.5      | 程序计数器             | 52 |  |  |  |

$Page: 2/359 \\ + 出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。$

#### iMQ Technology Inc.

| L | No.: TDL | DSO1-M | 6825 -CN  | Name: MQ6825/MQ6815 中文产品规格书 | Version: V1.9 |

|---|----------|--------|-----------|-----------------------------|---------------|

|   |          | 4.5.1  | 程序计数器     |                             | 52            |

|   |          |        |           | 女器数值的关系                     |               |

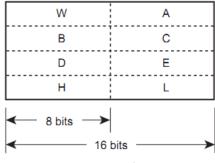

|   | 4.6      |        |           | X44X (243) (3)              |               |

|   |          |        |           |                             |               |

|   |          |        |           |                             |               |

|   |          | 4.6.3  | DE 寄存器    |                             | 54            |

|   |          | 4.6.4  | HL 寄存器    |                             | 54            |

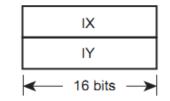

|   |          |        |           | , <sub>IY</sub>             |               |

|   | 4.7      | 程序     | <br>状态字   |                             | 55            |

|   |          | 4.7.1  | 零标帜 ZF    |                             | 56            |

|   |          | 4.7.2  | 进位标帜 CF   |                             | 56            |

|   |          | 4.7.3  | 半进位标帜 HF  |                             | 56            |

|   |          | 4.7.4  | 正负号标帜 SF  |                             | 56            |

|   |          | 4.7.5  | 溢位标帜 VF   |                             | 56            |

|   |          | 4.7.6  | 跳转状态标帜 JF |                             | 57            |

|   | 4.8      | 外围     | 线路低耗电功能   |                             | 58            |

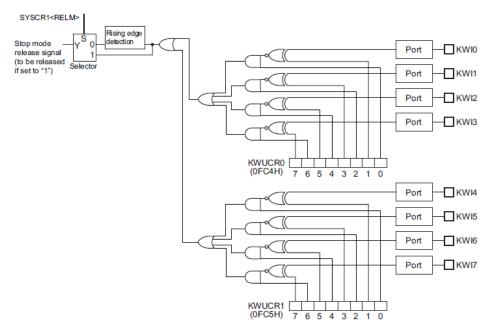

|   | 4.9      | 唤醒     | ! KWU     |                             | 61            |

|   |          | 4.9.1  | 唤醒 KWU 架构 |                             | 61            |

|   |          | 4.9.2  | 唤醒 KWU 控制 |                             | 62            |

|   |          | 4.9.3  | 唤醒 KWU 功能 |                             | 64            |

|   | 5. 复位]   | 功能     |           |                             | 66            |

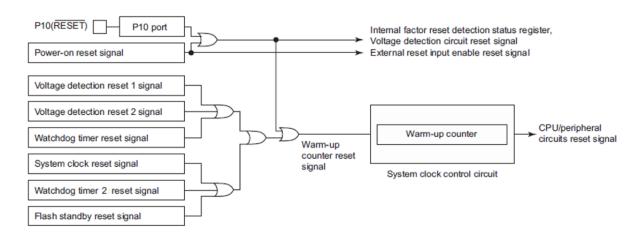

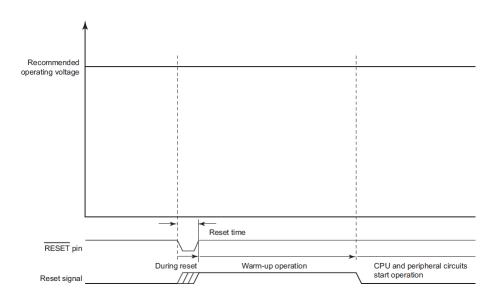

|   | 5.1      | 复位     | 控制线路      |                             | 66            |

|   |          | 5.1.1  | 复位架构      |                             | 66            |

|   |          | 5.1.2  | 复位控制      |                             | 67            |

|   |          | 5.1.3  | 复位功能      |                             | 69            |

|   |          | 5.1.4  | 复位信号产生因素  |                             | 71            |

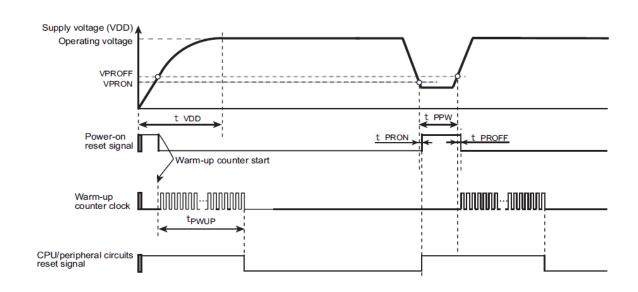

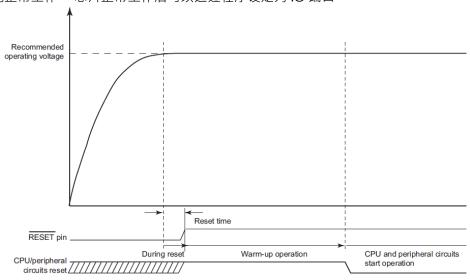

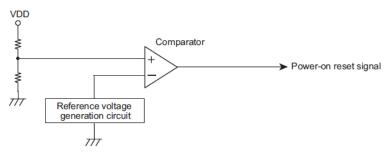

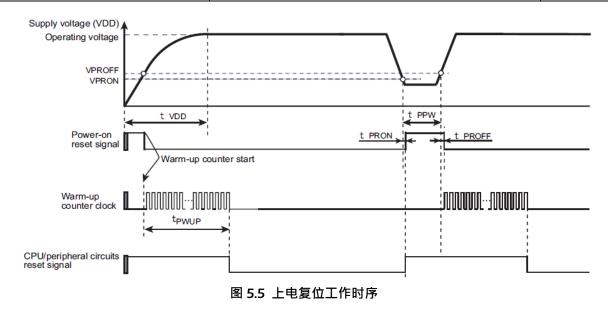

|   | 5.2      | 上电     | .复位线路     |                             | 74            |

|   |          | 5.2.1  | 上电复位架构    |                             | 74            |

|   |          | 5.2.2  | 上电复位功能    |                             | 74            |

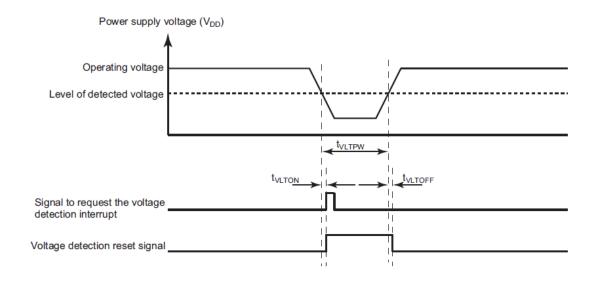

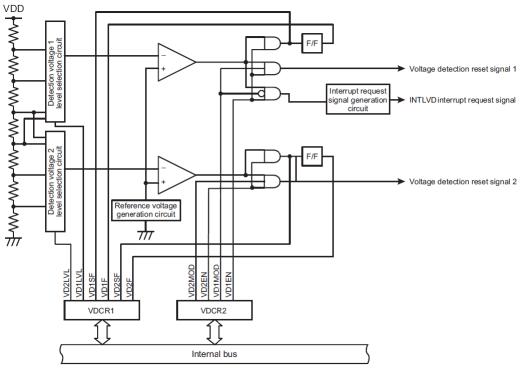

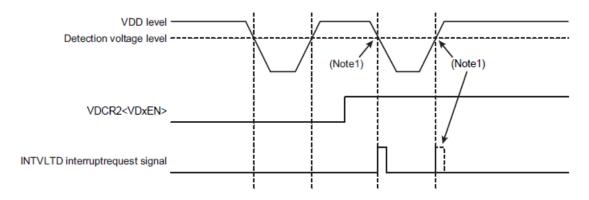

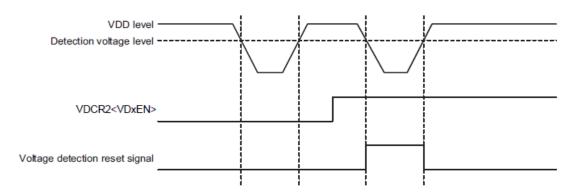

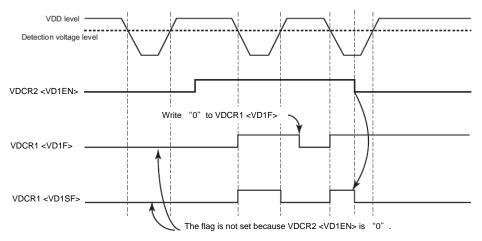

|   | 5.3      | 电压     | 检测线路      |                             | 75            |

5.3.1 电压检测架构.......75

No.: TDDS01-M6825 -CN

#### iMQ Technology Inc.

|          |                | 1                   | I   |  |  |  |

|----------|----------------|---------------------|-----|--|--|--|

|          | 5.3.2          | 电压检测控制              | 76  |  |  |  |

|          | 5.3.3 电压检测功能   |                     |     |  |  |  |

|          | 5.3.4          | 电压检测寄存器设定           | 80  |  |  |  |

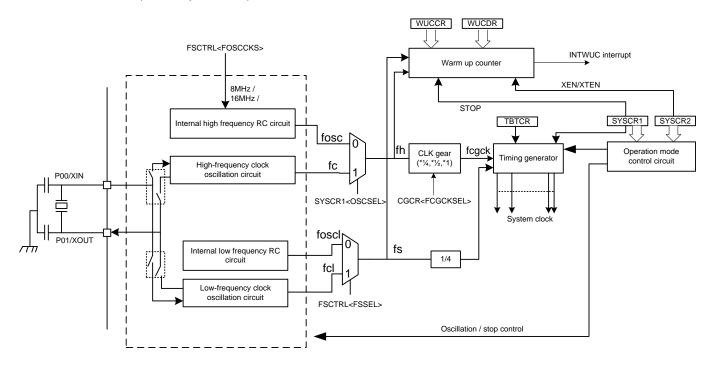

| 6.系统时    | <b>対</b> 钟控制   | ∥器                  | 82  |  |  |  |

| 6.1      | 系统             | 时钟架构                | 82  |  |  |  |

| 6.2      | 系统             | 时钟控制                | 83  |  |  |  |

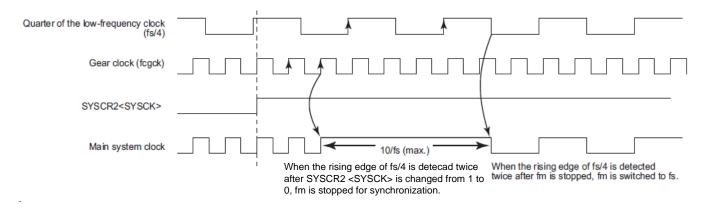

| 6.3      | 系统             | 时钟功能                | 87  |  |  |  |

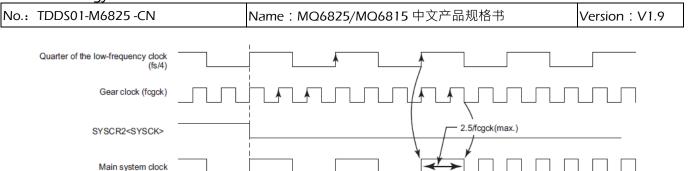

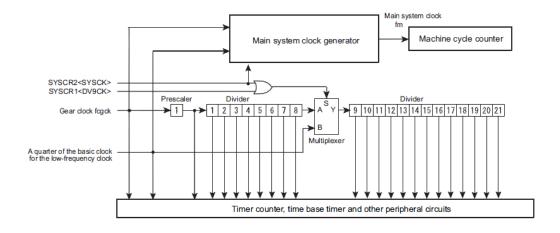

|          | 6.3.1          | 时钟产生器               | 87  |  |  |  |

|          | 6.3.2          | 时钟齿轮                | 89  |  |  |  |

|          | 6.3.3          | 时序产生器               | 89  |  |  |  |

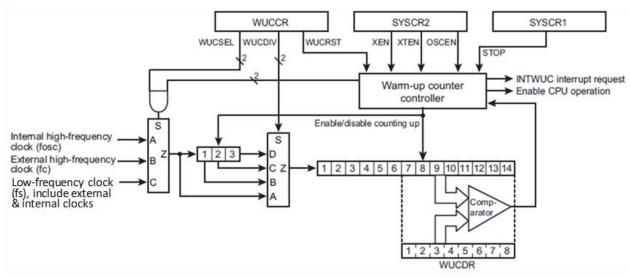

| 6.4      | 唤醒             | 计数器                 | 91  |  |  |  |

|          | 6.4.1          | 唤醒计数器操作–由硬件控制振荡     | 91  |  |  |  |

|          | 6.4.2          | 唤醒计数器操作–由软件控制振荡     | 93  |  |  |  |

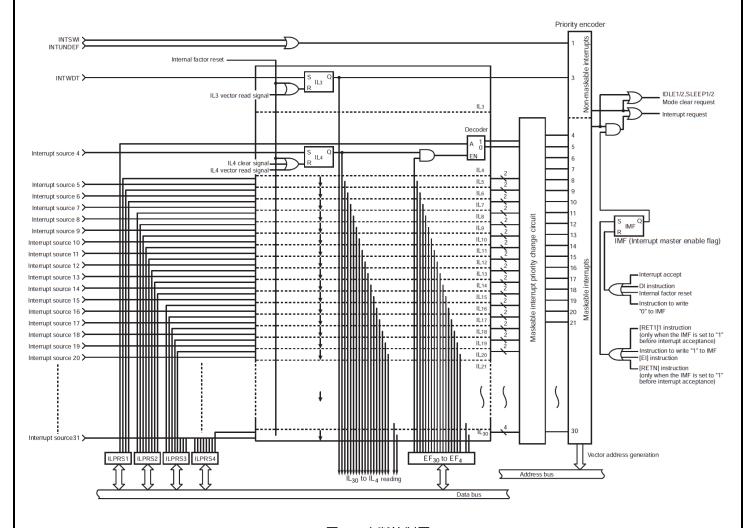

| 7. 中断.   |                |                     | 94  |  |  |  |

| 7.1      | 中断             | 锁存器 IL31 至 IL3      | 96  |  |  |  |

| 7.2      | 中断             | 允许寄存器 EIR           | 97  |  |  |  |

| 7.3      | 中断             | 主允许标帜 IMF           | 97  |  |  |  |

| 7.4      | 个别             | 中断允许标帜 EF31 至 EF4   | 97  |  |  |  |

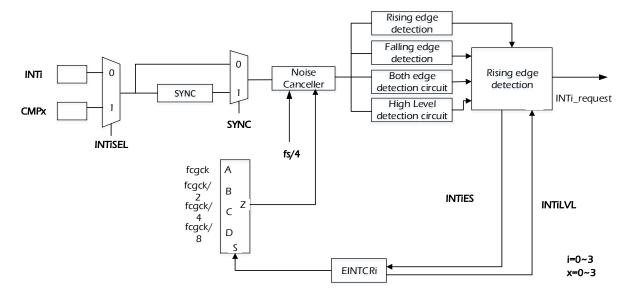

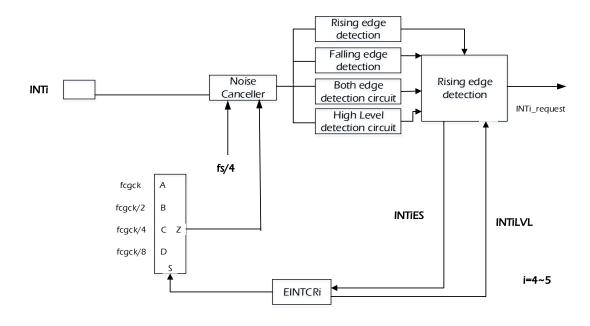

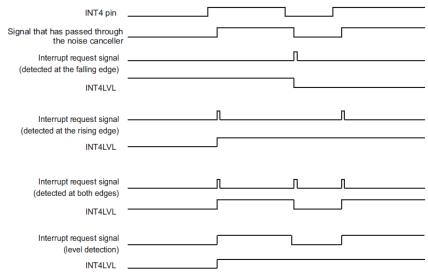

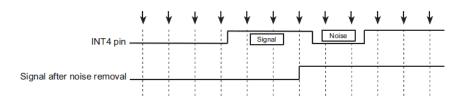

| 7.5      | 外部             | 中断控制线路              | 101 |  |  |  |

|          | 7.5.1          | 外部中断架构              | 101 |  |  |  |

|          | 7.5.2          | 外部中断控制              | 103 |  |  |  |

|          | 7.5.3          | 外部中断功能              | 109 |  |  |  |

| 8. I/O 端 | <del>і</del> П |                     | 112 |  |  |  |

| 8.1      | I/O !          | 端口控制寄存器             | 113 |  |  |  |

| 8.2      | I/O !          | 端口设定                | 114 |  |  |  |

| 8.3      | I/O            | 端口寄存器               | 118 |  |  |  |

|          | 8.3.1          | P0 端口(P01 和 P00)寄存器 | 118 |  |  |  |

|          | 8.3.2          | P1 端口(P10)寄存器       | 121 |  |  |  |

|          | 8.3.3          | P2 端口(P27 到 P20)寄存器 | 123 |  |  |  |

|          | 8.3.4          | P4 端口(P47 到 P40)寄存器 | 126 |  |  |  |

|          | 8.3.5          | P5 端口(P57 到 P51)寄存器 | 129 |  |  |  |

|          |                |                     |     |  |  |  |

Name: MQ6825/MQ6815 中文产品规格书

Version: V1.9

#### iMQ Technology Inc.

| No.: TDDS01-M6825 -CN |            |                     | Name: MQ6825/MQ6815 中文产品规格书 | Version: V1.9 |

|-----------------------|------------|---------------------|-----------------------------|---------------|

|                       | 8.3.6      | P7 端口(P77 到 P76     | 0)寄存器                       | 131           |

|                       | 8.3.7      |                     | ·<br>0)寄存器                  |               |

|                       | 8.3.8      |                     | ·<br>0)寄存器                  |               |

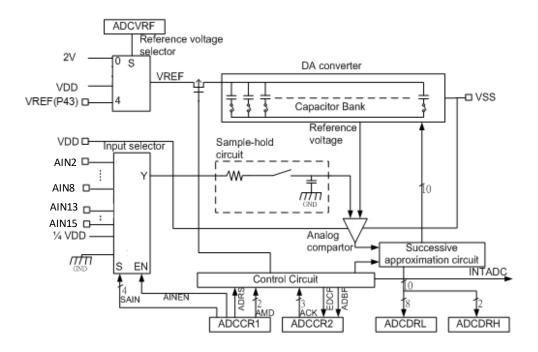

| 9. 10 位               |            |                     |                             |               |

| 9.1                   | AD \$      | 专换器架构               |                             | 139           |

| 9.2                   | AD \$      | 专换器控制               |                             | 140           |

| 9.3                   | AD \$      | 专换器功能               |                             | 144           |

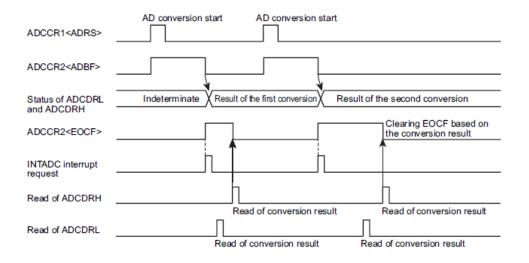

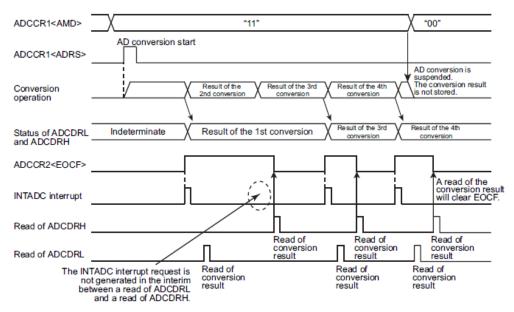

|                       | 9.3.1      | 单次模式                |                             | 144           |

|                       | 9.3.2      | 重复模式                |                             | 145           |

|                       | 9.3.3      | 禁止 AD 操作与强制         | Ϳ AD 操作停止                   | 146           |

| 9.4                   | AD \$      | 专换器寄存器设定 <b>.</b> . |                             | 146           |

| 9.5                   | <b>启</b> 动 | 停止/空闲 0/低速模         | 式                           | 146           |

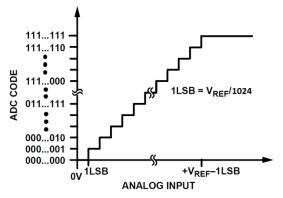

| 9.6                   | 模拟         | 信号输入电压与 AD          | 转换结果                        | 147           |

| 9.7                   | 注意         | 事项                  |                             | 148           |

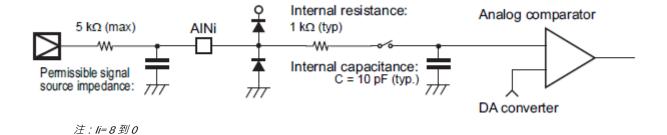

|                       | 9.7.1      | 模拟信号输入引脚电           | 3压范围                        | 148           |

|                       | 9.7.2      | 模拟信号输入引脚作           | ₹ I/O 端口用                   | 148           |

|                       |            |                     |                             |               |

| 10. 定日                | 付器/计       | 数器                  |                             | 149           |

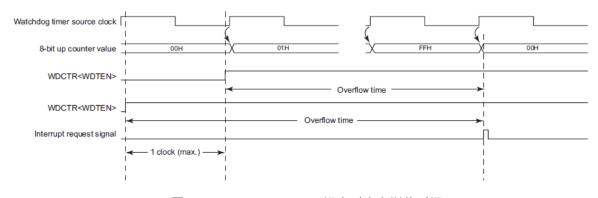

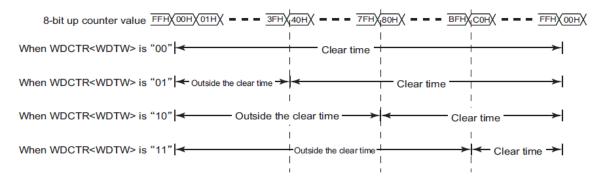

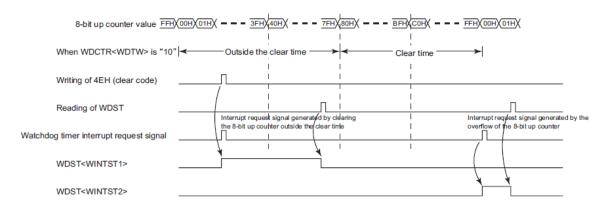

| 10                    | .1 看门      | 狗定时器/看门狗定时          | 寸器 2 (WDT/WDT2)             | 149           |

|                       | 10.1.1     | 看门狗定时器架构            |                             | 149           |

|                       | 10.1.2     | 2 看门狗定时器 /看         | 门狗定时器 2 控制                  | 150           |

|                       | 10.1.3     | 3 看门狗定时器 /看         | 门狗定时器 2 功能                  | 152           |

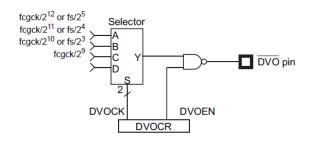

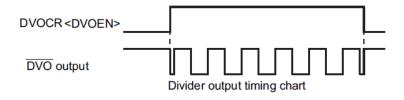

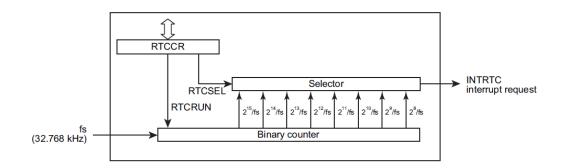

| 10                    | .2 分频      | 器输出(DVOB)           |                             | 157           |

|                       | 10.2.1     | 分频器输出架构             |                             | 157           |

|                       | 10.2.2     | 2 分频器输出控制           |                             | 157           |

|                       | 10.2.3     | 3 分频器输出功能           |                             | 158           |

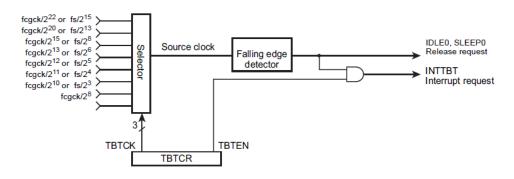

| 10                    |            |                     |                             |               |

|                       |            |                     |                             |               |

|                       |            |                     |                             |               |

|                       |            |                     |                             |               |

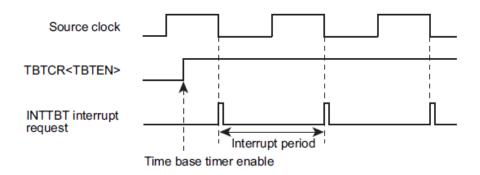

| 10                    | .4 实时      | 时钟(RTC)             |                             | 161           |

|                       |            |                     |                             |               |

No.: TDDS01-M6825 -CN

#### iMQ Technology Inc.

| 10.4.1 实时时钟架构                                                       | 161 |

|---------------------------------------------------------------------|-----|

| 10.4.2 实时时钟控制                                                       | 161 |

| 10.4.3 实时时钟功能                                                       | 163 |

| 10.4.4 实时时钟工作                                                       | 163 |

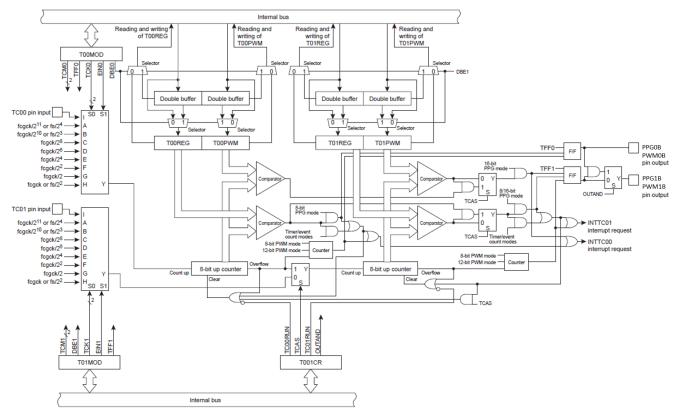

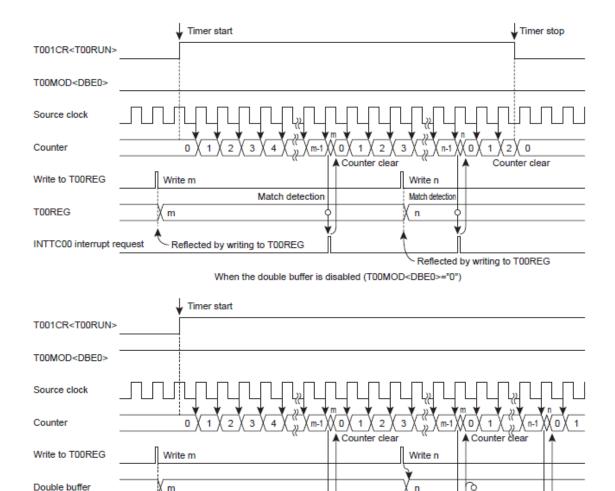

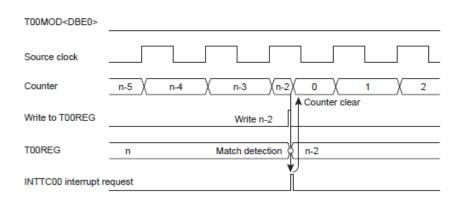

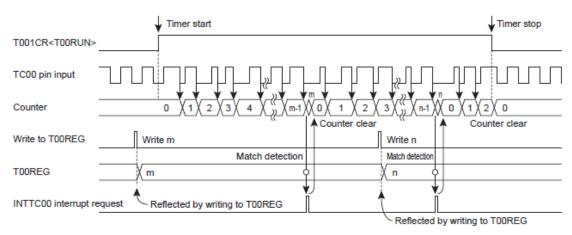

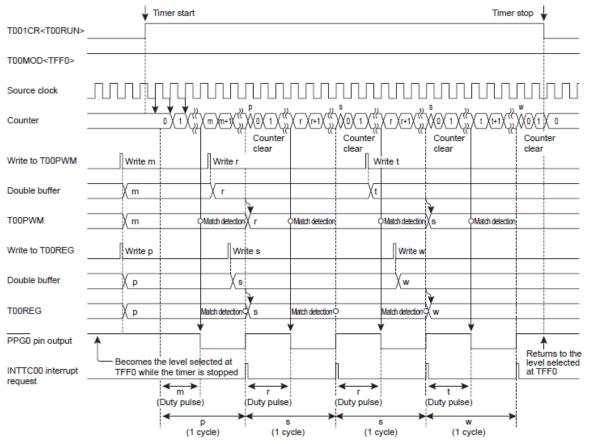

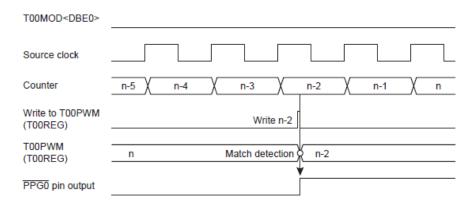

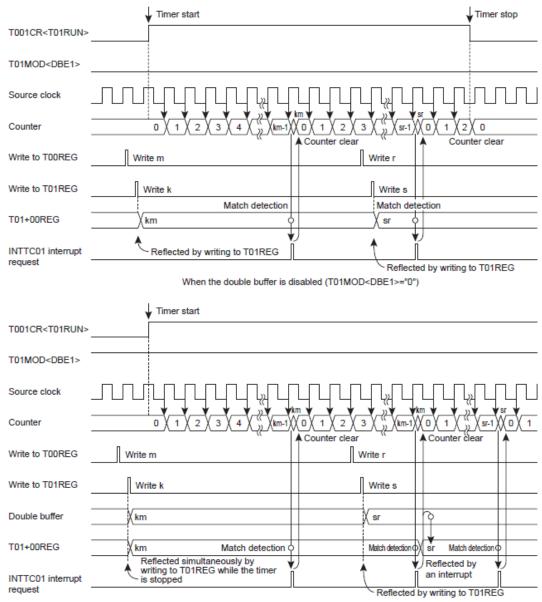

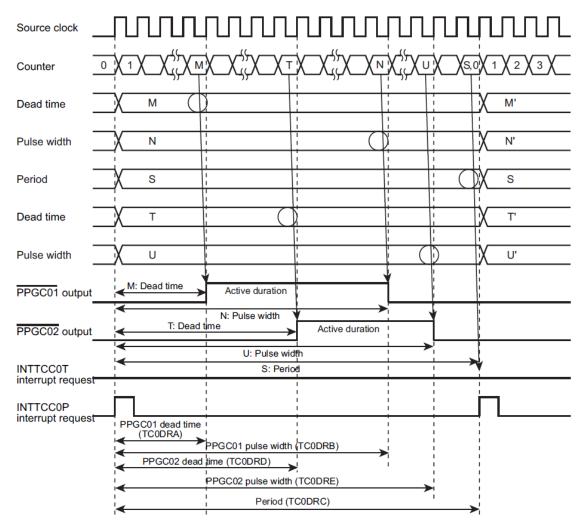

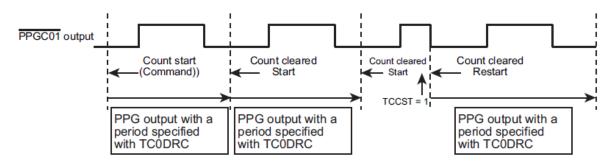

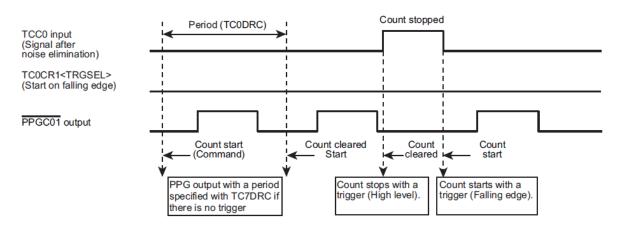

| 10.5 8 位定时器计数器(TC0)                                                 | 165 |

| 10.5.1 8 位定时器计数器控制                                                  | 166 |

| 10.5.2 低耗电功能                                                        | 172 |

| 10.5.3 定时器功能                                                        | 172 |

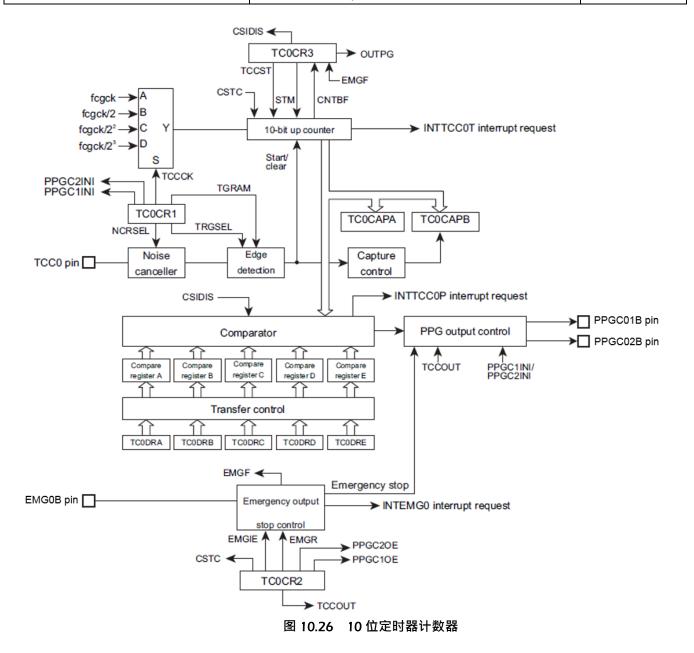

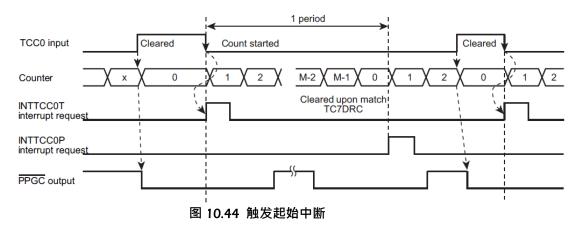

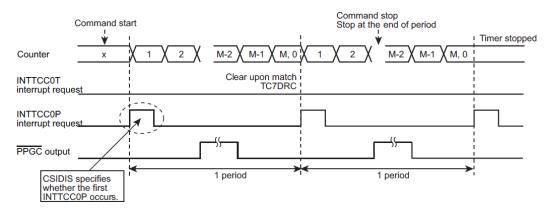

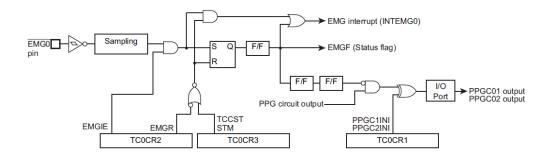

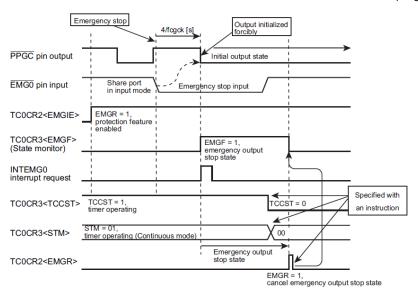

| 10.6 10 位定时器/计数器(TCC0、TCC1、TCC2)                                    | 199 |

| 10.6.1 10 位定时器计数器控制                                                 | 201 |

| 10.6.2 低耗电功能                                                        | 206 |

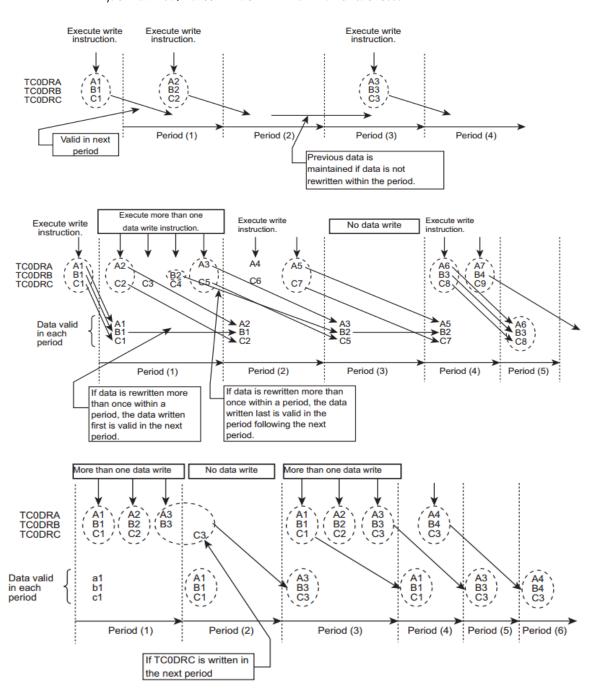

| 10.6.3 配置控制及数据寄存器                                                   | 207 |

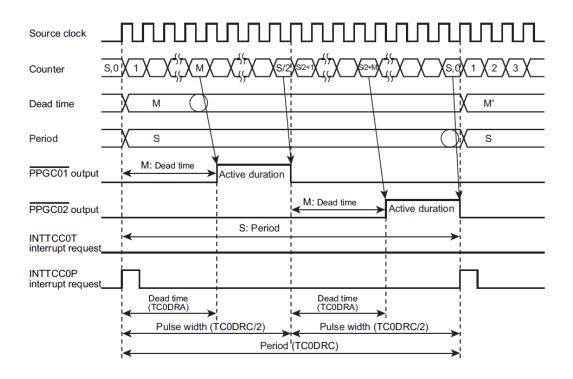

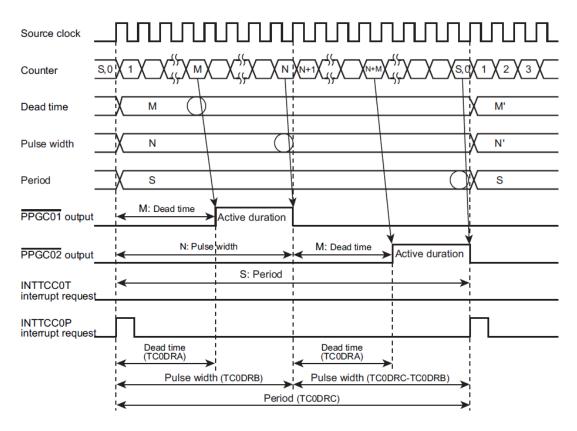

| 10.6.4 10 位定时器功能                                                    | 209 |

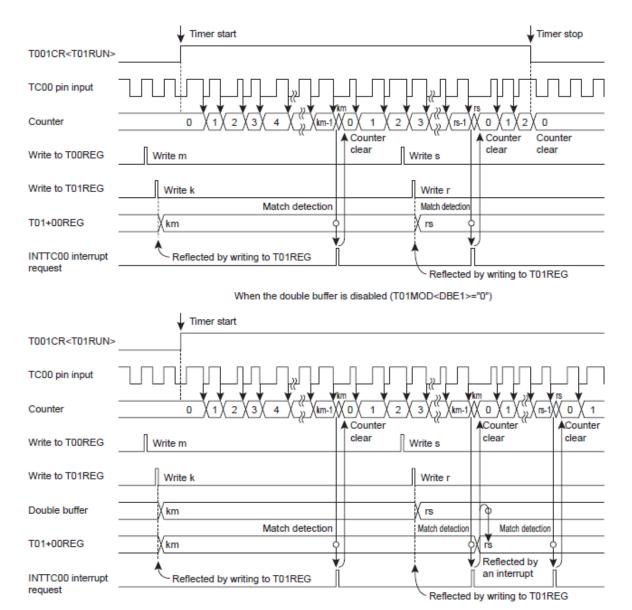

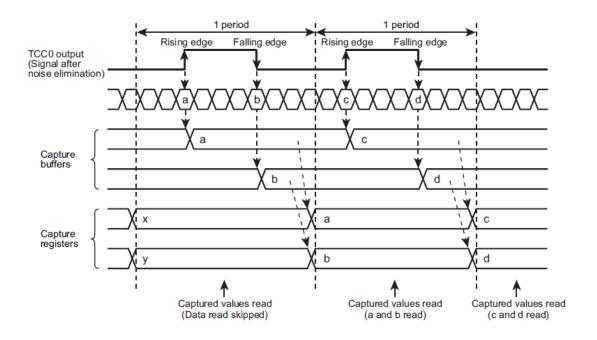

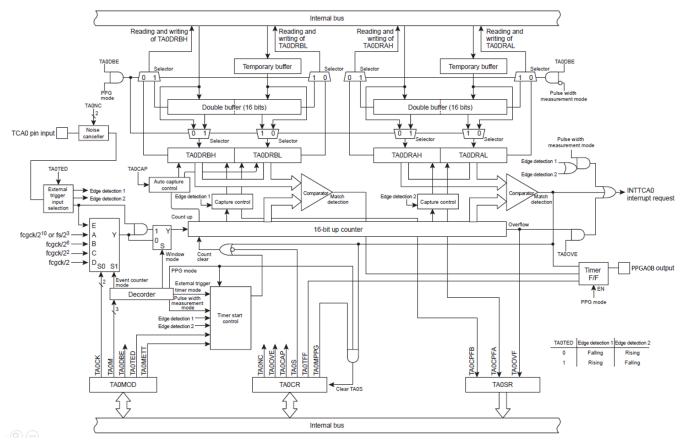

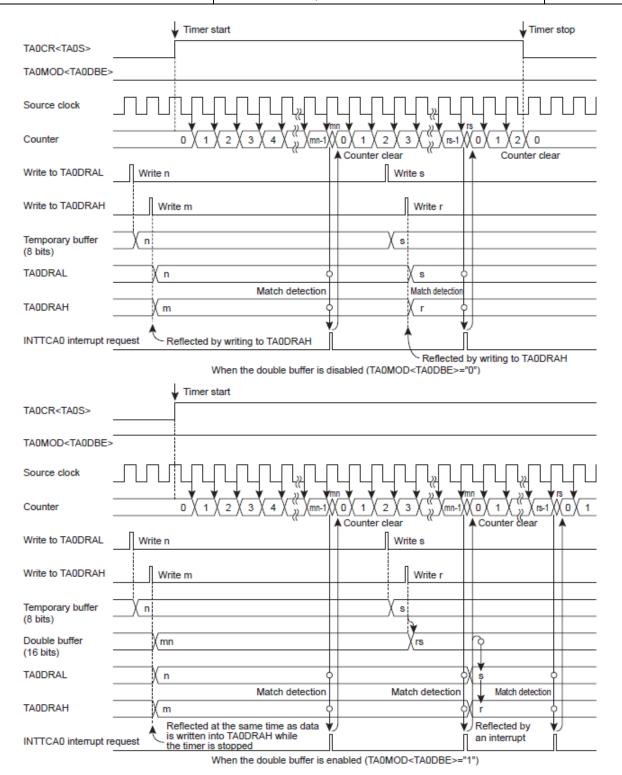

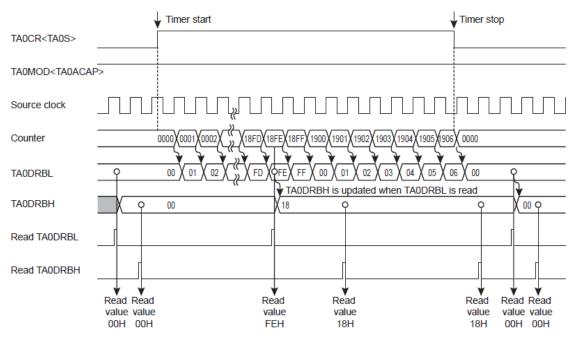

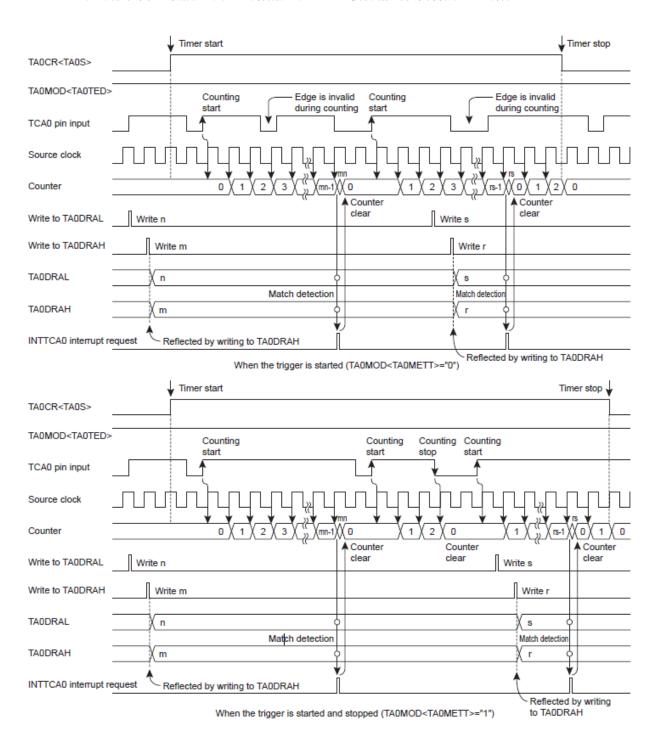

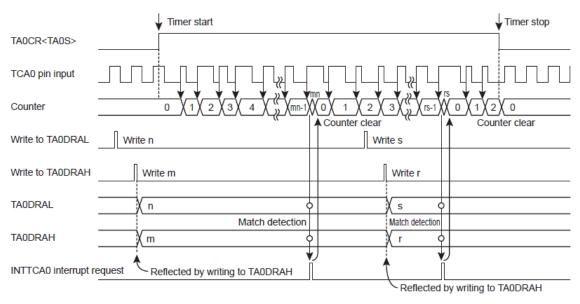

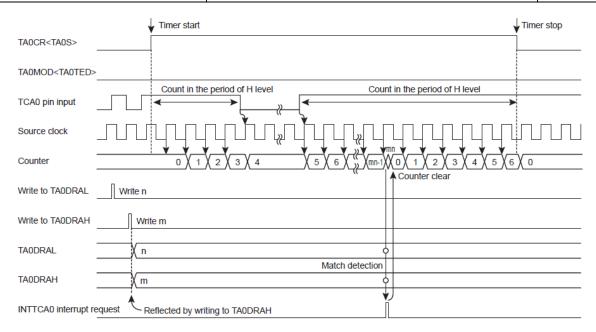

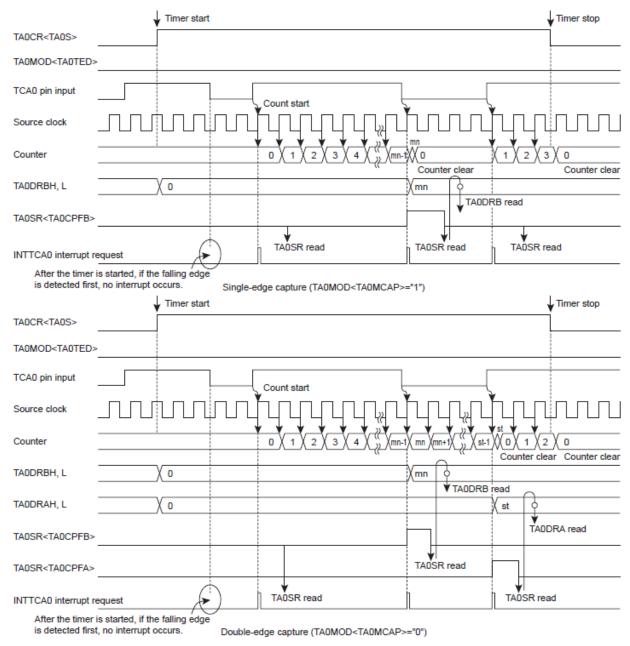

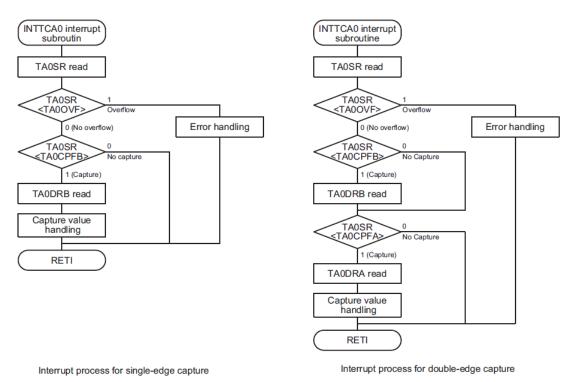

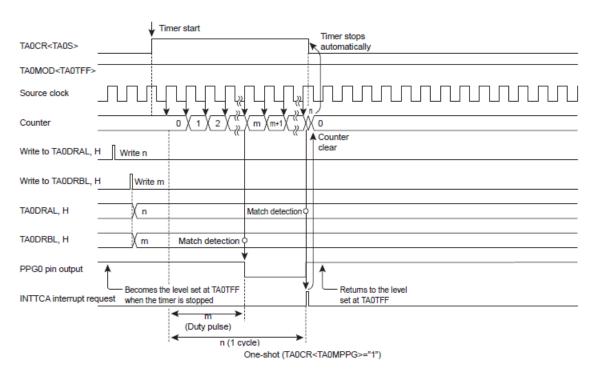

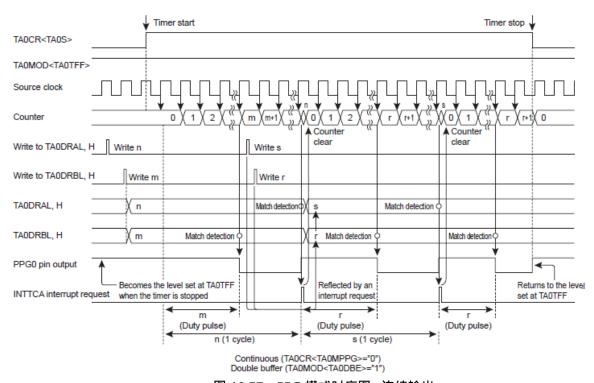

| 10.7 16 位定时器计数器(TCA0、TCA1)                                          | 231 |

| 10.7.1 16 位定时器计数器控制                                                 | 232 |

| 10.7.2 低耗电功能                                                        | 236 |

| 10.7.3 定时器功能                                                        | 236 |

| 10.7.4 噪声抑制                                                         | 250 |

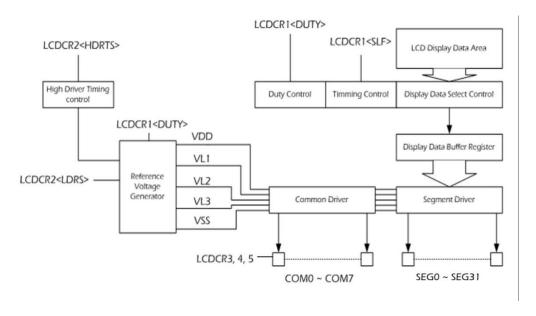

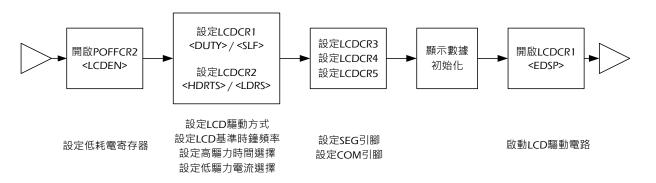

| 11. LCD 驱动功能                                                        | 251 |

| 11.1 LCD 驱动架构                                                       | 251 |

| 11.2 LCD 驱动控制                                                       | 252 |

| 11.3 低耗电功能                                                          | 256 |

| 11.4 LCD 驱动功能                                                       | 257 |

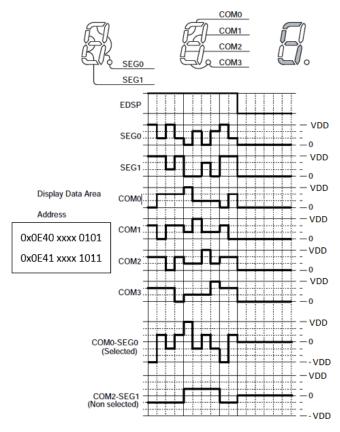

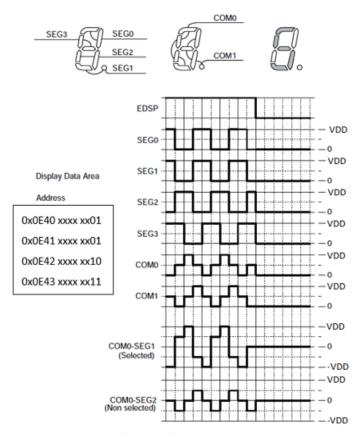

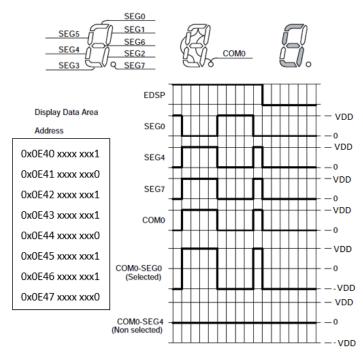

| 11.4.1 LCD 显示允许控制 (LCDCR1 <edsp>)</edsp>                            | 257 |

| 11.4.2 LCD 驱动方式选择 (LCDCR1 <duty>)</duty>                            | 258 |

| 11.4.3 框频率设定 (LCDCR1 <slf>)</slf>                                   | 260 |

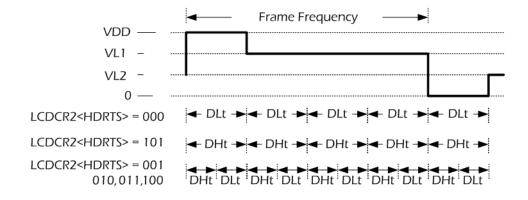

| 11.4.4 高驱力时间选择 (LCDCR2 <hdrts>)与低电流选择 (LCDCR2<ldrs>)</ldrs></hdrts> | 261 |

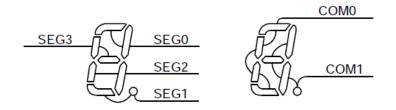

| 11.5 LCD 显示数据设定                                                     | 263 |

| 11.6 LCD 驱动功能之控制范例                                                  | 265 |

| 11.6.1 初始化                                                          | 265 |

| 11.6.2 显示数据设定                                                       | 265 |

|                                                                     |     |

Name: MQ6825/MQ6815 中文产品规格书

Version: V1.9

$Page: 6/ 359 \\ + 出版物内容版权为汉芝电子所有·非经汉芝电子书面同意·不得变更内容及使用·汉芝电子保留随时修改本出版物内容之权益·恕不另行通知。购买汉芝电子产品前·请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域·汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。$

No.: TDDS01-M6825-CN

#### iMQ Technology Inc.

| ,                                                 |     |

|---------------------------------------------------|-----|

| 11.6.3 驱动输出范例                                     | 267 |

| 11.7 LCD 进入 STOP mode 范例程序                        | 269 |

| 12. 通用异步收发器 (UART)                                | 271 |

| 12.1 UART 架构                                      | 271 |

| 12.2 UART 控制                                      | 276 |

| 12.3 防止 UART1CR1 与 UART1CR2 寄存器改变的保护机制            | 276 |

| 12.4 启动停止模式、空闲 0 模式或睡眠 0 模式                       | 277 |

| 12.4.1 寄存器状态转换                                    | 277 |

| 12.4.2 TXD 引脚状态转换                                 | 277 |

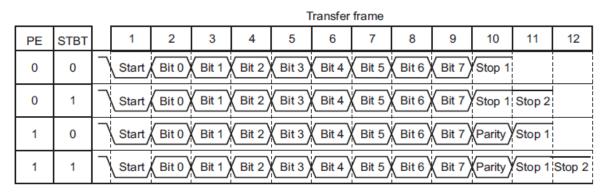

| 12.5 收发数据格式                                       | 278 |

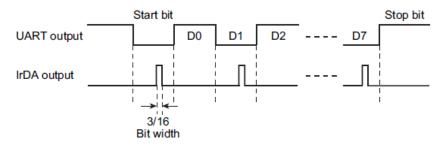

| 12.6 红外线数据收发模式                                    | 278 |

| 12.7 收发波特率 (Baud Rate)                            | 279 |

| 12.7.1 收发波特率计算方法                                  | 280 |

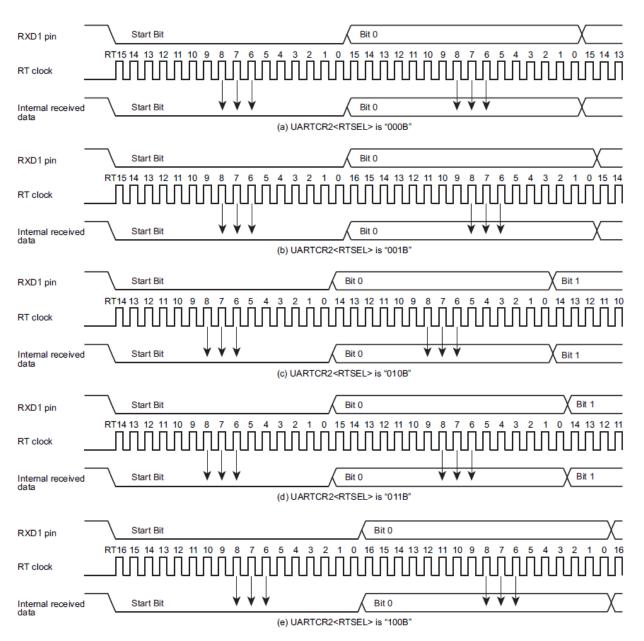

| 12.8 数据取样方法                                       | 282 |

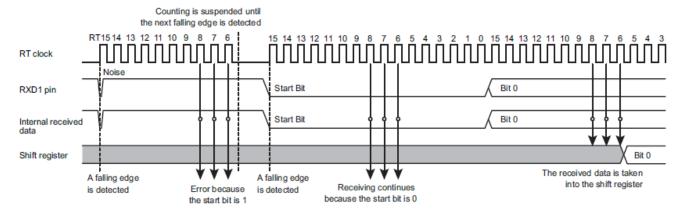

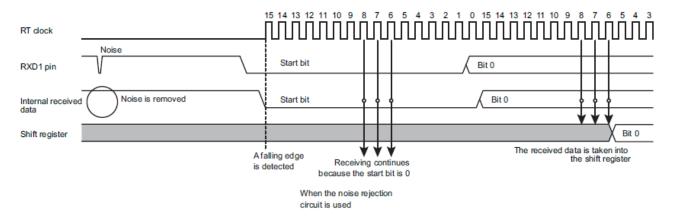

| 12.9 接收数据的噪声抑止                                    | 283 |

| 12.10 发送/接收工作                                     | 284 |

| 12.10.1 数据发送工作                                    | 284 |

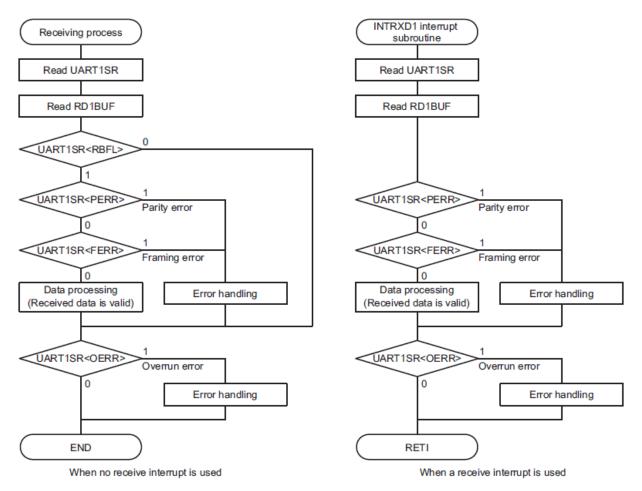

| 12.10.2 数据接收工作                                    | 285 |

| 12.11 状态标帜                                        | 285 |

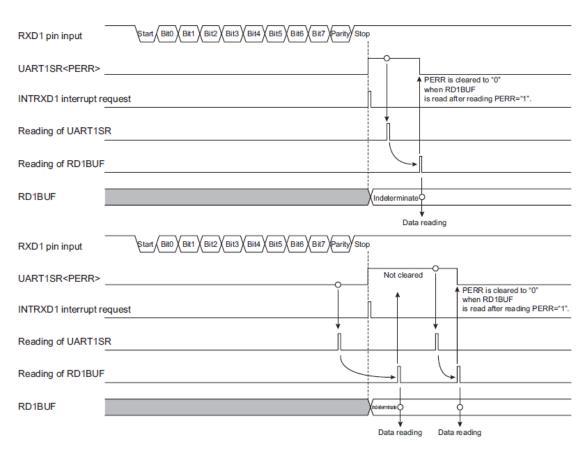

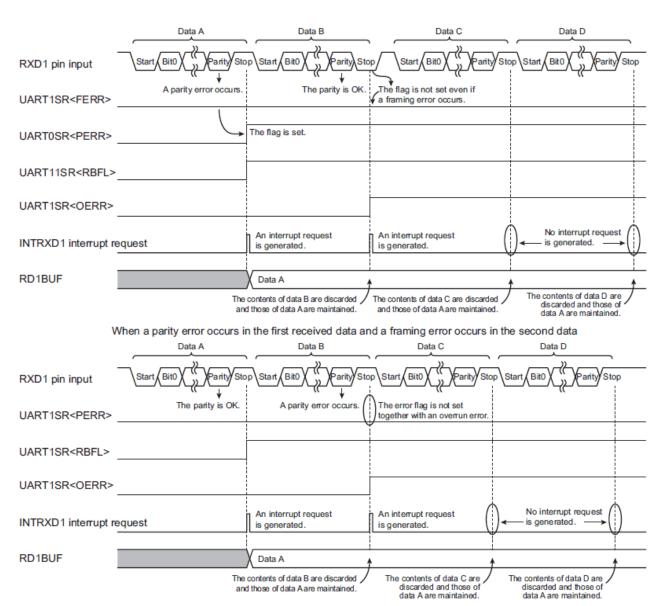

| 12.11.1 奇偶校验错误标帜                                  | 285 |

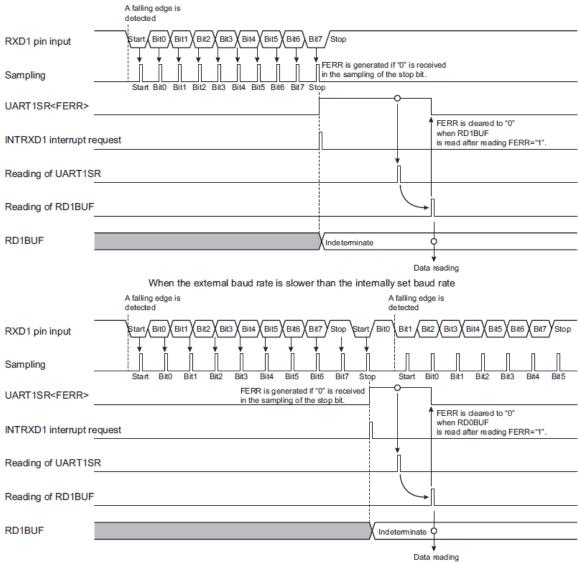

| 12.11.2 数据框错误标帜                                   | 286 |

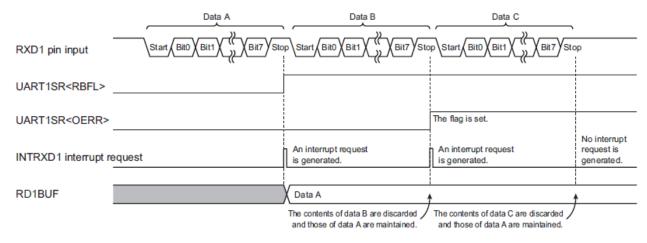

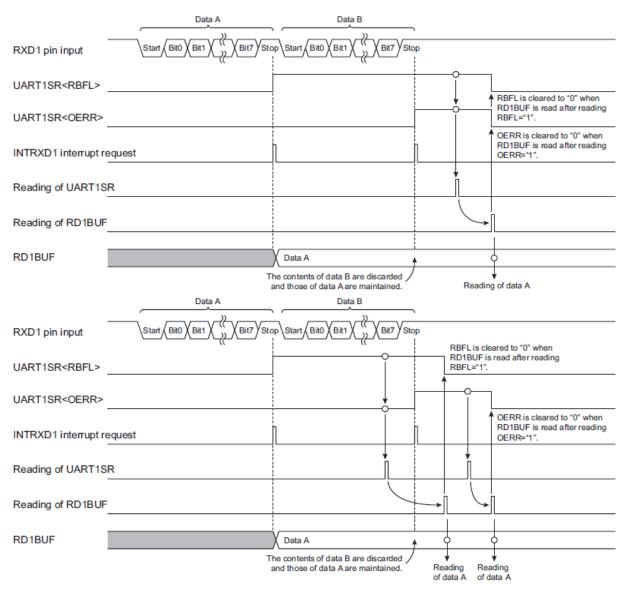

| 12.11.3 溢出错误标帜                                    | 287 |

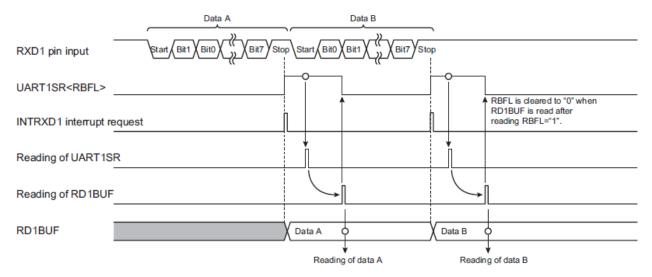

| 12.11.4 接收寄存器 已满标帜                                | 289 |

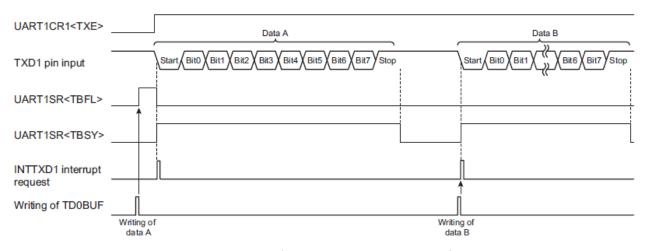

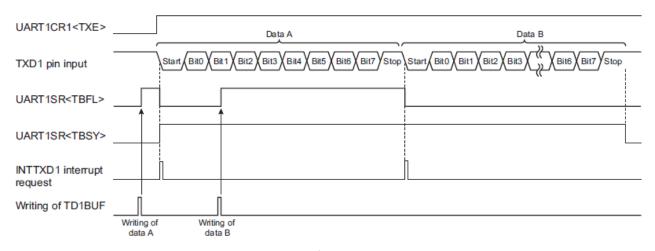

| 12.11.5 发送忙碌标帜                                    | 290 |

| 12.11.6 发送寄存器 已满标帜                                | 291 |

| 12.12 接收进程                                        | 291 |

| 13. Flash 存储器                                     | 294 |

| 13.1 Flash 存储器控制                                  | 294 |

| 13.2 Flash 存储器功能                                  | 295 |

| 13.2.1 Flash 存储器命令序列与切换控制(FLSCR1 <flsmd>)</flsmd> | 295 |

| 13.3 命令序列 Command Sequence                        | 296 |

|                                                   |     |

Name: MQ6825/MQ6815 中文产品规格书

Version: V1.9

## iMQ Technology Inc.

| No.: TDDS01-M6825 -CN | Name: MQ6825/MQ6815 中文产品规格书 | Version: V1.9 |

|-----------------------|-----------------------------|---------------|

|                       |                             |               |

| 13.3.1                  | 字节编程 Byte Program              | 296 |

|-------------------------|--------------------------------|-----|

| 13.3.2                  | 区块擦除 Sector Erase (128 字节部分擦除) | 296 |

| 13.3.3                  | 进入产品 ID 模式                     | 297 |

| 13.3.4                  | 跳出产品 ID 模式                     | 297 |

| 13.4 存取                 | Flash 存储器区域                    | 297 |

| 14. 串行总线接               | □(SBI)/ I2C                    | 298 |

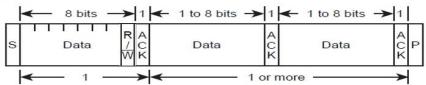

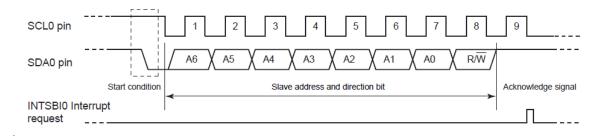

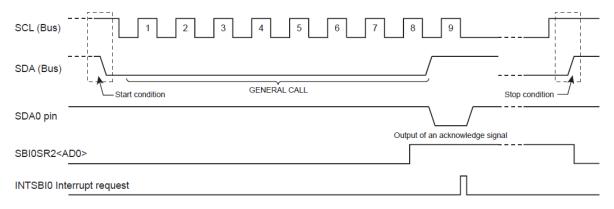

| 14.1 通信格                | §式                             | 298 |

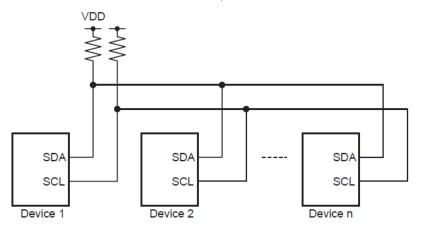

| 14.1.1                  | I2C 总线                         | 298 |

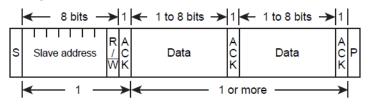

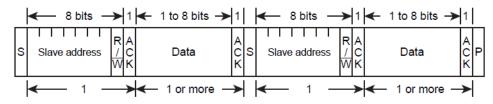

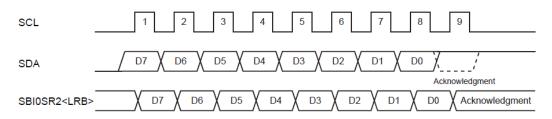

| 14.1.2                  | 通用数据格式                         | 299 |

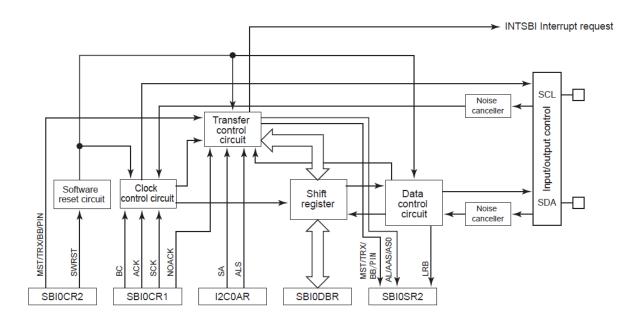

| 14.2 框图                 |                                | 300 |

| 14.3 控制                 |                                | 300 |

| 14.4 功能                 |                                | 306 |

| 14.4.1                  | 低功耗功能                          | 306 |

| 14.4.2                  | 选取从属地址配对检测与广播呼叫检测              | 306 |

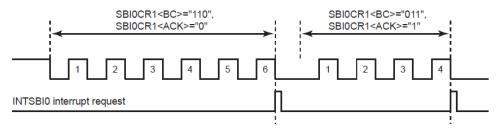

| 14.4.3                  | 选取数据传输的时钟数与选取应答或单一应答模式         | 306 |

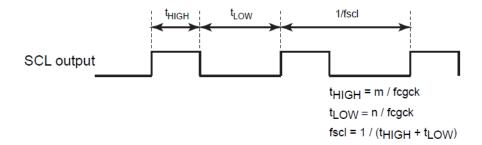

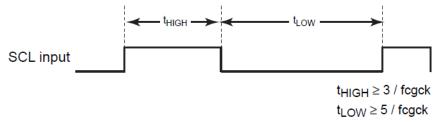

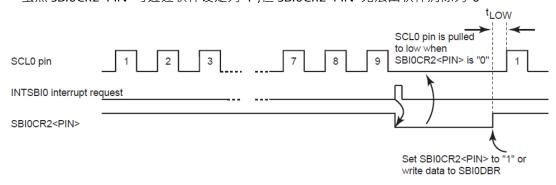

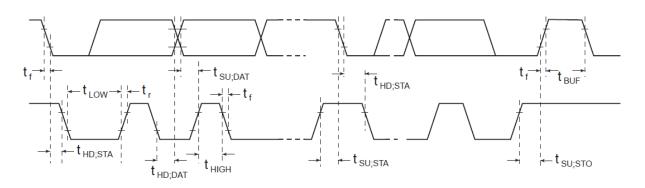

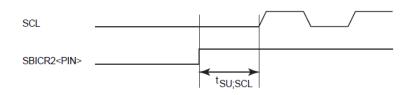

| 14.4.4                  | 串行时钟                           | 308 |

| 14.4.5                  | 选取主控/从属                        | 310 |

| 14.4.6                  | 选取传输/接收                        | 311 |

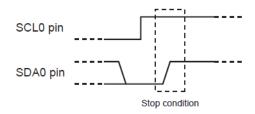

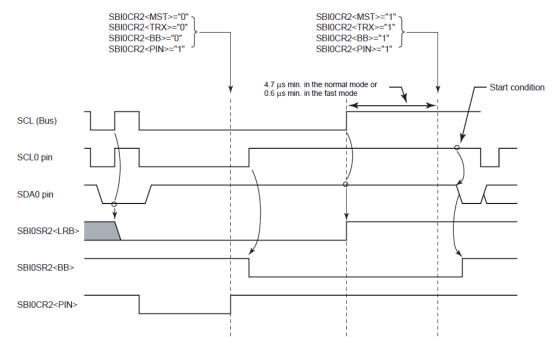

| 14.4.7                  | 生成开始/停止条件                      | 311 |

| 14.4.8                  | 中断服务需求发布与释放                    | 312 |

| 14.4.9                  | 设定串行总线接口模式                     | 313 |

| 14.4.10                 | 0 软件复位                         | 313 |

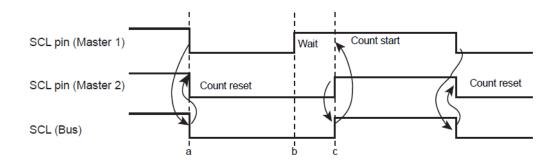

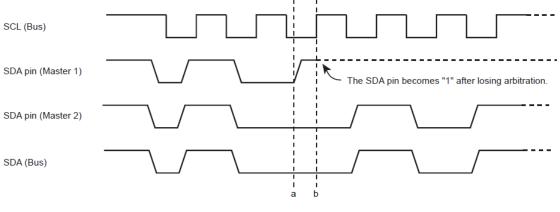

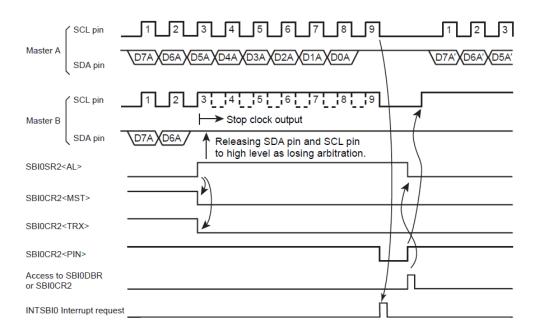

| 14.4.1                  | 1 仲裁丢失检测功能                     | 313 |

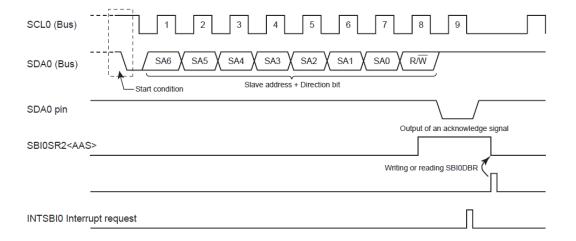

| 14.4.1                  | 2 从属地址配对检测                     | 315 |

| 14.4.13                 | 3 广播呼叫检测                       | 316 |

| 14.4.14                 | 4 最后接收位的监控                     | 316 |

| 14.4.1                  | 5 从属地址与地址辨识模式说明                | 316 |

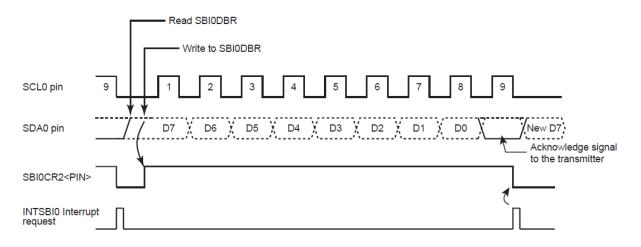

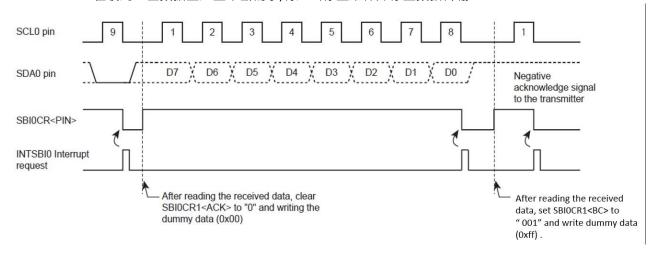

| 14.5 I <sup>2</sup> C 总 | 线的数据传输                         | 318 |

| 14.5.1                  | 设备初始化                          | 318 |

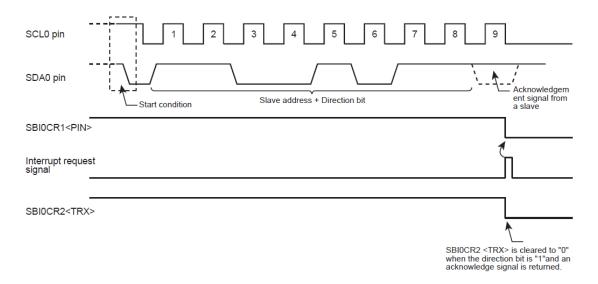

| 14.5.2                  | 开始条件与从属地址产生                    | 318 |

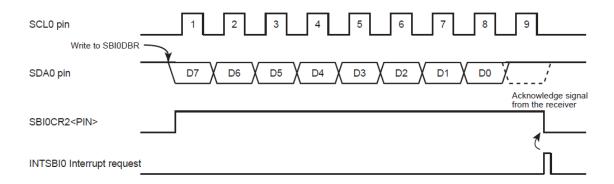

| 14.5.3                  | 1 字数据传输                        | 319 |

#### iMQ Technology Inc.

| No.: TDDS01-M6825 -CN | Name: MQ6825/MQ6815 中文产品规格书 | Version: V1.9 |

|-----------------------|-----------------------------|---------------|

| 14.5.4 停止条件产生         |                             | 323           |

|                       |                             |               |

|                       |                             |               |

|                       |                             |               |

|                       |                             |               |

|                       |                             |               |

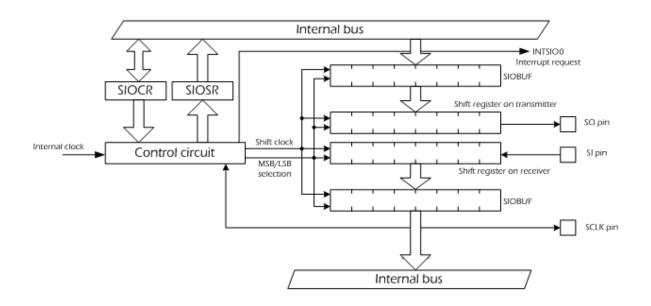

| 16.1 框图               |                             | 329           |

| 16.2 控制               |                             | 329           |

| 16.3 低耗电功能            |                             | 333           |

| 16.4 功能               |                             | 334           |

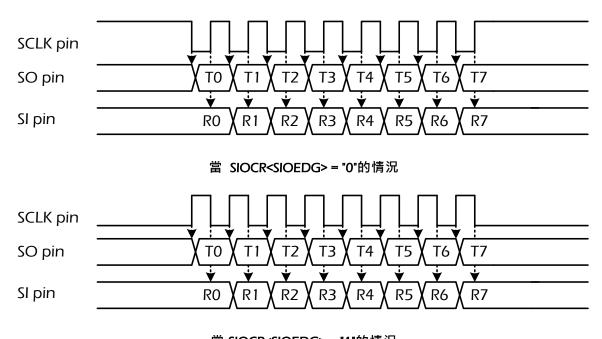

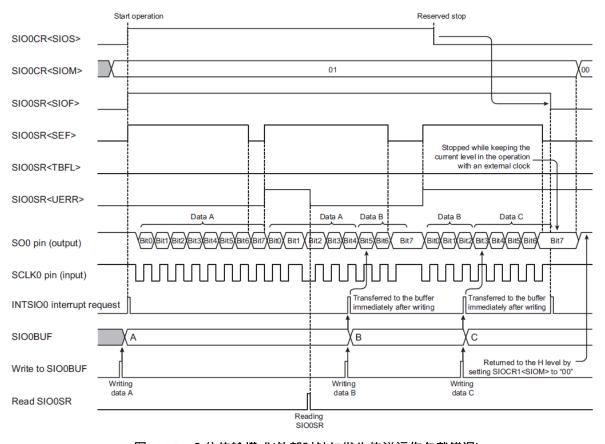

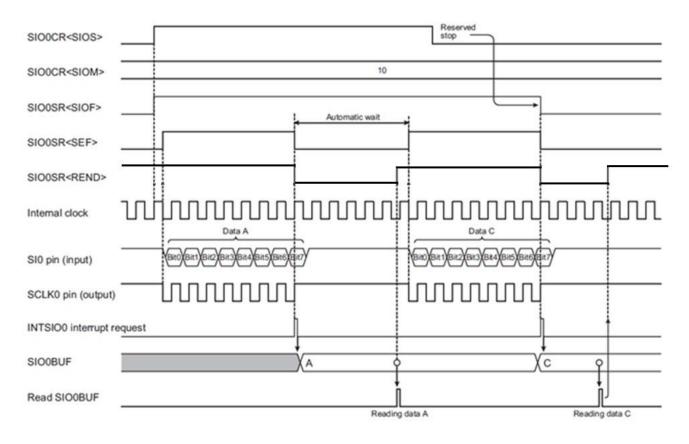

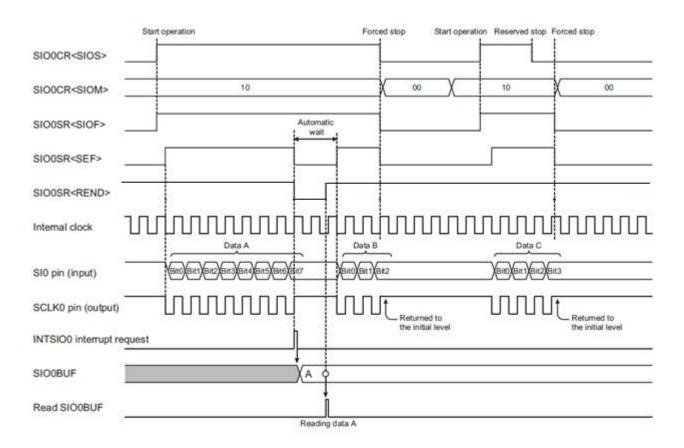

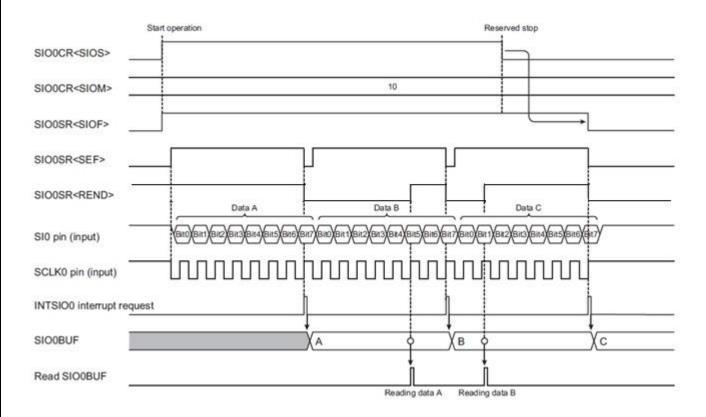

| 16.4.1 传送模式           |                             | 334           |

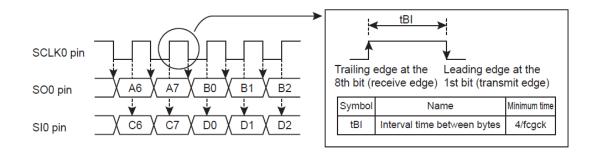

| 16.4.2 串行时钟           |                             | 334           |

| 16.4.3 触发边沿选择         |                             | 335           |

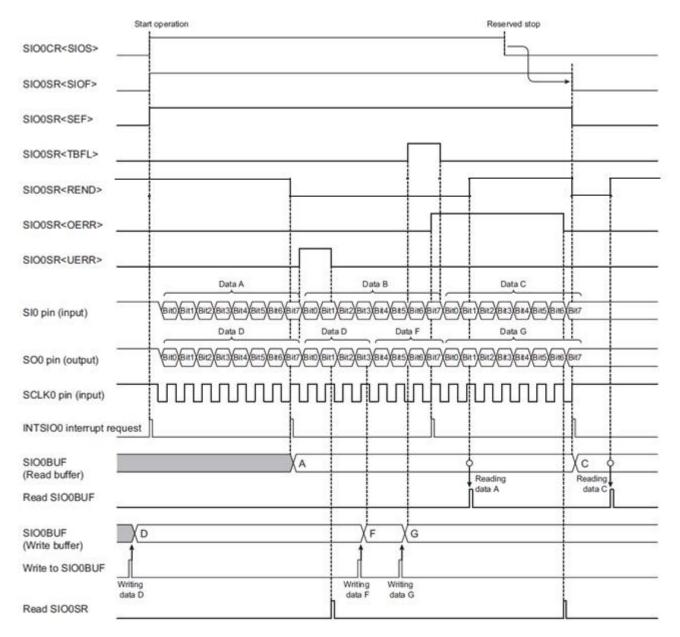

| 16.5 传送模式             |                             | 336           |

| 16.5.1 8 位传送模式        |                             | 336           |

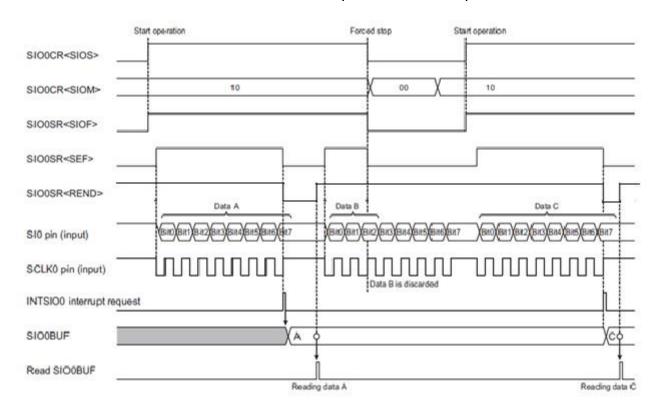

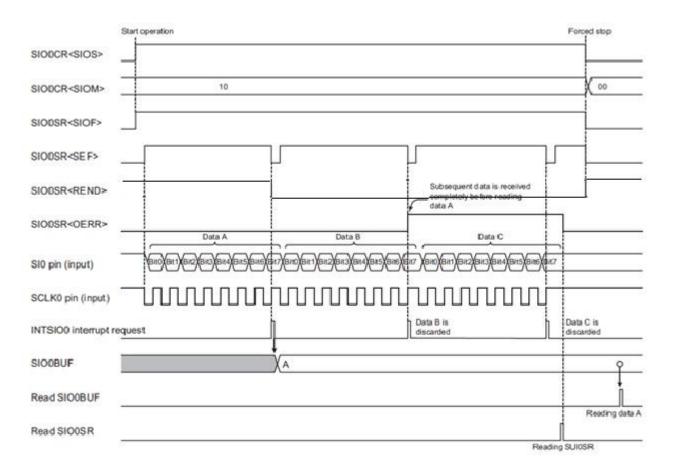

| 16.5.2 8 位接收模式        |                             | 341           |

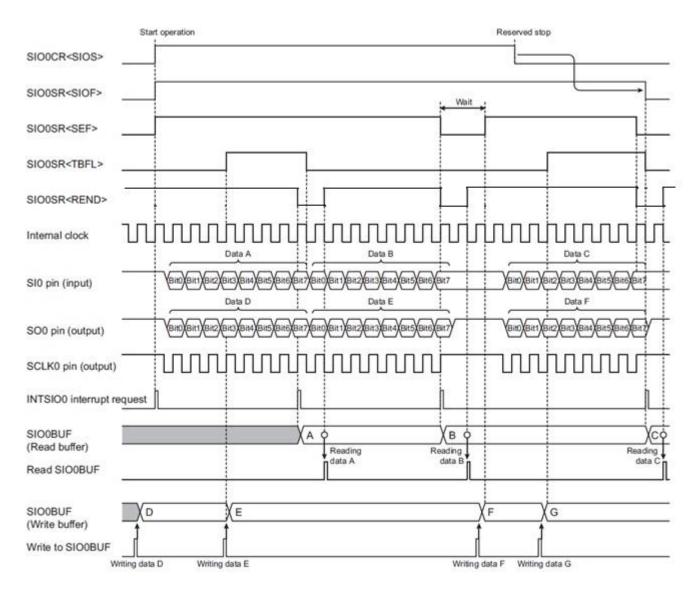

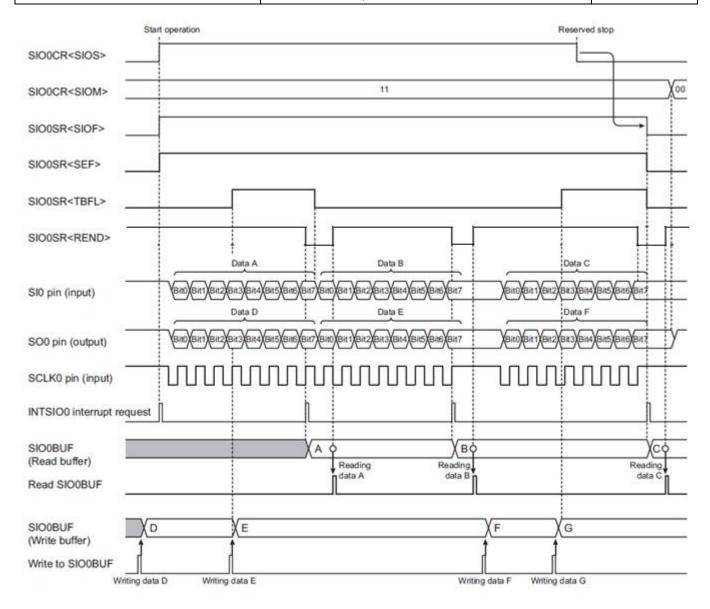

| 16.5.3 8 位传送/接收模:     | 式                           | 346           |

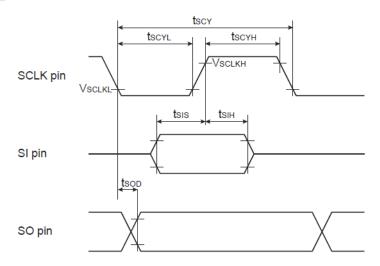

| 16.6 AC 特性            |                             | 351           |

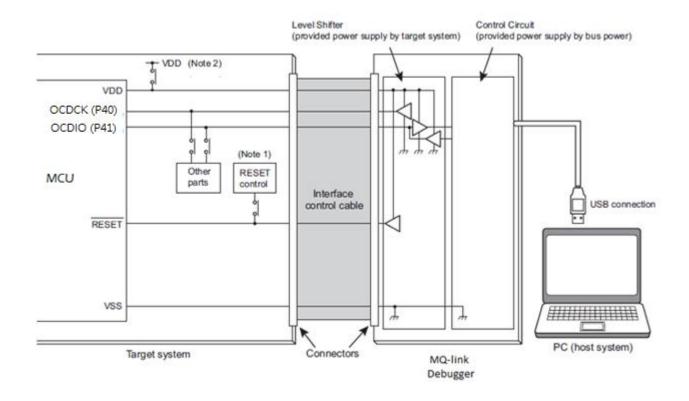

| 附录 A. 片上仿真功能(OCDE)    |                             | 352           |

| 附录 B. 产品型号信息          |                             | 354           |

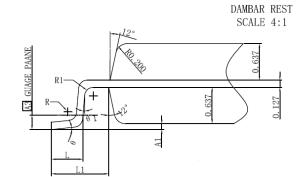

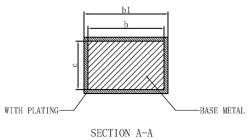

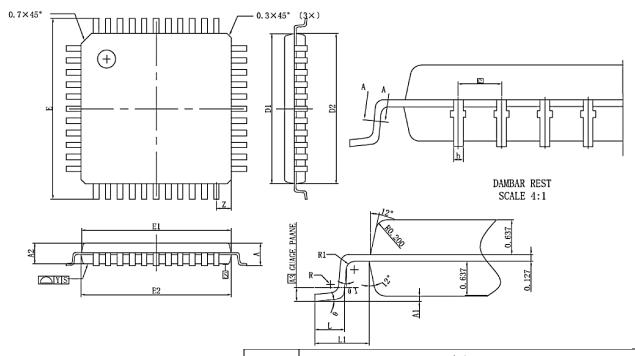

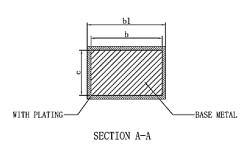

| 附录 C. 封装信息            |                             | 355           |

| 附录 D. 使用注意事项          |                             | 357           |

#### iMQ Technology Inc.

No.: TDDS01-M6825 -CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

## 1. 修改记录

| Version | Approved<br>Date | Description                                        |

|---------|------------------|----------------------------------------------------|

|         |                  | 1.「CH 2.4 引脚配置/说明」新增图 2-3 Reset 建议线路               |

|         |                  | 2.「CH 6.2 系统时钟控制」· FSCTRL 寄存器移除 bit3~bit6 注释。      |

|         |                  | 3.「CH 8.2 I/O 端口设定」· P75,P76,P77 对应 PxCR,PxFC 设定值  |

| V1.9    | 2022/3/8         | 4.「CH 10.4.2 实时时钟控制」 RTCCR 寄存器新增备注 4               |

|         |                  | 5.「CH 10.5.1 8 位定时器计数器控制」T00MOD 新增备注               |

|         |                  | 6.「11.2 LCD 驱动控制 」 LCDCR2 新增线路备注                   |

|         |                  | 7.「附录 D、使用注意事项新增 RTC 相关 」                          |

| \/1 O   | 2021/9/14        | 1.新增「CH10.7.3.6 可编程脉冲产生 PPG 输出模式」叙述:需在 PPG 初始      |

| V1.8    |                  | 化后·再对 PxFC 进行设定。                                   |

|         |                  | 1.修正「CH2.2 重点说明」产品比较表格之 MTP 说明                     |

|         |                  | 2.修正「CH2.4 引脚配置/说明」、「CH8.3.3 P2 端口寄存器」· P26,P27 新增 |

|         | 2021/7/30        | TXD1,RXD1 叙述                                       |

| V1.7    |                  | 3.修正「CH8.3.8 P9 端口寄存器」表格叙述                         |

|         |                  | 4.「CH11 LCD 驱动功能」新增注 2、「CH11.2 LCD 驱动控制」LCDCR2 寄   |

|         |                  | 存器新增注 3                                            |

|         |                  | 5.修正 POFFCFR2 叙述                                   |

| V1.6    | 2021/2/1         | 1.修正「3.6 MTP 电气特性」内容                               |

| V1.5    | 2020/2/14        | 1.修正「9.10 位 AD 转换器」的「图 9.1 10 位 AD 转换器」、「ADC 寄     |

| V 1.J   | 2020/2/17        | 存器」内容·移除 ADC 内部参考电压 3V、4V。                         |

#### iMQ Technology Inc.

No.: TDDS01-M6825 -CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

| V1.4 | 2019/10/04 | 1. 新增「2.1 定时器/计数器」之 RTC 叙述 2. 更改图 2.2 MQ6825/MQ6815 外部参考线路及描述内容 3. 「2.4 引脚配置/说明」48pin 与 44 pin 新增 注 2、注 3 4. 新增「3.2 工作条件」之备注 5. 新增「3.9 上电复位特性」及「3.10 LVD 电气特性」 6. 更新「7.5.1 外部中断架构」图 7.2 及图 7.3 7. 修改「7.5.2 外部中断控制」寄存器 EINTCR0,EINTCR1, EINTCR2 之 Bit 6 位符号由 NCE 修改为 SYNC 8. 更正「8.1 I/O 端口寄存器」,原「POFFCR4」更正为「POFFCR3」 9. 新增图 10.10 8 位定时器计数器、图 10.26 10 位定时器计数器、图 10.48 16 位定时器计数器 |

|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |            | 10. 新增「15 比较器」之叙述内容 11. 原 SPI 更正为 SIO,移除 P87/ SS1、P77/SS0 描述,相关章节更新; 更新图 16.1~16.15 12. 新增「附录 D」低速 1 (Slow 1)使用 RTC 相关及工作电流特性相关                                                                                                                                                                                                                                                   |

| V1.3 | 2018/9/6   | <ol> <li>更新「8.3.4 P4 端口(P47 到 P40) 寄存器」P2PU, P2PD,P4PU, P4PD, P7PU, P7PD</li> <li>新增「14.7 LCD 进入 STOP mode 的范例程序」</li> <li>附录 D 新增脚位相关(P2、P4、P7)与 LCD 使用注意事项</li> </ol>                                                                                                                                                                                                           |

No.: TDDS01-M6825-CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

- 1. 更新「2.2 重点说明」章节中选型表之 LVD 规格

- 2. 新增「2.4 引脚配置/说明」章节中附注

- 3. 更新「4.8 外围线路低耗电功能」、「12.1 UART 架构」、「14.3 控制」章 节中 低功耗寄存器 1 POFFCR1 位叙述

- 4. 更新低耗电寄存器 0 POFFCRO 位名称,影响章节有:

- 4.8 外围线路低耗电功能

- 10.5.1.3 定时器计数器 00 与 01 共享寄存器

- 10.6.1.1 定时器计数器 CO

- 10.7.1.16 16 位定时器计数器控制

- 5. 更新图 4.2 SFR 清单中 0x0026~0x0029 寄存器

- 6. 更新图 4.2 SFR1、SFR2、SFR3 地址所对应的寄存器名

- 7. 更新表 7.1 中断列表叙述

- 8. 更新图 7.2 外部中断架构

- 9. 更新表 7.2 外部中断叙述文字

- 10. 更新「7.4 个别中断允许标帜 EF31 至 EF4」章节之中断锁存器 ILL 与

- 11. 更新「7.4 个别中断允许标帜 EF31 至 EF4」章节之中断允许寄存器 EIRL/EIRH 功能

- 12. 更新「7.4 个别中断允许标帜 EF31 至 EF4」章节之中断锁存器 ILD 功能

- |13. 更新 「 7.4 个别中断允许标帜 EF31 至 EF4」章节之中断允许寄存器 EIRD 功能

- 14. 新增「8.3.3 P2 端口(P27 到 P23)寄存器」、「8.3.4 P4 端口(P47 到 P40) 寄存器」、「8.3.5 P7 端口(P77 到 P70)寄存器」、「8.3.6 P8 端口(P83 到 P80)寄存器」、「8.3.7 P9 端口(P91 到 P90)寄存器」章节中附注

- 15. 更新「8.3.5 P5 端口(P57 到 P51)寄存器」章节中 P5 端口内置下拉电 阻控制寄存器 P5PD 与 P5 端口输入数据寄存器 P5PRD 之命名笔误

- 16. 修正「8.3.7 P9 端口(P93 到 P90)寄存器」UART 输入输出控制寄存器 UATCNG 地址

- 17. 新增「9.2 AD 转换控制」章节中 ADC 控制寄存器 1 ADCCR1 之附注

- 18. 更新「10.5.3.7 12 位脉宽调制 PWM 输出模式」章节内容叙述

- 19. 更新图 10.13 PWM00B 脉冲输出之示意文字

- 20. 更正「10.6.1.1 定时器计数器 CO」章节中定时器/计数器 CO 控制寄存 器 2 TCOCR2 位名称笔误

- 21. 更新「10.6.1.1 定时器计数器 CO」章节中 定时器/计数器 CO 控制寄 存器 TCOCR1 之位叙述

- 22. 修正「11.2 LCD 驱动控制」LCD 控制寄存器 2 LCDCR2 位名称

- 23. 新增「11.2 LCD 驱动控制」章节中 LCD 控制寄存器 LCDCR3、LCDCR4、 LCDCR5、LCDCR6、LCDCR7 之附注。

- 24. 更新「12.1 UART 架构」UART1 状态寄存器 UART1SR 叙述

- 25. 更新「12.7 收发波特率(Baud rate)」清单

#### V1.2 2017/10/31

#### iMQ Technology Inc.

No.: TDDS01-M6825 -CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

|      |            | ,                                                     |

|------|------------|-------------------------------------------------------|

|      |            | 26. 更新「15. 比较器」章节中架构图叙述与增加使用备注                        |

|      |            | 27. 新增「16. 同步串行收发器 SIO」章节                             |

|      |            | 新增 LOFP44 封装,更新下方信息:                                  |

|      |            | - 「2.1 功能特性」中封装形式                                     |

| V1.1 | 2016/1/4   | - 「2.2 重点说明」中系列产品比较表                                  |

|      |            | - 「2.4 引脚配置/说明」中脚位示意与说明                               |

|      |            | - 「附录 C. 封装信息」                                        |

|      |            | 1.更新「2.4 引脚配置/说明」中之 P55, P56, P57 引脚功能由 TCC0B, TCC1B, |

|      |            | TCC2B 修正为 TCC0, TCC1, TCC2。                           |

|      |            | 2.更新「7. 中断」中「表 7.1 中断列表」之中断锁存器 ILD24, 25, 28, 29,     |

|      |            | 30,31 所对应之中断源名称。                                      |

|      |            | 3.更新「表 8.2 I/O 端口设定表」中                                |

|      |            | - P26, P27, P80, P81, P82, P83 有关 PPG 输出的功能名称         |

| V1.0 | 2016/10/11 | - P55, P56, P57 有关 TCC 输入的功能名称                        |

|      |            | - P75, P76, P77 有关 EMG 输入的功能名称                        |

|      |            | 4.更新「8.3 I/O 端口寄存器」章节中以下寄存器的内容:「P9 端口输出锁存             |

|      |            | 寄存器」,「P9 端口输入输出控制寄存器」,「P9 端口功能控制寄存器」,                 |

|      |            | 「P9 端口内置上拉电阻控制寄存器」,「P9 端口内置下拉电阻控制寄存                   |

|      |            | 器」,「P9 端口输入数据寄存器」。                                    |

|      |            | 5.更新「8.3 I/O 端口寄存器」章节中「UART 输入输出控制寄存器」内容。             |

|      |            |                                                       |

iMQ Technology Inc.

No.: TDDS01-M6825 -CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

## 2. 产品简介

## 2.1 功能特性

#### 基本信息

工作电压范围: 2.0V ~ 5.5V (使用LCD时: 2.6V~5.5V)

- 工作温度范围: -40℃~85℃

- i87高效能8位单片机核心搭配完整指令集

#### 内存配置

- MQ6815具有16K x 8位程序Flash内存 (重复烧写100K次,可模拟EEPROM)

- MQ6825具有16K x 8位程序Flash内存 (重复烧写100K次,可模拟EEPROM) 与16K x 8位程序MTP内存

- 2048 x 8位数据存储器RAM(堆栈寄存器)

- 64 x 8位信息块存储器

#### I/O 端口配置

- 最多46个输入/输出双向I/O端口、2个Hidriving输出引脚

- 具备2个35mA LED驱动输出 (P80/P81)、 其余除P10外、共27个I/O具备15mA输出

- 2个8位PPG输出(具有互补输出)

- 3组(6个)10位PPG输出(具有互补输出)

- 2个16位PPG输出

- 16个外部系统唤醒引脚

- 40个可编程的上拉与下拉I/O端口

- 6个通用异步收发传输器传送/接收引脚 (引脚共享描述请参阅2.4)

#### LCD 显示驱动

- 最多8 COM X 28 SEG 或4 COM X 32 SEG (具有DMA)

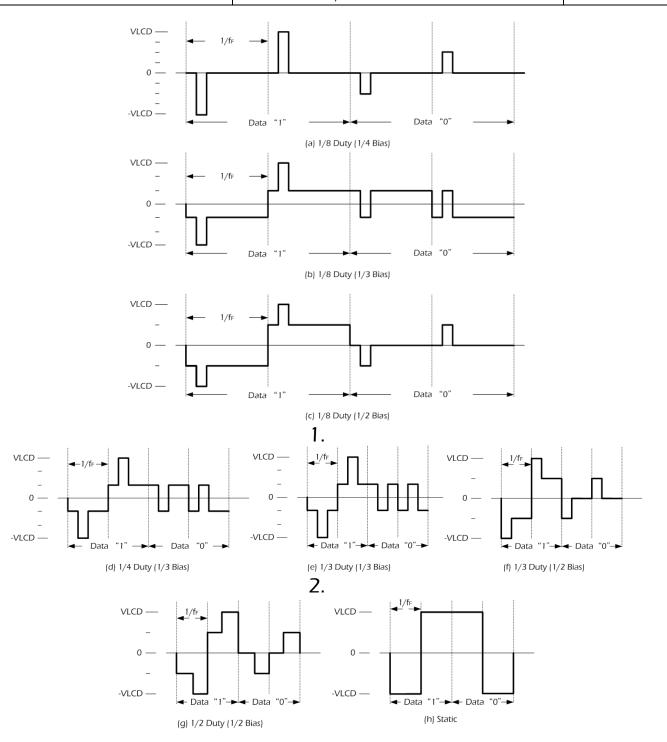

- 支持8种LCD型态 静态、1/8占空(1/4, 1/3,1/2偏压)、1/4占空(1/3偏压)、1/3占 空(1/3,1/2偏压)、1/2占空(1/2偏压) (详细细节请参阅"11 LCD 驱动功能"章节)

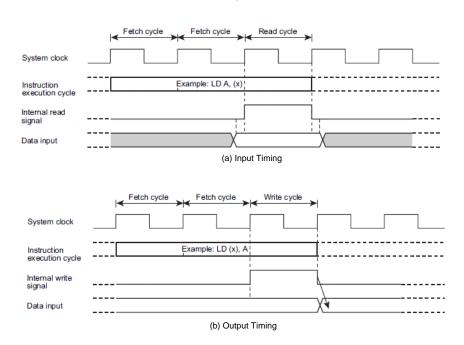

#### 指令周期

指令周期fcgck可设定为高频时钟频率fc的 1/1、1/2、1/4或1/8

#### 系统时钟源

- 可选择外部或内部RC振荡器作系统时钟源

- 可使用频率为1MHz~16MHz、或32kHz的 低频外部晶振源

- 内部高速RC振荡器频率16MHz

- 内部低速RC振荡器频率24KHz

#### 定时器/计数器

- 2个8位定时器 (TCO,具有互补输出,可组 成1个16位定时器)

- 3个10位定时器

- 2个16位定时器 (TCA,有capture功能)

- 时基定时器 (Time Base Timer, TBT)

- 看门狗定时器 (Watch Dog Timer, WDT)

- 看门狗定时器 2 (WDT2)

- 唤醒计数器 (Warm-up Counter, WUC)

- 实时时钟 (Real Time Clock, RTC)

- 8位分频器输出 (Divider, DVO) RTC在Slow1操作下, 搭配外部32.768K Crystal,会有±50ppm误差(Topr=25℃),请 参考附录D的使用注意事项"

#### 多样化的系统工作模式

- 依时钟源数分成单时钟/双时钟2种操作模式

- 单时钟模式下有1个普通模式、3个节电模式 (空闲1、空闲0、停止)

- 双时钟模式下有1个普通模式、6个节电模式 (空闲2、低速2/1、睡眠1/0、停止)

- 普通模式:高/低速时钟都正常工作

- 低速模式:由低速时钟进行低电耗操作

- 空闲模式:CPU停止工作,输出端口以高速 或高/低速时钟共享工作

- 睡眠模式: CPU停止工作,输出端口以低速 时钟工作

Page: 14/ 359

Pk版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。

P产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害

汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

No.: TDDS01-M6825-CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

- 2组通用异步收发传输器端口 (UART)

- 2组串行外围接口 (SIO)

- 1組工业标准串口通讯(I<sup>2</sup>C)

- 29个中断源

- 最多26个内部中断源

- 6个外部中断输入引脚 (中断相关细节请参阅7.1~7.5)

- 12+1个10位AD转换器端口

- 最多12个AD转换器输入端口

- 1个内部1/4 VDD电池量测输入端口

- 3个AD转换器内部参考电压源4V、3V、2V

- 1个AD转换器外部参考电压源选择,电压范 围2.0V~5.5V

- 停止模式:振荡器停止,输出端口保持原输

- (详细细节请参阅4.3)

- 2组共8级低电压检测(LVD)系统

- 片上仿真功能(OCDE)

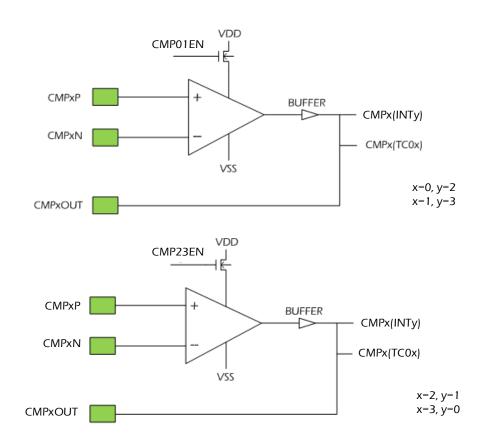

- 最多4组比较器 (Comparator)

- 封装形式

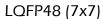

- LQFP 48 (7x7) 引脚

- LOFP 44 (10x10) 引脚

注: 使用 MO6825/MO6815 系列产品前,请详细参阅附录 D 的使用注意事项。

### 2.2 重点说明

MQ6825/MQ6815 是一个高速度高性能的 8 位单片机。此单片机在一块芯片上使用了 i87 中央处理器 CPU 内核·内置 16K x 8 位程序 Flash 存储器、16K x 8 位程序 MTP 内存(仅在 MQ6825)与 128 x 8 位数 据 Flash 存储器、2048 x 8 位数据存储器 RAM、信息块存储器、多样的 I/O 端口功能、8 COM x 28 SEG LCD 驱动、LED 驱动、多组定时器与计数器、时钟产生器,以及高精度的 10 位 AD 转换器。MQ6815 具 备多样化的单、双时钟源系统工作模式·用户可依性能、耗电等不同需求进行工作模式的优化调整。此外· MQ6825/MQ6815 的程序开发支持汇编及 C 语言两种编程语言。

由于本规格书中列及的存储器容量不超过 64K x 8 位,存储器地址将以 0x0000 至 0xFFFF 的格式表示。

如果端口的输出为低电平有效,该端口表示如 RESET、PWMOO、PWMO1、PMWO2、PWMO3、PWMO4、 PWM05、DVO 等·本规格书将以"B"加于该端口名称的后方如 RESETB、PWM00B、PWM01B、PWM02B、 PWM03B、PWM04B、PWM05B、DVOB 等作为表示。

此外·本规格书以"寄存器名称<位符号>"的命名方式表示特定位的寄存器。举例来说·ILL<IL5>表示位符号 IL5 对应的 ILL 寄存器。

**Page: 15/ 359** 图版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。 P产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害 汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

#### iMQ Technology Inc.

No.: TDDS01-M6825 -CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

| 产品型号              | MQ6825LQ048HALR                                             | MQ6815LQ048HALR                                             | MQ6825LA044HALR                                             | MQ6815LA044HALR                                             |

|-------------------|-------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|

| 脚位数               | 48                                                          | 48                                                          | 44                                                          | 44                                                          |

| (IO 数)            | (46)                                                        | (46)                                                        | (42)                                                        | (42)                                                        |

| 工作电压              | 2.0~5.5V                                                    | 2.0~5.5V                                                    | 2.0~5.5V                                                    | 2.0~5.5V                                                    |

| 工作温度              | -40~85C                                                     | -40~85C                                                     | -40~85C                                                     | -40~85C                                                     |

| 外部唤醒              | 16                                                          | 16                                                          | 15                                                          | 15                                                          |

| Flash 容量<br>/烧写次数 | 16K Bytes/10 万次                                             | 16K Bytes/10 万次                                             | 16K Bytes/10 万次                                             | 16K Bytes/10 万次                                             |

| MTP 容量<br>/烧写次数   | 16K Bytes/10 万次                                             | N/A                                                         | 16K Bytes/10 万次                                             | N/A                                                         |

| RAM               | 2048 Bytes                                                  | 2048 Bytes                                                  | 2048 Bytes                                                  | 2048 Bytes                                                  |

| ADC               | 10-bit x 12-CH<br>(1/4 VDD, 内, 外)* <sup>1</sup>             | 10-bit x 12-CH<br>(1/4 VDD, 内, 外)* <sup>1</sup>             | 10-bit x 9-CH<br>(1/4 VDD, 内, 外)* <sup>1</sup>              | 10-bit x 9-CH<br>(1/4 VDD,内,外)* <sup>1</sup>                |

| LCD               | 8x28 或 4x32                                                 | 8x28 或 4x32                                                 | 8x24 或 4x28                                                 | 8x24 或 4x28                                                 |

| 中断                | 外部: 6<br>内部: <b>26</b>                                      | 外部: 6<br>内部: 26                                             | 外部: 6<br>内部: 26                                             | 外部: 6<br>内部: 26                                             |

| 内部晶振 / 精准度        | 16MHz<br>+/- 1% @ 25C<br>+/- 2% @ 0~85C<br>+/- 3% @ -40~85C | 16MHz<br>+/- 1% @ 25C<br>+/- 2% @ 0~85C<br>+/- 3% @ -40~85C | 16MHz<br>+/- 1% @ 25C<br>+/- 2% @ 0~85C<br>+/- 3% @ -40~85C | 16MHz<br>+/- 1% @ 25C<br>+/- 2% @ 0~85C<br>+/- 3% @ -40~85C |

| 外部晶振              | 1~16MHz 或<br>32768Hz                                        | 1~16MHz 或<br>32768Hz                                        | 1~16MHz 或<br>32768Hz                                        | 1~16MHz 或<br>32768Hz                                        |

| 定时器/              | 8bit x 2<br>10bit x 3<br>16bit x 2                          |

|                   | WDT,TBT,<br>RTC,WUC                                         | WDT,TBT,<br>RTC,WUC                                         | WDT,TBT,<br>RTC,WUC                                         | WDT,TBT,<br>RTC,WUC                                         |

| PWM/PPG           | 8bit x 2<br>10bit x 3<br>16bit x 2                          |

| 低电压检测             | 8级<br>(+/- 0.1V)* <sup>2</sup>                              | 8级<br>(+/- 0.1V)* <sup>2</sup>                              | 8 级<br>(+/- 0.1V)*2                                         | 8级<br>(+/- 0.1V)*2                                          |

| 传输                | UART x 2,<br>SIO x 2,<br>I <sup>2</sup> C x 1               | UART x 2,<br>SIO x 2,<br>I <sup>2</sup> C x 1               | UART x 2,<br>SIO x 2,<br>I <sup>2</sup> C x 1               | UART x 2,<br>SIO x 2,<br>I <sup>2</sup> C x 1               |

| 比較器               | 比較器 x 4                                                     | 比較器 x 4                                                     | 比較器 x 3                                                     | 比較器 x 3                                                     |

| 片上仿真              | 有                                                           | 有                                                           | 有                                                           | 有                                                           |

| 封装                | LQFP48                                                      | LQFP48                                                      | LQFP44                                                      | LQFP44                                                      |

**Page: 16/ 359**本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

#### iMQ Technology Inc.

No.: TDDS01-M6825-CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

\*1: 「1/4 VDD」表示具有 1 个内部 1/4 VDD 电池量测输入端口; 「内」表示 ADC 有内部参考电压(2V/3V/4V); 「外」表示 ADC 使用外部参考电压。

\*2: 产品具有 2 组 LVD·每组有 4 级电压·精准度最小可达+/-0.1V, 各级的详细规格请参阅规格书内容。

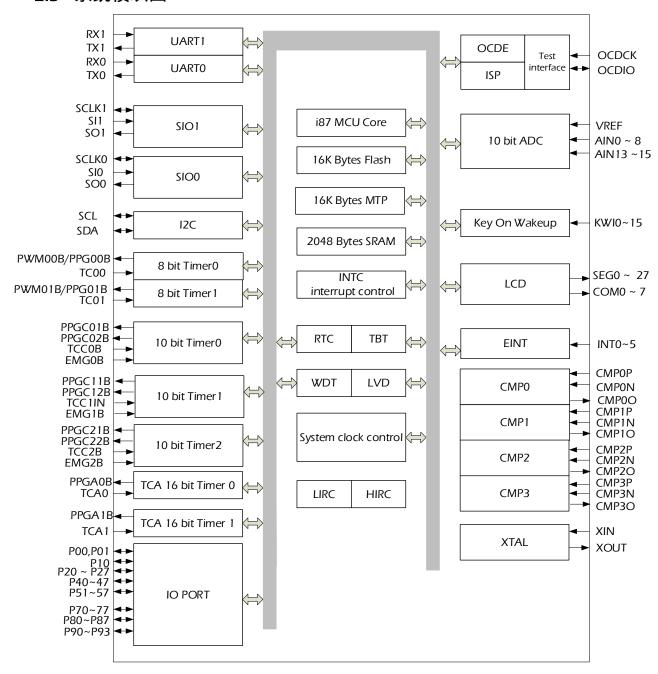

#### 2.3 系统模块图

图 2.1 MQ6825/MQ6815 系统模块图

Page: 17/359 本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

No.: TDDS01-M6825-CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

## 2.4 引脚配置/说明

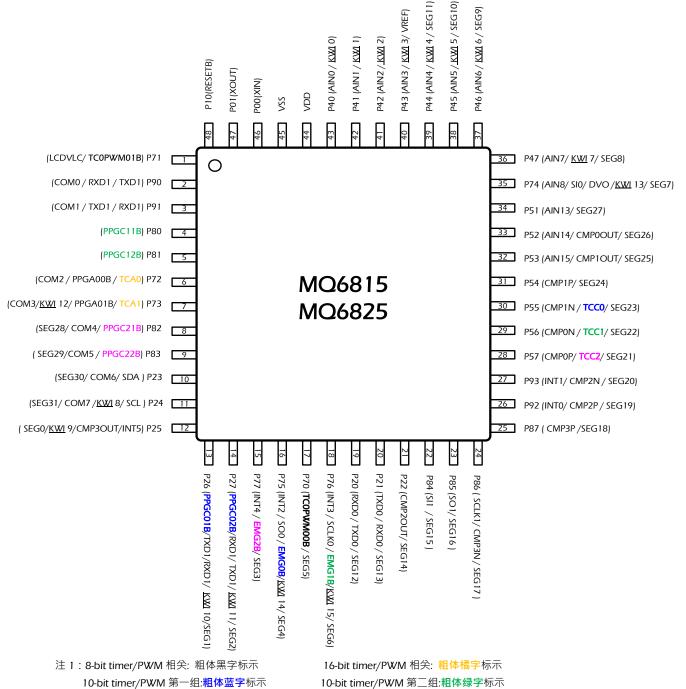

LOFP 48 (7x7) 封装型态引脚配置

产品型号:MQ6825LQ048HALR/MQ6815LQ048HALR

10-bit timer/PWM 第三组: 粗体粉红字标示

注 2:仿真需连接 P40/OCDCK、P41/OCDIO、P10/RESETB、VDD、VSS。客户在系统板上所预留之仿真脚位,不建议增加其它元器 件以免影响仿真特性或功能。

注 3:烧录需连接 P40/OCDCK、P41/OCDIO、P10/RESETB、VDD、VSS。客户在系统板上所预留之烧录脚位,不建议增加其它元器 件以免影响特性或功能

Page: 18/ 359 权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。 品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害 芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

No.: TDDS01-M6825-CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

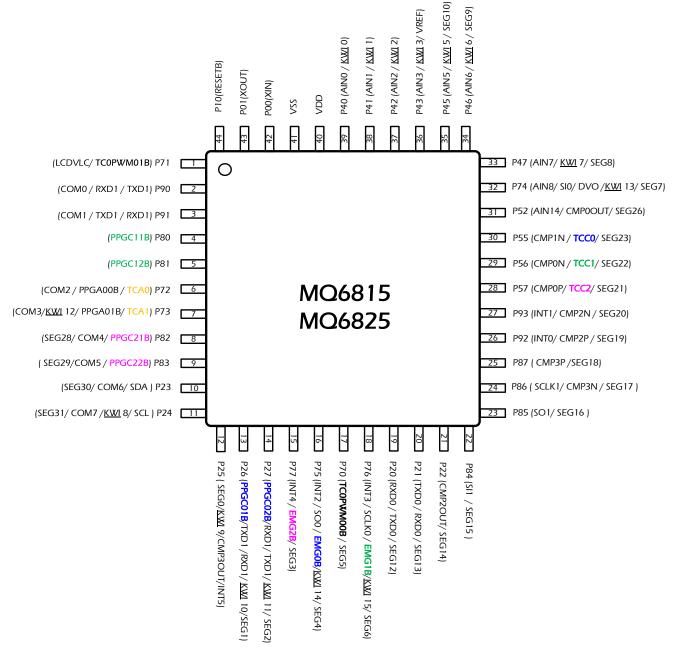

#### LOFP 44 (10x10) 封装型态引脚配置

产品型号:MQ6825LA044HALR/MQ6815LA044HALR

注 1:8-bit timer/PWM 相关: 粗体黑字标示

16-bit timer/PWM 相关: 粗体橘字标示

10-bit timer/PWM 第一组:粗体蓝字标示

10-bit timer/PWM 第二组:粗体绿字标示

10-bit timer/PWM 第三组: 粗体粉红字标示

注 2:仿真需连接 P40/OCDCK、P41/OCDIO、P10/RESETB、VDD、VSS。客户在系统板上所预留之仿真脚位,不建议增加其它元器 件以免影响仿真特性或功能。

注 3:烧录需连接 P40/OCDCK、P41/OCDIO、P10/RESETB、VDD、VSS。客户在系统板上所预留之烧录脚位,不建议增加其它元器 件以免影响特性或功能。

Page: 19/ 359 权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。 品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害 芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

#### iMQ Technology Inc.

No.: TDDS01-M6825 -CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

| <b>48</b> 引脚<br>编号 | <b>44</b> 引脚<br>编号 | 引脚名称与 端口/选择功能                                      | LCD驱动<br>引脚(注 <b>7</b> ) | 输入  | 输出I/O类型                                       | 功能说明                                                                                                                      |

|--------------------|--------------------|----------------------------------------------------|--------------------------|-----|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

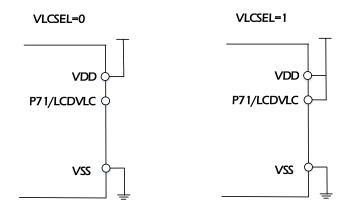

| 1                  |                    | P71/ <b>TC01/PWM01B/PPG0 1B</b> (注4)               | LCDVLC (Note 7)          | I/O | 上拉<br>下拉<br>LCD驱动                             | P71为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>8位定时器/计数器相关引脚TC01/PWM01B/ PPG01B 与P71共享引脚。                                     |

| 2                  |                    | P90/TXD1/RXD1<br>P91/RXD1/TXD1                     | COM0<br>COM1             | I/O | 上拉<br>下拉<br>UART<br>LCD驱动                     | P90与P91为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>通用异步接收/发送(UART)引脚TXD1及RXD1、与LCD驱动引脚COM0及COM1分别与P90及P91共享引脚。                |

| 4<br>5             |                    | P80/ <b>PPGC11B</b><br>P81/ <b>PPGC12B</b><br>(注5) | -                        | I/O | 高驱动电流                                         | P80与P81为具35mA电流驱动之输出端口。<br>10位定时器/计数器TCC1之引脚PPGC11B及 PPGC12B分别与P80及P81共享引脚。                                               |

| 6                  | 6                  | P72/ <b>TCA0/PPGA0B</b><br>(注6)                    | СОМ2                     | I/O | 上拉<br>下拉<br>LCD驱动                             | P72为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 16位定时器/计数器TCA0引脚TCA0/ PPGA0B 及LCD驱动引脚COM2分别与P72共享引脚。                              |

| 7                  | 7                  | P73/TCA1/PPGA1B/KWI12<br>(注1, 注6)                  | СОМЗ                     | I/O | 上拉<br>下拉<br>唤醒输入<br>LCD驱动                     | 73为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 16位定时器/计数器TCA1引脚TCA1/PPGA1B及唤醒输入 KWI12及LCD驱动引脚COM3与P73共享引脚。                        |

| 8                  |                    | · ·                                                | COM4/SEG28<br>COM5/SEG29 | I/O | 上拉<br>下拉<br>LCD驱动                             | P82与P83为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 10位定时器/计数器TCC2之引脚PPGC21B及PPGC22B、与LCD驱动引脚COM4、SEG28及COM5、SEG29分别与P82及P83共享引脚。 |

| 10                 | 10                 | P23/SDA                                            | COM6/SEG30               | I/O | 上拉<br>下拉<br>I <sup>2</sup> C<br>LCD驱动         | P23为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>工业标准串口通讯 (I <sup>2</sup> C) 引腳SDA与LCD驱动引脚COM6、<br>SEG30与P23共享引脚。               |

| 11                 | 11                 | P24/SCL./KWI8<br>(注1)                              | COM7/SEG31               | I/O | 上拉<br>下拉<br>I <sup>2</sup> C<br>唤醒输入<br>LCD驱动 | P24为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>工业标准串口通讯 (I <sup>2</sup> C) 引腳SCL及唤醒输入KWI8与LCD驱动引脚COM7、 SEG31与P24共享引脚。         |

| 12                 | 12                 | P25/INT5/CMP3OUT/KWI9<br>(注1)                      | SEG0                     | I/O | 上拉<br>下拉<br>外部中断<br>比较器输出<br>唤醒输入<br>LCD驱动    | P25为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>外部中断INT5及唤醒输入KWI9、比较器输出CMP3OUT与<br>LCD驱动引脚SEG0与P25共享引脚。                        |

**Page: 20/ 359**本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

#### iMQ Technology Inc.

No.: TDDS01-M6825 -CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

| 13<br>14 | 13<br>14 | P26/ <b>PPGC01B</b> / TXD1/<br>RXD1/ KWI10<br>P27/ <b>PPGC02B</b> / RXD1/<br>TXD1 / KWI11<br>(注1, 注5) | SEG1<br>SEG2   | I/O | 上拉<br>下拉<br>UART<br>唤醒输入<br>LCD驱动        | P26与P27为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 10位定时器/计数器TCC0之引脚PPGC01B及PPGC02B、通用异步接收/发送(UART)引脚TXD1及RXD1、唤醒输入KWI10、KWI11与LCD驱动引脚SEG1、SEG2分别与P26及P27共享引脚。 |

|----------|----------|-------------------------------------------------------------------------------------------------------|----------------|-----|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15       | 15       | P77/INT4/ EMG2B                                                                                       | SEG3           | I/O | 上拉<br>下拉<br>外部中断<br>LCD驱动                | P77为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>外部中断INT4与10位定时器/计数器TCC2之引脚EMG2B与LCD驱动引脚SEG3与P77共享引脚。                                                         |

| 16       | 16       | P75/INT2/<br>SO0/ <b>EMG0B</b> /KWI14<br>(注1)                                                         | SEG4           | I/O | 上拉<br>下拉<br>外部中断<br>SIO<br>唤醒输入<br>LCD驱动 | P75为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>外部中断INT2与串行外围接口(SIO) SOO及10位定时器/计数器TCCO之引脚EMG0B及唤醒输入KWI14及LCD驱动引脚SEG4与P75共享引脚。                               |

| 17       | 17       | P70/ <b>TC00/PW/M00B/PPG0 0B</b> (注4)                                                                 | SEG5           | I/O | 上拉<br>下拉<br>LCD驱动                        | P70为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>8位定时器/计数器相关引脚TC00/PWM00B/PPG01B及LCD驱动引脚SEG5皆与P70共享引脚。                                                        |

| 18       | 18       | P76/SCLK0/<br><b>EMG1B</b> /KWI15<br>(注1)                                                             | SEG6           | I/O | 上拉<br>下拉<br>SIO<br>唤醒输入<br>LCD驱动         | P76为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>串行外围接口(SIO) SCLK与10位定时器/计数器TCC1之引脚<br>EMG1B及唤醒输入KWI15与LCD驱动引脚SEG6皆与P76共享引脚。                                  |

| 19<br>20 | 19<br>20 | P20/RXD0/TXD0<br>P21/TXD0/RXD0                                                                        | SEG12<br>SEG13 | I/O | 上拉<br>下拉<br>UART<br>SIO<br>LCD驱动         | P20与P21为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>通用异步接收/发送 (UART) 引脚 TXD0及RXD0、与串行外围接口 (SIO)SCLK1、SI1与LCD驱动引脚SEG12及SEG13分別与P20及P21共享引脚。                   |

| 21       | 21       | P22/SO1/CMP2OUT                                                                                       | SEG14          | I/O | 上拉<br>下拉<br>SIO<br>比较器输出<br>LCD驱动        | P22为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>串行外围接口(SIO)SO1 比较器输出CMP2OUT及LCD驱动引脚SEG14与P22共享引脚。                                                            |

| 22<br>23 | 22<br>23 | P84/SI1<br>P85/SO1                                                                                    | SEG15<br>SEG16 | I/O | 上拉<br>下拉<br>SIO<br>LCD驱动                 | P84与P85为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>串行外围接口 (SIO) SI1、SO1与LCD驱动引脚SEG15、SEG16皆与P84、P85共享引脚。                                                    |

**Page: 21/ 359**本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

#### iMQ Technology Inc.

No.: TDDS01-M6825 -CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

| 24                   | 24                  | P86/SCLK1/CMP3N                                        | SEG17                            | I/O | 上拉<br>下拉<br>SIO<br>比较器输入<br>LCD驱动          | P86为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>串行外围接口 (SIO) SCLK1、比较器输入CMP3N、与LCD驱动引脚SEG17皆与P86共享引脚。                                                                                                  |

|----------------------|---------------------|--------------------------------------------------------|----------------------------------|-----|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25                   | 25                  | P87/ /CMP3P                                            | SEG18                            | I/O | 上拉<br>下拉<br>比较器输入<br>LCD驱动                 | P87为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>比较器输入CMP3P与LCD驱动引脚SEG18与P87共享引脚。                                                                                                                       |

| 26<br>27             | 26<br>27            | P92/INT0/CMP2P<br>P93/INT1/CMP2N                       | SEG19<br>SEG20                   | 1/0 | 上拉<br>下拉<br>外部中断<br>比较器输入<br>LCD驱动         | P92与P93为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>外部中断 INTO、INT1及比较器输入CMP2P、CMP2N与<br>LCD驱动引脚SEG19、 SEG20分別与P92、P93共享引脚。                                                                             |

| 28<br>29<br>30<br>31 | 28<br>29<br>30<br>- | P57/CMP0P/TCC2 P56/CMP0N/TCC1 P55/CMP1N/TCC0 P54/CMP1P | SEG21<br>SEG22<br>SEG23<br>SEG24 | 1/0 | 上拉<br>下拉<br>比较器输入<br>LCD驱动                 | P57、P56、 P55、P54为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>比较器输入CMPOP、CMPON、CMP1N、CMP1P与LCD驱动引脚SEG21、SEG22、 SEG23、SEG24分别与P57、P56、P55、P54共享引脚。<br>10位定时器/计数器TCC2、TCC1、TCC0之引脚分别与P57、P56、P55、P54共享引脚。 |

| 32<br>33             | - 31                | P53/AIN15/CMP1OUT<br>P52/AIN14/CMP0OUT<br>(注2)         | SEG25<br>SEG26                   | 1/0 | 上拉<br>下拉<br>AD转换输入比<br>较器输出<br>LCD驱动       | P53与P52为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 AD转换输入AIN15、AIN14与比较器输入CMP1OUT、 CMP0OUT与LCD驱动引脚SEG25、SEG26分别与P53、P52共享引脚。                                                                             |

| 34                   | -                   | P51/AIN13<br>(注2)                                      | SEG27                            | I/O | 上拉<br>下拉<br>AD转换输入<br>LCD驱动                | P51为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>AD转换输入AIN13与LCD驱动引脚SEG27与P51共享引脚。                                                                                                                      |

| 35                   | 32                  | P74/AIN8/SI0/DVO/KWI13<br>(注1, 注2, 注8)                 | SEG7                             | 1/0 | 上拉<br>下拉<br>AD转换输入<br>SIO<br>唤醒输入<br>LCD驱动 | P74为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>AD转换输入AIN8与串行外围接口 (SIO)引脚 SIO及DVO及唤醒输入KWI13与LCD驱动引脚SEG7与P74共享引脚。                                                                                       |

| 36                   | 33                  | P47/AIN7/KWI7<br>(注1, 注2)                              | SEG8                             | I/O | 上拉<br>下拉<br>AD转换输入<br>喚醒输入<br>LCD驱动        | P47为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>AD转换输入AIN7、唤醒输入KWI7及LCD驱动引脚SEG8与P47共享引脚。                                                                                                               |

**Page: 22/ 359**本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

#### iMQ Technology Inc.

No.: TDDS01-M6825-CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

| 37<br>38<br>39 | 34<br>35<br>-  | P46/AIN6/KWI6<br>P45/AIN5/KWI5<br>P44/AIN4/KWI4<br>(注1, 注2) | SEG9<br>SEG10<br>SEG11 | 1/0   | 上拉<br>下拉<br>AD转换输入<br>唤醒输入<br>LCD驱动 | P46、P45与P44为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 AD转换输入AIN6、AIN5、AIN4及唤醒输入KWI6、KWI5、KWI4与LCD驱动引脚SEG9、SEG10、SEG11分别与P46、P45与P44共享引脚。 |

|----------------|----------------|-------------------------------------------------------------|------------------------|-------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 40             | 36             | P43/AIN3/KWI3/VREF<br>(注1, 注2)                              | -                      | 1/0   | 上拉<br>下拉<br>AD转换输入<br>唤醒输入          | P43为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>AD转换输入AIN3及唤醒输KWI3及VREF与P43共享引脚。                                                        |

| 41<br>42<br>43 | 37<br>38<br>39 | P42/AIN2/KWI2<br>P41/AIN1/KWI1<br>P40/AIN0/KWI0<br>(注1, 注2) | -                      | 1/0   | 上拉<br>下拉<br>AD转换输入<br>唤醒输入          | P42、P41与P40为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 AD转换输入AIN2、AIN1、AIN0及唤醒输入KWI2、KWI1、KWI0分别与P42、P41与P40共享引脚。                         |

| 44             | 40             | VDD                                                         | -                      | Power |                                     | VDD电源输入                                                                                                                            |

| 45             | 41             | VSS                                                         | -                      | GND   | -                                   | 接地                                                                                                                                 |

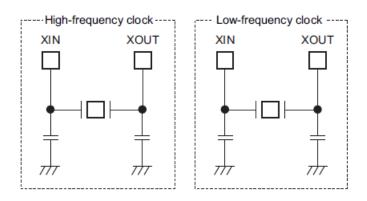

| 46<br>47       | 42<br>43       | P00/XIN<br>P01/XOUT                                         | -                      | 1/0   | 上拉<br>下拉<br>外部晶振连接<br>(高低频)         | P00与P01为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 XIN及XOUT为外部晶体振荡器连接引脚·分别与P00及P01共享引脚。                                                   |

| 48             | 44             | P10/RESETB                                                  | -                      | I/O   | 上拉                                  | P10为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻。<br>复位信号输入RESETB与P10共享引脚·为低电平有效。上电后P10默认是复位功能·请注意必须为高电平后·芯片才能正常工作。芯片正常工作後可以通过程序设定为IO端口。          |

注 1 :KWI0~KWI15 可定义为系统唤醒的输入引脚 其中 KWI0~KWI7 分别和 P40~P47 共享引脚 而 KWI8~KWI15 分别和 P24~P27 与 P73~P76 共享引脚。

注 2: AINO~AIN8 与 AIN13~AIN15 为 10 位 AD 转换器的模拟信号输入引脚。

注 3: PWMOxB (x=0 到 1)的详细说明,请参考 10.5 节"8 位定时器/计数器"。

注 4: PPGCx1B 與 PPGCx2B (x=0 到 2)的详细说明,请参考 10.6 节"10 位定时器/计数器"。

注 5: TCAO 及 PPGAOB 的详细说明,请参考 10.7 节"16 位定时器/计数器"。

注 6: 在线烧录之引脚为 VSS、VDD、P10、P40 与 P41。

注 7: 使用 LCD 功能时,请将 LCD 相关引脚 COM 与 SEGJ设为输入模式;另外 LCD 面板的工作电压请和芯片的 VDD 同电位。

注 8: P74 脚位若作为 AIN 功能(AIN8)·且与其他 AIN 同时使用时·进入 STOP 模式会增加额外功耗;故在 AIN 通道数量足够的状 况下,请尽量避免使用 P74 的 AIN 功能(AIN8)。

#### iMQ Technology Inc.

No.: TDDS01-M6825-CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

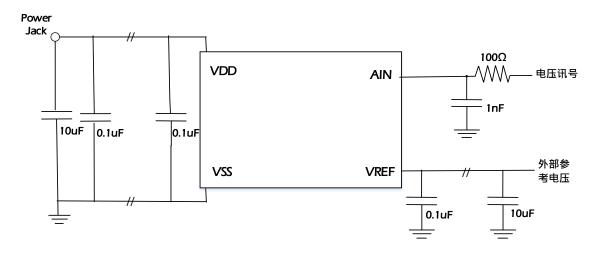

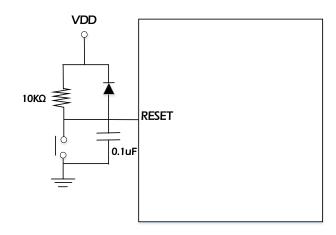

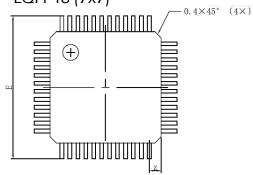

图 2.2 为在使用 MQ6825/MQ6815 时建议的外部参考线路,包含三个部份:

- 1. 在靠近 MCU 端 VDD 加上 0.1uF 的电容,此电容的位置应尽可能地接近 MCU;在靠近 Power Jack 端加上需加上 10uF 并联 0.1uF 的电容。有助于强化产品的抗干扰(EFTB)能力,可以避免电源突波或 杂讯的影响。

- 2. 在使用 ADC 时,请在 AIN 讯号输入脚位串接一个 100ohm,并且接一个 1nF 的电容到地。这是为了 过滤可能的杂讯。

- 3. 为了过滤可能的杂讯,在使用 ADC 并使用外部参考电压时,靠近参考电压端加上 10uF 电容,靠近 MCU 端加 0.1uF 的电容。

图 2.2 MQ6825/MQ6815 外部参考线路

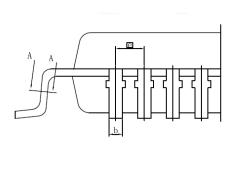

图 2.3 使用 MQ6825/MQ6815 时建议使用外部线路(复位引脚)

Page: 24/ 359 版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。 产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害 汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

#### iMQ Technology Inc.

No.: TDDS01-M6825 -CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

## 3. 电气特性

## 3.1 极限参数

单片机操作时切勿超过以下任一项极限参数值。即使仅是极短时间,也可能造成单片机损坏或性能衰退, 严重者可能导致起火或爆炸、造成伤害。因此,请确保采用本单片机 MQ6825/MQ6815 设计开发之产品 或系统不超过以下极限参数值。

$(V_{SS} = 0V)$

| 参数        | 符号                | 引脚                                                                  | 极限参数                                                                                                                  | 单位    |

|-----------|-------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------|

| 工作电压范围    | $V_{DD}$          |                                                                     | -0.3 to 6.0                                                                                                           | V     |

| 输入电压范围    | $V_{IN}$          | 全部 I/O 引脚                                                           | $-0.3$ to $V_{DD} + 0.3$                                                                                              | V     |

| 输出电压范围    | V <sub>OUT</sub>  | 全部 I/O 引脚                                                           | $-0.3$ to $V_{DD} + 0.3$                                                                                              | V     |

|           | I <sub>OUT1</sub> | Port0、P10、Port2、Port5、P71、<br>P74~P77、 P84~P87、Port9(IOL:輸出拉电<br>流) | 15                                                                                                                    |       |

| 输出电流 (单脚) | I <sub>OUT2</sub> | Port4、P70、P72、P73、P82、P83 (IOL:输<br>出拉电流)                           | -0.3 to 6.0<br>-0.3 to V <sub>DD</sub> + 0.3<br>-0.3 to V <sub>DD</sub> + 0.3                                         | mA    |

|           | I <sub>OUT3</sub> | P80/P81 (IOL:输出拉电流)                                                 | 60                                                                                                                    |       |

|           | I <sub>OUT4</sub> | 全部 I/O 引脚,不包含 P80、P81 (IOH:输入<br>灌电流)                               | -0.3 to 6.0  -0.3 to V <sub>DD</sub> + 0.3  -0.3 to V <sub>DD</sub> + 0.3  15  40  60  -15  -30  120  -60  -40 to 125 |       |

|           | I <sub>OUT5</sub> | P80/P81(IOH:输入灌电流)                                                  | -0.3 to 6.0  -0.3 to V <sub>DD</sub> + 0.3  -0.3 to V <sub>DD</sub> + 0.3  15  40  60  -15  -30  120  -60  -40 to 125 |       |

| 检出中海 (首和) | $\Sigma I_{OUT1}$ | 全部 I/O 引脚(IOL:输出拉电流)                                                | 120                                                                                                                   | mΑ    |

| 输出电流 (总和) | $\Sigma I_{OUT2}$ | 全部 I/O 引脚 (IOH:輸入灌电流)                                               | -0.3 to 6.0  -0.3 to V <sub>DD</sub> + 0.3  -0.3 to V <sub>DD</sub> + 0.3  15  40  60  -15  -30  120  -60  -40 to 125 | 111/1 |

| 储存温度范围    | $T_{STG}$         |                                                                     | -40 to 125                                                                                                            | °C    |

| 工作温度范围    | $T_{OPR}$         |                                                                     | -40 to 85                                                                                                             | °C    |

iMQ Technology Inc.

No.: TDDS01-M6825 -CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

## 3.2 工作条件

$(V_{SS} = 0V, T_{OPR} = -40 \text{ to } 85^{\circ}C)$

|   | 参数           | 符号                | 引脚 / 条件                                 | 测试条件                                                      | 最小                    | 标准     | 最大                    | 单位      |

|---|--------------|-------------------|-----------------------------------------|-----------------------------------------------------------|-----------------------|--------|-----------------------|---------|

|   | T./c.d.E.    |                   | 未使用 LCD                                 |                                                           | 2.0                   | -      | 5.5                   | V       |

|   | 工作电压         | $V_{DD}$          | 使用 LCD                                  | <u> </u>                                                  | 2.6                   | -      | 5.5                   | V       |

| 4 | 輸入高电压        | V <sub>IH</sub>   | 全部 I/O 引脚                               | ← 所有工作模式  ← 所有工作模式  ← の の の の の の の の の の の の の の の の の の | V <sub>DD</sub> x0.75 | -      | $V_{DD}$              | V       |

| 4 | 輸入低电压        | VIL               | 全部 I/O 引脚                               |                                                           | 0                     | -      | V <sub>DD</sub> x0.25 | V       |

|   | 外部高速时钟       | fc                | XIN, XOUT                               | )/ 20 to 5 5)/                                            | 1.0                   | -      | 16                    | MHz     |

|   | 外部低速时钟       | $f_{CL}$          | XIN, XOUT (32.768KHz) (注)               | $V_{DD} = 2.0 \text{ to } 5.5V$                           | 30.0                  | 32.768 | 34.0                  | KHz     |

|   |              |                   | FSCTRL <fosccks>="00"-8MHz</fosccks>    | $V_{DD} = 2.0 \text{ to } 5.5 \text{V}$                   | -1%                   | 8.00   | +1%                   | MHz     |

| 时 |              |                   | FSCTRL <fosccks>="01" - 16MHz</fosccks> | 25°C                                                      | -1%                   | 16.00  | +1%                   | IVIITIZ |

| 钟 | <br>  内部高速时钟 | £                 | FSCTRL <fosccks>="00"- 8MHz</fosccks>   | $V_{DD} = 2.0 \text{ to } 5.5 \text{V}$                   | -2%                   | 8.00   | +2%                   | MHz     |

| 频 | 内即回还的铁       | f <sub>OSC</sub>  | FSCTRL <fosccks>="01" - 16MHz</fosccks> | 0°C ~85°C                                                 | -2%                   | 16.00  | +2%                   | IVIIIZ  |

| 率 |              |                   | FSCTRL <fosccks>="00"- 8MHz</fosccks>   | $V_{DD} = 2.0 \text{ to } 5.5 \text{V}$                   | -3%                   | 8.00   | +3%                   | N / L 1 |

|   |              |                   | FSCTRL <fosccks>="01" - 16MHz</fosccks> | -40°C ~85°C                                               | -3%                   | 16.00  | +3%                   | MHz     |

|   | 内部低速时钟       | f <sub>OSCL</sub> | 24KHz                                   | $V_{DD} = 2.0 \text{ to } 5.5 \text{V}$                   | -                     | 24     | -                     | KHz     |

|   | 系统齿轮时钟       | $f_{CGCK}$        | 设定 CGCR <fcgcksel></fcgcksel>           | $V_{DD} = 2.0 \text{ to } 5.5 \text{V}$                   | 0.125                 | 1      | 16                    | MHz     |

注:RTC 在 Slow1 操作下, 搭配外部 32.768K Crystal ,会有±50ppm 误差(Topr=25℃), 请参考附录 D 的使用注意事项

**Page: 26/ 359**本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

#### iMQ Technology Inc.

No.: TDDS01-M6825 -CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

## 3.3 直流(DC)电气特性

$(V_{SS} = 0V, T_{OPR} = -40 \text{ to } 85^{\circ}C)$

| 参数   | 符号               | 引脚                                                       | 测试条件                        | 最小   | 标准   | 最大   | 单位 |

|------|------------------|----------------------------------------------------------|-----------------------------|------|------|------|----|

| 滞后电压 | V <sub>HS</sub>  | 全部 I/O 引脚                                                |                             | -    | 0.9  | -    | V  |

| 输入电流 | I <sub>IN</sub>  | 全部 I/O 引脚                                                | $V_{DD} = 5.5V$             | -    | -    | ±2   | μА |

| 上拉电阻 | R <sub>UP</sub>  | 全部 I/O 引脚、P80/P81 除外、<br>P10 关闭 RESETB 功能                | V <sub>IN</sub> = 5.5V / 0V | 30   | 50   | 70   | ΚΩ |

| 工拉由四 | Б                | 全部 I/O 引脚、P10/P80/P81                                    | $V_{DD}/V_{IN} = 5.5V$      | 27.5 | 55   | 82.5 | ΚΩ |

| 下拉电阻 | $R_{DN}$         | 除外                                                       | $V_{DD}/V_{IN} = 2.0V$      | 120  | 200  | 300  | ΚΩ |

|      | I <sub>OL1</sub> | 全部 I/O 引脚,<br>P40~P47,P70,P72,P73,P80,<br>P81,P82,P83 除外 | V <sub>DD</sub> = 5.5V      | 3.0  | 5.0  | -    | mA |

| 输出电流 | I <sub>OL2</sub> | P40~P47,P70,P72,P73,P82,<br>P83                          | $V_{OL} = 0.55V$            | 9.0  | 15.0 | -    | mA |

|      | I <sub>OL3</sub> | P80/P81                                                  |                             | 21.0 | 35.0 | -    | mA |

|      | I <sub>OH1</sub> | 全部 I/O 引脚、P80/P81 除外                                     | $V_{DD} = 5.5V$             | 3.0  | 5.0  | -    | mA |

|      | I <sub>OH2</sub> | P80/P81                                                  | $V_{OH} = 4.95V$            | 9.0  | 15.0 | -    | mA |

注:I/O 最大操作速度为 500KHz。

注:标准值条件为 T<sub>OPR</sub> = 25°C、V<sub>DD</sub> = 5.5V。

$(V_{SS} = 0V, T_{OPR} = 25^{\circ}C)$

| 参数                   | 符号              | 测试条件                                                                                                                                                                 | 最小 | 标准  | 最大  | 单位 |

|----------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-----|----|

| 工作电流 - 普通 1,2 模式     |                 | $V_{DD} = 5.5V$ $f_{cgck} = \underline{16.0 \text{ MHz}}$ $f_{S} = 24 \text{ KHz}$ $V_{DD} = 5.5V$ $f_{cgck} = \underline{8.0 \text{ MHz}}$ $f_{S} = 24 \text{ KHz}$ | -  | 4.0 | 4.8 |    |

| 工作电流 - 空闲 0, 1, 2 模式 |                 |                                                                                                                                                                      | -  | 2.4 | 3.0 | A  |

| 工作电流 - 普通 1,2 模式     |                 |                                                                                                                                                                      | -  | 3.2 | 4.0 | mA |

| 工作电流 - 空闲 0, 1, 2 模式 |                 |                                                                                                                                                                      | -  | 2.2 | 2.6 |    |

| 待机电流 - 低速 1 模式       | l <sub>DD</sub> |                                                                                                                                                                      | -  | 65  | 90  |    |

| 待机电流 - 睡眠 1 模式       |                 | $V_{DD} = 3.0V$<br>$f_S = 24 \text{ KHz}$                                                                                                                            | -  | 40  | 60  | 1  |

| 待机电流 - 睡眠 0 模式       |                 |                                                                                                                                                                      | _  | 40  | 60  | μΑ |

| 待机电流 - 停止模式          |                 | V <sub>DD</sub> = 5.5V                                                                                                                                               | _  | 15  | 25  |    |

注 1:标准值条件为 T<sub>OPR</sub> = 25℃、V<sub>DD</sub> = 5.0V。/除非特别指定/

注 2: 低速 2 模式下之工作电流值与空闲 0, 1, 2 模式相同。

**Page: 27 / 359**本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

#### iMQ Technology Inc.

No.: TDDS01-M6825-CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

$(V_{SS} = 0V, T_{OPR} = -40 \text{ to } 55^{\circ}C)$

| 参数                   | 符号              | 测试条件                                                                         | 最小 | 标准  | 最大  | 单位 |

|----------------------|-----------------|------------------------------------------------------------------------------|----|-----|-----|----|

| 工作电流 - 普通 1,2 模式     |                 | $V_{DD} = 5.5V$ $f_{cgck} = \frac{16.0 \text{ MHz}}{f_{S} = 24 \text{ KHz}}$ |    | 4.0 | 5.0 |    |

| 工作电流 - 空闲 0, 1, 2 模式 |                 |                                                                              | -  | 2.4 | 3.2 |    |

| 工作电流 - 普通 1,2 模式     |                 | $V_{DD} = 5.5V$                                                              | -  | 3.2 | 4.2 | mA |

| 工作电流 - 空闲 0, 1, 2 模式 | ,               | $f_{cgck} = 8.0 \text{ MHz}$ $f_{S} = 24 \text{ KHz}$                        | -  | 2.2 | 2.8 |    |

| 待机电流 - 低速 1 模式       | I <sub>DD</sub> |                                                                              | -  | 65  | 180 |    |

| 待机电流 - 睡眠 1 模式       |                 | $V_{DD} = 3.0V$<br>$f_S = 24 \text{ KHz}$                                    | -  | 40  | 120 | 1  |

| 待机电流 - 睡眠 0 模式       |                 |                                                                              | _  | 40  | 120 | μΑ |

| 待机电流 - 停止模式          |                 | V <sub>DD</sub> = 5.5V                                                       | -  | 15  | 50  |    |

注 1:标准值条件为 Tope = 25℃、VDD = 5.0V。(除非特别指定)

注 2: 低速 2 模式下之工作电流值与空闲 0, 1, 2 模式相同。

$(V_{SS} = 0V, T_{OPR} = -40 \text{ to } 85^{\circ}C)$

|                      | 1               |                                                                             | 1 4 22 | OV, IOPR | 10 10 | 05 0 |

|----------------------|-----------------|-----------------------------------------------------------------------------|--------|----------|-------|------|

| 参数                   | 符号              | 测试条件                                                                        | 最小     | 标准       | 最大    | 单位   |

| 工作电流 - 普通 1,2 模式     |                 | $V_{DD} = 5.5V$                                                             | _      | 4.0      | 5.2   |      |

| 工作电流 - 空闲 0, 1, 2 模式 |                 | $f_{cgck} = \frac{16.0 \text{ MHz}}{f_S = 24 \text{ KHz}}$ $V_{DD} = 5.5 V$ |        | 2.4      | 3.4   | A    |

| 工作电流 - 普通 1, 2 模式    |                 |                                                                             | -      | 3.2      | 4.4   | mA   |

| 工作电流 - 空闲 0, 1, 2 模式 |                 | $f_{cgck} = 8.0 \text{ MHz}$ $f_{S} = 24 \text{ KHz}$                       | -      | 2.2      | 3.0   |      |

| 待机电流 - 低速 1 模式       | l <sub>DD</sub> |                                                                             | -      | 65       | 300   |      |

| 待机电流 - 睡眠 1 模式       |                 | $V_{DD} = 3.0V$<br>$f_S = 24 \text{ KHz}$                                   | -      | 40       | 260   | 0    |

| 待机电流 - 睡眠 0 模式       |                 | -                                                                           | -      | 40       | 260   | μА   |

| 待机电流 - 停止模式          |                 | V <sub>DD</sub> = 5.5V                                                      | -      | 15       | 190   |      |

注 1:标准值条件为  $T_{OPR}$  = 25°C、 $V_{DD}$  = 5.0V  $\circ$  /除非特别指定/

注 2: 低速 2 模式下之工作电流值与空闲 0, 1, 2 模式相同。

No.: TDDS01-M6825-CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

## 3.4 AD 转换电气特性

$(V_{SS} = 0V, 2.7V \le V_{DD} \le 5.5V, T_{OPR} = 25^{\circ}C)$

|                                 | (V33 0V, 2.7 V = VDD= 3.5 V, 10PR 25 C) |                            |          |      |             |     |

|---------------------------------|-----------------------------------------|----------------------------|----------|------|-------------|-----|

| 参数                              | 符号                                      | 测试条件                       | 最小       | 标准   | 最大          | 单位  |

| 模拟信号参考电压                        | $V_{REF}$                               |                            |          |      | $V_{DD}$    | V   |

| Analog Reference Voltage        | V REF                                   | _                          |          |      | <b>V</b> DD | V   |

| 模拟信号输入电压                        | V <sub>AIN</sub>                        | _                          | $V_{ss}$ | _    | $V_{DD}$    | V   |

| Analog input voltage range      | VAIN                                    |                            | A 22     |      | <b>V</b> DD | V   |

| 转换时间                            |                                         | fcgck = 2MHz               |          | 16.0 | _           | 115 |

| Conversion Time                 |                                         | ADCCR2 <ack> = "000"</ack> |          | 10.0 | _           | μς  |

| 微分非线性误差 (DNL)                   |                                         | _                          |          |      | ±2.0        | LSB |

| Differential Nonlinearity Error |                                         | _                          |          |      | ±2.0        | טכ  |

| 积分非线性误差 (INL)                   |                                         | _                          |          |      | ±2.0        | LSB |

| Integral Nonlinearity Error     |                                         |                            |          |      | ±2.0        | LJD |

| 零点误差                            |                                         | _                          |          |      | ±2.0        | LSB |

| Zero Point Error                |                                         | _                          |          |      | ±2.0        | LJD |

| 全刻度误差                           |                                         | _                          |          |      | ±2.0        | LSB |

| Full Scale Error                |                                         | _                          |          |      | ±∠.U        | LJD |

| 总误差                             |                                         | _                          | _        | _    | ±2.0        | LSB |

| Total Error                     |                                         | _                          |          |      | ∸∠.∪        | כטט |

$(V_{SS} = 0V, 2.0V \le V_{DD} < 2.7V, T_{OPR} = 25^{\circ}C)$

| 参数                              | 符号               | 测试条件                       | 最小       | 标准   | 最大          | 单位  |

|---------------------------------|------------------|----------------------------|----------|------|-------------|-----|

| 模拟信号参考电压                        | $V_{REF}$        | _                          | _        | _    | $V_{DD}$    | V   |

| Analog Reference Voltage        | V REF            |                            |          | _    | <b>∨</b> DD | V   |

| 模拟信号输入电压                        | V <sub>AIN</sub> | _                          | $V_{ss}$ | _    | $V_{DD}$    | V   |

| Analog input voltage range      | VAIN             |                            | A 22     |      | טט ע        | V   |

| 转换时间                            |                  | fcgck = 2MHz               | _        | 32.0 | _           | μς  |

| Conversion Time                 |                  | ADCCR2 <ack> = "001"</ack> |          | 52.0 |             | μ3  |

| 微分非线性误差 (DNL)                   |                  | _                          | _        | _    | ±4.0        | LSB |

| Differential Nonlinearity Error |                  |                            |          |      | _ 1.0       | LJD |

| 积分非线性误差 (INL)                   |                  | _                          | _        | _    | ±4.0        | LSB |

| Integral Nonlinearity Error     |                  |                            |          |      | _ 1.0       | LJD |

| 零点误差                            |                  | _                          | _        |      | ±4.0        | LSB |

| Zero Point Error                |                  |                            |          |      | ± 1.0       | LJD |

| 全刻度误差                           |                  | _                          | _        | _    | ±4.0        | LSB |

| Full Scale Error                |                  |                            |          |      | 1.0         | LJD |

| 总误差                             |                  | _                          | _        |      | ±4.0        | LSB |

| Total Error                     |                  |                            |          |      | - 1.0       | ככב |

注 1: 总误差包含量化误差以外的所有误差,其定义为距离理想 AD 转换曲线的最大偏差值。

注 2:AIN 引脚的电压输入范围应在 V<sub>REF</sub>至 V<sub>SS</sub> 之间。如在此范围之外·AD 转换值将为不确定值·且将影响其他 AD 通道之转换值。

**Page: 29/ 359**本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

No.: TDDS01-M6825-CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

## 3.5 Flash 电气特性

$(V_{SS} = 0V, 2.0V \le V_{DD} \le 5.5V, T_{OPR} = -40 \text{ to } 85^{\circ}\text{C})$

| 参数              | 测试条件              | 最小 | 标准 | 最大      | 单位 |

|-----------------|-------------------|----|----|---------|----|

| Flash 存储器保证烧写次数 |                   | 1  | -  | 100,000 | 次  |

| Flash 存储器烧写时间   |                   | _  | _  | 40      | μs |

|                 | 整颗擦除 chip erase   | 1  | -  | 40      |    |

| Flash 存储器擦除时间   | 区块擦除 sector erase | _  | _  | Г       | ms |

|                 | (1 区块 = 128 字节)   |    |    |         |    |

**Page:** 30 / 359 本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

No.: TDDS01-M6825-CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

## 3.6 MTP 电气特性

$(V_{SS} = 0V, 2.0V \le V_{DD} \le 5.5V, T_{OPR} = -40 \text{ to } 85^{\circ}C)$

| 参数            | 测试条件              | 最小 | 标准 | 最大      | 单位 |

|---------------|-------------------|----|----|---------|----|

| MTP 存储器保证烧写次数 |                   | _  | _  | 100,000 | 次  |

| MTP 存储器烧写时间   |                   | _  | -  | 40      | μs |

|               | 整颗擦除 chip erase   | _  | _  | 40      |    |

| MTP 存储器擦除时间   | 区块擦除 sector erase | _  | _  | 5       | ms |

|               | (1 区块 = 128 字节)   | -  |    | )       |    |

iMQ Technology Inc.

No.: TDDS01-M6825-CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

## 3.7 LCD 电气特性

$(V_{SS} = 0V, T_{OPR} = 25^{\circ}C)$

| 参数         | 符号              | 测试条件                                | 最小   | 标准   | 最大   | 单位 |

|------------|-----------------|-------------------------------------|------|------|------|----|

| LCD 工作电压   | V <sub>DD</sub> |                                     | 2.6  | _    | 5.5  | V  |

| LCD 偏压输出 1 |                 | 1/4 偏压型 LCD, V <sub>DD</sub> = 5.0V | 3.19 | 3.75 | 4.31 | V  |

|            | V <sub>L1</sub> | 1/3 偏压型 LCD, V <sub>DD</sub> = 5.0V | 2.83 | 3.33 | 3.83 | V  |

|            |                 | 1/2 偏压型 LCD, V <sub>DD</sub> = 5.0V | 2.12 | 2.50 | 2.88 | V  |

| LCD 恒压检U.3 | .,              | 1/4 偏压型 LCD, V <sub>DD</sub> = 5.0V | 2.12 | 2.50 | 2.88 | V  |

| LCD 偏压输出 2 | $V_{L2}$        | 1/3 偏压型 LCD, V <sub>DD</sub> = 5.0V | 1.42 | 1.67 | 1.92 | V  |

| LCD 偏压输出 3 | V <sub>L3</sub> | 1/4 偏压型 LCD, V <sub>DD</sub> = 5.0V | 1.06 | 1.25 | 1.44 | V  |

**Page: 32/ 359**本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

No.: TDDS01-M6825-CN Name: MQ6825/MQ6815 中文产品规格书 Version: V1.9

## 3.8 比较器电气特性

$(T_{OPR} = -40 \text{ to } 85^{\circ}\text{C})$

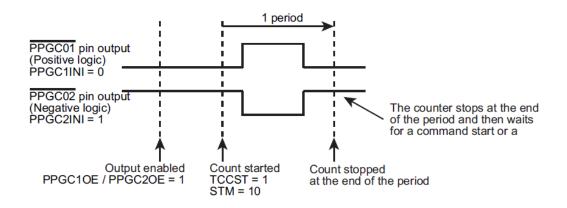

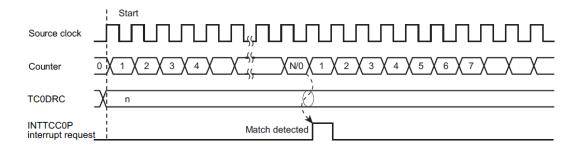

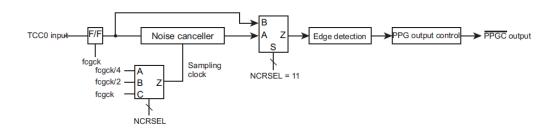

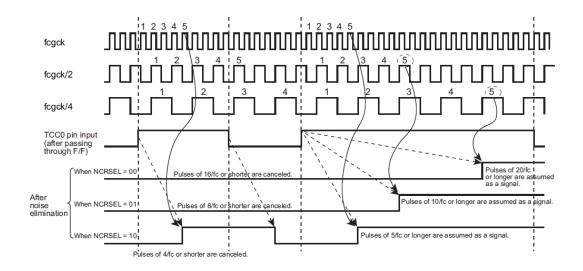

| 参数      | 符号               | 测试条件                                  | 最小  | 标准 | 最大       | 单位 |