## 24V 3A 高效同步降压转换器

Check for Samples: LGS5124

## 特性

■ 宽输入电压范围: 4.5V 至 24V

■ 输出电压范围: 0.8V-19V

——提供可调的输出电压选项

■ 工作结温范围: -40°C - +125°C

■ 提供固定 500KHz 的开关频率

■ 3A 最大连续输出电流

■ 高达 95%的系统转换效率

■ 逐周期限流保护

■ 安全、可靠运行特性

--内部软启动

——过热和过流保护

--输出短路保护

■ 超小型方案尺寸

--小型 SOT23-6 封装

■ 在整个负载范围内具有高效率和低功率耗散

## 订购信息

| 器件型号    | 封装      | 封装尺寸         |

|---------|---------|--------------|

| LGS5124 | SOT23-6 | 3.0mmx 3.0mm |

### 说明

LGS5124 是一个宽输入电压范围、高转换效率的同步降压转换器。LGS5124 提供高达 3A 的负载电流能力,输出电压在宽范围内可调。内部集成的峰值电流控制模式允许外部电路使用小型器件(包括陶瓷电容和小型封装电感),同时低输出电压纹波的特点使得 LGS5124 在高精度、低噪声的使用中发挥重要作用。内部集成的开关 MOSFET、环路补偿以及软启动,极大减少了外部器件的数量,可以实现小尺寸方案设计。LGS5124 具备极快的负载瞬态响应和极高的系统转换效率使其成为多种工业级和消费级应用的理想选择。

### 应用

- 12V、18V 分布式电源总线

- 工业级

- ——视频监控和安全系统

- ——用电器

- 消费级

- ——数字电视和液晶显示器

- ——数字机顶盒

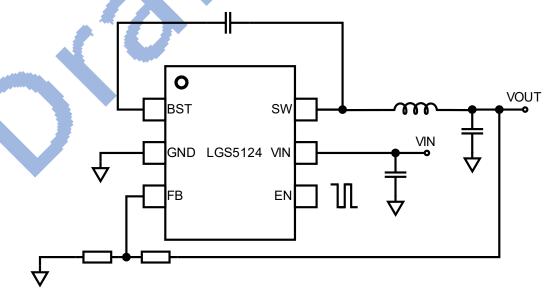

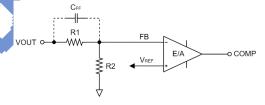

图 1 典型应用拓扑

版权 ©2022-present,棱晶半导体(南京)有限公司

# 历史修订记录

注: 以前版本的页码可能与当前版本页码不同

| Changes from Rev.A V0.1 Aug.2022 to V 0.2 Nov.2022 | 页码  |

|----------------------------------------------------|-----|

| 更新了 EC Table 的数据和推荐应用图以及 PCB Layout 参考             | ALL |

| Changes from Rev.A V0.2 Nov.2022 to V 0.3 Nov.2022 | 页码  |

| 更新了芯片定义和特性描述                                       | ALL |

● 当前文档为修订版 Rev A V0.3,本手册相关参数仅对本版本相关指标和描述承认。

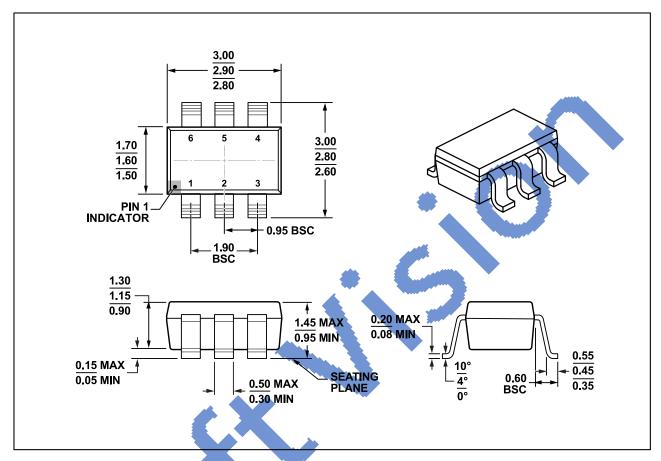

# 封装与引脚排列

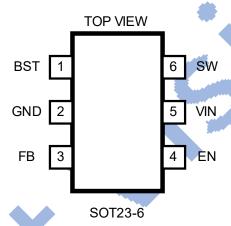

图 2 SOT23-6 Package

#### PACKAGE REFERENCE

图 3 PACKAGE REFERENCE TOP VIEW

# 引脚功能

| 引脚编号 | 引脚名称 | 说明                                                        |

|------|------|-----------------------------------------------------------|

| 1    | BST  | 自举电路引脚。把高侧 MOSFET 的 Gate 端电压升高,需要在该引脚和 SW 引脚之间连接 0.1μF    |

| 1    | DST  | 电容器使用。                                                    |

| 2    | GND  | 功率地引脚。                                                    |

|      | CD.  | 反馈输入引脚。通过外部电阻分压,将输出端的电压波动反馈回 IC,同时通过电阻分压比设置               |

| 3    | FB   | 输出电压值。                                                    |

| 4    | EN   | 输出使能引脚。置高使能输出;置低关闭输出。                                     |

| 5    | VIN  | 电源输入引脚。在该引脚和 GND 引脚之间连接 $10\mu$ F 或更大的旁路电容进行滤波 $^{(1)}$ 。 |

| 6    | SW   | 转换器开关节点。外部连接功率电感。                                         |

<sup>(1)</sup> 注意滤波电容的滤波半径,方便起见,尽量将电容靠近芯片放置。

版权 ©2022-present,棱晶半导体(南京)有限公司

# 绝对额定最大值 (1)

温度范围: -40°C---+125°C (除非另有说明)

| 参数                                        | 最小值   | 最大值   | 单位 |

|-------------------------------------------|-------|-------|----|

| VIN、EN、SW 至 GND 电压                        | - 0.3 | 35    |    |

| BST 至 SW 电压                               | - 0.3 | 6     | V  |

| FB 至 GND 电压                               | - 0.3 | 6     |    |

| 储存温度(Storage temperature)T <sub>stg</sub> | - 65  | + 150 | S  |

| 结温(Junction Temperature)T」                | - 40  | +125  |    |

<sup>(1)</sup> 如果器件工作条件超过上述"绝对最大值",可能引起器件永久性损坏。这仅是极限参数,不建议器件在极限值或超过极限值的条件下工作, 器件长时间工作在极限条件下可能会影响其可靠性。

## ESD 等级

|                  |        |                            | VALUE | UNIT |

|------------------|--------|----------------------------|-------|------|

| V                | 静电放电测试 | Human-body model (HBM)     | ±2000 | V    |

| V <sub>ESD</sub> | 静电放电测风 | Charged-device model (CDM) | ±1000 | V    |

ESD(静电放电)敏感器件。

带电器件和电路板可能会在没有察觉的情况下放电。尽管本产品具有专利或专有保护电路,但在遇到高能量 ESD 时,器件可能会损坏。因此,应当采取适当的 ESD 防范措施,以避免器件性能下降或功能丧失。

# 推荐工作条件 (1)

| 输入电压 | VIN 至 GND 电压     | 4.5  | 24    |    |

|------|------------------|------|-------|----|

| 柳八七正 | EN 至 GND 电压      | 2    | 24    | V  |

| 输出电压 | V <sub>OUT</sub> | 0.8  | 19    |    |

| 输出电流 | louт             | 0    | 3     | Α  |

| 结温   | T <sub>J</sub>   | - 40 | + 125 | °C |

<sup>(1)</sup> 推荐工作条件表示芯片在何种情况下可以正常工作,但不代表具体参数性能,详细请参考后文的技术规格。

版权 ©2022-present,棱晶半导体(南京)有限公司

# 技术规格

如无特殊说明,V<sub>IN</sub>=12V,V<sub>OUT</sub>=5V,TA=25°C.

|                    | 参数                                     | 测试条件                   | 最小值 | 典型值 | 最大值 | 单位  |  |  |

|--------------------|----------------------------------------|------------------------|-----|-----|-----|-----|--|--|

| 输入特性(V             | IN PIN)                                |                        |     |     |     |     |  |  |

| $V_{IN_{R}}$       | 最小输入电压(rising)                         | 上升阈值                   |     | 4.5 |     | ٧   |  |  |

| $V_{IN_{F}}$       | 最小输入电压(falling)                        | 下降阈值                   |     | 4   |     | ٧   |  |  |

| $V_{IN\_MAX}$      | 最大输入电压                                 |                        |     | 24  |     | ٧   |  |  |

| I <sub>SD</sub>    | 关机电流                                   | EN 置低                  |     |     | 1   | μΑ  |  |  |

| 使能特性(E             | N PIN)                                 |                        |     |     |     |     |  |  |

| $V_{\text{EN}\_R}$ | EN 上升阈值                                | T」= 25°C               |     | 1.5 |     | ٧   |  |  |

| $V_{EN_{F}}$       | EN 下降阈值                                |                        |     | 0.8 |     | ٧   |  |  |

| 电流特性(C             | URRENT LIMIT)                          |                        |     |     |     |     |  |  |

| I <sub>sc_Hs</sub> | 高侧 MOSFET 电流限制                         |                        |     | 3.2 |     | Α   |  |  |

| MOS 管特性            | (MOSFETS)                              |                        |     |     |     |     |  |  |

| $R_{dson\_HS}$     | 高侧 MOS 管导通电阻                           |                        |     | 78  |     | mΩ  |  |  |

| $R_{dson\_LS}$     | 低侧 MOS 管导通电阻                           |                        |     | 87  |     | mΩ  |  |  |

| 软启动过程              |                                        |                        |     |     |     |     |  |  |

| Tss                | 第一次 SW 脉冲到 VouT-good (1)               | V <sub>IN</sub> > 4.5V |     | 0.5 |     | ms  |  |  |

| 反馈回路               |                                        |                        |     |     |     |     |  |  |

| $V_{FB}$           | 反馈电压                                   |                        |     | 0.8 |     | ٧   |  |  |

| 开关特性               |                                        |                        |     |     |     |     |  |  |

| FSW                | 开关频率                                   | <b>A</b>               |     | 500 |     | KHz |  |  |

| 系统特性               |                                        |                        |     |     |     |     |  |  |

| D <sub>MAX</sub>   | 最大开关占空比                                |                        |     | 93  |     | %   |  |  |

| 热特性                |                                        |                        |     |     |     |     |  |  |

| TSD                | 热关机(1)                                 |                        |     | 150 |     | °C  |  |  |

| TSD_H              | 热关机的迟滞(1)                              |                        |     | 25  |     | °C  |  |  |

| (1) Guarante       | eed by characterization or design, not | production tested      |     |     |     |     |  |  |

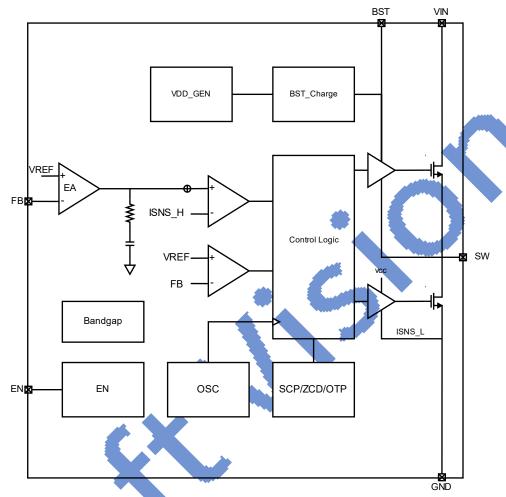

# 功能框图

图 4 内部功能框图

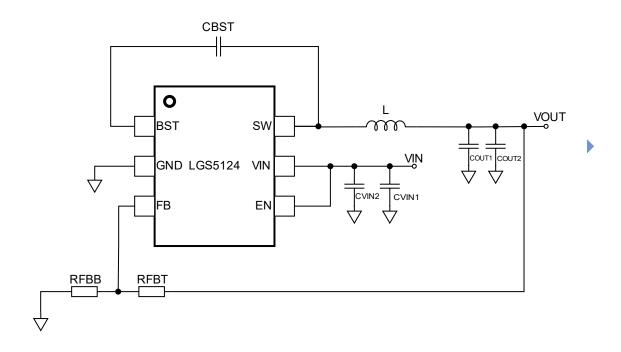

## 典型应用电路

图 5 LGS5124 典型应用拓扑

表 5 LGS5124 外部器件取值推荐

| VOUT(V) | L (µH) | C <sub>OUT1/2</sub> | C <sub>VIN1/2</sub> (1) | R <sub>FBB</sub> (Ω) <sup>(3)</sup> | $R_{FBT}(\Omega)$ | C <sub>BST</sub> (2) |

|---------|--------|---------------------|-------------------------|-------------------------------------|-------------------|----------------------|

| 3.3     | 4.7    | 22μF×2              | 22µF+100nF              | 10.7K                               | 33K               | 100nF                |

| 5       | 10     | 22μF×2              | 22µF+100nF              | 10.7K                               | 56K               | 100nF                |

| 12      | 22     | 22µF×2              | 22µF+100nF              | 10.7K                               | 150K              | 100nF                |

- (1) 输入电容推荐使用 X7R 或 X5R 的陶瓷电容,并尽量贴近 IC 放置,详见后文关于输入电容推荐的描述。

- (2) BST 至 SW 的电容请选择耐压高于 10V 的陶瓷电容,并尽量贴近 IC 引脚放置。

- (3) 当前反馈网络电阻分压比仅为参考值,为了保证输出稳定,请尽量按照推荐值设置反馈分压网络。

LGS5124 - Nov 2022

## 特性说明

#### 概述

LGS5124 是内部开关型的同步降压 DC/DC 稳压器,集成了所有的控制器和保护电路,可以极大降低系统面积。具备 SKIP 控制模式,将快速瞬态响应与高效率相结合。LGS5124 外置分压网络可设定输出电压,实现宽输入输出范围,以满足广泛的使用需要。

附加功能包括:软启动,热关机,UVLO 欠压锁定,最大占空比限制,和智能电流限制关闭定时器。同时具备短路保护功能,在输出短路情况下避免 IC 过热。

### 省电模式(Power Save Mode)

除了连续导通模式(CCM)以外,LGS5124 还具有省电模式,该模式通过暂停开关操作来实现,这样可以降低开关损耗,让转换器在轻负载条件下保持较高效率。Skip Comparator 通过比较 I<sub>SKIP</sub> 和 I<sub>REF</sub> 来管理和切换工作状态,当前电流需求低于 I<sub>SKIP</sub> 时,比较器控制暂停切换;当电流需求增加时(V<sub>OUT</sub> 下降),比较器控制激活电流环路进入连续开关模式,使 V<sub>OUT</sub> 上升,此时 I<sub>REF</sub> 将会下降,当 I<sub>REF</sub> 低于 I<sub>SKIP</sub> 时,再次暂停切换。由于输出电压会不定期地骤降和恢复,因此这种模式下的输出电压纹波大于 CCM 工作模式下的纹波。

### 软启动(Soft-Start)

LGS5124 设置内部软启动。软启动可防止在启动过程中输出电压超调。芯片启动时,IC 内部电路会产生一个软启动电压 (V<sub>SS</sub>) ,该电压从 0V 开始上升,当它小于内部参考(V<sub>REF</sub>)时,V<sub>SS</sub> 代替 V<sub>REF</sub> 作为误差放大器的参考电压;当 V<sub>SS</sub> 超过 V<sub>REF</sub> 时,误差放大器使用 V<sub>REF</sub> 作为参考电压。

在整个启动阶段,开关电流限制依然有效,避免上电即短路的情形发生。当输出有非常大的电容时(例如 2200μF 甚至更大),输出电压上升速度会比 Vss 慢,受限于最大开关限流,从启动到达到目标电压设定值的时间会大于软启动过程的时间。

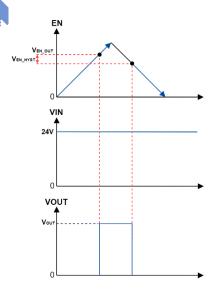

#### EN——IC 使能

EN 引脚的电压控制 LGS5124 的启动和关闭。当 EN 电压小于 V<sub>EN\_OUT</sub> 时芯片保持低功耗待机状态,当 EN 引脚处电压大于 V<sub>EN\_OUT</sub>时,IC 进入软启动模式。EN 引脚的高耐压决定了 EN 引脚可以直接上拉到 VIN 电压,对最小化应用方案有重要作用。

图 6 EN 上电掉电表现

版权 ©2022-present, 棱晶半导体(南京)有限公司

#### 热关机

当结温开始升至 150℃以上时,热关机(Thermal Shutdown) 将被激活,系统会强制关闭稳压器输出。当结温降至 130℃ 以下时,LGS5124 将会重新尝试进行软启动。

本器件的保证工作结温范围为-40°C 至+125°C,高结温会降低工作寿命,结温长时间高于 125°C时,器件寿命会缩短。请注意,与这些规格一致的最高环境温度取决于具体工作条件以及电路板布局、额定封装热阻和其他环境因素。

结温 $(T_J$ ,单位为°C)根据环境温度 $(T_A$ ,单位为°C)和功耗 $(P_D$ 单位为 W)计算,计算公式如下:

$$T_I = T_A + (P_D \times \theta_{IA})$$

其中 θ<sub>JA</sub>(单位为°C/W)为封装热阻。

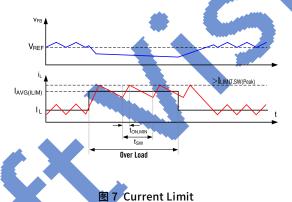

#### 最大电流限制

LGS5124DC-DC 稳压器输出具备逐周期过流限制功能。当 SW 电流触发 l LIMIT.SW(Peak),BUCK 输出会进入逐周期限流状态。 ILIMIT.SW(Peak)与电感大小和输入压差相关,ILIMIT.SW(Peak)仅为参考最小值。当长时间过流或短路时,将可能触发全局 OTP 保护。

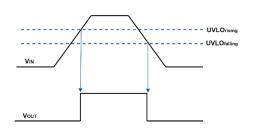

## 输入欠压保护(VULO)

为了防止芯片在低电压下的误操作,LGS5124 内部集成一个欠压锁定电路。当 VIN 电压低于低于一定值时,会触发 UVLO 保护机制,关闭稳压器输出。当 VIN 大于 UVLO<sub>rising</sub> 时会重新

图 8 UVLO 上升下降阈值

#### 最大占空比 D<sub>MAX</sub>

当输入输出压差很低时,BUCK 切换到最大占空比工作状态,此时,高端 N 沟道 MOSFET 处于常开状态,将关断时间缩至 最短。在最大占空比工作条件下,由于输出电压是输入电压值和最大占空比限值的乘积,输出电压会骤降至调节范围以下。

版权 ©2022-present,棱晶半导体(南京)有限公司

# 应用信息

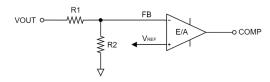

#### 输出电压 Vour

LGS5124 的电压调节回路会将 FB 电压调节至与内部参考电压相同,可以通过改变 R1 和 R2 的电阻比例来调节输出电压大小。电阻分压器从输出节点连接到地,中点连接至 FB 引脚。

图 9 设置输出电压

分压网络电阻可根据以下公式计算:

$$R_2 = \frac{V_{FB}}{V_{OUT} - V_{FB}} \times R_1$$

较大的分压电阻可以减少流过分压网络的电流,提高电压转换效率。但是电阻阻值太大会使反馈回路更容易受噪声影响。建议使用精度±1%或者更好的分压电阻,温度系数 100mmp 或更低,电阻阻值限制在几十 KΩ最佳。如果 FB 引脚接地或断开,输出电压值会被驱动至输入电压值附近。应注意,此时接在输出的负载可能会损坏。反馈回路应保持远离 PCB 噪声干扰的地方,可参考后文给出的 PCB 布局参考。

### 前馈电容 Cff

在某些情况下,前馈电容 CFF 可以跨接在 VOUT-FB 的电阻上来增加环路相位裕度,提高负载瞬态响应。

$C_{FF}$  的引入可以在反馈回路中与反馈电阻形成新的零点 $(Z_{FF})$ 和极点 $(P_{FF})$ ,如果将零点置于出现单位增益的频率之前可以增加频率带宽,使得稳压器输出振铃减小并更快稳定,从而提高系统的瞬态响应。

通常  $C_{FF}$  的选择值越大可以提供更大的带宽,但是过大的  $C_{FF}$  会造成环路增益带宽频率过高,导致环路不稳定。 $C_{FF}$  的一般值在  $22pF\sim220pF$  之间。

图 10 CFF 前置补偿电容

CFF 可根据以下公式估算:

$$C_{FF} = \frac{\sqrt{\frac{V_{FB}}{V_{OUT}}}}{2\pi \times R_1 \times f_c}$$

#### 自举电容 Crst

LGS5124 降压驱动器高侧开关驱动电路要求偏置电压高于 VDD,以确保高侧 MOS 管处于开启状态。BST 和 SW 之间的电容  $C_{BST}$  作为 "电荷泵",将 BST 端的电压升高到 SW+VDD( $V_{BST-SW}=5V$ ),为  $C_{BST}$  充电的导通二极管集成在 LGS5124 的芯片内部,尽可能最小化使用方案的尺寸。 $C_{BST}$  推荐使用  $0.1\mu$ F 电容器,耐压值高于  $10\sim16V$ 。

版权 ©2022-present,棱晶半导体(南京)有限公司

#### 输入电容 Cvin

LGS5124 要求使用去耦电容来滤除输入端的噪声干扰。去耦电容典型推荐值为  $10\mu F$ ,额定电压必须大于 IC 所要求的最大输入电压,最好应为最大输入电压的两倍<sup>(1)</sup>。该电容的增加可以减小输入电压纹波,并且在负载瞬变时保持输入端电压的稳定。同时,在输入端与滤波电容并联一个小型 100nF 陶瓷电容有助于滤除高频噪声。小型电容器滤波半径小,应放置在距离芯片尽可能近的位置,以确保其发挥最好的滤波效果。

在 LGS5124 的测试过程中,我们选择了 10μF, 50V, X7R 和 100nF, 50V, X7R 的陶瓷电容器。

(1) 陶瓷电容的直流偏置效应(DC-Bias Effect)使得电容的有效值下降。请尽可能参照所选电容器的直流偏压特性选择合适的电容.封装尺寸、额定电压和介质材料都会造成额定电容值和有效电容值的差异。

### 输出电容 Cout

LGS5124 允许使用的输出电容值范围比较广,为保证成本和较小的体积,尽量选择合适的输出电容。实际应用中,输出电容会直接影响输出电流瞬态响应时的电压过冲/欠冲和输出电压的纹波。当负载发生瞬态变化时,输出电容需要在环路调节完成前提供电荷,瞬态电压变化值 $\Delta V_{OUT}$ 可由以下公式计算:

$$\Delta V_{OUT} = \Delta I_{OUT} * ESR$$

其中 $\Delta I_{OUT}$ 表示负载电流的跳变值,ESR 为输出电容的等效串联电阻值。

输出电压纹波由两部分组成:一是电感电流纹波流过输出电容的 ESR 引起的,二是电感电流纹波对输出电容充放电引起的。

$$\Delta V_{OUT-ripple} = \frac{\Delta I_L}{8 \times C_{OUT} \times F_{SW}} + \Delta I_L \times ESR$$

$\Delta I_L$ 表示电感纹波电流, $F_{SW}$ 表示 MOSFET 开关频率

为了在瞬态变化中保持较小的输出电压过冲或欠冲、减小输出<mark>纹波,需</mark>要电容具有较大的容值和较小的 ESR,这也会使成本和体积增加,选择合适的输出电容至关重要<sup>(1)(2)</sup>。

- (1) 输出电容过大也会影响芯片的正常启动和回路稳定性。

- (2) 可以直接使用典型应用中推荐的 X7R 的陶瓷电容,或者将其作为一个选择输出电容值的参考标准。

#### 功率电感L

对于功率电感的选型主要考虑电感的饱和电流,要基于所期望的纹波电流 $\Delta I_L$ ,即电感中随负载电流变化的交流电流有效值。一般控制在最大负载电流  $I_{OUT-MAX}$  的 20%-40%之间。电感值可由以下公式进行计算:

$$\Delta I_L = \frac{(V_{IN} - V_{OUT}) \times D}{L \times F_{SW}}$$

D 表示开关占空比,可用 $D=rac{v_{OUT}}{v_{IN}}$ 近似计算,得到的电感值单位是  $\mu H$ 。

电感饱和电流值必须高于最大的负载电流和纹波电流之和:

$$I_{L-MAX} \ge I_{OUT-MAX} + \frac{\Delta I_L}{2}$$

一般来说,选择电感值较低的电感会具有更小的 DCR,能应对更快速的瞬态响应,使用方案的尺寸更小。但是过低的电感会产生更大的电感电流纹波,从而导致使用同样 $C_{OUT}$  时的输出电压纹波更大。

经过测试,典型应用中推荐的电感值可以作为使用参考。

版权 ©2022-present,棱晶半导体(南京)有限公司

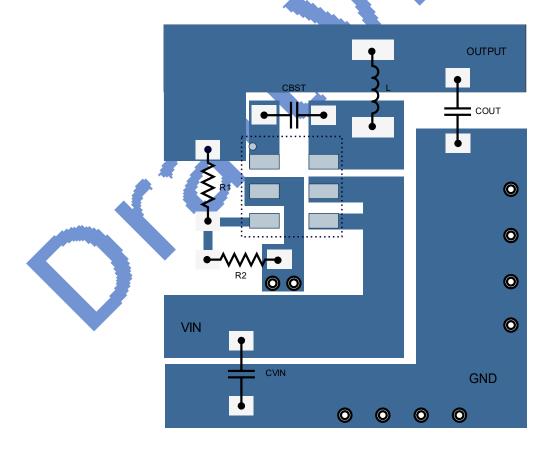

## 参考 PCB 布局

#### 概述

LGS5124 的高集成度使 PCB 板布局非常简明清晰。较差的布局会影响 LGS5124 的性能,造成电磁干扰(EMI)、电磁兼容性 (EMC)差、地跳以及电压损耗,进而影响使用的稳定性。为了优化其电气和热性能,请参照下列规则来实现 PCB 布局布线,确保最佳性能:

- 将高频陶瓷输入电容 C<sub>VIN</sub> 尽可能放置在距离 LGS5124 的 VIN 和 GND 引脚近的位置,以降低引入**到输出**引脚的高频噪声,减小 EMI 辐射。此外,保持输入输出电容在所在层上连接到大面积 GND 上。

- 对功率回路最好使用大面积覆铜的方式,使输入输出连接回路尽可能宽,减小传输过程中的损耗,使效率最大化。

- 为增强散热和连接性,可以增加过孔数量来实现顶层和其他电源层或地层之间的互连。请确保 PCB 板有足够的铺铜区域用来散热,使结温保持在 125°C以下。

- 应考虑电感所产生的 ACR 和 DCR 损耗,所造成的热量传导给芯片。可酌情将电感放置稍远或合理设计热岛。

- 反馈电阻 R<sub>FBT</sub> 和 R<sub>FBB</sub> 应位于靠近 FB 引脚的位置,将前馈电容 C<sub>FF</sub> 与 R<sub>FBT</sub> 平行放置,反馈回路与 FB 和 GND 引脚距离 必须近,适当的与 V<sub>OUT</sub> 距离可以相对放远一些,需要保证反馈回路远离任何噪声源(如 SW 节点)。

图 11 参考 PCB 布局

版权 ©2022-present,棱晶半导体(南京)有限公司

## 封装外形描述

## 1.45mm 高度 6 引脚 SOT-23 塑封 SOIC

#### NOTE:

- (1) 所有的数据单位都是毫米,括号内的任何尺寸仅供参考。尺寸和公差符合 ASME Y14.5M。

- (2) 本图如有更改,恕不另行通知。

- (3) 此尺寸不包括塑模毛边,塑模每侧的毛边或突起不超过 0.25 毫米。

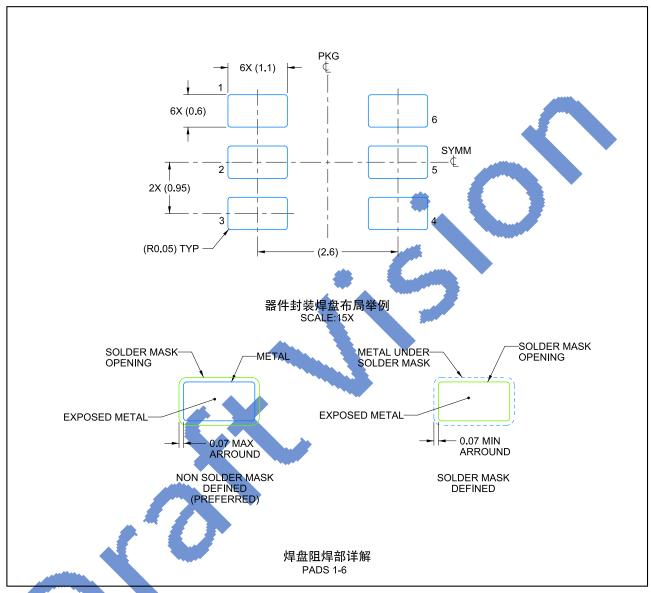

## 器件封装焊盘布局举例

## 1.45mm 高度 6 引脚 SOT-23 塑封 SOIC

#### NOTE:

- (1) 基于 IPC-7351 依赖于久经考验的数学算法,综合考虑了制造、组装和元件容差,从而精确计算的焊盘图形。

- (2) 信号焊盘之间和周围的焊接掩膜公差可能因电路板制造而异。

版权 ©2022-present,棱晶半导体(南京)有限公司

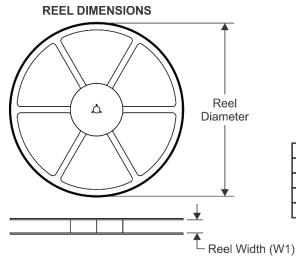

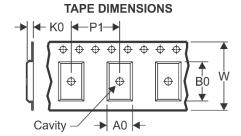

### TAPE AND REEL INFORMALEGEND-SION

|    | Dimension designed to accommodate the component width  |

|----|--------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length |

Dimension designed to accommodate the component thickness

Overall width of the carrier tape

Pitch between successive cavity centers

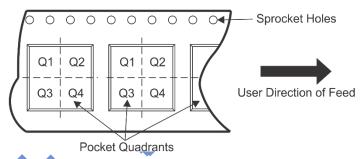

#### **QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*ALL dimensions are nominal

| Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel Width<br>W1(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|--------------------|------|------|----------------------|------------|------------|------------|------------|-----------|------------------|

| SOT23-6         | DBV                | 6    | 3000 | 180.0                | 8.4        | 3.2        | 3.2        | 1.4        | 1.4       | Q3               |

版权 ©2022-present,棱晶半导体(南京)有限公司

## 免责声明

和 Legend-si 是棱晶半导体有限公司的商标,Legend-si 拥有多项专利、商标、商业机密和其他知识产权。Legend-si 对公司产品提供可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、技术支持和其他资源,但不就本司任何产品用于任何特定目的做出担保。Legend-si 不承担任何因产品的使用产生的责任,包括使用方须遵守的法律法规和安全使用标准。

对于在规格书中提到的产品参数,在不同的应用条件下实际性能可能会产生变化。任何参数的配置和使用必须经由客户的技术支持进行验证,对本文档所涉及的内容进行变更,恕不另行通知。Legend-si 对您的使用授权仅限于产品的应用,除此之外不得复制或展示所述资源,Legend-si 也不提供任何人或第三方机构的知识产权授权许可。如因使用所述资源而产生任何索赔、赔偿、成本、债务及任何损失,Legend-si 对此概不负责,并且您须赔偿由此对 Legend-si 造成的损害。

Legend-si 所提供产品均受 Legend-si 的销售条款以及 www.Legend-si.com 上或随附 Legend-si 产品提供的其他可适用条款的约束。Legend-si 提供所述资源并不扩展或以其他方式更改 Legend-si 针对 Legend-si 产品所发布的可适用的担保范围或担保免责声明。

Legend-si 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: 江苏省南京市浦口区江淼路 88 号腾飞大厦 C座 1403 室 电话: 025-58196091

Copyright © 2022-present 棱晶半导体(南京)有限公司