# Hangzhou Nannochap Electronics Co., Ltd.

**ENS001-A\_Datasheet**

# **Revision History**

| Rev | Date       | Author   | Description              |

|-----|------------|----------|--------------------------|

| 1.0 | 29/11/2022 | Nanochap | First Draft              |

| 1.1 | 30/3/2023  | Nanochap | Second Draft             |

| 1.2 | 31/3/2023  | Nanochap | Third Draft Add reminder |

| 1.3 | 7/7/2023   | Nanochap | Modify some parameters   |

|     |            |          | <u></u>                  |

|     |            |          |                          |

|     |            |          |                          |

|     | × //       |          | 74.                      |

|     |            |          |                          |

## Contents

| L | IST ( | OF TABLES                                                                       | VIII             |

|---|-------|---------------------------------------------------------------------------------|------------------|

| L | IST ( | OF FIGURES                                                                      | X                |

| 1 |       | OVERVIEW                                                                        | 1                |

|   | 1.1   | APPLICATIONS                                                                    |                  |

|   | 1.2   | FEATURES                                                                        |                  |

|   | 1.3   | BLOCK DIAGRAM                                                                   |                  |

| 2 |       |                                                                                 |                  |

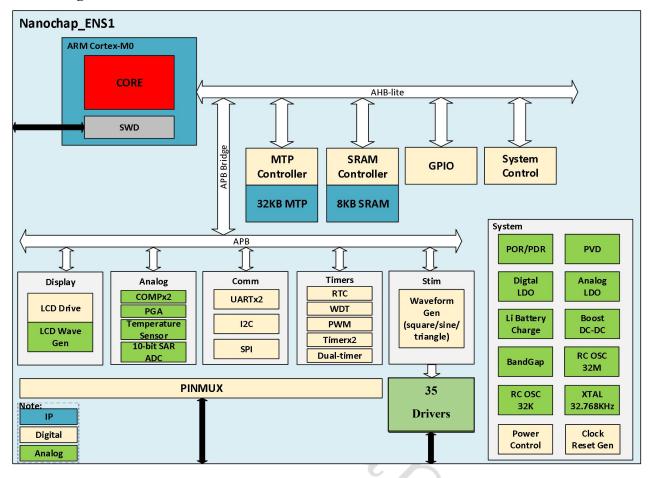

|   | 2.1   | PIN DESCRIPTION  PIN AND PACKAGE DEFINITION  MEMORY                             | 5                |

| 3 |       | MEMORY                                                                          | 11               |

| ٠ | 3.1   | MEMORY MAP EMBEDDED SRAM                                                        | 11               |

|   | 3.2   | EMBEDDED SRAM                                                                   | 12               |

|   | 3.3   | BOOT CONFIGURATION                                                              | 12               |

| 4 |       | MULTI TIME PROGRAM (MTP)                                                        | 14               |

|   | 4.1   | MULTI TIME PROGRAM (MTP)  OVERVIEW                                              | 1.4              |

|   | 4.1.1 | Feature List                                                                    | 1 <b>4</b><br>14 |

|   | 4.2   | BLOCK DIAGRAM                                                                   |                  |

|   | 4.3   | FUNCTION DESCRIPTION                                                            | 16               |

|   | 4.3.1 | Supported user operation mode                                                   | 16               |

|   | 4.3.2 | Definition of Sector Write operation in MTP block                               |                  |

|   | 4.3.3 | Definition of Bootloader Sector in MTP block                                    | 17               |

|   | 4.3.4 | Definition of trim and ID configuration information region in information block | 17               |

|   | 4.3.5 | Definition of user configuration information region in information block        | 17               |

|   | 4.3.6 | User access authority for MTP                                                   | 18               |

|   | 4.3.7 | Timing parameters                                                               | 19               |

| 5 |       | SYSTEM CONTROL UNIT (SCU)                                                       | 20               |

|   | 5.1   | PMU                                                                             | 20               |

|   | 5.2   | RESET CONTROL                                                                   |                  |

|   | 5.3   | CLOCK CONTROL                                                                   | 23               |

|   | 5.3.1 | Clock Tree Structure                                                            | 23               |

|   | 5.3.2 | Clock Description in Different Power Modes                                      | 25               |

|   | 5.3.3 | Clock Switch Sequence                                                           | 26               |

|   | 5.4   | REGISTERS                                      | 27 |

|---|-------|------------------------------------------------|----|

| 6 |       | CPU                                            | 37 |

|   | 6.1   | Overview                                       | 37 |

|   | 6.2   | PROCESSOR CONFIGURATION                        |    |

|   | 6.3   | CORE REGISTERS                                 | 37 |

|   | 6.4   | EXCEPTIONS AND INTERRUPTS                      |    |

|   | 6.5   | DEBUG                                          | 40 |

| 7 |       | CORTEX-M0 PERIPHERALS                          | 41 |

|   | 7.1   | OVERVIEW                                       | 41 |

|   | 7.2   | NESTED VECTORED INTERRUPT CONTROLLER           |    |

|   | 7.2.1 | Registers                                      |    |

|   | 7.3   | SYSTEM CONTROL BLOCK                           |    |

|   | 7.4   | SYSTICK TIMER                                  |    |

|   | 7.4.1 | Registers                                      | 49 |

| 8 |       | GENERAL PURPOSE I/OS (GPIO)                    | 51 |

|   | 8.1   | OVERVIEW                                       | 51 |

|   | 8.1.1 | Feature List                                   |    |

|   | 8.2   | FUNCTION DESCRIPTION                           |    |

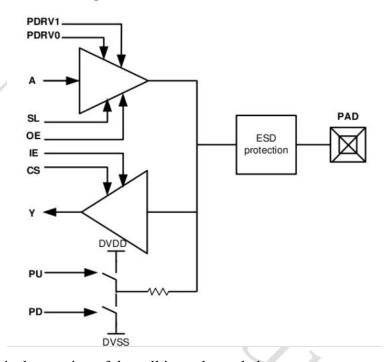

|   | 8.2.1 | Tri-state Digital I/O Cell                     | 52 |

|   | 8.2.2 | Alternate Function Multiplexer                 | 53 |

|   | 8.2.3 |                                                |    |

|   | 8.2.4 | Output Configuration                           |    |

|   | 8.2.5 | Analog Function                                |    |

|   | 8.2.6 | I/O Data Bitwise Handling                      |    |

|   | 8.3   | REGISTERS                                      | 55 |

| 9 |       | EXTENDED INTERRUPT AND EVENT CONTROLLER (EXTI) | 64 |

|   | 9.1   | OVERVIEW                                       | 64 |

|   | 9.1.1 | Feature List                                   | 64 |

|   | 9.2   | FUNCTION DESCRIPTION                           |    |

|   | 9.2.1 | EXTI connections                               |    |

|   | 9.2.2 | EXTI configurable event input wakeup           |    |

|   | 9.2.3 | EXTI direct event input wakeup                 |    |

|   | 9.3   | REGISTERS                                      | 67 |

| 1 | 0     | SERIAL PERIPHERAL INTERFACE (SPI)              | 70 |

|   | 10.1  | OVERVIEW                                       | 70 |

|   | 10.1. | 1 Feature List                                 | 70 |

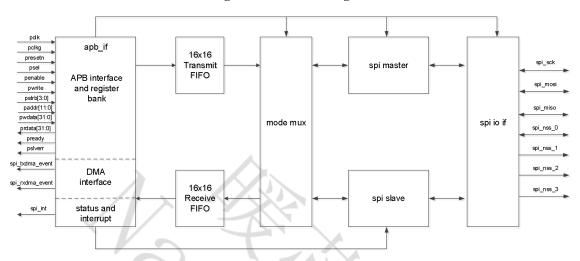

| 10.2   | BLOCK DIAGRAM                               | 71       |

|--------|---------------------------------------------|----------|

| 10.3   | FUNCTION DESCRIPTION                        |          |

| 10.3.1 | SPI Pins                                    |          |

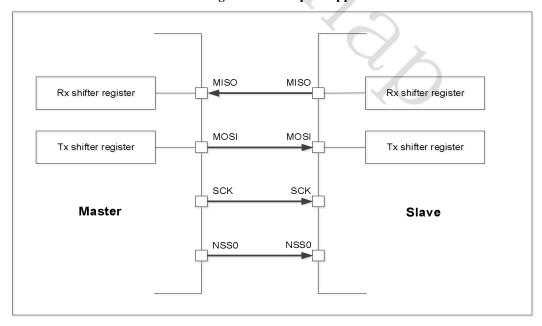

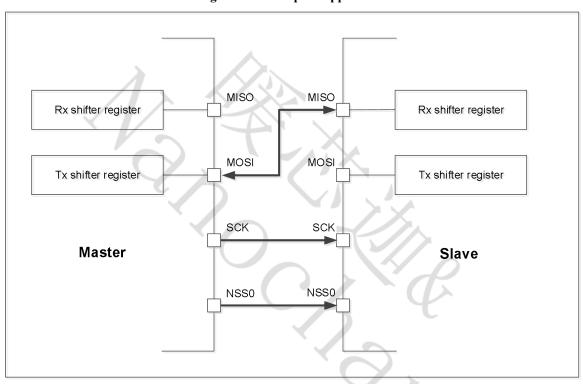

| 10.3.2 | Communications                              |          |

| 10.3.3 | Configurations of SPI                       |          |

| 10.3.4 | Sequence Handling                           |          |

| 10.4   | REGISTERS                                   | 82       |

| 11 U   | UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER | (UART)90 |

| 11.1   | OVERVIEW                                    | 90       |

| 11.1.1 | Feature List                                |          |

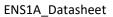

| 11.2   | BLOCK DIAGRAM                               | 92       |

| 11.3   | FUNCTION DESCRIPTION                        |          |

| 11.3.1 | Baud Rate Control                           | 93       |

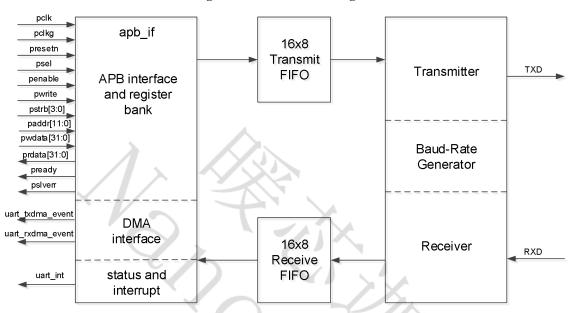

| 11.3.2 | Protocol Description                        | 93       |

| 11.3.3 |                                             |          |

| 11.3.4 | Auto Flow Control                           | 97       |

| 11.3.5 | Loopback Control                            |          |

| 11.3.6 | Reset                                       |          |

| 11.3.7 | Initialization                              | 98       |

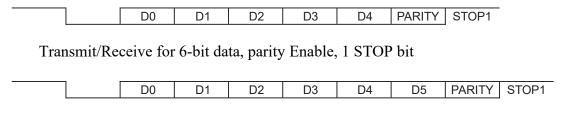

| 11.3.8 | Interrupt Support                           | 99       |

| 11.4   | REGISTERS                                   | 101      |

| 12 I   | NTER-INTEGRATED CIRCUIT INTERFACE (I2C)     | 113      |

| 12.1   | OVERVIEW                                    | 113      |

| 12.1.1 | Feature List                                | 113      |

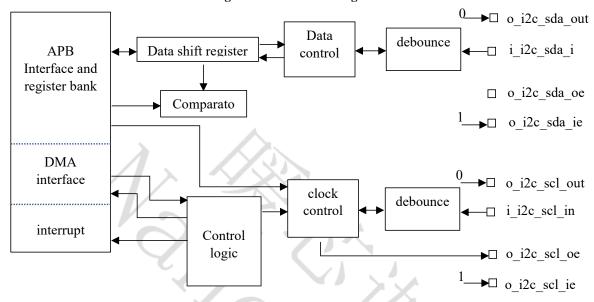

| 12.2   | BLOCK DIAGRAM                               | 115      |

| 12.3   | FUNCTION DESCRIPTION                        |          |

| 12.3.1 | Supported Mode                              | 116      |

| 12.3.2 | I2C Slave Mode                              | 116      |

| 12.3.3 | I2C Master Mode                             | 117      |

| 12.3.4 | Error Conditions                            | 118      |

| 12.3.5 | I2C Interrupt                               | 118      |

| 12.4   | REGISTERS                                   | 120      |

| 13 F   | REAL-TIME CLOCK (RTC)                       | 127      |

| 13.1   | OVERVIEW                                    | 127      |

| 13.1.1 | Feature List                                |          |

| 13.2   | BLOCK DIAGRAM                               | 128      |

| 13.3   | FUNCTION DESCRIPTION                        | 129      |

| Nanochap |                                    | ENSTA_Datasileet |

|----------|------------------------------------|------------------|

| 13.3.1   | Clock and Prescaler                | 129              |

| 13.3.2   | Real-time clock and calendar       | 129              |

| 13.3.3   | Time/Calendar/Alarm Data Mode      | 129              |

| 13.3.4   | Programmable Alarm                 | 130              |

| 13.3.5   | Periodic Wakeup                    | 131              |

| 13.3.6   | Initialization and Configuration   | 131              |

| 13.4     | REGISTERS                          | 133              |

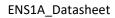

| 14 V     | WATCHDOG TIMER (WDT)               | 138              |

| 14.1     | OVERVIEW                           | 138              |

| 14.1.1   | Feature List                       | 138              |

| 14.2     | FLOW DIAGRAM                       | 139              |

| 14.3     | FUNCTION DESCRIPTION               | 140              |

| 14.3.1   | Clock Configuration                |                  |

| 14.3.2   | Operation                          | 140              |

| 14.4     | REGISTERS                          | 141              |

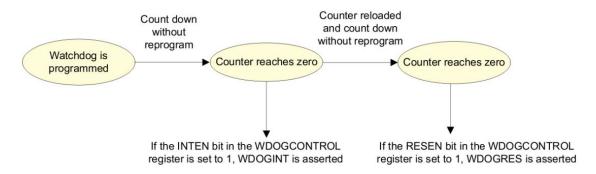

| 15 F     | PULSE WIDTH MODULATION (PWM)       | 144              |

| 15.1     | OVERVIEW                           |                  |

| 15.1.1   | Feature List                       | 144              |

| 15.2     | BLOCK DIAGRAM                      | 145              |

| 15.3     | FUNCTION DESCRIPTION               |                  |

| 15.3.1   | Single Edge Controlled PWM Outputs |                  |

| 15.3.2   | Double Edge Controlled PWM Outputs | 146              |

| 15.4     | REGISTERS                          | 148              |

| 16 T     | OVERVIEW                           | 155              |

| 16.1     | OVERVIEW                           | 155              |

| 16.1.1   | Feature List                       |                  |

| 16.2     | BLOCK DIAGRAM                      |                  |

| 16.3     | FUNCTION DESCRIPTION               |                  |

| 16.4     | REGISTERS                          | 156              |

| 17 I     | DUAL-TIMERS                        | 158              |

| 17.1     | OVERVIEW                           | 158              |

| 17.1.1   | Feature List                       | 158              |

| 17.2     | BLOCK DIAGRAM                      |                  |

| 17.3     | FUNCTION DESCRIPTION               |                  |

| 17.3.1   | Free-running Mode                  |                  |

| 17.3.2   | Periodic Timer Mode                |                  |

| 17.3.3   | One-shot Timer Mode                | 159              |

| 17.3.4             | Operation                              | 159        |

|--------------------|----------------------------------------|------------|

| 17.4               | REGISTERS                              | 161        |

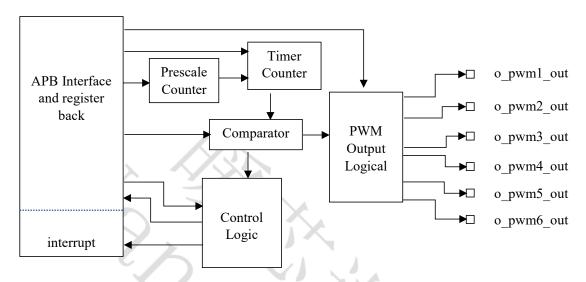

| 18 A               | NALOG CONTROL (ANAC)                   | 167        |

| <b>18.1</b> 18.1.1 | COMPARATOR                             |            |

| 18.1.2             | Block Diagram                          | 168        |

| 18.1.3             | Function Description                   | 169        |

| 18.2               | REGISTERS                              | 170        |

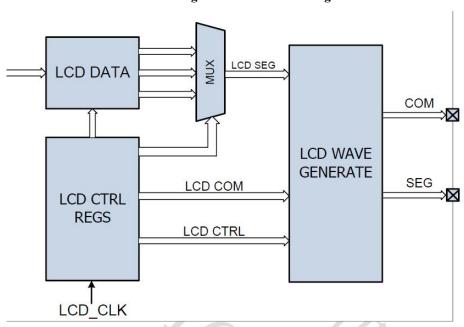

| 19 L               | IQUID CRYSTAL DISPLAY CONTROLLER (LCD) | 176        |

| <b>19.1</b> 19.1.1 | OVERVIEW                               | <b>176</b> |

| 19.2               | BLOCK DIAGRAM                          | 177        |

| 20 A               | PPENDIX                                | 178        |

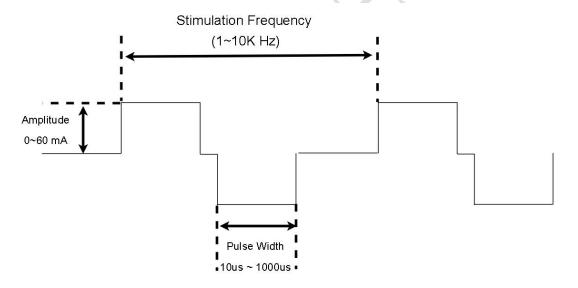

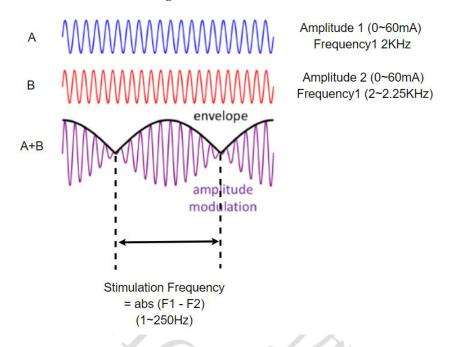

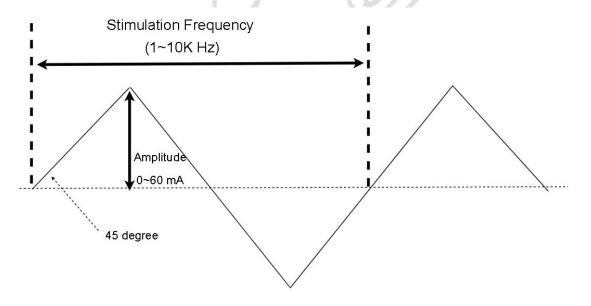

| 20.1               | STIMULATION PARAMETERS                 |            |

| 20.1.1             | Stimulation channel                    |            |

| 20.1.2             | Waveform example                       |            |

| 20.1.3             | Waveform registers                     | 180        |

## **List of Tables**

| Table 1 Interface Signal Table                        | 5   |

|-------------------------------------------------------|-----|

| Table 2 Boot Modes                                    | 12  |

| Table 3 User operation mode                           | 16  |

| Table 4 MTP block memory array configuration          | 16  |

| Table 5 user configuration information definition     | 17  |

| Table 6 MTP access authority                          | 18  |

| Table 7 Low-power Mode Summary                        | 21  |

| Table 8 Functionalities depending on the working mode | 21  |

| Table 9 Clock description in different power modes    | 25  |

| Table 10 SYSCTRL Registers                            |     |

| Table 11 Processor Configuration                      | 37  |

| Table 12 Core Registers                               | 37  |

| Table 13 Interrupt Vector Table                       | 39  |

| Table 14 Core Peripheral Register Regions             | 41  |

| Table 15 NVIC Registers                               | 41  |

| Table 16 SCB Registers                                | 44  |

| Table 17 SysTick Timer Registers                      |     |

| Table 18 Logical Operation Table                      |     |

| Table 19 GPIO Registers                               | 55  |

| Table 20 EXTI line connections                        | 65  |

| Table 21 EXTI Registers                               | 67  |

| Table 22 SPI Registers                                | 82  |

| Table 23 UART Character Time                          | 96  |

| Table 24 UART Interrupt Source                        | 99  |

| Table 25 UART Registers                               | 101 |

| Table 26 Interrupt Table                              | 118 |

| Table 27 I2C Registers                                | 120 |

| Table 28 RTC Data Mode                                | 130 |

| Table 29 RTC Registers                                | 133 |

## ENS1A\_Datasheet

| Table 30 | WDT Registers            | 141 |

|----------|--------------------------|-----|

| Table 31 | PWM Registers            | 148 |

| Table 32 | Timer Registers          | 156 |

| Table 33 | Dual-Timers Registers    | 161 |

| Table 34 | COMP0 Pins and Registers | 169 |

| Table 35 | COMP1 Pins and Registers | 169 |

| Table 36 | Analog Control Registers | 170 |

# **List of Figures**

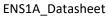

| Figure 1 Top Level Block Diagram                                                            | 4   |

|---------------------------------------------------------------------------------------------|-----|

| Figure 2 Memory Map Diagram                                                                 | 11  |

| Figure 3 MTP Block Diagram                                                                  | 15  |

| Figure 4 Clock Tree                                                                         | 24  |

| Figure 5 Function Schematic of I/O Cell                                                     | 52  |

| Figure 6 SPI Block Diagram                                                                  | 71  |

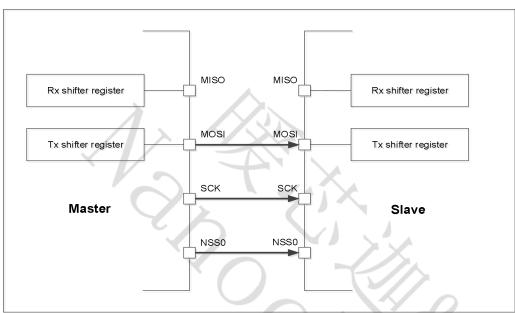

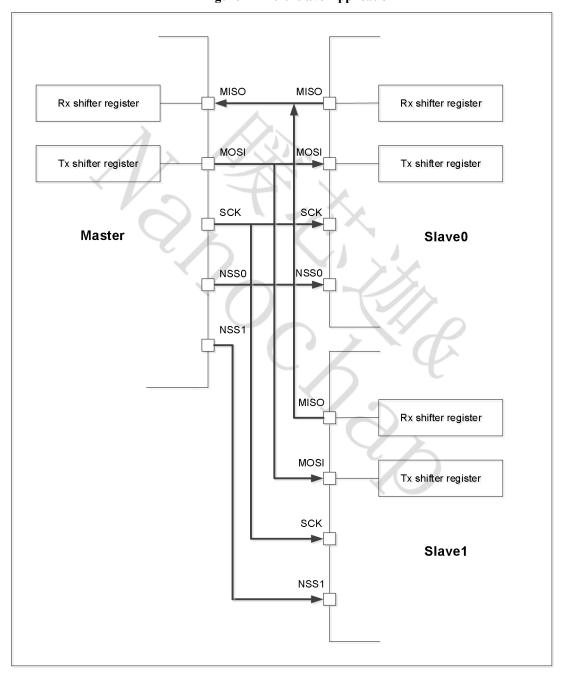

| Figure 7 Full-duplex Application                                                            | 72  |

| Figure 8 Half-duplex Application                                                            | 73  |

| Figure 9 Master in Transmit-only and Slave in Receive-only Mode                             | 74  |

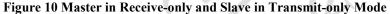

| Figure 10 Master in Receive-only and Slave in Transmit-only Mode                            | 74  |

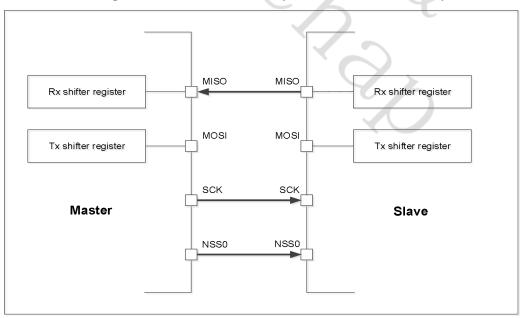

| Figure 11 Multi-slave Application                                                           | 75  |

| Figure 12 NSS Pulse Mode                                                                    | 76  |

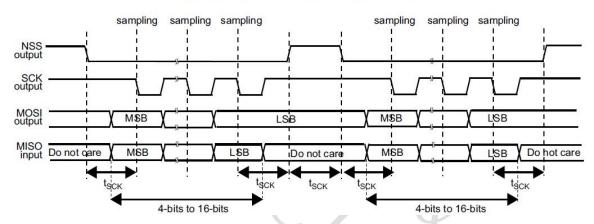

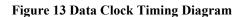

| Figure 13 Data Clock Timing Diagram                                                         | 77  |

| Figure 12 NSS Pulse Mode  Figure 13 Data Clock Timing Diagram  Figure 14 UART Block Diagram | 92  |

| Figure 15 UART Interrupt Output                                                             | 100 |

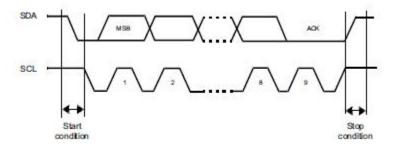

| Figure 16 I2C Bus Protocol                                                                  | 113 |

| Figure 17 I2C Block Diagram                                                                 |     |

| Figure 18 RTC Block Diagram                                                                 |     |

| Figure 19 WDT Flow Diagram                                                                  | 139 |

| Figure 20 PWM Block Diagram                                                                 | 145 |

| Figure 21 Timer Block Diagram                                                               | 155 |

| Figure 22 Dual-Timers Block Diagram                                                         | 158 |

| Figure 23 Comparator Block Diagram                                                          | 168 |

| Figure 24 LCD Block Diagram                                                                 | 177 |

| Figure 25 Square waveform                                                                   | 178 |

| Figure 26 Sine waveform                                                                     | 179 |

| Figure 27 Triangle waveform                                                                 | 179 |

## 1 Overview

The ENS1A is a single chip stimulator device. It integrates a powerful ARM MCU with an integrated battery charger circuit, power supply switcher, a high-voltage boost converter and a high-compliance stimulation block. The ENS1A can be utilized in targeted applications with minimal off-chip components. The stimulator block is designed to drive anodic and cathodic stimulation currents pulses up to 60mA. Eight channels of drivers are available in this device. The ENS1A generates multiple stimulation patterns to support various applications. The system can be configured to support intermediate frequency physiotherapy, conventional TENS, Muscle Rehabilitation and implantable stimulation.

1

## 1.1 Applications

- Muscle Strengthening and Weak Muscle Rehabilitation

- Intermediate Frequency Physiotherapy

- Deep Brain Stimulation

- Spinal Cord Stimulation

- Cochlear Implant

#### 1.2 Features

- Operation temperature range: -40°C to 85°C

- Operating voltage range: 2.5V to 5V

- Integrated 5~60V High Voltage Boost Converter

- Core

- ➤ 32-bit ARM Cortex-M0 CPU

- ➤ Frequency up to 32MHz

- Memories

- ➤ 32Kbytes MTP memory

- ➤ 8Kbytes SRAM

- Clocks

- ➤ HSI RC 4-32MHz

- ➤ Up to 32MHz external clock

- ➤ LSI RC about 32KHz

- ➤ LSE OSC with external crystal 32.768KHz

- Low power mode

- > Sleep mode

- ➤ low-power run mode

- ➤ Low-power sleep mode

- > Stop mode

- 4 Wide-Range Drivers (8 electrodes) (Max 60V)

- ➤ Output current: 33uA~67 mA, with 255 steps

- ➤ Output unit current: 33uA~264uA, 8 steps

- ➤ 2us~infinity pulse width

- ➤ Up to 250 kHz sinusoidal/triangle/square or arbitrary waveform

- > Can be used for TENS, IFT, EMS

- 8 Middle-Range Drivers (16 electrodes) (Max 60V)

- ➤ Output current: 50uA~52 mA, with 255 steps

- ➤ Output unit current: 50, 72 ~ 204 uA (8 steps)

- ➤ 2us~infinity pulse width

- > Up to 250 kHz sinusoidal/triangle/square or arbitrary waveform

- > Can be used for DBS, SCS

- 23 Channels Low-Range Drivers (24 electrodes) (Max 60V)

- ➤ 8uA~2 mA output current, 255 steps of 8uA

- > 2us~infinity pulse width

- ➤ Up to 250 kHz sinusoidal/triangle/square or arbitrary waveform

- > Can be used for Cochlear Implant

- Peripheral analog circuits

- ➤ 12-bit ADC: 0 to VDD conversion range

- ➤ Temperature Sensor

- ➤ COMPx2

- > PGA

REV1.3

- ➤ Integrated battery charger

- ➤ Power-on/Power down reset (POR/PDR)

- ➤ Low Voltage Detector (LVD)

- 24 GPIOs

- LCD Drive

- ➤ COMx4, SEGx16

- 96-bit unique ID

- Communication Interface

- > UART x2, with hardware flow control

- > SPI x2, with master/slave mode

- ➤ I<sup>2</sup>C x2, with master/slave mode

- Various timers

- ➤ Real Time Clock (RTC)

- ➤ Watchdog Timer (WDT)

- > Pulse Width Modulation (PWM)

- ➤ 32-bit Timer x2

- ➤ 32-bit or 16-bit dual-timer

- ➤ SysTick Timer

## 1.3 Block Diagram

Figure 1 Top Level Block Diagram

### **Block diagram:**

REV1.3

# 2 Pin Description

## 2.1 Pin and Package definition

**Table 1 Interface Signal Table**

https://www.nanochap.com Tel: 4008605922

5

| Pin<br>No. | PIN NAME   | Primary Funtion (ALT Function 0)      | ALT Function 1 | ALT Function<br>2 | ALT Fu | unction 3      |

|------------|------------|---------------------------------------|----------------|-------------------|--------|----------------|

| 1          | VDD_IO     | 3.3V IO Supply                        | -              | -                 | -      | -              |

| 2          | VDD_DIG    | 1.8V Digital Core Supply              | -              | -                 | -      | -              |

| 3          | CLK32K_OUT | 32 kHz Crystal OUT                    | -              | -                 | -      | -              |

| 4          | CLK32K_IN  | 32 kHz Crystal IN                     | -              | -                 | -      | -              |

| 5          | VSS_DIG    | Digital Ground                        | -              | -                 | -      | -              |

| 6          | GPIO12     | GPIO12                                | UART1_RXD      | мсо               | SEG4   | COMP1_VIP<br>0 |

| 7          | GPIO13     | GPIO13                                | UART1_TXD      | SPI0_NSS1         | SEG5   | COMP1_VIP<br>1 |

| 8          | GPIO14     | GPIO14                                | UART1_RTS_N    | SPI0_NSS2         | SEG6   | COMP1_VIN<br>0 |

| 9          | GPIO15     | GPIO15                                | UART1_CTS_N    | SPI0_NSS3         | SEG7   | COMP1_VIN<br>1 |

| 10         | GPIO16     | GPIO16                                | PWM1_OUT       | SPI1_SCK          | SEG8   | PGA_VIP0       |

| 11         | GPIO17     | GPIO17                                | PWM2_OUT       | SPI1_MOSI         | SEG9   | PGA_VIP1       |

| 12         | GPIO18     | GPIO18                                | PWM3_OUT       | SPI1_MISO         | SEG10  | PGA_VIN0       |

| 13         | GPIO19     | GPIO19                                | PWM4_OUT       | SPI1_NSS0         | SEG11  | PGA_VIN1       |

| 14         | GPIO20     | GPIO20                                | PWM5_OUT       | COMP0_OUT         | SEG12  | PGA_EXVC<br>M  |

| 15         | VPP_MTP    | MTP Memory VPP pin                    | -              |                   | -      | -              |

| 16         | VDD_DIG    | 1.8V Digital Core Supply              | - , \          |                   | -      | -              |

| 17         | VSS_DIG    | Digital Ground                        | -              |                   | -      | -              |

| 18         | GPIO21     | GPIO21                                | PWM6_OUT       | COMP1_OUT         | SEG13  | ADC_IN0        |

| 19         | GPIO22     | GPIO22                                | TIMER0_EXTIN   | -                 | SEG14  | ADC_IN1        |

| 20         | GPIO23     | GPIO23                                | TIMER1_EXTIN   | -                 | SEG15  | ADC_IN2        |

| 21         | nRST       | Reset, Active LOW, Default = 1        | -6             | <u>ک</u> ۔        | -      | -              |

| 22         | TESTEN     | TEST Enable, Active HIGH, Default = 0 | _ <            | ✓ .               | -      | -              |

| 23         | BOOTSEL0   | Boot Select 0, Default = 0            | -              | -                 | -      | -              |

| 24         | BOOTSEL1   | Boot Select 1, Default = 0            | -              | -                 | -      | -              |

| 25         | VDD_IO     | 3.3V IO Supply                        | -              | -                 | -      | -              |

| 26         | VSS_IO     | IO Ground                             | -              | -                 | -      | -              |

|            |            | Driver B and Driver C                 |                |                   |        |                |

|            | STIMU15    | Outputs                               |                |                   |        | -              |

| 27         |            | /DB_ELE15/DC_ELE7                     | -              | -                 | -      |                |

|            |            | Driver B and Driver C                 |                |                   |        |                |

|            | STIMU14    | Outputs                               |                |                   |        | _              |

| 28         |            | /DB_ELE14/DC_ELE6                     | -              | _                 | _      |                |

| 29         | STIMU13    | Driver B and Driver C<br>Outputs      | -              | -                 | -      | -              |

|            | 1          | 1                                     | 1              | 1                 | I .    | l              |

https://www.nanochap.com

|    |          | /DB_ELE13/DC_ELE5        |       |                   |   |   |

|----|----------|--------------------------|-------|-------------------|---|---|

|    |          | Driver B and Driver C    |       |                   |   |   |

|    | STIMU12  | Outputs                  |       |                   |   | _ |

| 30 |          | /DB_ELE12/DC_ELE4        | -     | _                 | _ |   |

|    |          | Driver B and Driver C    |       |                   |   |   |

|    | STIMU11  | Outputs                  |       |                   |   | - |

| 31 |          | /DB_ELE11/DC_ELE3        | -     | -                 | - |   |

|    |          | Driver B and Driver C    |       |                   |   |   |

|    | STIMU10  | Outputs                  |       |                   |   | _ |

| 32 |          | /DB_ELE10/DC_ELE2        | -     | _                 | - |   |

|    | CTIMALIO | Driver B and Driver C    |       |                   |   |   |

| 33 | STIMU9   | Outputs /DB_ELE9/DC_ELE1 | -     | _                 | - | _ |

|    | CTIMALIO | Driver B and Driver C    |       |                   |   |   |

| 34 | STIMU8   | Outputs /DB_ELE8/DC_ELE0 | (F) - | _                 | _ | _ |

|    |          | Driver A and Driver B    |       |                   |   |   |

|    | STIMU7   | Outputs                  | -114  |                   |   | - |

| 35 |          | /DA_CH3_Anode/DB_ELE7    | 7.    | -                 | - |   |

|    |          | Driver A and Driver B    |       | 4                 |   |   |

|    | STIMU6   | Outputs                  |       | C .               |   | - |

| 36 |          | /DA_CH3_Cathode/DB_ELE6  | -     | // <sub>2</sub> - | - |   |

|    |          | Driver A and Driver B    |       |                   |   |   |

|    | STIMU5   | Outputs                  |       |                   |   | - |

| 37 |          | /DA_CH2_Anode/DB_ELE5    |       |                   | - |   |

|    |          | Driver A and Driver B    |       |                   |   |   |

|    | STIMU4   | Outputs                  | ~ /   |                   |   | - |

| 38 |          | /DA_CH2_Cathode/DB_ELE4  | Y-    | -                 | - |   |

|    | HVDD     | High Voltage Supply for  |       | >                 |   | _ |

| 39 | 111000   | Stimulation Drivers      | - 7   | -                 | - |   |

|    | HVDD     | High Voltage Supply for  |       |                   |   | _ |

| 40 |          | Stimulation Drivers      | _     | -                 | - |   |

|    |          | Driver A and Driver B    |       |                   |   |   |

|    | STIMU3   | Outputs                  |       |                   |   | - |

| 41 |          | /DA_CH1_Anode//DB_ELE3   | -     | -                 | - |   |

|    |          | Driver A and Driver B    |       |                   |   |   |

|    | STIMU2   | Outputs                  |       |                   |   | - |

| 42 |          | /DA_CH1_Cathode/DB_ELE2  | -     | -                 | - |   |

|    |          | Driver A and Driver B    |       |                   |   |   |

|    | STIMU1   | Outputs                  |       |                   |   | - |

| 43 |          | /DA_CH0_Anode/DB_ELE1    | -     | -                 | - |   |

|    |          | Driver A and Driver B    |       |                   |   |   |

|    | STIMU0   | Outputs                  |       |                   |   | - |

| 44 |          | /DA_CH0_Cathode/DB_ELE0  | -     | -                 | - |   |

|    | Тапоспар   |                       |            |          |   |   |

|----|------------|-----------------------|------------|----------|---|---|

|    |            | Driver B and Driver C |            |          |   |   |

|    | STIMU23    | Outputs               |            |          |   | - |

| 45 |            | /DB_ELE23/DC_SW7      | -          | -        | - |   |

|    |            | Driver B and Driver C |            |          |   |   |

|    | STIMU22    | Outputs               |            |          |   | - |

| 46 |            | /DB_ELE22/DC_SW6      | -          | -        | - |   |

|    |            | Driver B and Driver C |            |          |   |   |

|    | STIMU21    | Outputs               |            |          |   | - |

| 47 |            | /DB_ELE21/DC_SW5      | -          | -        | - |   |

|    |            | Driver B and Driver C |            |          |   |   |

|    | STIMU20    | Outputs               |            |          |   | - |

| 48 |            | /DB_ELE20/DC_SW4      | -          | -        | - |   |

|    |            | Driver B and Driver C |            |          |   |   |

|    | STIMU19    | Outputs               |            |          |   | _ |

| 49 |            | /DB_ELE19/DC_SW3      |            | -        | - |   |

|    |            | Driver B and Driver C | -//X       |          |   |   |

|    | STIMU18    | Outputs               |            |          |   | _ |

| 50 |            | /DB_ELE18/DC_SW2      | -          | -        | - |   |

|    |            | Driver B and Driver C |            | C        |   |   |

|    | STIMU17    | Outputs               |            |          |   | _ |

| 51 |            | /DB_ELE17/DC_SW1      | -          |          | - |   |

|    |            | Driver B and Driver C |            |          |   |   |

|    | STIMU16    | Outputs               |            |          |   | - |

| 52 |            | /DB_ELE16/DC_SW0      |            | τ.       | - |   |

|    | BOOST_OUT3 | DC-DC BOOSTER OUTPUT  | × //       |          |   | _ |

| 53 | 00001_0010 | 3                     | 4          | -        | - |   |

|    | BOOST_OUT3 | DC-DC BOOSTER OUTPUT  |            | >        |   | _ |

| 54 | 00001_0010 | 3                     | - 7        | <u> </u> | - |   |

|    | SW5        | DC-DC BOOSTER         | <b>/</b> ( |          |   | _ |

| 55 | 0000       | INDUCTOR-DIODE 5      | -          | -        | - |   |

|    | SW5        | DC-DC BOOSTER         |            |          |   | _ |

| 56 | 3773       | INDUCTOR-DIODE 5      | -          | -        | - |   |

|    | SW4        | DC-DC BOOSTER         |            |          |   | _ |

| 57 |            | INDUCTOR-DIODE 4      | -          | -        | - |   |

|    | SW4        | DC-DC BOOSTER         |            |          |   | _ |

| 58 | O V V ¬    | INDUCTOR-DIODE 4      | -          | -        | - | _ |

|    | BOOST_OUT2 | DC-DC BOOSTER OUTPUT  |            |          |   | _ |

| 59 | 50001_0012 | 2                     | -          | -        | - | _ |

|    | BOOST_OUT2 | DC-DC BOOSTER OUTPUT  |            |          |   | _ |

| 60 | 50001_0012 | 2                     | -          | -        | - | _ |

|    | SW3        | DC-DC BOOSTER         |            |          |   | _ |

| 61 | 3003       | INDUCTOR-DIODE 3      |            | -        | - |   |

|    |            |                       |            |          |   |   |

|    |                   | DC-DC BOOSTER                  |              |              |      |          |

|----|-------------------|--------------------------------|--------------|--------------|------|----------|

| 62 | SW3               | INDUCTOR-DIODE 2               | -            | _            | _    | -        |

|    | 0).1.0            | DC-DC BOOSTER                  |              |              |      |          |

| 63 | SW2               | INDUCTOR-DIODE 2               | -            | _            | _    | -        |

|    | 0).1.0            | DC-DC BOOSTER                  |              |              |      |          |

| 64 | SW2               | INDUCTOR-DIODE 2               | -            | _            | _    | -        |

|    | DOOCT OUT1        | DC-DC BOOSTER OUTPUT           |              |              |      |          |

| 65 | BOOST_OUT1        | 1                              | -            | _            | -    | -        |

|    | BOOST_OUT1        | DC-DC BOOSTER OUTPUT           |              |              |      |          |

| 66 | BOO31_0011        | 1                              | -            | -            | -    | _        |

|    | SW1               | DC-DC BOOSTER                  |              |              |      | _        |

| 67 | 3001              | INDUCTOR-DIODE 1               | -            | -            | -    |          |

|    | SW1               | DC-DC BOOSTER                  |              |              |      | _        |

| 68 | 3441              | INDUCTOR-DIODE 1               | -            | -            | -    |          |

|    |                   | Gate-control signal for        | X4           |              |      |          |

|    | EX_MOS1           | external main switching        | -/ix         |              |      | -        |

| 69 |                   | NMOS for DC-DC Booster         | - 1          | -            | -    |          |

|    |                   | Gate-control signal for        |              | A            |      |          |

|    | EX_MOS2           | external over-voltage          |              |              |      | _        |

|    | _                 | discharging NMOS for DC-       |              |              |      |          |

| 70 |                   | DC booster                     | -            | / -          | -    |          |

| 71 | AVSS              | Analog Ground                  | - > \        | 4            | -    | -        |

| 72 | AVSS              | Analog Ground                  |              | 4            | -    | -        |

| 73 | VBAT              | 4.2V Battery Input             |              | · -          | -    | -        |

| 74 | VBAT              | 4.2V Battery Input             |              | -            | -    | -        |

| 75 | AVDD5P0           | 5V DC input for charging       |              |              |      | -        |

| 75 | A) (DD            | battery                        | -            | -            | -    |          |

| 76 | AVDD              | 3.3V LDO Output                | -            | <u> </u>     | -    | -        |

| 77 | DIG_LDO           | 1.8V LDO Output                | - ~          |              | -    | -        |

| 70 | VSYS_LDO          | 4.23V LDO output for           |              |              |      | -        |

| 78 | VDD DIG           | battery charging circuit       | <del>-</del> | -            | -    |          |

| 79 |                   | 1.8V Digital Core Supply       | <del>-</del> | -            | -    | -        |

| 80 | VSS_DIG<br>VDD_IO | Digital Ground  3.3V IO Supply | <del>-</del> | -            | -    | -        |

| 82 | VSS_DIG           | Digital Ground                 | <del>-</del> | -            | -    | -        |

| 83 | VDD DIG           | 1.8V Digital Core Supply       | <del>-</del> | -            | -    | -        |

| 84 | GPIO0             | SWCLK                          | GPIO0        | -<br>USE CIV | -    | -        |

| 85 | GPIO0             | SWDIO                          | GPIO1        | HSE_CLK      |      | -        |

| 86 | GPIO1<br>GPIO2    | GPIO2                          | UARTO_RXD    | SPI1_NSS1    | -    | -        |

| 87 | GPIO2<br>GPIO3    | GPIO2                          | UARTO_TXD    | <del>-</del> | -    | -        |

| 88 | GPIO3             | GPIO3                          | UARTO_RTS_N  | SPI1_NSS2    | COM0 | PCA OUT  |

| 89 | GPIO5             | GPIO5                          |              | SPI1_NSS3    | +    | PGA_OUT  |

| 09 | GPIUS             | GNIOD                          | UART0_CTS_N  | _            | COM1 | ANA_BIST |

https://www.nanochap.com

| 92 | GPIO9  | GPIO9                                   | SPI0_MOSI | I2C1_SDA | SEG1 | COMP0_VIP      |

|----|--------|-----------------------------------------|-----------|----------|------|----------------|

| 94 | GPIO10 | GPIO10                                  | SPI0_MISO | _        | SEG2 | COMP0_VIN<br>0 |

| 95 | GPIO11 | GPIO11                                  | SPI0_NSS0 | RTC_1HZ  | SEG3 | COMP0_VIN<br>1 |

| 96 | VSS_IO | IO Ground                               | -         | -        | -    | -              |

| 97 | HVSS   | High Voltage Ground -<br>GND BOTTOM PAD | -         | -        | -    | -              |

Note: Please refer to schematic diagram for design. If you need to use the BOOST circuit overvoltage, overtemperature function, please contact the manufacturer.

Copyright@ 2023Nanochap

Tel: 4008605922

10

# 3 Memory

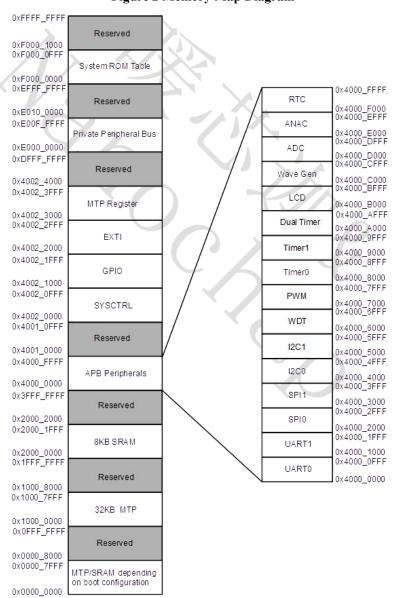

## 3.1 Memory Map

Program memory, data memory, registers and I/O ports are organized within the same linear 4-Gbyte address space. The bytes are coded in memory in Little Endian format. All the memory map areas that are not allocated on-chip memories and peripherals are considered "Reserved".

Figure 2 Memory Map Diagram

Tel: 4008605922

11

https://www.nanochap.com

REV1.3

### 3.2 Embedded SRAM

The embedded SRAM capability is 8Kbytes. This SRAM can be accessed by bytes, half-words (16 bits) or full words (32 bits). This memory can be addressed at maximum system clock frequency without wait state.

The SRAM start address is 0x2000 0000.

The CPU can access the SRAM from address 0x0000\_0000 when physical remap is selected through BOOT pin or REMAP register.

## 3.3 **Boot Configuration**

Three boot modes can be selected through the BOOT0 and BOOT1 pins, as shown in the following table.

| Boot mode selection |           | Boot mode       | Aliasing                                                                    |

|---------------------|-----------|-----------------|-----------------------------------------------------------------------------|

| Boot1 pin           | Boot0 pin |                 |                                                                             |

| Х                   | 0         | MTP base        | MTP main area from base is selected as boot area for application code usage |

| 0                   | 1         | MTP high 4KByte | MTP high 4KByte area is selected as boot area for bootloader usage          |

| 1                   | 1         | Embedded SRAM   | Embedded SRAM is selected as boot area for debug usage                      |

**Table 2 Boot Modes**

After startup delay has elapsed, CPU fetches the top-of-stack value from address 0x0000 0000, then starts code execution from the boot memory at 0x0000 0004.

Boot from MTP main area at base address: the MTP memory is aliased in the boot memory space  $(0x0000\_0000)$ , but still accessible from its original memory space  $(0x1000\_0000)$ . In other words, the MTP memory contents can be accessed starting from address  $0x0000\_0000$  or  $0x1000\_0000$ .

Boot from MTP high 4KByte area: the MTP high 4Kbyte area is used for bootloader, it is aliased in the boot memory space (0x0000\_0000), but still accessible from its original memory space (0x1000\_7000) The remaining 28KByte space is used for application code.

Boot from the embedded SRAM: the SRAM is aliased in the boot memory space (0x0000 0000), but it is still accessible from its original memory space (0x2000 0000).

12

https://www.nanochap.com Tel: 4008605922

Once the BOOT0 and BOOT1 pins are selected, the application software can modify the memory in the code area. This modification is performed by programming the REMAP bits in SYSCTRL register.

BOOT0 and BOOT1 default is weak pull-down, when boot from bootloader space, that is boot0 pin need to be pulled high, software can clear the GPIO\_PD[24] register to save power.

# 4 Multi Time Program (MTP)

#### 4.1 Overview

YEG8K32F18B5AA1 is an embedded MTP IP macro fabricated in the Globalfoundries 0.18um BCDlite 1.8V - ULL 6V 40V-65V Process. The memory arrays are partitioned into three memory blocks each. One is the MTP block (8K x 32 bits); one is the Information block (32 x 32 bits); the other is the EEPROM block (512 x 8 bits).

The YEG8K32F18B5AA1 supports two operating mode: User mode and Test mode.

User modes provide five memory operation: reset(RESET) / standby(STANDBY) / static(STATIC) / read(READ) / write with internal high voltage (INTHV WRITE).

Test modes provide four memory operations: measure memory cell current(CLEN) / read for data retention test(MRGN READ) / write with internal high voltage for data retention test(MRGN INTHV WRITE) / write all MTP density with external high voltage(EXTHV WRITE ALL).

#### 4.1.1 Feature List

- Memory organization: MTP block(8K x 32 bits); information block(32 x 32 bits); EEPROM block(512 x 8 bits).

- MTP block supports 32-bit read and sector write operation.

- Information block support 32-bit read and 32-bit write operation.

- EEPROM block support byte read and byte write operation.

- Re-write data without erase operation.

- Write time is not a fixed value.

- BUSY signal provides a hardware method of detecting write operation completion.

- Writing MTP key: 0x5A5A5A5A.

14

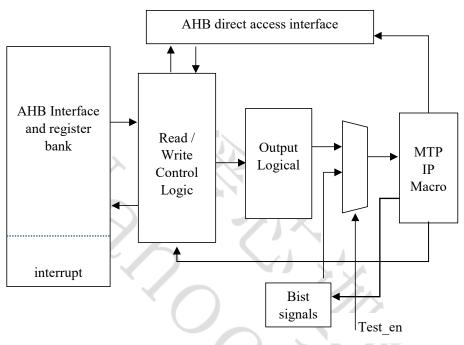

## 4.2 Block Diagram

A functional block diagram of the MTP controller is shown as below.

Figure 3 MTP Block Diagram

REV1.3

REV1.3

### 4.3 Function Description

#### 4.3.1 Supported user operation mode

User modes can operate in one of the five following modes

- Reset(RESET)

- Standby(STANDBY)

- Static(STATIC)

- Read(READ)

- Write with internal high voltage(INTHV WRITE)

Operating mode selection is showed as below

Pin Name RESET STANDBY STATIC READ INTHV WRITE RESETB2 L H H H H CS L L H H H READ L or H L or H L H L WR L or H L or H L L H CLEN L or H L or H L Τ. L L **IFREN** L or H EEPROM L or H L or H L or H L Η L H SRL L or H L or H L L L MRGN L or H L or H L L T. HVEN L or H L or H L L L WRALL L or H L or H L L L VPP VDD2

Table 3 User operation mode

### 4.3.2 Definition of Sector Write operation in MTP block

Memory array in MTP block is integrated by several sectors. The ADDRESS of each sector defined and described as below table.

Only "sector write" operation is allowed on MTP block.

Write data into memory array randomly is not allowed. Write operations are initiated continuously from the 1st address to the last address of the target sector.

Table 4 MTP block memory array configuration

16

Copyright@ 2023Nanochap

| Sector NO. | Used Address  | Sector NO. | Used Address  |

|------------|---------------|------------|---------------|

| Sector 0   | 0000H ~ 03FFH | Sector 4   | 1000H ~ 13FFH |

| Sector 1   | 0400H ~ 07FFH | Sector 5   | 1400H ~ 17FFH |

| Sector 2   | 0800H ~ 0BFFH | Sector 6   | 1800H ~ 1BFFH |

| Sector 3   | OCOOH ~ OFFFH | Sector 7   | 1C00H ~ 1FFFH |

#### 4.3.3 Definition of Bootloader Sector in MTP block

Bootloader sector address is sector7 in MTP block. When DBGPA\_EN and BOOTLD\_WEN turn off, bootloader sector can be written by SWD. The software application only can read bootloader sector.

# 4.3.4 Definition of trim and ID configuration information region in information block

Trim configuration information region address is from 0x0018 to 0x001B. Device ID configuration information region address is from 0x001C to 0x001E. They is used to store analog trim values and device ID values that will be automatically loaded to relational configuration registers after power on and reset.

### 4.3.5 Definition of user configuration information region in information block

User configuration information region address is 0x001F. It is used to store user configuration information that will be automatically loaded to configuration registers after power on and reset.

Bit Field Name **Field Description** Default 31:24 23:16 BOOTLD SWDPA EN Bootloader SWD 0x55 access protection enable: 0x55: on Other: off 15:8 DBGPA EN 0xAA Debug port access protection enable: 0xAA: on Other: off 7:0 SEC\_ACL\_EN application code lock enable: 0x33 0X33: enable aclock Other: forbid aclock

Table 5 user configuration information definition

## 4.3.6 User access authority for MTP

Table 6 MTP access authority

| MTP regi      | on             | MTP_DBGPA_EN | SEC_ACL | BOOTLD_SWDPA_EN | SWD        | Application |

|---------------|----------------|--------------|---------|-----------------|------------|-------------|

| MTP<br>block  | Sector0        | 1            | 0       | х               | -          | Read/write  |

| DIOCK         | sector6        |              | 1       | х               | -          | -           |

|               |                | 0            | 0       | х               | Read/write | Read/write  |

|               |                |              | 1       | х               | Read/write | -           |

|               | Bootloa        | 1            | х       | 1               | -          | Read        |

|               | der<br>region  |              |         | 0               | -          | Read        |

|               | Sector7        | 0            | х       | 1               | -          | Read        |

|               |                | 1            |         | 0               | Read/write | Read        |

| Informa       | Other          | 1            | х       | х               | -          | Read/write  |

| tion<br>block | region         | 0            | х       | х               | Read/write | Read/write  |

|               | Trim<br>and ID | 1            | х       | х               | -          | Read        |

|               | region         | 0            | x       | х               | Read/write | Read        |

|               | User           | 1            | х       | Х               | -          | Read        |

|               | region         | 0            | х       | Х               | Read/write | Read        |

| EEPROM        | block          | 1            | х       | Х               | 7          | Read/write  |

|               |                | 0            | х       | X               | Read/write | Read/write  |

## 4.3.7 Timing parameters

|                               | Symbol                     | Min.     | Тур. | Max.        | Unit |    |

|-------------------------------|----------------------------|----------|------|-------------|------|----|

| VDD1 Setup Time               | Tpws                       | 100      | 5    | 250         | ns   |    |

| VDD1 Hold Time                |                            | Tpwh     | 100  | 23          | (52) | ns |

| VDD2 Setup Time               |                            | Trsts    | 100  | . =         | (H)  | ns |

| VDD2 Hold Time                |                            | Trsth    | 100  | 50          | 332  | ns |

| Setup Time From RE            | SETB to CS                 | Trscs    | 40   | =1          | 1545 | us |

| Hold Time From RES            | SETB to CS                 | Trsch    | 100  | =1          | 1275 | ns |

| CS to READ / WR Se            | etup time                  | Tesetrls | 100  | 20          | 1923 | ns |

| Address/Data Setup T          | ime                        | Tads     | 20   | 8           | 0.80 | ns |

| Address Hold Time             | 63                         | Tadhr    | 50   |             |      | ns |

| Read Pulse Width              | MTP and Information blocks | Trpw     | 60   | 23          | (52) | ns |

|                               | EEPROM block               |          | 250  |             | (14) | ns |

| READ Access Time              | MTP and Information blocks | Trac     | 26   |             | 60   | ns |

|                               | EEPROM block               |          | ñ    | 27          | 250  | ns |

| D 10 1 T                      | MTP and Information blocks |          | 80   | =           | 755  | ns |

| Read Cycle Time               | EEPROM block               | Trc      | 270  | 25          | 1923 | ns |

| DOUT Hold Time                | ,.                         | Tdoh     | 3    | **          | 0.00 | ns |

| WR Pulse Width                |                            | Twpw     | 100  | 50<br>E3    | 838  | ns |

| Address/Data Hold T           | ime for Write              | Tadhw    | 50   | 27          | 122  | ns |

| Write Time                    | MTP and Information blocks |          | 8    | 0.5         | (%)  | ms |

| (changed code)                | EEPROM block               | Twr      | āe   | 0.15        | 838  | ms |

| Write Time (non-changed code) |                            | 1        | 1    | 21          | 1945 | us |

| BUSY Access Time to WR        |                            | Tbas     | Ħ    | -           | 100  | ns |

| Write Recovery Time           |                            | Twrc     | 100  | <u>12</u> } | 1924 | ns |

| Measurement Current Wait Time |                            | Tmcw     | 100  | £.          |      | ns |

| Address Hold Time for         | or CLEN                    | Tadhc    | 20   | 8 5         | 85   | ns |

# 5 System Control Unit (SCU)

#### 5.1 **PMU**

By default, MCU is in run mode after a system or a power-on reset. In run mode the CPU is clocked by HCLK (default is 8MHz from HSI RC) and the program code is executed. Several low-power modes are available to save power when the CPU does not need to be kept running. When RTC/LCD are not used in some applications, the LSI RC (about 32kHz) and LSE OSC with external crystal (accurate 32.768kHz) can be disabled to save power by software. Also there are peripherals enable bits in SYSCTRL register, if some peripherals are not used, user can disable the peripherals to gate their clocks.

Five power modes are supported:

- Run mode: normal run mode, CPU is running at high frequency clock, all peripherals can be active.

- Sleep mode: HCLK is gated. CPU/All AHB peripherals clock off, all APB peripherals and core peripherals such NVIC, SysTick, etc. can run and wake up the CPU when an interrupt or an event occurs.

- Low-power run mode: system clock(SYSCLK) is switched to LFCLK which is about 32KHz. To save power, User can copy program to SRAM to execute.

- Low-power sleep mode: system clock(SYSCLK) is switched to LFCLK which is about 32KHz. Same as sleep mode, HCLK is gated.

- Stop mode: HSI RC is disabled. LFCLK can be kept running.

In addition, the power consumption in run mode can be reduced by one of the following means:

- Slowing down the system clocks

- Gating the clocks to the APB and AHB peripherals when they are unused.

If the SLEEPONEXIT bit of the SCR is set to 1, when the processor completes the execution of an exception handler and returns to thread mode it immediately enters sleep mode. Use this mechanism in applications that only require the processor to run when an interrupt occurs.

Normally, the processor wakes up only when it detects an exception with sufficient priority to cause exception entry.

Some embedded systems might have to execute system restore tasks after the processor wakes up, and before it executes an interrupt handler. To achieve this set the PRIMASK bit to 1. If an interrupt arrives that is enabled and has a higher priority than current exception priority, the processor wakes up but does not execute the interrupt handler until the processor sets PRIMASK to zero.

**Table 7 Low-power Mode Summary**

| Mode name              | Entry                                                                           | Wakeup source                                                                | Wakeup<br>system clock                       | Effect on clocks                        |

|------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------|

| Sleep<br>(Sleep-now or | WFI or return from ISR                                                          | Any interrupt                                                                | Same as before                               | HCLK is off                             |

| Sleep-on-exit)         | WFE                                                                             | Wakeup event                                                                 | entering<br>sleep mode                       |                                         |

| Low-power run          | Set SYSCLK_SEL to 2'b1x                                                         | Set SYSCLK_SEL to 2'b0x                                                      | No change                                    | None                                    |

| Low-power<br>sleep     | Set SYSCLK_SEL to 2'b1x + WFI or return from ISR  Set SYSCLK_SEL to 2'b1x + WFE | Any interrupt  Wakeup event                                                  | Same as before entering low-power sleep mode | HCLK is off                             |

| Stop                   | SLEEPDEEP bit<br>+ WFI or return<br>from ISR or<br>WFE                          | Any EXTI line (configured in the EXTI registers) Specific peripherals events | HSI RC                                       | All clocks off<br>except LSI and<br>LSE |

Table 8 Functionalities depending on the working mode

| Function      | Run | Sleep | Low-power<br>run | Low-power<br>sleep | Stop |

|---------------|-----|-------|------------------|--------------------|------|

| CPU           | Υ   | -     | Υ                | -                  | -    |

| MTP<br>memory | Y   | -     | Υ                | -                  | -    |

| SRAM          | Υ   | -     | Υ                | -                  | -    |

| HSI           | 0   | 0     | 0                | 0                  | -    |

| LSI           | 0   | 0     | 0                | 0                  | 0    |

| LSE           | 0   | 0     | 0                | 0                  | 0    |

| LVD           | 0   | 0     | 0                | 0                  | 0    |

21

| COMP0/1              | 0 | 0 | 0 | 0 | 0 |

|----------------------|---|---|---|---|---|

| ADC                  | 0 | 0 | 0 | 0 | - |

| Wave<br>generator    | 0 | 0 | 0 | 0 | - |

| RTC                  | 0 | 0 | 0 | 0 | 0 |

| LCD                  | 0 | 0 | 0 | 0 | 0 |

| UARTO/1              | 0 | 0 | 0 | 0 | - |

| I2C0/1               | 0 | 0 | 0 | 0 | - |

| SPIO/1               | 0 | 0 | 0 | 0 | - |

| Timer/dual-<br>timer | 0 | 0 | 0 | 0 | - |

| WDT                  | 0 | 0 | 0 | 0 | - |

| PWM                  | 0 | 0 | 0 | 0 | - |

| GPIOs                | 0 | 0 | 0 | 0 | 0 |

Y = Yes. O = Optional

### 5.2 Reset Control

ENS1A reset control includes the control of two kinds of reset, power reset and system reset. The power on reset, known as a cold reset, resets the full system during a power up. A system reset resets the processor core and peripheral IP components with the exception of DBG control and RTC.

The Power reset is generated by Power On reset and Power Down reset (POR/PDR reset). The power reset sets all registers to their reset values. The power reset which active signal is low will be de-asserted when the internal LDO voltage regulator ready to provide 1.8V power. When power down, the PDR threshold voltage can be configured as xxx(TBD). The RESET service routine vector is fixed at address 0x0000\_0004 in the memory map.

Debug logic and RTC can be only reset by POR/PDR.

A system reset is generated by the following events:

- Power on reset

- External reset pin

- Watchdog timer reset

- The SYSRESETREQ bit in Cortex-M0 AIRCR register is set as soft reset.

- CPU lockup (when CPU is in HardFault or NMI handler, another HardFault event occurs)

#### 5.3 Clock Control

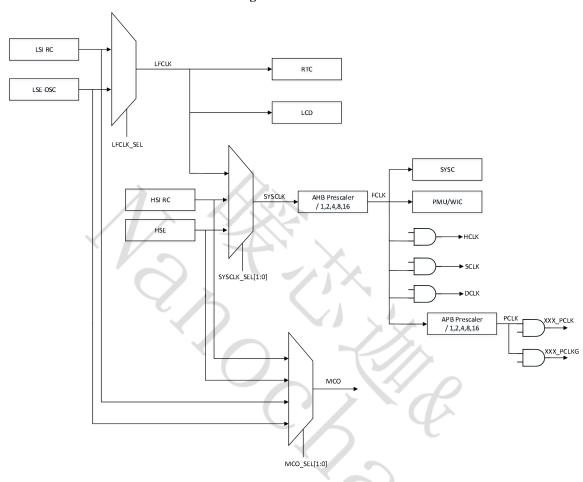

#### **5.3.1** Clock Tree Structure

Four different clock sources can be used:

- HSI RC a high-speed fully-integrated RC oscillator producing HSI clock (about 4-32MHz)

- **HSE** a high-speed external clock (up to 32MHz)

- LSI RC a low-speed fully integrated RC oscillator producing LSI clock (about 32KHz)

- LSE OSC a low-speed oscillator with external crystal resonator (accurate 32.768KHz)

The clock tree structure as below:

REV1.3

**Figure 4 Clock Tree**

One of the following clocks can be selected as system clock (SYSCLK):

- LFCLK (from LSI or LSE)

- HSI

- HSE

The system clock maximum frequency is 32MHz. Upon system reset, the HSI clock is selected as system clock.

A switch from one clock source to another occurs only if the target clock source is ready.

LFCLK can be selected from LSI or LSE. LSI and LSE clock can be disabled by software.

REV1.3

For LSE oscillator, at normal operation, set LSE\_OSCEN and LSE\_CLKEN to 1. At stand-by condition, set LSE\_CLKEN to 0. The clock output at XTALOUTCORE can be disabled, while keep the oscillator core running. If there is a need to drive a clock signal into the chip via the input pin for testing purpose, a bypass multiplexer is included

in the cell which routes clock signals driven at INVINPAD directly to XTALOUTCORE. To enable this feature, set OSCEN to 0, which also turns off the oscillator core.

### **5.3.2** Clock Description in Different Power Modes

AHB and APB peripheral clocks can be disabled by software.

Sleep and low-power sleep modes stop the HCLK.

Stop modes stop all clocks and HSI RC is disabled except LSI and LSE, when leaving the Stop mode, HSI becomes automatically the system clock.

The MCO pins output, independently of each other, the clock selected from: LSI/LSE/HSI/HSE.

Below table shows the clock status (on/off/user) in each low-power mode.

Table 9 Clock description in different power modes

| Clocks | Run                             | LP run             | Sleep                           | LP sleep                        | Stop | Description                                        |

|--------|---------------------------------|--------------------|---------------------------------|---------------------------------|------|----------------------------------------------------|

| LSI    | User                            | On                 | User                            | User                            | User | 32KHz internal RC oscillator                       |

| LSE    |                                 | Selection          | (                               | L /                             |      | 32.768KHz crystal oscillator                       |

| LFCLK  |                                 | depends<br>on user |                                 |                                 | 2    | Switched low frequency Clock from LSI and LSE      |

| HSI    | On                              | User               | On                              | On                              | Off  | HSI RC 4-32MHz                                     |

| HSE    | Selection<br>depends<br>on user | User               | Selection<br>depends<br>on user | Selection<br>depends<br>on user | User | Up to 32MHz external clock                         |

| SYSCLK | On                              | On                 | On                              | On                              | Off  | Switched system clock from HSI, HSE and LFCLK      |

| FCLK   | On                              | On                 | On                              | On                              | Off  | AHB Free-running clock divided from SYSCLK         |

| HCLK   | On                              | On                 | Off                             | Off                             | Off  | AHB bus clock, which is used for CPU/MTP/SRAM/GPIO |

| SCLK   | On                              | On                 | On                              | On                              | Off  | CPU core system clock, which is used for NVIC      |

REV1.3 25 Copyright@ 2023Nanochap

| DCLK  | Dynamic | Dynamic | Dynamic | Dynamic | Off | CPU core debug clock, when there is no debug request, it's gated |

|-------|---------|---------|---------|---------|-----|------------------------------------------------------------------|

| PCLK  | On      | On      | On      | On      | Off | APB free-running clock                                           |

| PCLKG | Dynamic | Dynamic | Off     | Off     | Off | APB gated bus clock, when there is no APB cycle, it's gated      |

### **5.3.3** Clock Switch Sequence

When switching SYSCLK from HSI to HSE, configure as below sequence

- 1) Make sure HSE clock is running normally

- 2) Set SYSCLK SEL to 2'b01

- 3) Polling SYSCLK SWSTS to be 2'b01

- 4) Set HSI EN to 0

When switching SYSCLK from HSI to LFCLK, configure as below sequence

- 1) Make sure LFCLK is running normally, if LFCLK source need to be changed, do the LFCLK switch sequence firstly

- 2) Set SYSCLK\_SEL to 2'b1x

- 3) Polling SYSCLK\_SWSTS to be 2'b1x

- 4) Set HSI EN to 0

When switching LFCLK from LSI to LSE, configure as below sequence

26

- 5) Set both LSE OSCEN and LSE CLKEN to 1

- 6) Wait LSE stable (stable time to be confirmed)

- 7) Set LFCLK SEL to 1

- 8) Polling LFCLK SWSTS to be 1

- 9) Set LSI\_EN to 0

REV1.3

# 5.4 Registers

#### **Table 10 SYSCTRL Registers**

| Offset | Acronym    | Register Description                                    |  |  |  |

|--------|------------|---------------------------------------------------------|--|--|--|

| 00h    | CLK_CFG    | Clock Configuration Register                            |  |  |  |

| 04h    | HSI_CTRL   | HSI Control Register                                    |  |  |  |

| 08h    | LSI_CTRL   | LSI Control Register                                    |  |  |  |

| 0Ch    | LSE_CTRL   | LSE Control Register                                    |  |  |  |

| 10h    | AHB_CLKEN  | AHB Peripheral Clock Enable Register                    |  |  |  |

| 14h    | APB_CLKEN  | APB Peripheral Clock Enable Register                    |  |  |  |

| 18h    | PERI_CLKEN | Peripheral Working Clock Enable Register                |  |  |  |

| 1Ch    | SLP_PCLKEN | APB Peripheral Clock Enable in Sleep/Stop mode Register |  |  |  |

| 20h    | RST_CTRL   | Reset Control Register                                  |  |  |  |

| 24h    | RST_FLAG   | Reset Flag Register                                     |  |  |  |

| 28h    | PRST_KEY   | Peripheral Reset Enable Key Register                    |  |  |  |

| 2Ch    | AHB_RST    | AHB Peripheral Reset Register                           |  |  |  |

| 30h    | APB_RST    | APB Peripheral Reset Register                           |  |  |  |

| 34h    | SYS_CFG    | System Configuration Register                           |  |  |  |

| 38h    | PMU_CTRL   | PMU Control Register                                    |  |  |  |

#### Offset Address: 03-00h

#### **Clock Configuration Register**

| Bit   | Field Name | Attribute | Default | Field Description                                                                                                                           |

|-------|------------|-----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 31:18 | -          | RO        | 0       | Reserved                                                                                                                                    |

| 17:16 | MCO_SEL    | RW        | 0       | MCU clock output selection  00: HSI  01: HSE  10: LSI  11: LSE                                                                              |

| 15    | -          | RO        | 0       | Reserved                                                                                                                                    |

| 14:12 | APB_PRES   | RW        | 0       | APB clock prescaler  0xx: PCLK not divided  100: PCLK divided by 2  101: PCLK divided by 4  110: PCLK divided by 8  111: PCLK divided by 16 |

27

|              | DO                       |                                       |                                                                                  |

|--------------|--------------------------|---------------------------------------|----------------------------------------------------------------------------------|

| -            | RO                       | 0                                     | Reserved                                                                         |

| AHB_PRES     | RW                       | 0                                     | AHB clock prescaler                                                              |

|              |                          |                                       | 0xx: HCLK not divided                                                            |

|              |                          |                                       | 100: HCLK divided by 2                                                           |

|              |                          |                                       | 101: HCLK divided by 4                                                           |

|              |                          |                                       | 110: HCLK divided by 8                                                           |

|              |                          |                                       | 111: HCLK divided by 16                                                          |

| -            | RO                       | 0                                     | Reserved                                                                         |

| LFCLK_SWSTS  | RO                       | 0                                     | LFCLK switch status                                                              |

|              |                          | × ×                                   | 0: LSI as LFCLK                                                                  |

| ` /          |                          | 7                                     | 1: LSE as LFCLK                                                                  |

| LFCLK_SEL    | RW                       | 0                                     | LFCLK switch selection                                                           |

|              |                          |                                       | 0: LSI as LFCLK                                                                  |

|              |                          |                                       | 1: LSE as LFCLK                                                                  |

| SYSCLK_SWSTS | RO                       | 0                                     | System clock switch status                                                       |

|              |                          |                                       | 00: RCHF as system clock                                                         |

|              |                          |                                       | 01: EXTHF as system clock                                                        |

|              |                          |                                       | 1x: LFCLK as system clock                                                        |

| SYSCLK_SEL   | RW                       | 0                                     | System clock switch selection                                                    |

|              |                          |                                       | 00: HSI as system clock                                                          |

|              |                          |                                       | 01: HSE as system clock                                                          |

|              |                          |                                       | 1x: LFCLK as system clock                                                        |

|              |                          |                                       | The setting is forced by hardware to 00 (HSI selected) when MCU exits Stop mode. |

|              | - LFCLK_SWSTS  EFCLK_SEL | - RO  LFCLK_SWSTS RO  SYSCLK_SWSTS RO | - RO 0  LFCLK_SWSTS RO 0  LFCLK_SEL RW 0                                         |

#### Offset Address: 07-04h

#### **HSI Control Register**

| Bit  | Field Name | Attribute | Default | Field Description                                                     |

|------|------------|-----------|---------|-----------------------------------------------------------------------|

| 31:6 | -          | RO        | 0       | Reserved                                                              |

| 5:4  | HSI_FREC   | RW        | 01b     | HSI OSC frequency selection                                           |

|      |            |           |         | 00: 4MHz                                                              |

|      |            |           |         | 01: 8MHz                                                              |

|      | ,          |           |         | 10: 16MHz                                                             |

|      | 1          | \ \ \ \   |         | 11: 32MHz                                                             |

| 3:1  | × //       | RO        | -0      | Reserved                                                              |

| 0    | HSI_EN     | RW        | 1       | HSI OSC clock enable                                                  |

|      |            | C >       |         | Set and cleared by software.                                          |

|      |            |           |         | Cleared by hardware to stop HSI OSC when entering stop mode.          |

|      |            | <b>X</b>  |         | Forced by hardware to keep the HSI OSC ON when it is used directly or |

|      |            |           |         | indirectly as system clock (when leaving stop mode)                   |

|      |            |           |         | 0: HSI OSC OFF                                                        |

|      |            |           |         | 1: HSI OSC ON                                                         |

#### Offset Address: 0B-08h

#### **LSI Control Register**

| Bit  | Field Name | Attribute | Default | Field Description |

|------|------------|-----------|---------|-------------------|

| 31:1 | -          | RO        | 0       | Reserved          |

| 0    | LSI_EN     | RW        | 1       | LSI enable bit    |

|      |            |           |         | 0: disabled       |

|      |            |           |         | 1: enabled        |

#### Offset Address: 0F-0Ch

#### **LSE Control Register**

| Bit   | Field Name | Attribute | Default | Field Description               |

|-------|------------|-----------|---------|---------------------------------|

| 31:29 | -          | RO        | 0       | Reserved                        |

| 1     | LSE_CLKEN  | RW        | 0       | LSE clock enable bit            |

|       |            |           |         | 0: clock output disabled        |

|       |            |           |         | 1: clock output enabled         |

| 0     | LSE_OSCEN  | RW        | 0       | LSE oscillator enable bit       |

|       | / x 4      |           |         | 0: turn off the oscillator core |

|       | /          |           |         | 1: turn on the oscillator core  |

#### Offset Address: 13-10h

#### **AHB Peripheral Clock Enable Register**

| Bit  | Field Name         | Attribute | Default | Field Description                                                                                 |

|------|--------------------|-----------|---------|---------------------------------------------------------------------------------------------------|

| 31:4 | -                  | RO        | 0       | Reserved                                                                                          |

| 2:0  | AHB_PORT_CLKE<br>N | RW        | 111b    | Bit2: MTP register access HCLK enable bit  Bit1: EXTI HCLK enable bit  Bit0: GPIO HCLK enable bit |

#### Offset Address: 17-14h

#### **APB Peripheral Clock Enable Register**

| Bit   | Field Name    | Attribute | Default | Field Description                         |

|-------|---------------|-----------|---------|-------------------------------------------|

| 31:16 | -             | RO        | 0       | Reserved                                  |

| 15:0  | APB_PORT_CLKE | RW        | 0       | Bit15: RTC PCLK enable bit                |

|       |               |           |         | Bit14: Analog control PCLK enable bit     |

|       |               |           |         | Bit13: ADC control PCLK enable bit        |

|       |               |           |         | Bit12: Waveform generator PCLK enable bit |

|       |               |           |         | Bit11: LCD drive PCLK enable bit          |

|       |               |           |         | Bit10: Dual-timers PCLK enable bit        |

|       |               |           |         | Bit9: Timer 1 PCLK enable bit             |

Tel: 4008605922

|  |  | Bit8: Timer 0 PCLK enable bit |