## 1. 特性

• 8 路差分模数转换器 (ADC) 输入

• 优异的性能:

- 动态范围: 1kSPS 时为 122dB

64kSPS 时为 91dB

- 串扰: -110dB

- 总谐波失真(THD): 50Hz 和 60Hz 时为 -

116dB

• 模拟电源范围选项:

- 3V 至 5V (单极)

- ±2.5V (双极, 允许直流耦合)

数字: 1.8V 至 3.6V低功耗: 每通道 2mW

• 数据速率: 1, 2, 4, 8, 16, 32, 64 和 128kSPS

• 可编程增益: 1, 2, 3, 4, 6, 8, 12, 24

• 故障检测和器件测试功能

• SPI 数据接口和四个通用输入输出接口 (GPIO)

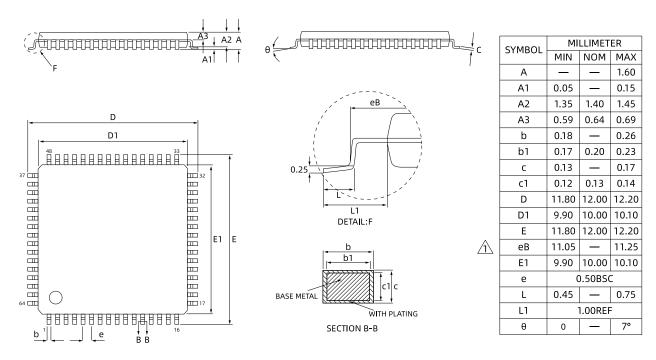

• 封装: LQFP-64

• 工作温度范围: -40°C 至 +105°C

## 2. 应用

电源保护: 断路器和继电器保护电能计量: 单相、多相和电能质量

• 电池测试系统 • 测试和测量

• 同步采样数据采集系统

## 3. 概述

LHA787X 是一系列多通道同步采样、24 位 Δ-Σ 模数转换器 (ADC),内置可编程增益放大器(PGA)、内部基准和振荡器。凭借 ADC 的宽动态范围、可扩展数据传输速率以及内部故障检测监测计,LHA787X 受到工业电源监测和保护以及测试和测量应用的青睐。真正的高阻抗输入支持LHA787X 直接与电阻分压器网络或电压互感器相连以测量线路电压或与电流互感器或罗戈夫斯基线圈相连来测量电流。借助于高集成度和出色的性能,LHA787X 系列产品可在大大降低尺寸、功耗和总体成本的前提下创建可升级的工业用电源系统。

LHA787X 在每通道上有一个灵活输入多路复用器, 此多路复用器被独立连接至内部生成信号以实现测试、温度、和故障检测。故障检测可在器件内部执行, 此器件使用集成的带有数模转换器 (DAC)控制的触发电平的比较器。LHA787X 运行的数据速率可高达 128kSPS。

完整的模拟前端 (AFE) 解决方案封装在 LQFP-64 封装内并且额定工业用温度范围为 -40℃至+105℃。

## 器件信息 (1)

| 器件型号    | 封装        | 封装尺寸(标称值)         |

|---------|-----------|-------------------|

| LHA787X | LQFP (64) | 10.00mm x 10.00mm |

(1) 要了解所有可用封装,请参见数据表末尾的可订购产品附录。

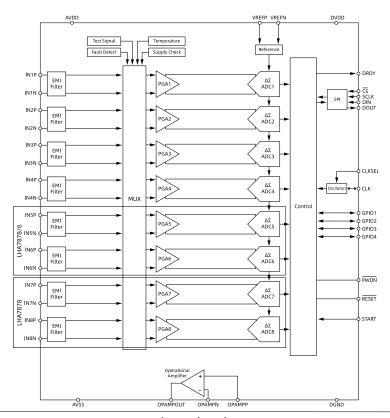

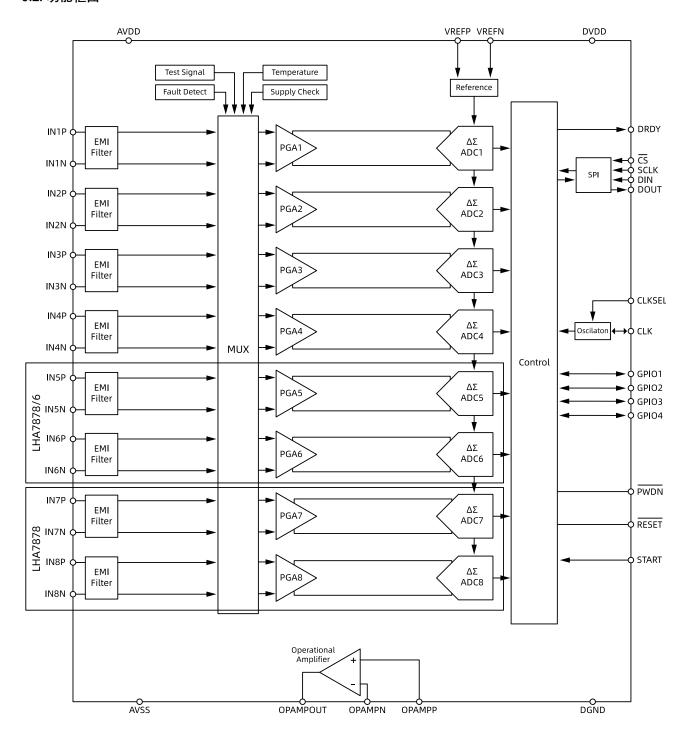

## 4. 功能框图

# 目录

| 1. | . 特性                         | 1   |

|----|------------------------------|-----|

| 2. | 应用                           | 1   |

| 3. | . 概述                         | 1   |

| 4. | . 功能框图                       | 1   |

| 5. | . 版本历史                       | 5   |

|    | . 引脚配置和功能                    |     |

|    | 、                            |     |

| 1. |                              |     |

|    | 7.1. 绝对最大额定值                 |     |

|    | 7.2. ESD 性能                  |     |

|    | 7.3. 推荐工作条件                  |     |

|    | 7.4. 热信息                     |     |

|    | 7.5. 电气特性                    |     |

|    | 7.6. 时间要求                    |     |

|    | 7.7. 开关特性                    |     |

|    | 7.8. 典型特征                    | 11  |

| 8. | . 参数测量信息                     | 13  |

|    | 8.1. 噪声测量                    | 13  |

| 9. | . 详细描述                       | 15  |

|    | O. 1. HIT :- 1.              | 1 - |

|    | 9.1. 概述                      |     |

|    | 9.2. 功能框图                    |     |

|    | 9.3. 功能描述                    |     |

|    | 9.3.1. 电磁干扰(EMI)滤波器          |     |

|    | 9.3.2. 输入多路选择器               |     |

|    | 9.3.2.2. 测试信号(TESTP 和 TESTN) |     |

|    | 9.3.2.3. 温度传感器(TEMPP TEMPN)  |     |

|    | 9.3.2.4. 电源测量(MVDDP, MVDDN)  |     |

|    | 9.3.3. 模拟输入                  |     |

|    | 9.3.4. PGA 设置和输入范围           |     |

|    | 9.3.4.1. 输入共模范围              |     |

|    | 9.3.5. DELTA SIGMA 调制器       |     |

|    | 9.3.6. CLOCK                 |     |

|    | 9.3.7. 数字抽取滤波器               |     |

|    | 9.3.8. 电压基准                  |     |

|    | 9.3.9. 输入超出范围检测              |     |

|    | 9.3.10. 通用数字 IO (GPIO)       |     |

|    | 5.6.10, 12/11 X 1 10 (OI 10) |     |

| 9.4. 设备切能模式                                        | 23 |

|----------------------------------------------------|----|

| 9.4.1. START                                       | 23 |

| 9.4.1.1. 建立时间                                      | 23 |

| 9.4.1.2. 输入信号阶跃                                    | 24 |

| 9.4.2. RESET (RESET)                               | 24 |

| 9.4.3. POWER-DOWN (PWDN)                           | 24 |

| 9.4.4. 连续转换模式                                      | 24 |

| 9.4.5. 数据检索                                        | 25 |

| 9.4.5.1. 数据就绪(DRDY)                                | 25 |

| 9.4.5.2. 回读数据                                      | 26 |

| 9.4.5.3. 状态字                                       | 26 |

| 9.4.5.4. 回读长度                                      | 26 |

| 9.5. 通讯                                            | 27 |

| 9.5.1. 数据格式                                        | 27 |

| 9.5.2. SPI 接口                                      | 27 |

| 9.5.2.1. SPI 选择( <u>CS</u> )                       | 27 |

| 9.5.2.2. 串行时钟(SCLK)                                | 27 |

| 9.5.2.3. 数据输入(DIN)                                 | 28 |

| 9.5.2.4. 数据输出(DOUT)                                | 28 |

| 9.5.3. SPI 命令定义                                    | 28 |

| 9.5.3.1. 发送多字节命令                                   | 29 |

| 9.5.3.2. 唤醒:退出待机模式                                 | 29 |

| 9.5.3.3. 待机:进入待机模式                                 | 29 |

| 9.5.3.4. RESET:将寄存器重置为默认值                          | 29 |

| 9.5.3.5. START:开始转换                                | 29 |

| 9.5.3.6. 停止:停止转换                                   | 29 |

| 9.5.3.7. OFFSETCAL:通道偏移校准                          | 29 |

| 9.5.3.8. RDATAC:启动读取数据连续模式                         | 30 |

| 9.5.3.9. SDATAC:停止读取数据连续模式                         | 30 |

| 9.5.3.10. RDATA:读取数据                               | 30 |

| 9.5.3.11. RREG:从寄存器读取                              | 31 |

| 9.5.3.12. WREG:写寄存器                                | 31 |

| 9.6. 寄存器列表                                         | 32 |

| 9.6.1. 寄存器说明                                       | 32 |

| 9.6.1.1. ID: ID 控制寄存器(工厂编程,只读)(地址=00H) [RESET=XXH] | 32 |

| 9.6.1.2. CONFIG1:配置寄存器 1 (地址=01H) [RESET=1EH]      | 33 |

| 9.6.1.3. CONFIG2:配置寄存器 2 (地址=02H) [RESET=C0H]      | 33 |

| 9.6.1.4. CONFIG3:配置寄存器 3 (地址=03H) [RESET=00]       | 34 |

| 9.6.1.5. 故障:故障检测控制寄存器(地址=04H) [复位=00H]             | 34 |

| 9.6.1.6. CHNSET:通道设置(地址=05H 至 0CH) [RESET=00H]     | 35 |

| 9.6.1.7. FAULT_STATP:故障检测正输入状态(地址=12H) [RESET=XXH] | 36 |

| 9.6.1.8. FAULT_STATN:故障检测负输入状态(地址=13H) [RESET=XXH] | 36 |

| 9.6.1.9. GPIO:通用 IO 寄存器(地址=14H) [RESET=0FH] | 37 |

|---------------------------------------------|----|

| 10. 应用和实现                                   | 37 |

| 10.1. 应用信息                                  | 37 |

| 10.1.1. 未使用的输入和输出引脚                         |    |

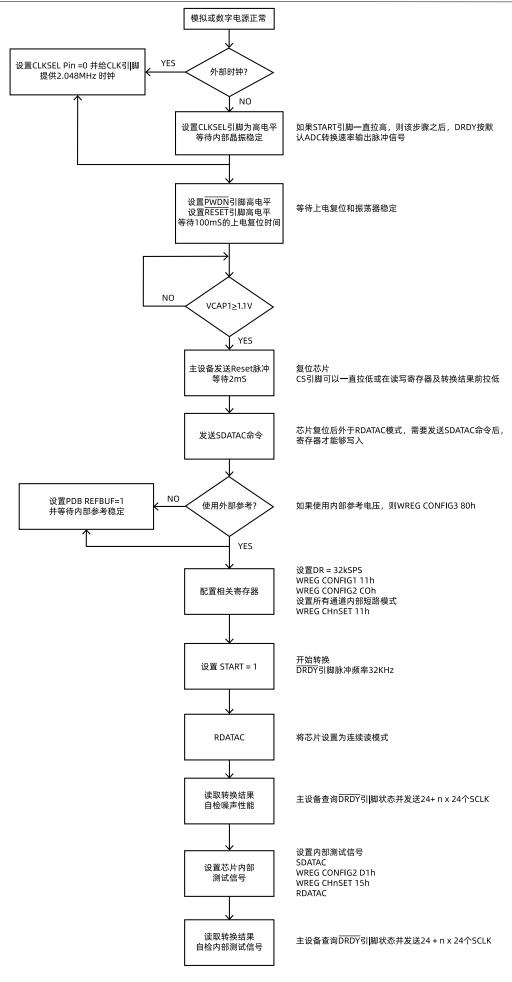

| 10.1.2. 配置芯片可以进行基本数据采样                      | 38 |

| 10.1.3. 多器件配置                               | 40 |

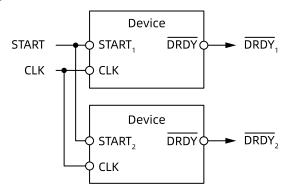

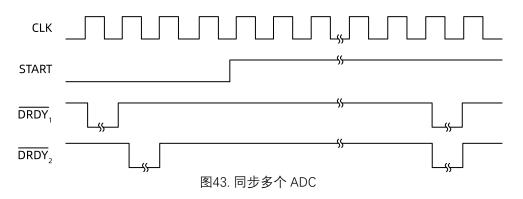

| 10.1.3.1. 同步多个器件                            | 40 |

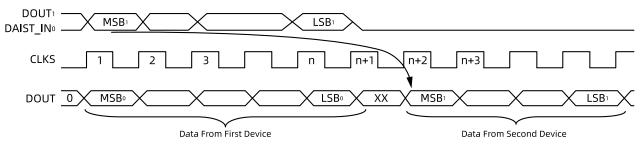

| 10.1.3.2. 标准配置                              | 40 |

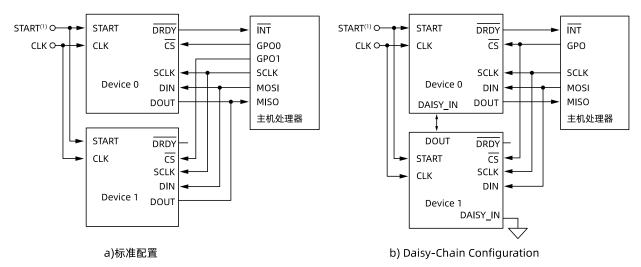

| 10.1.3.3. 菊花链配置                             | 40 |

| 11. 电源建议                                    | 42 |

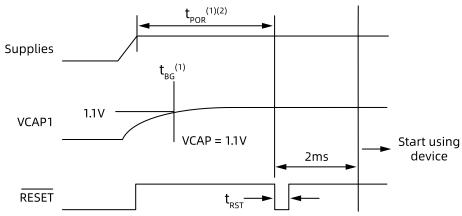

| 11.1. 上电时序                                  | 42 |

| 11.2. 推荐的外部电容值                              | 42 |

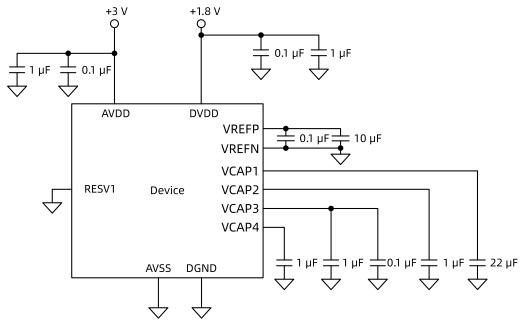

| 11.3. 单极电源的设备连接                             | 43 |

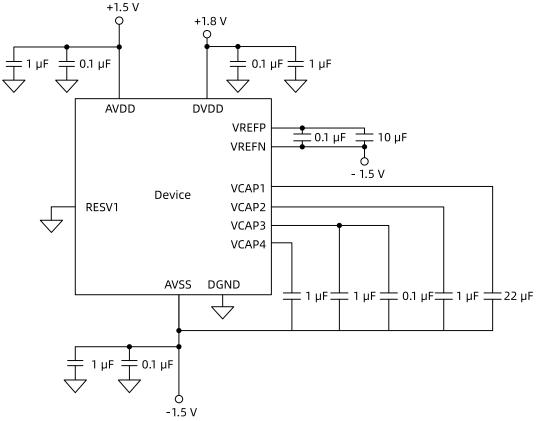

| 11.4. 用于双极电源的器件连接                           | 43 |

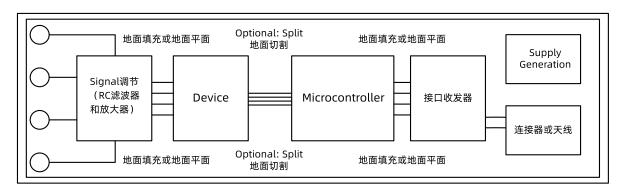

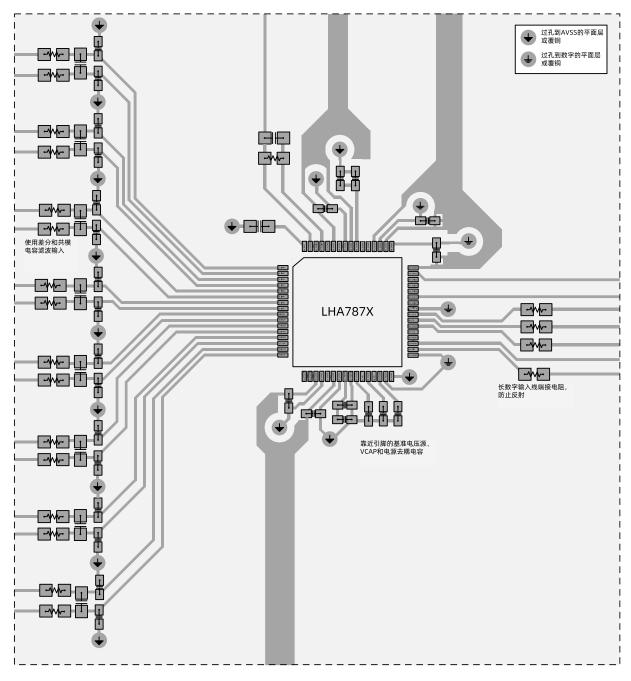

| 12. LAYOUT                                  | 44 |

| 12.1. 设计指引                                  | 44 |

| 12.2. 布局示例                                  | 45 |

| 13. 封装和可订购信息                                | 46 |

| 14. 采购指南                                    | 46 |

# 5. 版本历史

| 版本号   | 日期          | 更新内容                                                                                           |

|-------|-------------|------------------------------------------------------------------------------------------------|

| PreA  | 2023年3月13日  | 初版                                                                                             |

| PreB  | 2023年6月2日   | 更新寄存器相关内容                                                                                      |

| PreC  | 2023年6月17日  | 1. 增加噪声测量数据<br>2. 增加 8.8 典型特征<br>3. 更新 8.5 电气特性<br>4. 新增图片表格                                   |

| PreD  | 2023年11月10日 | 1. 修改图 42 图 49 图 53<br>2. 增加包装信息<br>3. 修改寄存器位属性<br>4. 修改 7.5 电气特性指标<br>5. 修改部分描述<br>6. 增加小包装规格 |

| Rev.A | 2024年4月10日  | 正式版                                                                                            |

| Rev.B | 2024年10月9日  | 1. 更改 Pin 53, 54 脚描述 2. 修改表 4 中 模拟输入的共模计算公式 3. 删除表 40 中 PIN 54 脚 4. 修改图 50 中 53, 54 脚处的外接电容    |

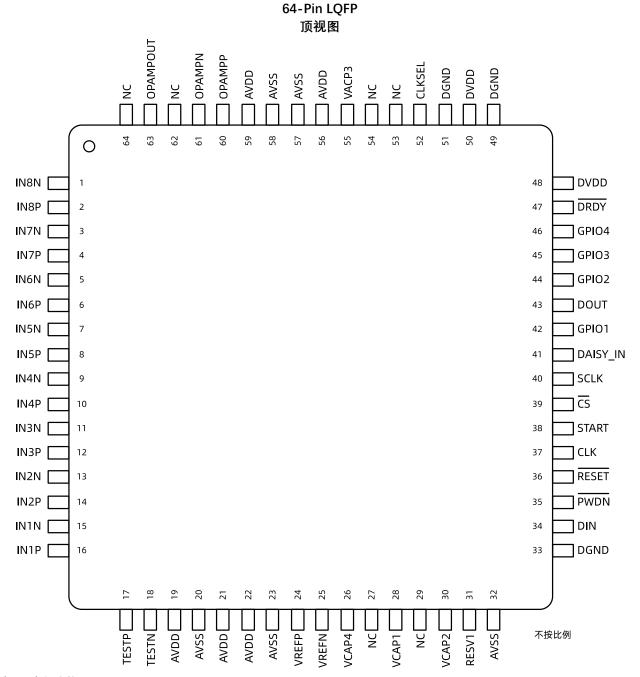

## 6. 引脚配置和功能

表1. 引脚功能

| PIN      |                    | 1/0  | DESCRIPTION                               |  |

|----------|--------------------|------|-------------------------------------------|--|

| NAME     | NO.                | 1/0  | DESCRIPTION                               |  |

| AVDD     | 19, 21, 22, 56, 59 | 电源   | 模拟电源。每个 AVDD 管脚连接一个 1µF(或更大)电容器到 AVSS。    |  |

| AVSS     | 20, 23, 32, 57, 58 | 电源   | 模拟地                                       |  |

|          | 39                 | 数字输入 | 芯片选择; 低有效                                 |  |

| CLK      | 37                 | 数字输入 | 主时钟输入。如果未使用,请连接到 DGND。                    |  |

| CLKSEL   | 52                 | 数字输入 | 主时钟选择                                     |  |

| DAISY_IN | 41                 | 数字输入 | 菊花链输入。如果未使用,请连接到 DGND。                    |  |

| DGND     | 33, 49, 51         | 电源   | 数字地                                       |  |

| DIN      | 34                 | 数字输入 | 串行数据输入                                    |  |

| DOUT     | 43                 | 数字输出 | 串行数据输出                                    |  |

| DRDY     | 47                 | 数字输出 | 数据就绪;低电平有效。如果未使用,请使用 10-KΩ电阻连接到<br>DGND。  |  |

| DVDD     | 48, 50             | 电源   | 数字核心电源。每个 DVDD 引脚连接一个 1µF (或更大)电容器到 DGND。 |  |

|                     | PIN                   | I/O                                   | DESCRIPTION                              |

|---------------------|-----------------------|---------------------------------------|------------------------------------------|

| NAME                | NO.                   |                                       |                                          |

| GPIO1               | 42                    | 数字输入/输出                               | 通用输入输出引脚 1。如果未使用,请使用 10-KΩ电阻连接到<br>DGND。 |

| GPIO2               | 44                    | 数字输入/输出                               | 通用输入输出引脚 2。如果未使用,请使用 10-KΩ电阻连接到<br>DGND。 |

| GPIO3               | 45                    | 数字输入/输出                               | 通用输入输出引脚 3。如果未使用,请使用 10-KΩ电阻连接到<br>DGND。 |

| GPIO4               | 46                    | 数字输入/输出                               | 通用输入输出引脚 4。如果未使用,请使用 10-KΩ电阻连接到<br>DGND。 |

| IN1N <sup>(1)</sup> | 15                    | 模拟输入                                  | 负模拟输入 1                                  |

| IN1P <sup>(1)</sup> | 16                    | 模拟输入                                  | 正模拟输入 1                                  |

| IN2N <sup>(1)</sup> | 13                    | 模拟输入                                  | 负模拟输入 2                                  |

| IN2P (1)            | 14                    | 模拟输入                                  | 正模拟输入 2                                  |

| IN3N (1)            | 11                    | 模拟输入                                  | 负模拟输入 3                                  |

| IN3P <sup>(1)</sup> | 12                    | 模拟输入                                  | 正模拟输入 3                                  |

| IN4N (1)            | 9                     | 模拟输入                                  | 负模拟输入 4                                  |

| IN4P (1)            | 10                    | <br>模拟输入                              | 正模拟输入 4                                  |

| IN5N (1)            | 7                     | 模拟输入                                  | 负模拟输入 5 (仅限 LHA7876 和 LHA7878)           |

| IN5P (1)            | 8                     | 模拟输入                                  | 正模拟输入 5 (仅限 LHA7876 和 LHA7878)           |

| IN6N (1)            | 5                     | 模拟输入                                  | 负模拟输入 6 (仅限 LHA7876 和 LHA7878)           |

| IN6P (1)            | 6                     | 模拟输入                                  | 正模拟输入 6 (仅限 LHA7876 和 LHA7878)           |

| IN7N <sup>(1)</sup> | 3                     | 模拟输入                                  | 负模拟输入 7 (仅限 LHA7878)                     |

| IN7P <sup>(1)</sup> | 4                     | 模拟输入                                  | 正模拟输入 7 (仅限 LHA7878)                     |

| IN8N (1)            | 1                     | 模拟输入                                  | 负模拟输入 8(仅限 LHA7878)                      |

| IN8P (1)            | 2                     | 模拟输入                                  | 正模拟输入 8(仅 LHA7878)                       |

| NC                  | 27, 29, 53, 54 62, 64 | ————————————————————————————————————— | 没有连接,保持浮空。可使用 10-KΩ或更高电阻连接到 AVDD 或AVSS。  |

| OPAMPN              | 61                    | 模拟输入                                  | 运算放大器反相输入;如果未使用,则保持浮空,并关闭运算放大器。          |

| OPAMPP              | 60                    | 模拟输入                                  | 运算放大器同相输入;如果未使用,则保持浮空,并关闭运算放大器。          |

| OPAMPOUT            | 63                    | 模拟输出                                  | 运算放大器输出;如果未使用,请保持浮空,并关闭运算放大器。            |

| PWDN                | 35                    | 数字输入                                  | 掉电;低电平有效                                 |

| RESET               | 36                    | 数字输入                                  | 系统复位;低电平有效                               |

| RESV1               | 31                    | 数字输入                                  | 保留以备将来使用。直接连接到 DGND。                     |

| SCLK                | 40                    | 数字输入                                  | 串行时钟输入                                   |

| START               | 38                    | 数字输入                                  | 开始转换                                     |

| TESTN               | 18                    | 模拟输入/输出                               | 测试信号,负引脚。有关未使用的引脚,请参阅未使用的输入和输 部分。        |

| TESTP               | 17                    | 模拟输入/输出                               | 测试信号,正引脚。有关未使用的引脚,请参阅未使用的输入和输部分。         |

| VCAP1               | 28                    | 模拟输出                                  | 模拟旁路电容。将一个 22μF 电容连接到 AVSS。              |

| VCAP2               | 30                    | 模拟输出                                  | 模拟旁路电容。将 1μF 电容连接到 AVSS。                 |

| VCAP3               | 55                    | 模拟输出                                  | 旁路电容, 1μF 电容器连接到 DGND。                   |

| VCAP4               | 26                    | 模拟输出                                  | 模拟旁路电容。将 1μF 电容连接到 AVSS。                 |

| VREFN               | 25                    | 模拟输入                                  | 负参考电压。连接 AVSS。                           |

| VREFP               | 24                    | 模拟输入/输出                               | 正参考电压。连接一个>=10µF 电容到 VREFN。              |

<sup>(1)</sup> 将任何未使用或掉电的模拟输入引脚连接到 AVDD。

# 7. 规格

## 7.1. 绝对最大额定值

表2. 在工作环境温度范围内(除非另有说明) (1)

|        |              | MIN        | MAX        | UNIT |

|--------|--------------|------------|------------|------|

|        | AVDD to AVSS | -0.3       | 5.5        | V    |

| 电源电压   | AVSS to DGND | -3         | 0.2        | V    |

|        | DVDD to DGND | -0.3       | 3.9        | V    |

| 模拟输入电压 | 模拟输入到 AVSS   | AVSS - 0.3 | AVDD + 0.3 | V    |

| 数字输入电压 | 数字输入到 DVDD   | DGND-0.3   | DVDD + 0.3 | V    |

|        |                  | MIN  | MAX | UNIT |

|--------|------------------|------|-----|------|

| 输入电流   | 短暂的              | -100 | 100 | mΛ   |

| 期八七 // | 连续,除电源引脚外的所有其他引脚 | -10  | 10  | mA   |

| 温度     | 结温, Tj           |      | 150 | ٥,   |

| /皿/支   | 存储温度, Tstg       | -60  | 150 | C    |

<sup>(1)</sup> 超过绝对最大额定值所列的应力可能会对器件造成永久性损坏。这些只是压力额定值,并不意味着设备在这些或任何其他条件下的功能操作,超出了推荐的操作条件。长时间暴露在绝对最大额定条件下可能会影响器件的可靠性。

#### 7.2. ESD 性能

#### 表3. 性能

|              |                                     | VALUE | UNIT |

|--------------|-------------------------------------|-------|------|

|              | 人体模型(HBM)根据 ANSIESDAJEDECJS-001 (1) | ±1000 |      |

| V (ESD) 静电放电 | 充电设备型号(CDM),符合 JEDEC 规范 JESD22      | ±500  | V    |

<sup>(1)</sup> JEDEC 文件 JEP155 指出,500-VHBM 允许使用标准 ESD 控制过程进行安全制造。

#### 7.3. 推荐工作条件

表4. 在工作环境温度范围 (除非另有说明)

|                              |                   |                                        | MIN      | NOM         | MAX       | UNIT    |

|------------------------------|-------------------|----------------------------------------|----------|-------------|-----------|---------|

| 电源                           |                   |                                        |          |             |           |         |

| AVDD                         | 模拟电源              | AVDD to AVSS                           | 2.7      | 5.0         | 5.25      | V       |

| DVDD                         | 数字电源              | DVDD to DGND                           | 1.7      | 1.8         | 3.6       | V       |

|                              | 模拟数字电源            | AVDD to DVDD                           | -2.1     |             | 3.6       | V       |

| 模拟输入                         |                   |                                        |          |             |           |         |

| VIN                          | 差分输入电压            | VIN = VINxP) - V(INxN)                 | -VREF/增益 |             | VREF/增益   | V       |

| $V_{\text{CM}}$              | 共模输入电压            | VCM = (V(INxP) + VINxN)) / 2           | 请参阅 9.3  | .4.1 输入共模范围 | 部分        | V       |

| 电压基准输                        | <b>介入</b>         |                                        |          |             |           |         |

| VREF                         | 参考输入申压            | AVDD = 3 V, VREF = (VVREFP - VVREFN)   | 1        | 2.5         | AVDD      | V       |

| VKEF                         | 参考期八中压            | AVDD = 5 V, VREF = (VVREFP - VVREFN)   | 1        | 4           | AVDD      | V       |

| VREFN                        | 负参考输入             |                                        | AVSS     |             | V         |         |

| VREFP                        | 正输入               |                                        | AVDD -3  | AVSS + 2.5  | AVDD      | V       |

| 外部时钟源                        | <u> </u>          |                                        |          |             |           |         |

| ť                            | → □→6市#五 <b>②</b> | CLKSEL pin = 0, (AVDD -<br>AVSS) = 3 V | 1.7      | 2.048       | 2.25      | NAL I - |

| $f_{\scriptscriptstyle CLK}$ | 主时钟频率             | CLKSEL pin = 0, (AVDD -<br>AVSS) = 5 V | 1.0      | 2.048       | 2.25      | MHz     |

| 数字输入                         |                   | ,                                      |          |             |           |         |

|                              | 输入电压              |                                        | DGND-0.1 |             | DVDD+ 0.1 | V       |

| 温度范围                         |                   |                                        |          |             |           |         |

| TA                           | 工作环境温度            |                                        | -40      |             | 105       | °C      |

#### 7.4. 热信息

表5. 热信息

|                       |           | LHA787X |      |

|-----------------------|-----------|---------|------|

|                       | 热指标       | LQFP    | UNIT |

|                       |           | 64 PINS |      |

| R <sub>ja</sub>       | 结-环境热阻    | 35      | °C/W |

| R <sub>jc</sub> (top) | 结对壳(顶部)热阻 | 31      | °C/W |

| R <sub>jb</sub>       | 结对板热阻     | 26      | °C/W |

| W <sub>jt</sub>       | 结到顶特性参数   | 0.1     | °C/W |

| W <sub>jb</sub>       | 结对板特性参数   | NA      | °C/W |

| R <sub>JC</sub> (bot) | 结对壳(底部)热阻 | NA      | °C/W |

## 7.5. 电气特性

所有规格均为 DVDD=1.8V、AVDD=3V、AVSS=0V、VREF=2.4V、外部 fclk=2.048MHz、数据速率=8kSPS 和增益等于 1,除非另有说明。

<sup>(2)</sup> JEDEC 文件 JEP157 指出, 250-VCDM 允许使用标准 ESD 控制过程进行安全制造。

表6 电气特性

| PARAMETER             | 测试条                        | 件                                                 | MIN   | TYP               | MAX   | UNIT     |

|-----------------------|----------------------------|---------------------------------------------------|-------|-------------------|-------|----------|

| 模拟输入                  |                            |                                                   |       |                   |       |          |

| Cj 输入电容               |                            |                                                   |       | 20                |       | pF       |

| l <sub>B</sub> 输入偏置电流 | 正常范围内的                     | PGA 输出                                            |       | 2                 |       | nA       |

| 直流输入阻抗                |                            |                                                   |       | 500               |       | МΩ       |

| PGA                   |                            |                                                   |       |                   |       |          |

| 增益设置                  |                            |                                                   |       | 1,2,3,4,6,8,12,24 |       |          |

| ADC 性能                |                            |                                                   |       |                   |       |          |

| DR 数据速率               | $f_{cLK} = 2.048$          | MHz                                               | 1     |                   | 128   | kSPS     |

| 分辨率                   | DR = 1kSPS, 2kSPS, 4kSF    | PS, 8kSPS,16kSPS                                  | 24    |                   |       | Bits     |

| 刀折牛                   | DR = 32kSPS, 64 kS         | SPS, 128 kSPS                                     | 24    |                   |       | Bits     |

| 通道性能(DC 性能)           |                            |                                                   |       |                   |       |          |

| INL 积分非线性             | 全输入范                       | 围                                                 |       | 4                 |       | ppm      |

|                       | G = 1                      | G = 1                                             |       |                   |       | dB       |

| 动态范围                  | 1 以外的增殖                    | 1 以外的增益设置                                         |       |                   |       |          |

| 偏移误差                  |                            |                                                   |       | 30                |       | μV       |

| 偏移误差漂移                |                            |                                                   |       | 0.05              |       | μV/°C    |

| 增益误差                  | 排除电压基                      |                                                   |       | 0.1%              |       | 1        |

| 增益漂移                  | 排除电压基                      |                                                   |       | 1                 |       | ppm/°(   |

| 通道之间的增益匹配             |                            |                                                   |       | 0.2               |       | % of FS  |

| 通道性能(AC 性能)           |                            |                                                   |       |                   |       |          |

| CMRR 共模抑制比            | f <sub>см</sub> = 50 Hz an | $f_{CM} = 50 \text{ Hz and } 60 \text{ Hz}^{(1)}$ |       | -115              |       | dB       |

| PSRR 电源抑制比            | f <sub>PS</sub> = 50 Hz an | d 60 Hz                                           |       | -102              |       | dB       |

| 通道串扰                  | f <sub>IN</sub> =50Hz 和    | 60Hz                                              |       | -110              |       | dB       |

|                       | 2000 1 寸大世田 1 秒            | 3000:1 动态范围,1 秒<br>W量(Var)                        |       | 0.006%            |       |          |

| 精度                    | 3000:1                     | $AVDD = 5 V, V_{REF} = 4 V$                       |       | 0.004%            |       |          |

| SNR 信噪比               | f <sub>№</sub> =50Hz 和 60H |                                                   |       | 114               |       | dB       |

| THD 总谐波失真             | 10 Hz, 0.5                 |                                                   |       | -116              |       | dB       |

| 内部参考                  | <u> </u>                   |                                                   |       | l                 |       | <u> </u> |

|                       | $T_A = 25$ °C, $V_{REF}$   | = 2.4 V                                           | 2.395 | 2.4               | 2.405 | V        |

| V <sub>REF</sub> 輸出电压 | $TA = 25^{\circ}C, V_{B}$  |                                                   |       | 4                 |       | V        |

| V <sub>REF</sub> 精度   | ·                          |                                                   |       | ±0.2%             |       |          |

| 温度漂移                  | $T_A = -40^{\circ}C$ to    | +105°C                                            |       | 20                |       | ppm/°(   |

| Start-up time         | 稳定到 0                      | .2%                                               |       | 150               |       | mS       |

| 外部参考                  |                            |                                                   |       |                   |       | l l      |

| 输入阻抗                  |                            |                                                   |       | 6                 |       | kΩ       |

| 内部振荡器                 |                            |                                                   |       |                   |       | l .      |

|                       |                            |                                                   |       | ±2%               |       |          |

| 精度                    | $T_A = 25^{\circ}$         | °C                                                |       |                   | ±0.5% |          |

|                       | $T_A = -40^{\circ}C$ to    | T <sub>A</sub> = -40°C to 105°C                   |       |                   | 2.5%  |          |

| 内部振荡器时钟频率             | 标称频率                       | 茶                                                 |       | 2.048             |       | MHz      |

| 内部振荡器启动时间             |                            |                                                   |       | 20                |       | μS       |

| 内部振荡器功耗               |                            |                                                   |       | 60                |       | μW       |

| 故障检测和报警               |                            |                                                   |       |                   |       |          |

| 比较器阈值精度               |                            |                                                   |       | ±30               |       | mV       |

<sup>(1)</sup> 用(AVSS+0.3V)至(AVDD-0.3V)的共模信号测量 CMRR。指示的值是八个通道中的最小值。

所有规格均为 DVDD=1.8V、AVDD=3V、AVSS=0V、VREF=2.4V、外部 fcix=2.048MHz、数据速率=8kSPS 和增益=1,除非另有说明。

表7. 电气特性

| PARAMETER | 测试条件                      | MIN | TYP | MAX | UNIT           |

|-----------|---------------------------|-----|-----|-----|----------------|

| 运算放大器     |                           |     |     |     |                |

| 总噪音       | 0.1 Hz to 250 Hz          |     | 4   |     | μVrms          |

| 噪音密度      | 2 kHz                     |     | 50  |     | nV/√ <i>Hz</i> |

| GBP 增益带宽积 | 50 kΩ    10-pF load       |     | 580 |     | kHz            |

| SR 压摆率    | 50 kΩ    10-pF load       |     | 0.2 |     | V/µS           |

| 负载电流      |                           |     | 50  |     | μΑ             |

| THD 总谐波失真 | $f_{IN} = 100 \text{ Hz}$ |     | 70  |     | dB             |

|                              | PA         | RAME    | TER         | 测试条件                                                  | MIN         | TYP                                | MAX         | UNIT  |

|------------------------------|------------|---------|-------------|-------------------------------------------------------|-------------|------------------------------------|-------------|-------|

| 共植                           | 莫输入范       | 围       |             |                                                       | AVSS +0.3   |                                    | AVDD -0.55  | V     |

| 静る                           | 5功耗        |         |             |                                                       |             | 14                                 |             | μΑ    |

| 系统                           | 性视器        | :       |             | 1                                                     |             | •                                  | •           | II.   |

| 山山                           | 原监测误       | ¥       | Analog      |                                                       |             | 2%                                 |             |       |

| 电源                           | 品测庆        | 左       | Digital     |                                                       |             | 2%                                 |             |       |

| 芯片                           | <b>冷醒</b>  |         |             | 从上电到 DRDY 变低                                          |             | 150                                |             | mS    |

|                              |            |         |             | 待机模式                                                  |             | 31.25                              |             | μS    |

| 温度                           | ま 传感器      | 寺 数     | Voltage     | T <sub>A</sub> = 25°C                                 |             | 145                                |             | mV    |

|                              |            |         | Coefficient |                                                       |             | 490                                |             | μV/°C |

| 自测                           | 训试信号       |         |             |                                                       |             |                                    | 1           |       |

| 信된                           | 景频率        |         |             | 有关设置,请参阅寄存器部分                                         |             | f <sub>cLK</sub> / 2 <sup>21</sup> |             | Hz    |

| ін .                         | ,,,,       |         |             | 1770年,2793日 111177                                    |             | f <sub>cLK</sub> / 2 <sup>20</sup> |             |       |

| 信号                           | 电压         |         |             | 有关设置,请参阅寄存器部分                                         |             | ±Vref/1000                         |             | V     |

| ** -                         | 1 tA \ 1⊓  | #Aili/F | DVDD=1.8V 至 | 5.2.00                                                |             | ±Vref/1000                         |             |       |

| <b>数</b> ∃<br>V <sub>H</sub> | 逻辑电        |         | High        | 3.60)                                                 | 0.8 DVDD    |                                    | DVDD+0.1    | V     |

| V <sub>IL</sub>              | を押を<br>输入电 |         | Low         |                                                       | -0.1        |                                    | 0.2 DVDD    | V     |

| V <sub>IL</sub>              | 逻辑电        |         |             | I <sub>QH</sub> = -500 pA                             | 0.9 DVDD    |                                    | 0.2 0 0 0 0 | V     |

| Vol                          | を押で<br>輸出  |         | High<br>Low | $I_{QH} = -300 \text{ pA}$ $I_{OL} = +500 \text{ pA}$ | 0.9 0 0 0 0 |                                    | 0.1 DVDD    | V     |

|                              | 入电流        |         | LOW         | 0 V < V <sub>DigitalInput</sub> < DVDD                | -10         |                                    | 10          | μΑ    |

|                              |            |         | (大器关闭)      | 0 V V Digitalinput V D V D D                          | -10         |                                    | 10          | μΛ    |

|                              | K-0/IL (   | C##     | ()(HI)(P))  | AVDD - AVSS = 3 V                                     |             | 5.8                                | R           | mA    |

| $I_{AVDD}$                   |            |         |             | AVDD - AVSS = 5V                                      |             | 6.9                                |             | mA    |

|                              |            | 正常      | 模式          | DVDD = 3.3 V                                          |             | 1.2                                |             | mA    |

| I <sub>DVDD</sub>            |            |         |             | DVDD = 3.3 V<br>DVDD = 1.8 V                          |             | 1.0                                |             | mA    |

| 功非                           | E(模拟       | 电源=     | 3V)         | 1                                                     |             |                                    |             | l l   |

|                              |            |         |             | 正常模式                                                  |             | 10.                                | .6          | mW    |

|                              |            | L       | -HA7874     | 关断模式                                                  |             | 5                                  |             | μW    |

|                              |            |         |             | 待机模式                                                  |             | 0.3                                | 3           | mW    |

|                              |            |         |             | 正常模式                                                  |             | 13.                                | .7          | mW    |

| 静态                           | 5功耗        | l       | -HA7876     | 关断模式                                                  |             | 5                                  |             | μW    |

|                              |            |         |             | 待机模式                                                  |             | 0.3                                | 3           | mW    |

|                              |            |         |             | 正常模式                                                  |             | 17.                                | .4          | mW    |

|                              |            | L       | -HA7878     | 关断模式                                                  |             | 5                                  |             | μW    |

|                              |            |         |             | 待机模式                                                  |             | 0.3                                | 3           | mW    |

| 功耗                           | E(模拟       | 电源=     | 5V)         |                                                       |             |                                    |             |       |

|                              | Ţ          |         |             | 正常模式                                                  |             | 24.                                |             | mW    |

|                              |            | LHA7874 |             | 关断模式                                                  |             | 10                                 |             | μW    |

|                              | ļ          |         |             | 待机模式                                                  |             | 2.0                                |             | mW    |

|                              |            |         |             | 正常模式                                                  |             | 29.                                |             | mW    |

| 静态                           | 5功耗        | l       | -HA7876     | 关断模式                                                  |             | 10                                 |             | μW    |

|                              | ļ          |         |             | 待机模式                                                  |             | 2.0                                |             | mW    |

|                              |            |         |             | 正常模式                                                  |             | 34.                                |             | mW    |

|                              |            | L       | -HA7878     | 关断模式                                                  |             | 10                                 |             | μW    |

|                              |            |         |             | 待机模式                                                  |             | 2.0                                | 5           | mW    |

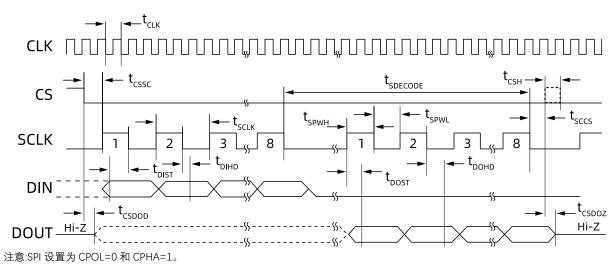

## 7.6. 时间要求

表8. 在工作环境温度范围内,DVDD=1.7V 至 3.6V (除非另有说明)

|                      |                          | 2.7 V < DVI | DD < 3.6 V | 1.7 V< DV | DD <2.0 V | UNIT  |

|----------------------|--------------------------|-------------|------------|-----------|-----------|-------|

|                      |                          | MIN         | MAX        | MIN       | MAX       | OINIT |

| tcik                 | 主时钟周期                    | 444         | 588        | 444       | 588       | ns    |

| tcssc                | 延迟时间,CS下降沿后的第一个 SCLK 上升沿 | 6           |            | 17        |           | ns    |

| t <sub>SCLK</sub>    | SCLK period              | 28          |            | 33        |           | ns    |

| t <sub>SPWH, L</sub> | 脉冲持续时间,SCLK 高或低          | 15          |            | 25        |           | ns    |

| t <sub>DIST</sub>    | 建立时间,DIN 在 SCLK 下降沿之前有效  | 10          |            | 10        |           | ns    |

| t <sub>DIHD</sub>    | 保持时间,DIN 在 SCLK 下降沿后有效   | 10          |            | 11        |           | ns    |

|                       |                             | 2.7 V < DV | DD < 3.6 V | 1.7 V< DV | DD <2.0 V | UNIT                         |

|-----------------------|-----------------------------|------------|------------|-----------|-----------|------------------------------|

|                       |                             | MIN        | MAX        | MIN       | MAX       | OIVIT                        |

| t <sub>сsн</sub>      | <br>CS 高电平脉冲时间              | 2          |            | 2         |           | tclk                         |

| t <sub>sccs</sub>     | —<br>延迟时间,第8个SCLK下降沿至CS高电平  | 4          |            | 4         |           | t <sub>clk</sub>             |

| t <sub>SDECODE</sub>  | 命令解码时间                      | 4          |            | 4         |           | $t_{\scriptscriptstyle CLK}$ |

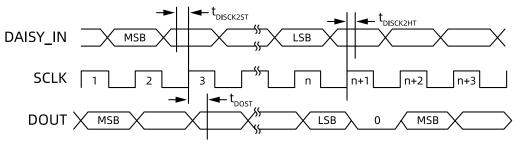

| t <sub>DISCK2ST</sub> | 建立时间,DAISYIN 在 SCLK 下降沿之前有效 | 10         |            | 10        |           | ns                           |

| t <sub>DISCK2HT</sub> | 保持时间,SCLK 下降沿后 DAISYIN 有效   | 10         |            | 10        |           | ns                           |

#### 7.7. 开关特性

表9. 在工作环境温度范围内,DVDD=1.7V 至 3.6V, DOUT 上的负载=20pF||100K0hm (除非另有说明)

|                   | PARAMETER                 | 2.7 V < DV | DD < 3.6 V | 1.7 V< DV | UNIT |      |

|-------------------|---------------------------|------------|------------|-----------|------|------|

|                   | PARAIVIETER               | MIN        | MAX        | MIN       | MAX  | UNII |

| tcsdod            | 性播延迟时间,CS下降沿到 DOUT 驱动     | 10         |            | 20        |      | ns   |

| t <sub>DOST</sub> | 传播延迟时间,SCLK 上升沿到有效的新 DOUT |            | 17         |           | 32   | ns   |

| t <sub>D0HD</sub> | 保持时间,SCLK 下降沿到无效 DOUT     | 10         |            | 10        |      | ns   |

| tcspoz            |                           |            | 10         |           | 20   | ns   |

图1. 串行接口定时

(1) n=通道数 x 分辨率+24 位。通道数为 8; 分辨率为 24 位。

图2. 菊花链接口时序

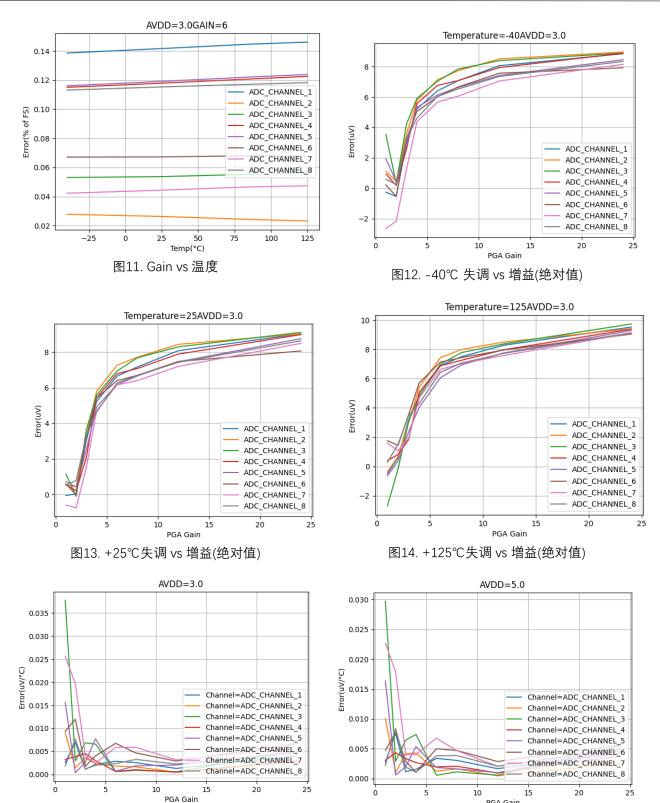

#### 7.8. 典型特征

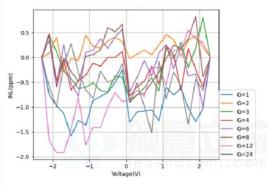

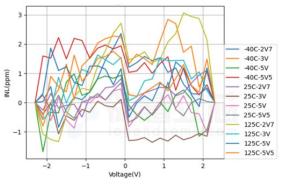

除非另有说明,否则所有曲线均处于 TA=25°C, AVDD=3V, AVSS=0V, DVDD=1.8V,部 VREFP=2.4V,VREFN =AVSS,外部 时钟=2.048MHz,数据速率=8kSPS 和增益=1。

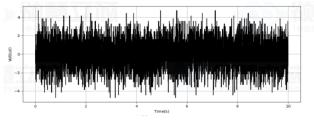

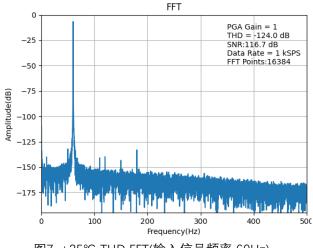

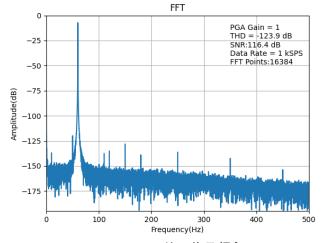

$\label{eq:avdd} AVDD=3V, AVSS=0V, DVDD=1.8V, internal\ VREFP=2.4V, VREFN=AVSS, external\ clock=2.048MHz\ data\ rate=1\ kSPS,\ gain=1$

图3. 输入参考噪声

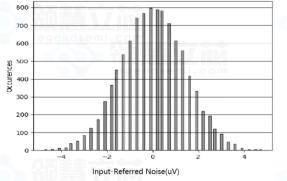

AVDD=3V,AVSS=0V,DVDD=1.8V,internal VREFP=2.4V,VREFN=AVSS,external clock= 2.048MHz data rate=1 kSPs, gain=1

图4. 噪声直方图

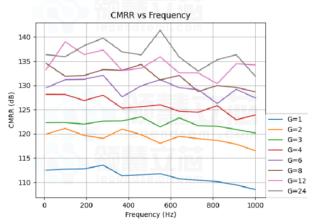

图5. CMRR vs 频率

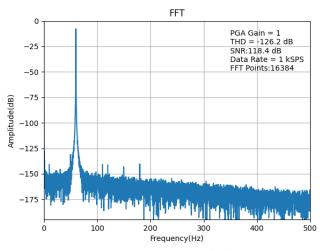

图6. -40℃ THD FFT(输入信号频率 60Hz)

图7. +25℃ THD FFT(输入信号频率 60Hz)

图8. +125℃ THD FFT(输入信号频率 60Hz)

$\label{eq:AVDD=3.3V,NVSFN=AVSS} AVDD=5.3V,VREFN=3.3V,Internal VREFP=2.4V,VREFN=AVSS external clock=2.048MHz, data rate=1 kSPS$

048MHz, data rate=1 kSPS 图9. INL vs PGA 增益

AVSS=0V,DVDD=3.3V,internal VREFP=2.4V,VREFN=AVSS,external clock=2.048MHz

图10. INL vs 温度/AVDD 电压

## 8. 参数测量信息

图15. AVDD=3V 失调温漂 vs PGA 增益

#### 8.1. 噪声测量

调整数据速率和 PGA 增益以优化 LHA787X 噪声性能。当通过降低数据速率来增加平均数时,噪声相应地下降。增加 PGA 增益可降低输入参考噪声,这在测量小电平信号时特别有用。输入参考噪声只是在芯片的输入引脚处观察到的噪声,假定 ADC 热噪声是恒定的,因此在输入处看到的噪声实际上是热噪声除以 PGA 增益。而芯片热噪声也会来自 PGA 本身,因此随着增益翻倍,输入参考噪声不会减少一半,但通常接近该数值。较低

图16. AVDD=5V 失调温漂 vs PGA 增益

的输入参考噪声可测量更小的信号,从而提高系统分辨率。但也会减少动态范围(即最小和最大可测量信号之间的差异),因此 ENOB 随着增益的增加而减少。表 10 总结了采用 3V 模拟电源时 LHA787X 的噪声性能。表 12 总结了采用 5V 模拟电源时 LHA787X 的噪声性能。数据代表了 TA=25°C 时的典型噪声性能。所示数据是来自多个器件的读数的平均结果,并且是在输入短路时测量的。至少使用 1000 个连续读数来计算每个读数的 RMS 噪声。对于两个最高数据速率,噪声受 ADC 量化噪声的限制,不具有高斯分布。表 10 和表 12 显示了用内部参考进行的测量。数据代表了 LHA787X 在使用低噪声外部基准电压源(如 LHR3025)时的有效位数(ENOB)和动态范围。使用公式 1 计算表 10 和表 12 中的 ENOB 数据。

$$ENOB = log_2 \left| \frac{VREF}{\sqrt{2} \times V_{RMS\_Noise} \times Gain} \right|$$

(1)

Dynamic Range =

$$20 \times log_{10} \left| \frac{VREF}{\sqrt{2} \times V_{RMS\_Noise} \times Gain} \right|$$

(2)

## 表10. 输入参考噪声:3V 模拟电源和 2.4V 基准电压源,噪声均方根值(µV)

| Data<br>Rate(kSPS) | GAIN_1  | GAIN_2  | GAIN_3  | GAIN_4  | GAIN_6  | GAIN_8 | GAIN_12 | GAIN_24 |

|--------------------|---------|---------|---------|---------|---------|--------|---------|---------|

| 1                  | 1.419   | 0.740   | 0.621   | 0.404   | 0.329   | 0.318  | 0.295   | 0.259   |

| 2                  | 2.000   | 1.038   | 0.882   | 0.580   | 0.471   | 0.447  | 0.424   | 0.371   |

| 4                  | 2.871   | 1.493   | 1.257   | 0.835   | 0.673   | 0.647  | 0.614   | 0.544   |

| 8                  | 4.179   | 2.175   | 1.814   | 1.270   | 1.049   | 1.000  | 0.940   | 0.859   |

| 16                 | 6.425   | 3.408   | 2.862   | 2.137   | 1.870   | 1.790  | 1.724   | 1.604   |

| 32                 | 11.630  | 6.192   | 5.318   | 4.510   | 4.071   | 3.949  | 3.810   | 3.690   |

| 64                 | 49.660  | 25.498  | 18.563  | 14.771  | 11.929  | 10.441 | 9.447   | 8.658   |

| 128                | 714.546 | 360.436 | 237.260 | 176.455 | 118.240 | 89.532 | 59.419  | 30.752  |

#### 表11. 输入参考噪声:3V 模拟电源和 2.4V 基准电压源,有效位数 ENOB(bit)

| Data<br>Rate(kSPS) | GAIN_1 | GAIN_2 | GAIN_3 | GAIN_4 | GAIN_6 | GAIN_8 | GAIN_12 | GAIN_24 |

|--------------------|--------|--------|--------|--------|--------|--------|---------|---------|

| 1                  | 20.190 | 20.130 | 19.797 | 20.003 | 19.711 | 19.347 | 18.873  | 18.061  |

| 2                  | 19.695 | 19.641 | 19.291 | 19.481 | 19.197 | 18.856 | 18.347  | 17.540  |

| 4                  | 19.173 | 19.117 | 18.779 | 18.955 | 18.680 | 18.322 | 17.812  | 16.989  |

| 8                  | 18.632 | 18.574 | 18.251 | 18.349 | 18.040 | 17.695 | 17.199  | 16.329  |

| 16                 | 18.011 | 17.926 | 17.593 | 17.599 | 17.206 | 16.855 | 16.324  | 15.428  |

| 32                 | 17.155 | 17.064 | 16.699 | 16.522 | 16.084 | 15.713 | 15.180  | 14.226  |

| 64                 | 15.061 | 15.022 | 14.895 | 14.810 | 14.533 | 14.310 | 13.870  | 12.996  |

| 128                | 11.214 | 11.201 | 11.219 | 11.231 | 11.224 | 11.210 | 11.217  | 11.167  |

## 表12. 输入参考噪声:5V 模拟电源和 2.4V 基准电压源,噪声均方根值(μV)

| Data<br>Rate(kSPS) | GAIN_1  | GAIN_2  | GAIN_3  | GAIN_4  | GAIN_6  | GAIN_8 | GAIN_12 | GAIN_24 |

|--------------------|---------|---------|---------|---------|---------|--------|---------|---------|

| 1                  | 1.405   | 0.717   | 0.601   | 0.397   | 0.316   | 0.299  | 0.276   | 0.241   |

| 2                  | 1.988   | 1.025   | 0.848   | 0.567   | 0.440   | 0.417  | 0.388   | 0.346   |

| 4                  | 2.837   | 1.488   | 1.207   | 0.797   | 0.651   | 0.613  | 0.564   | 0.501   |

| 8                  | 4.061   | 2.101   | 1.754   | 1.222   | 1.006   | 0.948  | 0.892   | 0.804   |

| 16                 | 6.384   | 3.349   | 2.792   | 2.093   | 1.803   | 1.734  | 1.644   | 1.540   |

| 32                 | 11.483  | 6.126   | 5.256   | 4.434   | 4.081   | 3.914  | 3.689   | 3.599   |

| 64                 | 49.688  | 24.997  | 18.328  | 14.778  | 11.721  | 10.488 | 9.423   | 8.616   |

| 128                | 711.635 | 354.879 | 238.430 | 176.490 | 118.739 | 89.663 | 59.162  | 30.798  |

#### 表13. 输入参考噪声:5V 模拟电源和 2.4V 基准电压源,有效位数 ENOB(bit)

| Data<br>Ratek(SPS) | GAIN_1 | GAIN_2 | GAIN_3 | GAIN_4 | GAIN_6 | GAIN_8 | GAIN_12 | GAIN_24 |

|--------------------|--------|--------|--------|--------|--------|--------|---------|---------|

| 1                  | 20.204 | 20.175 | 19.845 | 20.028 | 19.774 | 19.438 | 18.966  | 18.162  |

| 2                  | 19.704 | 19.659 | 19.347 | 19.513 | 19.293 | 18.958 | 18.474  | 17.641  |

| 4                  | 19.190 | 19.121 | 18.838 | 19.022 | 18.729 | 18.400 | 17.937  | 17.107  |

| 8                  | 18.673 | 18.624 | 18.299 | 18.406 | 18.101 | 17.772 | 17.275  | 16.424  |

| 16                 | 18.020 | 17.951 | 17.629 | 17.629 | 17.259 | 16.900 | 16.393  | 15.487  |

| 32                 | 17.173 | 17.080 | 16.716 | 16.546 | 16.081 | 15.726 | 15.226  | 14.262  |

| 64                 | 15.060 | 15.051 | 14.914 | 14.809 | 14.559 | 14.304 | 13.873  | 13.003  |

| 128                | 11.220 | 11.223 | 11.212 | 11.231 | 11.218 | 11.208 | 11.223  | 11.165  |

## 9. 详细描述

## 9.1. 概述

LHA787X 系列是具有集成可编程增益放大器(PGA)的低功耗、多通道、同时采样、24 位、delta-sigma ( $\Delta\Sigma$ )、模数转换器(ADC)。该器件在不同数据速率下的性能使该设备非常适合智能电网和其他工业电源监控、控制和保护应用。

LHA787X 器件具有可编程多路复用器,可进行各种内部监测信号测量,包括温度、电源和用于器件噪声测试的输入短路信号。PGA 增益可以从以下八种设置中选择一种:1/2/3/4/6/8/12/24。器件中的 ADC 提供 1kSPS、2kSPS、4kSPS、8 kSPS、16kSPS、32kSPS、64kSPS 和 128KSPS 的数据速率。这些器件使用兼容串行外设接口(SPI)的接口进行通信。提供四个通用 IO(GPIO)引脚供一般使用。使用多个设备轻松地向系统添加通道,并将其与 START 引脚同步。

内部基准电压可设置为 2.4V 或 4V。内部振荡器产生一个 2.048MHz 时钟。使用带有可编程阈值触发的集成比较器进行输入超量程或欠量程检测。LHA787X 的详细图如下。

#### 9.2. 功能框图

#### 9.3. 功能描述

#### 9.3.1. 电磁干扰(EMI)滤波器

输入端的 RC 滤波器在所有通道上用作 EMI 滤波器。-3dB 滤波器带宽约为 3MHz。

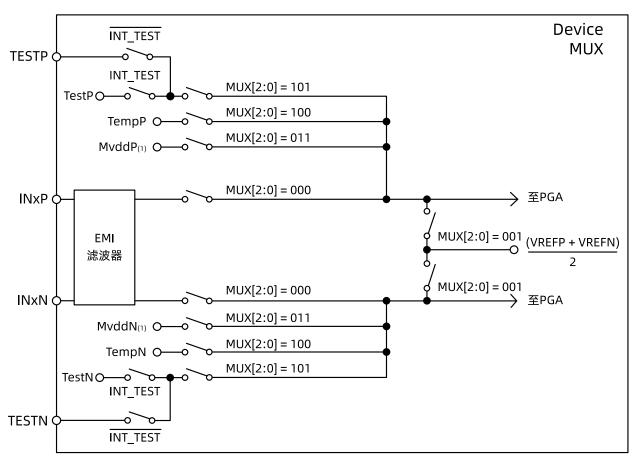

## 9.3.2. 输入多路选择器

LHA787X 输入多路选择器非常灵活,提供多种可配置信号切换选项。下图示出了该器件单通道上的多路复用器图。INxP 和 INxN 对于四个、六个或八个通道中的每一个都是独立的(取决于器件)。这种灵活性允许重要的器件和子系统诊断、校准和配置。通过将适当的值写入 CHnSET 寄存器来选择每个通道的开关设置(有关详细信息,请参阅寄存器部分中的 CHnSET 寄存器)。每个多路复用器的输出连接到单独的通道 PGA。

(1) MVDD 监控电源电压取决于通道号;请参阅电源测量(MVDDP、MVDDN)部分。

图17. 一个通道的输入多路复用框图

#### 9.3.2.1. 噪声测量

设 CHnSET[2:0]=001 将[(V<sub>VREFP</sub>+V<sub>VREFN</sub>)/2]的共模电压送入两个通道输入端。使用此设置可测试用户系统中的固有器件噪声。

#### 9.3.2.2. 测试信号(TestP 和 TestN)

设置 CHnSET[2:0]=101 可提供内部生成的测试信号,用于上电时的子系统验证。测试信号通过寄存器设置进行控制(详情参见 CONFIG2:配置寄存器 2 部分)。TEST\_AMP 控制信号幅度,TEST\_FREQ 控制测试信号的开关频率。测试信号在 TESTP 和 TESTN 引脚被多路复用并传输出器件。INT\_TEST 寄存器位(在 CONFIG2:配置寄存器 2 部分)停用内部测试信号,以便测试信号可以从外部驱动。此功能允许测试或校准具有相同信号的多个器件。

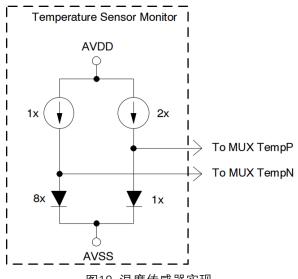

#### 9.3.2.3. 温度传感器(TempP TempN)

设置 CHnSET[2:0]=100 将温度传感器信号送入通道输入端。该传感器使用两个内部二极管,其中一个二极管的电流密度是 另一个二极管的 16 倍,如下图所示。二极管电流密度的差异产生与绝对温度成正比的电压差异。

图18. 温度传感器实现

由于封装对 PCB 的热阻较低,内部器件温度会密切跟踪 PCB 温度。LHA787X 的自发热导致读数高于周围 PCB 的温度。在进行温度测量时,建议将通道增益设置为 1。

公式 3 的比例因子将温度读数转换为℃。在使用该公式之前,温度读数代码必须首先转换为μV。

Temperature(°C) =

$$\left[\frac{\text{lag} \times \text{lg}(\mu V) - 145, 300 \mu V}{490 \mu V/^{\circ}C}\right] + 25^{\circ}C$$

(3)

#### 9.3.2.4. 电源测量(MVDDP, MVDDN)

设置 CHnSET[2:0]=011 可将通道输入设置为不同的器件电源电压。对于通道12567和8 (MVDDP MVDDN) 是[0.5x(AVDD-AVSS)]; 对于通道3和4 (MVDDP-MVDDN)是 DVDD/4。将增益设置为1,以避免在测量电源时使PGA 饱和。

#### 9.3.3. 模拟输入

器件的模拟输入被直接连接到片上集成的低噪声、低漂移、高输入阻抗、可编程增益放大器。放大器位于 各个通道多路复用器之后。

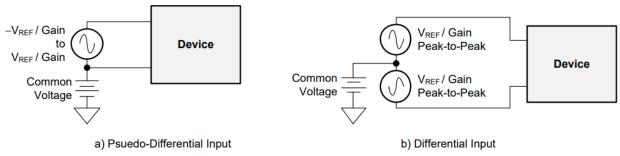

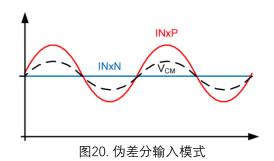

LHA787X 模拟输入为全差分输入。差分输入电压(VINxP-VINxN)范围在-VREF/gain 到 VREF/gain 之间。有关模拟输入和数字代码之间的相关性的解释,请参阅数据格式部分。驱动 LHA787X 模拟输入的一般方法有两种:伪差分或全差分,如下图所示。

图19. 驱动 LHA787X 的方法:伪差分或全差分

将 INxN 引脚保持在一个公共电压,最好是在中间电源,以配置全差分输入的伪差分信号。INxP 信号需要被限制在 Vcm-Vref/Gain 到 Vcm+Vref/Gain 范围内,并保持在绝对最大规格内,并验证最小值和最大值处的差分信号是否满足输入共模范围部分中讨论的共模输入规范。

将 INxP 和 INxN 处的信号配置为以共模电压 VCM 为中心并保持 180°相位差,以使用全差分输入模式。 INxP 和 INxN 输入幅度均保持在 Vcm+0.5xVref/Gain 到 Vcm-0.5xVref/Gain 范围内。最大值和最小值的差分电压等于 VREF/gain 和-VREF/gain。在差分配置中使用 LHA787X 可最大限度地扩大数据转换器的动态范围。为获得最佳性能,建议将共模电压设置在模拟电源的中点[(AVDD+AVSS)/2]。

如果没有使用任何模拟输入通道,则使用寄存器位关断这些引脚以节省功率。有关如何关断各个通道的更多信息,请参阅 SPI 命令定义部分。将任何未使用或掉电的模拟输入引脚直接连接到 AVDD。

#### 9.3.4. PGA 设置和输入范围

每个通道都有自己的可配置可编程增益放大器(PGA)。使用每个通道的 CHnSET 寄存器将增益设置为 8 种设置之一(1、2、3、4、6、8、12 和24)(有关详细信息,请参阅寄存器映射部分中的 CHnSET 寄存器)。LHA787X 是 CMOS 输入,因此电流噪声可忽略不计。

#### 9.3.4.1. 输入共模范围

模拟前端的可用输入共模范围取决于各种参数,包括最大差分输入信号、电源电压。共模范围 VCM 在公式 4 中定义:

$$AVDD - \frac{Vmax_{Diff}}{2} > Vcm > AVSS + \frac{Vmax_{Diff}}{2}$$

(4)

其中:

- · VMAX DIFF=PGA 输入端的最大差分信号

- ・ VCM = 共模电压

例如:

如果 AVDD-AVSS=3.3V, VMAX DIFF=1000mV, 那么 0.5V<Vcm<2.8V。

#### 9.3.5. Delta Sigma 调制器

每个 LHA787X 通道都有自己的 delta-sigma ( $\Delta\Sigma$ ) ADC。调制器以(f<sub>MoD</sub>=f<sub>CLK</sub>/2)的速率采样输入信号。与任何 delta-sigma ( $\Delta\Sigma$ )调制器一样,LHA787X 噪声整形直到 F<sub>MoD</sub>/2。

#### 9.3.6. Clock

LHA787X 提供两种不同的器件时钟来源:内部和外部。使用内部振荡器的内部时钟非常适合非同步、低功耗系统。内部振荡器经过微调,以确保室温下的精度。内部振荡器的精度在指定的温度范围内变化;有关详细信息,请参阅电气特性表。当同步多个 LHA787X 器件或同步外部事件时建议采用外部时钟,因为内部振荡器时钟性能会随温度变化而变化。时钟选择由 CLKSEL 引脚和 CLK\_EN 寄存器位控制。在模拟和数字电源上电后提供

外部时钟。

CLKSEL 引脚选择内部振荡器或外部时钟。CONFIG1 寄存器中的 CLK\_EN 位使能和禁止在 CLK 引脚上输出振荡器时钟。CLKSEL 引脚和 CLK\_EN 位的真值表如下表所示。在菊花链配置中使用多个器件时,CLK\_EN 位非常有用。在节电模式下,建议关闭外部时钟以节省功耗。

表14. CLKSEL 引脚和 CLK\_EN 位

| CLKSEL PIN | CLK_EN BIT | 时钟源               | CLK 引脚状态 |

|------------|------------|-------------------|----------|

| 0          | X          | 外部时钟              | 输入:外部时钟  |

| 1          | 0          | 内部振荡 <del>器</del> | 三态       |

| 1          | 1          | 内部振荡 <del>器</del> | 输出:内部振荡器 |

#### 9.3.7. 数字抽取滤波器

数字滤波器接收调制器输出比特流并抽取数据流。抽取比决定输出速率,抽取比等于 fmod/fdr。。通过调整抽取比,可以在分辨率和数据速率之间进行权衡:更高的抽取允许更高的分辨率(从而产生更低的数据速率),而更低的抽取会降低分辨率,但能够以更高的数据速率实现更宽的带宽。更高的数据速率通常用于实现软件重新采样技术的电源应用中,以帮助调整电压和电流通道的相位。

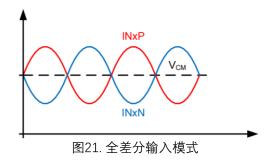

每个通道上的数字滤波器由三阶 Sinc 滤波器组成。输入阶跃变化需要三个转换周期才能使滤波器建立。使用 CONFIG 1 寄存器中的 DR[2:0]位调整 sinc3 滤波器的抽取比(详情请参阅寄存器映射部分)。数据速率设置是将所有通道设置为相同数据速率的全局设置。

Sinc 滤波器是一种可变抽取率、三阶低通滤波器。数据以 fmoo 的速率从调制器提供到滤波器。Sinc3 滤波器衰减高频调制器噪声,然后将数据流抽取为并行数据。抽取率会影响整个转换器数据速率。

公式 5 给出了缩放后的 sinc3 滤波器 Z 域传递函数。

$$|H(z)| = \left| \frac{1 - Z^{-N}}{1 - Z^{-1}} \right|^{3}$$

(5)

Sinc3 滤波器频域传递函数如公式 6 所示。

$$\left| H(f) \right| = \left| \begin{array}{c} \sin \left( \frac{N\pi f}{f_{MOD}} \right) \\ \hline N \times \sin \left( \frac{\pi f}{f_{MOD}} \right) \end{array} \right|^{3}$$

(6)

其中:

·N=抽取比

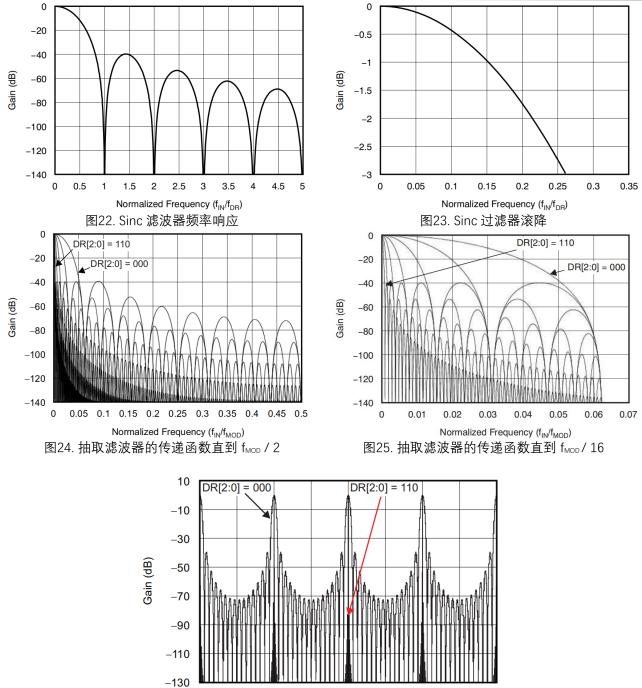

Sinc3 滤波器在输出数据速率及其倍数处产生陷波(零点)。在这些频率下,滤波器具有无限衰减。图 22 示出了 sinc 滤波器频率响应,图 23 示出了 sinc 滤波器滚降。图 24 和图 25 分别说明了直到 fmop/2 和 fmop/16 数据速率下滤波器的传递函数。图 26 说明了扩展到 4 倍 fmop 的传递函数。图 26 说明 LHA787X 通带在每个 fmop 处会自身重复。请注意,数字滤波器响应和滤波器陷波与主时钟频率成正比。

Normalized Frequency (f<sub>IN</sub>/f<sub>MOD</sub>) 图26. 抽取滤波器的传递函数直到 4fMOD 为 DR[2:0]=000 和 D R[2:0]=110

2

3.5

1.5

0

0.5

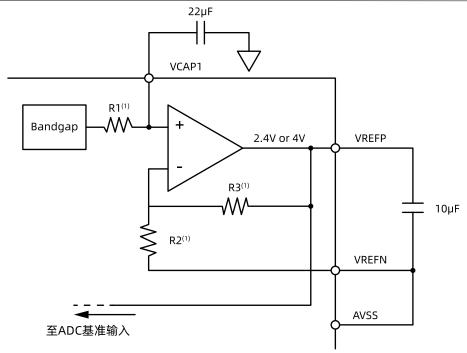

## 9.3.8. 电压基准

下图显示了内部 LHA787X 基准电压源的简化框图。参考电压相对于 AVSS 产生。使用内部基准电压时,请将 VREFN 连接到 AVSS。

对于 VREF=2.4V:R1=12.5KΩ, R2=25KΩ, R3=25KΩ。 对于 VREF=4V:R1=10.5KΩ, R2=15KΩ, R3=35KΩ。

图27. 内部参考

外部带限电容决定了参考噪声的贡献量。对于噪声要求高的系统,使带宽限制在 10Hz 以下,以便参考噪声不会影响系统噪声。当使用 3V 模拟电源时,内部基准必须设置为 2.4V。对于 5V 模拟电源,可以通过设置配置 2 寄存器中的 VREF\_4V 位将内部基准设置为 4V。

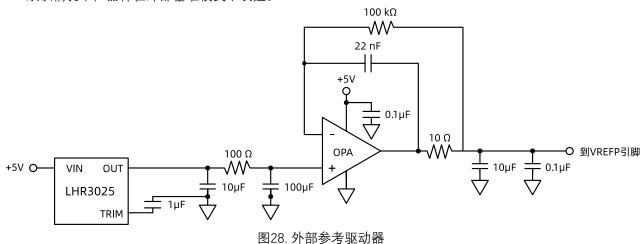

或者,可以关断内部基准缓冲器,并在外部驱动 VREFP。下图示出了典型的外部基准驱动电路。掉电由 CONFIG3 寄 存器中的 PD.REFBUF 位控制。当两个器件级联时,此掉电可以设置器件共用内部参考。

默认情况下,器件在外部基准模式下唤醒。

#### 9.3.9. 输入超出范围检测

LHA787X 集成了比较器,可检测输入信号的超出范围条件。基本原理是将输入电压与基于模拟电源的 3 位数模转换器(DAC)设置的阈值电压进行比较。比较器触发阈值电平由故障寄存器中的 COMP\_TH[2:0]位设置。

如果 LHA787X 从±2.5V 电源供电并且 COMP\_TH[2:0]=000(95%和 5%),高侧触发阈值设置在 2.25v[等于 AVSS+(AVDD-AVSS)x95%],低侧阈值设置在-2.25V[等于 AVSS+(AVDD-AVSS)x5%]。阈值计算公式适用于单极性和 双极性电源。

可以通过使用 COMP\_TH[2:0]位设置适当的阈值电平来检测故障状况。要确定哪些输入超出范围,请单独读取 FAULT \_STATP 和 FAULT\_STATN 寄存器,或将 FAULT\_STATx 位作为输出数据流的一部分并读取;具体请参阅数据输出(D0UT)部分。

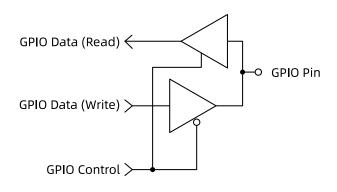

#### 9.3.10. 通用数字 IO (GPIO)

LHA787X 共有四个通用数字 IO(GPIO)引脚可用。通过 GPIOC 位将数字 IO 引脚配置为输入或输出。GPIO 寄存器中的 GPIOD 位指示引脚的电平。GPIO 逻辑高电平由 DVDD 的电压设置。当读取 GPIOD 位时,返回的数据是引脚的逻辑电平,无论它们被编程为输入还是输出。当 GPIO 引脚配置为输入时,写入相应的 GPIOD 位不起作用。配置为输出时,对 GPIOD 位的写入将设置输出电平。

如果配置为输入,则必须将 GPIO 引脚驱动到明确的状态。GPIO 引脚上电或复位后被设置为输入。下图显示了 GPIO 引脚结构。通过 10kΩ电阻将未使用的 GPIO 引脚直接连接到 DGND。

图29. GPIO 引脚实现

#### 9.4. 设备功能模式

#### 9.4.1. Start

使用 START 命令控制转换时,将 START 引脚保持为低电平。在多个设备配置中,START 引脚用于同步设备(有关更多详细信息,请参阅多个设备配置小节)。

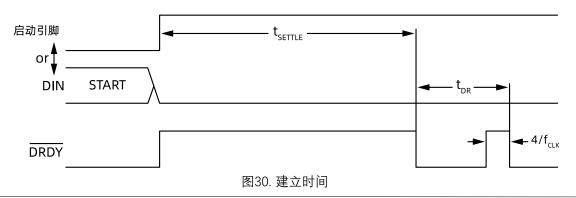

#### 9.4.1.1. 建立时间

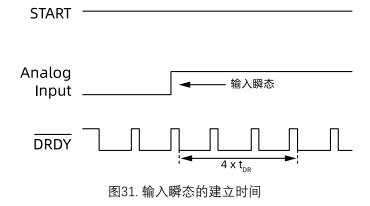

建立时间(Tsettle)是转换器在启动信号拉高到输出完全建立的所需时间。当 START 被拉高时, DRDY 也被拉 高。下一个 DRDY 下降沿指示数据准备就绪。下图示出了时序图,下表示出了不同数据速率下的建立时间。建立时间取决于 fclk 和抽取比(CONFIG1 寄存器中的 DR[2:0]位控制)。当初始建立时间过去后, DRDY 下降沿发生在设定的数据速率 tor。如果数据没有在 DOUT 上读回并且输出移位寄存器需要更新,则 DRDY 在返回低电平之 前变为高电平并保持 4 tclk,此时表示新数据已准备就绪。请注意,当 START 保持高电平,输入信号发生阶跃变化时,滤波 器需要 3xTcm 才能建立到新值。在第四个 DRDY 脉冲上可获得稳定后的数据。

表15. 不同数据速率的建立时间

| DR[2:0] | 正常模式 | UNIT             |

|---------|------|------------------|

| 000     | 152  | t <sub>clk</sub> |

| 001     | 296  | t <sub>clk</sub> |

| 010     | 584  | t <sub>clk</sub> |

| 011     | 1160 | t <sub>ськ</sub> |

| 100     | 2312 | tcık             |

| 101     | 4616 | tcık             |

| 110     | 9224 | t <sub>ськ</sub> |

#### 9.4.1.2. 输入信号阶跃

当 ADC 转换时,如果输入信号发生阶跃变化,输出数据需要 3tm 的建立延迟时间。在第四个 DRDY 脉冲上可获得稳定的数据。数据可在第 4 个 DRDY 脉冲之前的每个 DRDY 低电平转换处读取,但建议忽略。下图显示了模拟输入上的输入阶跃或输入瞬态事件完全建立所需的等待时间。

#### 9.4.2. Reset (RESET)

复位 LHA787X 的方法有两种:将 RESET 引脚拉低,或发送RESET命令。当使用复位引脚时,确保遵循最小脉冲持续时间满足规范,然后再将引脚 RESET 为高电平。复位命令在命令的第八个 SCLK 下降沿生效。复位后,需要 18 个 TCLK 周期才能完成配置寄存器到默认状态的初始化并开始转换周期。请注意,只要使用 WREG 命令将 CONFIG1 寄存器设置为新值,就会自动向数字滤波器发出内部复位。

#### 9.4.3. Power-Down (PWDN)

当PWDN拉低时,所有片上电路都掉电。要退出掉电模式,请将PWDN引脚置于高电平。从掉电模式退出后,内部振荡器和基准需要时间唤醒。在掉电期间,建议关闭外部时钟以节省功耗。

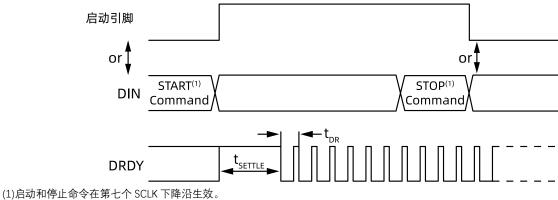

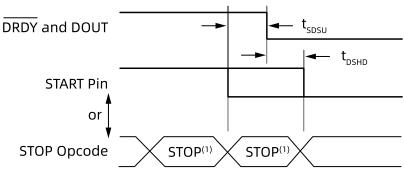

## 9.4.4. 连续转换模式

当 START 引脚变为高电平或发送 START 命令时,转换开始。如图 32 所示,当转换开始时 DRDY 输出变为高电平,当数据准备就绪时变为低电平。转换无限期地继续直到开始引脚被拉低或停止命令被传输.当 START 引脚拉低或发出 STOP 命令时,允许正在进行的转换完成。图 33 和表 16 显示了在这种模式下控制转换时所需的 DRDY 到 START 引脚或 START 和 STOP 命令的时序。Tsdbu 时序指示何时将 START 引脚变为低电平或何时在 DRDY 下降沿之前发送 STOP 命令以停止进一步的转换。Tdbhu 时序指示何时将 START 引脚变为低电平或在 DRDY 下降沿后发送 STOP 命令以完成当前转换并停止进一步转换。为了保持转换器连续运行,START 引脚可以永久地保持高电平。

图32. 连续转换模式

(1)启动和停止命令在传输结束时的第七个 SCLK 下降沿生效。

图33. 开始 DRDY 时刻

表16. 图 33<sup>(1)</sup>的时序特性

|       |                                         | MIN | UNIT |

|-------|-----------------------------------------|-----|------|

| tspsu | 建立时间:在 DRDY 下降沿之前启动引脚低电平或停止命令,以停止进一步的转换 | 16  | tcLK |

| toshd | 延迟时间:启动引脚低电平或停止命令以完成当前转换并停止进一步的 转换      | 16  | tcLK |

<sup>(1)</sup> 启动和停止命令在传输结束时的第七个 SCLK 下降沿生效。

#### 9.4.5. 数据检索

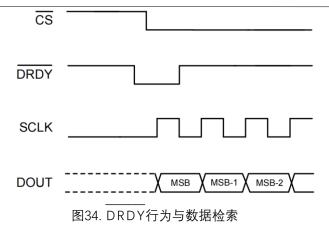

#### 9.4.5.1. 数据就绪(DRDY)

DRDY是一个从高电平转换到低电平的输出信号,表示新的转换数据已准备就绪。CS对数据就绪信号没有 影响。DRDY行为取决于设备是否处于 RDATAC 模式或 RDATA 命令用于按需读取数据。(有关详细信息,请参 阅 SPI 命令 定义部分的 RDATAC:开始读取数据连续模式和 RDATA:读取数据子部分)。

当使用 RDATA 命令读取数据时,读取操作可以与下一个DRDY重叠,而不会发生数据损坏。

START 引脚或 START 命令将器件置于正常数据捕获模式或脉冲数据捕获模式。

下图显示了数据检索过程中CS、DRDY、DOUT 和 SCLK 之间的关系(在 LHA787X 的情况下)。DOUT 在 SCLK 上升沿锁 存。DRDY在 SCLK 下降沿被拉高。请注意,DRDY在第一个 SCLK 下降沿变为高电平,无论是 从器件检索数据还是通 过 DIN 引脚发送命令。

无论CS状态如何,DRDY信号在第一个 SCLK 下降沿被清零。如果 SPI 总线用于与同一总线上的其他设备通信,则必须考虑此条件。

#### 9.4.5.2. 回读数据

数据检索可以通过两种方法之一来完成:

- 1. RDATAC: 连续读数据命令将设备设置为连续读取数据的模式,而不发送命令。有关更多详细信息,请参阅RDATAC:开始读取数据连续模式部分。

- 2. RDATA:读取数据命令要求向设备发送命令以加载输出移位用最新数据注册。有关更多详细信息,请参阅 RDATA: ReadData 部分。

转换数据是通过在 DOUT 上移出数据来读取的.DOUT 上数据的 MSB 在第一个 SCLK 上升沿被计时。 DRDY 第一个 SCL K 下降沿返回高电平。对于整个读取操作, DIN 应保持低电平。

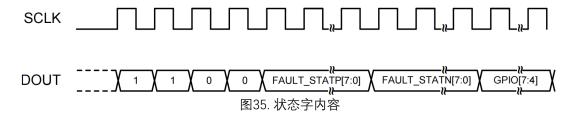

## 9.4.5.3. 状态字

状态字在数据回读之前,提供有关 LHA787X 状态的信息。状态字长 24 位,包含 FAULT\_STATP、FAULT\_STATN 和 GPIO 数据位的值。内容对齐下图所示。

状态字长始终为 24 位。对于 32-kSPS、64-kSPS 和 128-kSPS 数据速率,长度不会改变。

## 9.4.5.4. 回读长度

数据输出中的位数取决于通道数和每个通道的位数。每个通道数据的数据格式首先是两个补码和 MSB。

对于所有数据速率. 数据位数为:24 个状态位+每通道 24 位通道=216 位。

当使用用户寄存器设置关闭通道时,相应的通道输出设置为 0。但是,通道输出的顺序保持不变。

LHA787X 还提供多数据回读功能。通过简单地提供更多 SCLKs,可以多次读出数据,在这种情况下,MSB 数据字节 在读取最后一个字节后重复。CONFIG1 寄存器中的 DAISYIN 位必须设置为 1 才能进行多次读回。

9.5. 通讯

#### 9.5.1. 数据格式

CONFIG1 寄存器中的 DR [2:0] 位设置 LHA787X 的输出分辨率。

1 LSB =

$$(2 \times V_{REF} / Gain) / 2^{24} = FS / 2^{23}$$

(8)

正满量程输入 [V<sub>N</sub>≥(FS-1 LSB)=(V<sub>REF</sub>/Gain-1 LSB)] 产生 7FFFFFh 的输出码,负满量程输入(V<sub>N</sub>≤-FS=V REF</sub>/Gain)产生 800000h 的输出码。

下表总结了不同输入信号的理想输出代码。

表17.24 位理想输出代码与输入信号

| 输入信号,V <sub>(IN×P)</sub> - V <sub>(IN×N)</sub> | 理想输出代码(1) |  |  |  |

|------------------------------------------------|-----------|--|--|--|

| > FS (2 <sup>23</sup> - 1)/ 2 <sup>23</sup>    | 7FFFFFh   |  |  |  |

| FS/ 2 <sup>23</sup>                            | 000001h   |  |  |  |

| 0                                              | 000000h   |  |  |  |

| -FS/ 2 <sup>23</sup>                           | FFFFFFh   |  |  |  |

| <-FS                                           | 800000h   |  |  |  |

(1)排除噪声、INL、失调和增益误差的影响。

#### 9.5.2. SPI 接口

SPI 兼容串行接口由四个信号组成: CS、SCLK、DIN 和 DOUT。该接口用于读取转换数据、读写寄存器以及 \_\_\_\_\_\_\_\_ 控制 LHA787X 操作。 DRDY 用作状态信号,用于指示 ADC 数据何时准备好回读。当有新数据可用时, DRDY 变低。

#### 9.5.2.1. SPI 选择(CS)

一格CS设为高电平停用与器件的 SPI 通信,并复位串行接口。数据转换继续进行,并且可以监视 DRDY 以检查新的转换结果是否准备就绪。监控DRDY信号的主设备可以通过将CS引脚拉低来选择合适的从设备。串行通信完成后,始终等待四个或更多个 talk 周期,然后才将CS变为高电平。

#### 9.5.2.2. 串行时钟 (SCLK)

SCLK 为串行通信提供时钟。SCLK 是施密特触发输入,但建议尽可能保持 SCLK 无噪声,以防止毛刺无意中移位数据。推荐 SCLK 引脚对 DGND 加一弱下拉电阻。数据在 SCLK 的下降沿从 DIN 移入,在 SCLK 的上升沿从 DOUT 移出。

SPI 通信时,请确保向器件发出命令需要的完整的 SCLK 个数。否则可能会导致设备串行接口处于未知状 一 态,必要时将CS输入由低变高的信号以恢复 SPI 接口。

对于单个器件, SCLK 所需的最低速度取决于通道数、分辨率位数和输出数据速率。(有关多个设备, 请参阅多个设备配置部分。)

例如,如果 LHA787X 与 8kSPS 模式(24 位分辨率)一起使用,则最低 SCLK 速度为 1.755MHz 以移出所有

数据。

数据读取可以通过将设备置于 RDATAC 模式或根据需要发出数据的 RDATA 命令来完成。公式 9 中的 SCLK 速率限制适用于 RDATAG 对于 RDATA 命令,如果必须在两个连续的 DRDY 信号之间读取数据,则限制适用。公式 9 假设在数据 捕获之间没有发出其他命令。

$$(t_{SCLK} < t_{DR} - 4 t_{CLK})$$

/  $(N_{bits} \times 8 + 24)$

这里

• N 位=当前数据速率的数据分辨率(24 bits) (9)

#### 9.5.2.3. 数据输入(DIN)

DIN 与 SCLK 一起用于向设备发送数据。DIN 上的数据在 SCLK 的下降沿移到设备中。

该器件的通信本质上是全双工的。即使数据被移出,该设备也会监视移入的命令。当发送命令时,输出移位寄存器中的数据被移出。因此,在移出数据时,请确保 DIN 引脚上发送的任何内容都是有效的。当读取数据时没有命令要发送到设备时,在 DIN 上发送 NOP 命令。在 DIN 上发送多字节命令时,确保在发送多字节命令部分满足 tspecope 时序。

#### 9.5.2.4. 数据输出(DOUT)

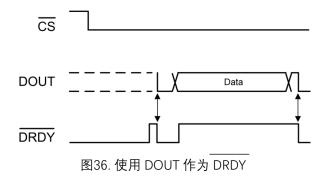

DOUT 与 SCLK 一起用于从器件读取转换和寄存器数据。数据首先在 SCLK MSB 的上升沿输出,当CS为高电平时,DOUT 进入高阻抗状态。在读取数据连续模式下(详情请参阅 SPI 命令定义部分),DOUT 输出线也可用于指示何时有新数据可用。如果新数据就绪时,CS为低电平 DOUT 线上的高电平到低电平转换与 DRDY 的高电平到低电平转换同步发生如下图所示。此功能可用于最小化器件和系统控制器之间的连接数量。

## 9.5.3. SPI 命令定义

LHA787X 提供灵活的配置控制。下表中总结的命令控制和配置设备操作。这些命令是独立的,除了寄存器读和寄存器写操作需要第二个命令字节来包含额外的数据。CS在命令之间保持高电平或低电平,但在整个命令操作(包括多字节命令)中必须保持低电平。系统命令和RDATA命令由LHA787X 在第七个 SCLK 下降沿解码。寄存器读写命令在第八 SCLK 下降沿进行解码。发出命令后将CS高时请务必遵循 SPI 时序要求。

表18. 命令定义

| COMMAND   | DESCRIPTION   | 第一个字节           | 第二字节 |

|-----------|---------------|-----------------|------|

| 系统命令      |               |                 |      |

| WAKEUP    | 从待机模式唤醒       | 0000 0010 (02h) |      |

| STANDBY   | 进入待机模式        | 0000 0100 (04h) |      |

| RESET     | 重置设备          | 0000 0110 (06h) |      |

| START     | 启动或重新启动(同步)转换 | 0000 1000 (08h) |      |

| STOP      | 停止转换          | 0000 1010 (OAh) |      |

| OFFSETCAL | 通道偏移校准        | 0001 1010 (1Ah) |      |

| 数据读取命令    |               |                 |      |

| IDDVIVC | 启用读取数据连续模式。<br>此模式是上电时的默认模式。 <sup>⑴</sup> | 0001 0000 (10h)              |                         |  |  |  |  |  |  |

|---------|-------------------------------------------|------------------------------|-------------------------|--|--|--|--|--|--|

| SDATAC  | 停止读取数据连续模式                                | 0001 0001 (11h)              |                         |  |  |  |  |  |  |

| RDATA   | 通过命令读取数据                                  | 0001 0010 (12h)              |                         |  |  |  |  |  |  |

| 寄存器读写命令 | 寄存器读写命令                                   |                              |                         |  |  |  |  |  |  |

| RREG    | 从地址 rrrrr 开始读取 n 个 nnnn 寄存器               | 001rrrrr(2xh) <sup>(2)</sup> | 000nnnnn <sup>(2)</sup> |  |  |  |  |  |  |

| WREG    | 从地址 rrnr 开始写入 n 个 nnnn 寄存器                | 010rrrrr(4xh) <sup>(2)</sup> | 000nnnnn <sup>(2)</sup> |  |  |  |  |  |  |

<sup>(1)</sup> 当处于 RDATAC 模式时, RREG 命令将被忽略。

#### 9.5.3.1. 发送多字节命令

LHA787X 串行接口以字节为单位解码命令,解码和执行每个命令需要 4tck周期。因此,当发送多字节命令 (例如 RREG 或 WREG) 时,当前字节(或命令)的末尾与下一字节必须使用 4 个 tclk 进行隔开。

假设 CLK 为 2.048MHz,则  $t_{SDECODE}$ (4  $t_{CLK}$ )为 1.96  $\mu$ S。当 SCLK 为 16MHz 时,一个字节可以在 0.5  $\mu$ S 内传输。此字节传输时间不符合  $t_{SDECODE}$ 规范;因此,必须在第一个字节之后和第二个字节之前插入  $1.46\mu$ S( $1.96\mu$ S  $-0.5\mu$ S)的延迟。如果 SCLK 为 4MHz,则在  $2\mu$ S 内传输一个字节。由于此传输时间超过  $t_{SDECODE}$ 规范( $2\mu$ S >1.96  $\mu$ S),处理器可以无延迟地发送后续字节。

#### 9.5.3.2. 唤醒:退出待机模式

唤醒命令退出低功耗待机模式,请参阅待机:进入待机模式部分。请务必留出足够的时间让处于待机模式的所有电路上电(详情请参阅电气特性表)。此命令没有 SCLK 速率限制,可以随时发出。任何后续命令必须在延迟 4tcux 周期后发送。

#### 9.5.3.3. 待机:进入待机模式

待机命令进入低功耗待机模式。除参考部分外,器件中的所有电路都掉电。待机模式功耗在电气特性表中指定。此命令没有 SCLK 速率限制,可以随时发出。在设备进入待机模式后,不要发送唤醒命令以外的任何其他命令。

#### 9.5.3.4. RESET:将寄存器重置为默认值

RESET 命令重置数字滤波器并将所有寄存器设置返回到其默认值;有关更多详细信息,请参阅 Reset (复位)部分。此命令没有 SCLK 速率限制,可以随时发出。执行复位命令需要 2ms。避免在此期间发送任何命令。

#### 9.5.3.5. START:开始转换

START 命令启动数据转换。将 START 引脚连接到低电平,通过 START 和 STOP 命令将 START 命令接低控制转换。如果正在进行转换,则此命令不起作用。STOP 命令用于停止转换。如果启动命令紧接着是停止命令,那么它们之间必须存在 4tclk 周期延迟的间隙。在进一步的转换停止之前,当前转换完成。此命令没有 SCLK 速率限制,可以随时发出。

## 9.5.3.6. 停止:停止转换

STOP 命令停止转换。将 START 引脚连接到低电平,通过命令控制转换。发送停止命令时,正在进行的转换完成并停止进一步的转换。如果转换已停止,则此命令不起作用。此命令没有 SCLK 速率限制,可以随时发出。

## 9.5.3.7. OFFSETCAL:通道偏移校准

OFFSETCAL 命令取消每个通道的偏移。建议每次 PGA 增益设置发生变化时发出 OFFSETCAL 命令。

发出 OFFSETCAL 命令时,设备将自身配置为最低数据速率(DR[2:0] = 110-1 kSPS),并对每个通道执行以下步骤:

- 将每个通道的模拟输入短路并连接到中间电源[(AVDD+AVSS)/2]

- 复位数字滤波器(需要滤波器建立时间=4t<sub>DR</sub>)

- 收集 16 个数据点进行校准=15tpx

<sup>(2)</sup> nnnnn=要读取或写入的寄存器数-1。例如,要读取或写入三个寄存器,请设置 nnnnn=0 (0010) 。rrrrr=读写命令的起始寄存器地址。

总校准时间=(19T<sub>DR</sub> x 8) +1 mS=153mS。

#### 9.5.3.8. RDATAC: 启动读取数据连续模式

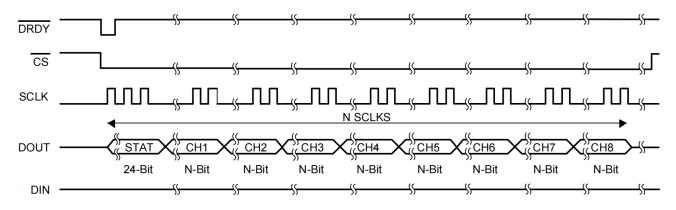

RDATAC 命令启用读取数据连续模式。在这种模式下,转换数据从器件检索,而不需要发出后续的 RDATA 命令。该模式在每个 DRDY 沿将转换数据放在输出寄存器中,这样就可以用下面的 SCLK 直接将数据移出。在使用新的 DRDY 下降沿更新数据之前,从器件中移出所有数据,以避免丢失数据。读取数据连续模式是器件默认模式;设备在上电时默认为该模式。下图显示了使用 RDATAC 模式时 LHA787X 数据输出协议。

注意: XSCLKs= (N 位) (8 通道) +24 位。 (N=24) 。

图37. LHA787X SPI 总线数据输出(八通道)

RDATAC 模式由 Stop Read Data Continuous 命令取消。如果设备处于 RDATAC 模式,则必须先发出 SDATAC 命令,然后才能将任何其他命令发送到设备。此命令没有 SCLK 速率限制。但是,后续数据检索 SCKK 或 SDATAC 命令应在完成之前至少等待 4tclk 周期。RDATAC 时序如下图所示。在 DR DY脉冲周围有一个 4tclk 周期的保持,在那里这个命令不能发出。如果没有从器件中检索到数据并且 CS保持为低电平,则与 DR DY 同步发生从高到低的 DOUT 转换。若要在发出 RDATAC 命令后从器件检索数据,请确保 START 引脚为高电平或发出 START 命令。下图显示了使用 RDATAC 命令的推荐方式。读取数据连续模式非常适合数据记录器或记录仪等应用,这些应用只需设置一次寄存器,无需重新配置。

(1) **t**UPDATE = **4** / **f**CLK。在此期间不要读取数据。

图38. 在 RDATAC 模式下读取数据

## 9.5.3.9. SDATAC:停止读取数据连续模式

SDATAC 命令取消读取数据连续模式。此命令没有 SCLK 速率限制,但下一个命令必须等待 4tc 周期才能完成。

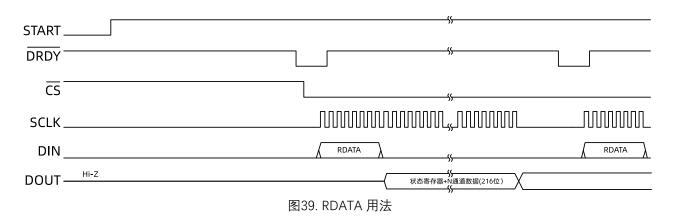

#### 9.5.3.10. RDATA:读取数据

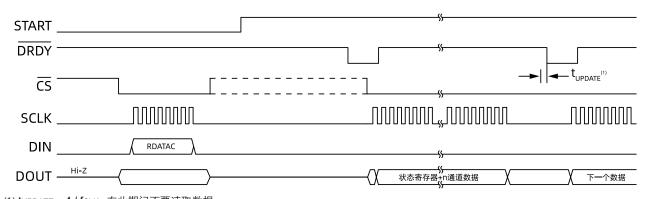

RDATA 命令在不处于读取数据连续模式时用最新数据加载输出移位寄存器。在 DRDY 变为低电平后发出此命令以读取转换结果。此命令没有 SCLK 速率限制,并且后续命令或数据检索 SCLK 不需要等待时间。若要在发出 RDATA 命令后从设备中检索数据,请确保 START 引脚为高电平或发出 START 命令。当使用 RDATA 命令读

取数据时,读取操作可以 与下一个DRDY发生重叠,而不会发生数据损坏。RDATA 可以在新数据可用后多次发送,从而支持多次数据回读。 下图说明了使用 RDATA 命令的推荐方式。RDATA 最适用于必须读取寄存器设

置或用户无法精确控制时序的系统。建议使用 RDATA 命令读取数据,以避免在未监视 DRDY 信号时发生数据损坏。

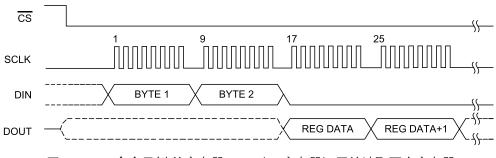

#### 9.5.3.11. RREG:从寄存器读取

RREG 命令读取一个或多个设备配置寄存器的内容。寄存器读取命令是一个两字节命令,后跟寄存器数据输出。第 —个字节包含命令和寄存器地址。第二个命令字节指定要读 1 的寄存器数。

第一个命令字节:001r rrrr,其中 r rrrr 是起始寄存器地址。

第二个命令字节:000n nnnn,其中 n nnnn 是要读取的寄存器数-1。

操作的第17个 SCLK 上升沿将第一个寄存器的 MSB 计时,如下图所示。当设备处于读取数据连续模式时,必须先发出 SDATAC 命令,然后才能发出 RREG 命令。RREG 命令可以随时发出。但是,由于此命令是多字节命令,因此存在 SCLK 速率限制,具体取决于发出 SCLK 的方式以满足 tspecode 时序。有关更多详细信息,请参阅SPI 接口部分的串行时钟(SCLK)小节。请注意,整个命令的CS为低电平。

图40. RREG 命令示例:从寄存器 00h (ID 寄存器)开始读取两个寄存器

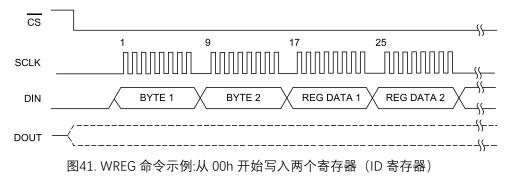

## 9.5.3.12. WREG:写寄存器

WREG 命令将数据写入一个或多个设备配置寄存器。寄存器写命令是一个两字节命令,后跟寄存器数据输入。第一 个字节包含命令和寄存器地址。第二个命令字节指定要写的寄存器数。

第一个命令字节:010r rrrr,其中 r rrrr 是起始寄存器地址。

第二个命令字节:000n nnnn.其中 n nnnn 是写入寄存器的个数-1。

在命令字节之后,寄存器数据跟随(MSB-first 格式),如下图所示。对于跨保留寄存器(0dh-11h)的多个寄存器写入,这些寄存器必须包含在寄存器计数中,并且必须写入保留寄存器的默认设置。WREG 命令可以随时发出。但是,由于此命令是多字节命令,因此存在 SCLK 速率限制,具体取决于发出 SCLK 的方式以满足 tspecope时序。对于整个命令,CS必须为低电平。

## 9.6. 寄存器列表

下表描述了各种 LHA787X 寄存器。

表19. 寄存器列表

| ADDRESS | REGISTER                  | 重置值 (十六 进制) | BIT 7      | BIT 6                                                                             | BIT 5       | BIT 4      | BIT 3      | BIT 2      | BIT 1      | BIT 0      |

|---------|---------------------------|-------------|------------|-----------------------------------------------------------------------------------|-------------|------------|------------|------------|------------|------------|

| 设备设置    | (只读寄存器)                   |             |            |                                                                                   |             |            |            |            |            |            |

| 00h     | ID                        | XX          | REV_ID2    | REV_ID1                                                                           | REV_ID0     | 0          | 0          | 0          | NU_CH2     | NU_CH1     |

| 全局设置    |                           |             |            |                                                                                   |             |            |            |            |            |            |

| 01h     | CONFIG1                   | 1E          | 0          | DAISYIN                                                                           | CLK_EN      | 1          | 1          |            | DR[2:0]    |            |

| 02h     | CONFIG2                   | C0          | 1          | 1                                                                                 | 0           | INT_TEST   | 0          | TEST_AMP0  | TEST_FF    | REQ[1:0]   |

| 03h     | CONFIG3                   | 00          | PDB_REFBUF | 0                                                                                 | VREF_4V     | 0          | OPAMP_REF  | PDB_OPAMP  | 0          | 0          |

| 04h     | FAULT                     | 00          | (          | COMP_TH[2:0]                                                                      |             | 0          | 0          | 0          | 0          | 0          |

| CHANNE  | CHANNEL-SPECIFIC SETTINGS |             |            |                                                                                   |             |            |            |            |            |            |

| 05h     | CH1SET                    | 00          | PD1        |                                                                                   | GAIN1 [2:0] |            | 0          | MUX1[2:0]  |            |            |

| 06h     | CH2SET                    | 00          | PD2        |                                                                                   | GAIN2[2:0]  |            | 0          | MUX2[2:0]  |            |            |

| 07h     | CH3SET                    | 00          | PD3        |                                                                                   | GAIN3[2:0]  |            | 0          | MUX3[2:0]  |            |            |

| 08h     | CH4SET                    | 00          | PD4        |                                                                                   | GAIN4[2:0]  |            | 0          | MUX4[2:0]  |            |            |

| 09h     | CH5SET                    | 00          | PD5        |                                                                                   | GAIN5[2:0]  |            | 0          |            | MUX5[2:0]  |            |

| 0Ah     | CH6SET                    | 00          | PD6        |                                                                                   | GAIN6[2:0]  |            | 0          |            | MUX6[2:0]  |            |

| 0Bh     | CH7SET                    | 00          | PD7        |                                                                                   | GAIN7[2:0]  |            | 0          |            | MUX7[2:0]  |            |

| 0Ch     | CH8SET                    | 00          | PD8        |                                                                                   | GAIN8[2:0]  |            | 0          |            | MUX8[2:0]  |            |

| 故障检测    | 状态寄存器(只该                  | 卖寄存器)       |            |                                                                                   |             |            |            |            |            |            |

| 12h     | FAULT_STATP               | XX          | IN8P_FAULT | IN7P_FAULT                                                                        | IN6P_FAULT  | IN5P_FAULT | IN4P_FAULT | IN3P_FAULT | IN2P_FAULT | IN1P_FAULT |

| 13h     | FAULT_STATN               | XX          | IN8N_FAULT | AULT IN7N_FAULT IN6N_FAULT IN5N_FAULT IN4N_FAULT IN3N_FAULT IN2N_FAULT IN1N_FAULT |             |            |            |            | IN1N_FAULT |            |

|         |                           |             |            |                                                                                   | GPIO SETTIN | GS         |            |            |            |            |

| 14h     | GPIO                      | 0F          | GPIOD4     | GPIOD3                                                                            | GPIOD2      | GPIOD1     | GPIOC4     | GPIOC3     | GPIOC2     | GPIOC1     |

<sup>(1)</sup> 当使用多个寄存器写命令时,寄存器 ODh、OEh、OFh、10h 和 11h 必须写入 O0h。

#### 9.6.1. 寄存器说明

## 9.6.1.1. ID: ID 控制寄存器(工厂编程,只读)(地址=00h) [reset=xxh]

该寄存器在器件制造期间被编程以指示器件特性。

表20. ID:ID 控制寄存器

| 7       | 6       | 5       | 4    | 3    | 2    | 1      | 0      |

|---------|---------|---------|------|------|------|--------|--------|

| REV_ID2 | REV_ID1 | REV_ID0 | 0    | 0    | 0    | NU_CH2 | NU CH1 |

| R-1h    | R-1h    | R-0h    | R-0h | R-0h | R-0h | R-xh   | R-xh   |

图例:R=只读;-n 二重置后的值

表21. ID:ID 控制寄存器字段说明

| Bit | Field       | Туре | Reset | Description                                                               |

|-----|-------------|------|-------|---------------------------------------------------------------------------|

| 7:5 | REV_ID[2:0] | R    | 6h    | <b>设备族标识。</b><br>此位指示设备系列。110:LHA787X。 000、001、010、011、<br>100、101、111:预留 |

| 4   | Reserved    | R    | 0h    | 总是读 0。                                                                    |

| 3:2 | Reserved   | R | 0h   | 总是读 0。                                        |

|-----|------------|---|------|-----------------------------------------------|

| 1:0 | NU_CH[2:0] | R | yn - | 设备标识位。00:8 通道设备 01:6 通道设备 10:4 通道设备 11:预<br>留 |

## 9.6.1.2. CONFIG1:配置寄存器 1 (地址=01h) [reset=1Eh]

该寄存器配置菊花链、时钟设置和每个 ADC 通道采样速率。

#### 表22. CONFIG1:配置寄存器 1

| 7      | 6        | 5      | 4      | 3      | 2       | 1       | 0       |

|--------|----------|--------|--------|--------|---------|---------|---------|

| 0      | DAISY IN | CLK EN | 1      | 1      | DR[2:0] | DR[2:0] | DR[2:0] |

| R/W-0h | R/W-0h   | R/W-0h | R/W-1h | R/W-1h | R/W-4h  | R/W-4h  | R/W-4h  |

图例:RW=读写;-n 二复位后的值

## 表23. CONFIG1:配置寄存器 1 字段说明

| Bit | Field    | Туре | Reset | Description                                                                      |

|-----|----------|------|-------|----------------------------------------------------------------------------------|

| 7   | Reserved | R/W  | 0h    | 必须设置为 0。                                                                         |

| 6   | DAISY_IN | R/W  | 0h    | <b>菊花链和多数据回读模式。</b><br>该位决定启用哪种模式。0:菊花链模式 1:多 数据回读模式                             |

| 5   | CLK_EN   | R/W  | Oh    | 时钟连接<br>该位确定当 CLKSEL 引脚=1 时内部振荡器信号是否连接到 CLK<br>引脚。<br>0:振荡器时钟输出禁用<br>1:振荡器时钟输出启用 |

| 4   | Reserved | R/W  | 1h    | 必须设置为 1。                                                                         |

| 3   | Reserved | R/W  | 1h    | 必须设置为 1。                                                                         |

| 2:0 | DR[2:0]  | R/W  | 1h    | <b>输出数据速率。</b><br>这些位决定输出数据速率                                                    |

<sup>(1)</sup>驱动外部设备时消耗额外的功率。

## 表24. 数据速率设置

| DR[2:0] RESOLUTION |               | 数据速率(kSPS) <sup>(1)</sup> |  |  |

|--------------------|---------------|---------------------------|--|--|

| 000                | 24-bit output | 64                        |  |  |

| 001                | 24-bit output | 32                        |  |  |

| 010                | 24-bit output | 16                        |  |  |

| 011                | 24-bit output | 8                         |  |  |

| 100                | 24-bit output | 4                         |  |  |

| 101                | 24-bit output | 2                         |  |  |

| 110                | 24-bit output | 1 (default)               |  |  |

| 111 24-bit output  |               | 128                       |  |  |

<sup>(1)</sup>其中 fclk=2.048MHz.

## 9.6.1.3. CONFIG2:配置寄存器 2 (地址=02h) [reset=C0h]

该寄存器配置测试信号的生成;有关更多细节,请参阅输入多路复用器部分。

## 表25. CONFIG2:配置寄存器 2

| 7      | 6      | 5      | 4          | 3      | 2        | 1 0            |

|--------|--------|--------|------------|--------|----------|----------------|

| 1      | 1      | 0      | INT TEST 0 |        | TEST AMP | TEST FREQ[1:0] |

| R/W-1h | R/W-1h | R/W-0h | R/W-0h     | R/W-0h | R/W-0h   | R/W-0h         |

图例:RW=读写;-n 二复位后的值

## 表26. CONFIG2:配置寄存器 2 字段说明

| Bit | Field          | Туре | Reset | Description                                                                                                                                   |

|-----|----------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Reserved       | R/W  | 110h  | 必须设置为 110。                                                                                                                                    |

| 4   | INT_TEST       | R/W  | 0h    | <b>测试信号源。</b><br>该位确定测试信号的源。0:测试信号由外部驱动 1:测试信号由内部产生                                                                                           |

| 3   | Reserved       | R/W  | 0h    | 必须设置为 0                                                                                                                                       |

| 2   | TEST_AMP       | R/W  | 0h    | <b>测信号幅度。</b><br>这些位确定校准信号幅度。<br>0: 1x (V <sub>VREFP</sub> -V <sub>VREFN</sub> )/1000<br>1: 1x (V <sub>VREFP</sub> -V <sub>VREFN</sub> )/1000 |

| 1:0 | TEST_FREQ[1:0] | R/W  |       | 测信号频率。这些比特确定测试信号频率。<br>00: 频率等于 fclk/2 <sup>21</sup><br>01:频率等于 fclk/2 <sup>20</sup><br>10:未使用<br>11:DC                                       |

## 9.6.1.4. CONFIG3:配置寄存器 3 (地址=03h) [reset=00]

该寄存器配置基准电压源和内部放大器。

## 表27. CONFIG3:配置寄存器 3

| 7          | 6      | 5       | 4      | 3         | 2         | 1        | 0        |

|------------|--------|---------|--------|-----------|-----------|----------|----------|

| PDB REFBUF | 0      | VREF 4V | 0      | OPAMP REF | PDB OPAMP | Reserved | Reserved |

| R/W-0h     | R/W-0h | R/W-0h  | R/W-0h | R/W-0h    | R/W-0h    | R/W-0h   | R/W-0h   |

## 表28. CONFIG3:配置寄存器 3 字段说明

| Bit | Field      | Туре | Reset | Description                                                                                                          |

|-----|------------|------|-------|----------------------------------------------------------------------------------------------------------------------|

| 7   | PDB_REFBUF | R/W  | 0h    | PDB_REFBUF:参考缓冲器被禁用<br>该位确定掉电参考缓冲器状态。<br>0:禁用内部基准缓冲器<br>1:启用内部基准缓冲器                                                  |

| 6   | Reserved   | R/W  | 0h    | 必须设置为 0。                                                                                                             |

| 5   | VREF_4V    | R/W  | 0h    | 内部参考电压。<br>该位确定内部参考电压 VREF。<br>0: VREF 设置为 2.4V<br>1: VREF 设置为 4V                                                    |

| 4   | Reserved   | R/W  | 0h    | 必须设置为 0。                                                                                                             |

| 3   | OPAMP_REF  | R/W  | 0h    | 运算放大器参考。<br>该位确定运算放大器同相输入是连接到 OPAMPP 引脚还是连接<br>到 内部(AVDD+AVSS)/2.<br>0:同相输入端连接到 OPAMPP 引脚<br>1:同相输入端连接到(AVDD+AVSS)/2 |

| 2   | PDB_OPAMP  | R/W  | 0h    | 运算放大器断电。该位使运算放大 器断电。<br>0:掉电运算放大器<br>1: 使能运算放大器                                                                      |

| 1   | Reserved   | R/W  | 0h    | 必须设置为 0。                                                                                                             |

| 0   | Reserved   | R/W  | 0h    | 必须设置为 0。                                                                                                             |

## 9.6.1.5. 故障:故障检测控制寄存器(地址=04h) [复位=00h]

该寄存器配置故障检测操作。

## 表29. 故障:故障检测控制寄存器

| 7            | 6            | 5            | 4      | 3      | 2      | 1      | 0      |

|--------------|--------------|--------------|--------|--------|--------|--------|--------|

| COMP TH[2:0] | COMP TH[2:0] | COMP TH[2:0] | 0      | 0      | 0      | 0      | 0      |

| R/W-0h       | R/W-0h       | R/W-0h       | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

图例:RW=读写;-n=复位后的值

## 表30. 故障:故障检测控制寄存器字段描述