# 兼容IEEE 802.3 AF/AT标准的以太网受电设备(PD)控制器

## 描述

SD4923E是一款兼容IEEE 802.3 af/at标准的以太网受电设备控制器芯片。该芯片为以太网供电系统(Power over Ethernet, PoE)中的受电设备提供了检测、分级和浪涌限流等功能。

芯片内部集成了耐压100V导通阻抗 $0.6\Omega$ 的功率MOSFET,支持最大850mA的工作电流。

芯片内置欠压保护和过热保护,并提供高电平的电源良好信号。

# 主要特点

- ◆ 兼容 IEEE 802.3 af/at 标准的受电设备接口

- ◆ 片上 100V、0.6Ω 的功率 MOSFET

- ◆ 180mA 浪涌限流

- ◆ 850mA 工作电流

- 电源良好信号指示

- ◆ 故障自动重试

- ◆ 欠压保护

- ◆ 过热保护

## 应用

- ◆ 视频监控

- ◆ IP 电话

- ► 无线 AP

# 产品规格分类

| 产品名称      | 封装类型            | 打印名称    | 环保等级 | 包装 |

|-----------|-----------------|---------|------|----|

| SD4923E   | ESOP-8-225-1.27 | SD4923E | 无卤   | 料管 |

| SD4923ETR | ESOP-8-225-1.27 | SD4923E | 无卤   | 编带 |

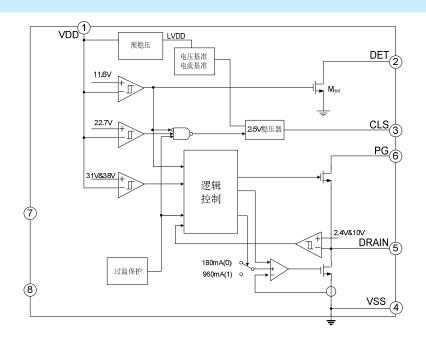

## 内部框图

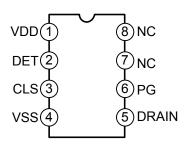

# 管脚排列图

# 管脚说明

| 管脚号 | 管脚名称  | I/O | 功 能 描 述                                              |

|-----|-------|-----|------------------------------------------------------|

| 1   | VDD   | Р   | POE 正电源输入                                            |

| 2   | DET   | I/O | POE 检测引脚,外接 24.9kΩ 电阻到 VDD,可以建立一个有效标记                |

| 3   | CLS   | 0   | POE 分级引脚,外接一个电阻到 VSS 可以设置 POE 功率等级,分级过程中该引脚被驱动至 2.5V |

| 4   | VSS   | G   | POE 负电源输入                                            |

| 5   | DRAIN | I/O | 连接开关电源负端                                             |

| 6   | PG    | 0   | 开关电源使能输出,高电平表示使能开关电源,下拉能力大于 200μA                    |

| 7   | NC    | NC  | 无连接                                                  |

| 8   | NC    | NC  | 无连接                                                  |

# 极限参数(除非特殊说明, Tamb=25°C, 参考电压为 VSS)

| 参数         | 端口              | 参数范围     | 单 位 |

|------------|-----------------|----------|-----|

| 输入电压       | VDD, DRAIN, DET | -0.3~100 | V   |

| 输入电压       | CLS             | -0.3~3   | V   |

| 输入电压       | PG,以DRAIN为参考    | -0.3~7   | V   |

| 输入电流       | VDD             | 0~500    | μΑ  |

| 输入电流       | PG              | 0~500    | μΑ  |

| 输入电流       | DET             | 0~2      | mA  |

| 输入电流       | DRAIN           | 内部限流960  | mA  |

| 输出电流       | CLS             | 0~60     | mA  |

| ESD HBM    |                 | 2        | KV  |

| ESD CDM    |                 | 750      | V   |

| 工作结温T」     |                 | +150     | °C  |

| 工作温度范围Tamb |                 | -40~+85  | °C  |

| 贮存温度范围Tstg |                 | -40~+125 | °C  |

# 电气参数(除非特殊说明, VDD=48V, T<sub>amb</sub>=25°C)

| 参数                             | 符号                             | 测试条件                                                                | 最小值      | 典型值  | 最大值  | 单位 |  |

|--------------------------------|--------------------------------|---------------------------------------------------------------------|----------|------|------|----|--|

| 检测                             |                                |                                                                     |          |      |      |    |  |

| 偏移电流                           | I <sub>offset</sub>            | DET 开路,VDD=DRAIN=1.9V,<br>测量 I <sub>VDD</sub> +I <sub>DRAIN</sub>   | 0.1      |      | 5    | μΑ |  |

| 休眠电流                           | I <sub>sleep</sub>             | DET 开路,VDD=DRAIN= 10.1V,<br>测量 I <sub>VDD</sub> +I <sub>DRAIN</sub> | 3        |      | 11   | μΑ |  |

| DET 漏电流                        | I <sub>leak</sub>              | VDD=DET=57V,测量 I <sub>DET</sub>                                     |          |      | 1.5  | μΑ |  |

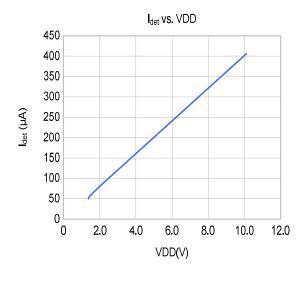

| 检测电流                           | I <sub>det</sub>               | VDD=DRAIN, VDD=1.4V                                                 |          | 56   | 70   | μΑ |  |

| Λ. bīī                         |                                | 测量 I <sub>VDD</sub> +I <sub>DRAIN</sub> +I <sub>DET</sub> VDD=10.1V |          | 412  | 440  |    |  |

| 分级                             |                                | 13.5V< VDD< 20.5V,测量I <sub>VDD</sub> +I <sub>DE</sub>               | T+IDBAIN |      |      |    |  |

|                                |                                | R <sub>CLS</sub> =1270Ω                                             | 1.92     | 2.12 | 2.20 | 0  |  |

|                                |                                | R <sub>CLS</sub> =243Ω                                              | 9.7      | 10.4 | 11.0 |    |  |

| 分级电流                           | I <sub>CLS</sub>               | R <sub>CLS</sub> =137Ω                                              | 17.5     | 18.3 | 19.4 | mA |  |

|                                | 1020                           | $R_{CLS}$ =90.9 $\Omega$                                            |          |      | 29.0 |    |  |

|                                |                                | R <sub>CLS</sub> =63.4Ω                                             | 37.5     | 39.4 | 41.5 |    |  |

| 4) (100 - 100 - 1) - 100 - 100 |                                | VDD 上升                                                              | 10.5     | 11.6 | 13.5 |    |  |

| 分级开启下限                         | V <sub>CL_OL</sub>             | VDD 下降                                                              | 9.0      | 10.5 | 12   | V  |  |

|                                |                                | VDD 上升                                                              | 21       | 22.7 | 24   | \  |  |

| 分级开启上限                         | 开启上限 V <sub>CL_OH</sub> VDD 下降 |                                                                     | 20       | 20.7 | 22   | V  |  |

| 传递MOSFET                       |                                |                                                                     |          |      |      |    |  |

| 导通阻抗                           | R <sub>on</sub>                | I <sub>DRAIN</sub> =300mA                                           |          | 0.6  | 1.2  | Ω  |  |

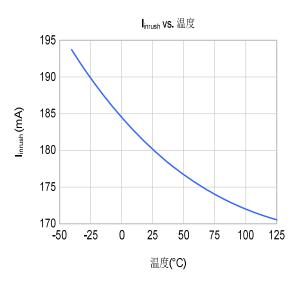

| 浪涌限流                           | I <sub>inrush</sub>            | V <sub>DRAIN</sub> =12V                                             | 130      | 180  | 240  | mA |  |

| 工作限流                           | I <sub>limit</sub>             | V <sub>DRAIN</sub> =1V                                              | 850      | 960  | 1080 | mA |  |

| UVLO(内部)                       |                                | T                                                                   |          |      | 1    |    |  |

| 内部 UVLO 阈值                     | V <sub>UVLO_IN</sub>           | UVLO=VSS, VDD 上升                                                    | 36.0     | 38.0 | 39.5 | V  |  |

|                                | V UVLO_IN                      | UVLO=VSS, VDD 下降                                                    | 30.0     | 31.0 | 32.5 | V  |  |

| 过温保护                           | 1                              | T                                                                   | 1        | I    | T    |    |  |

| 过温保护                           | T <sub>OTP</sub>               |                                                                     |          | 150  |      | °C |  |

| 过温保护迟滞                         | T <sub>OTP hys</sub>           |                                                                     |          | 20   |      | °C |  |

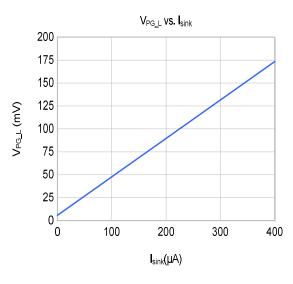

| 电源良好信号PG                       | 1                              | T                                                                   | _        | 1    | T    |    |  |

| PG 低电平                         | V <sub>PG L</sub>              | PG-DRAIN                                                            |          |      | 0.5  | V  |  |

| PG 高电平                         | V <sub>PG H</sub>              | PG-DRAIN                                                            |          | 5.6  |      | V  |  |

| PG 最大吸入电流                      | I <sub>sink PG</sub>           |                                                                     | 200      |      |      | μA |  |

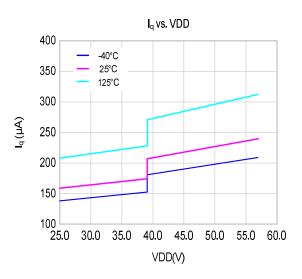

| 芯片静态电流                         | 1                              | I                                                                   |          |      | 1    |    |  |

| 静态电流                           | Iq                             | VDD=25~57V,测量 I <sub>VDD</sub> +I <sub>DET</sub>                    | 90       |      | 350  | μΑ |  |

版本号: 1.1

http://www.silan.com.cn

# 典型特性曲线

#### 功能描述

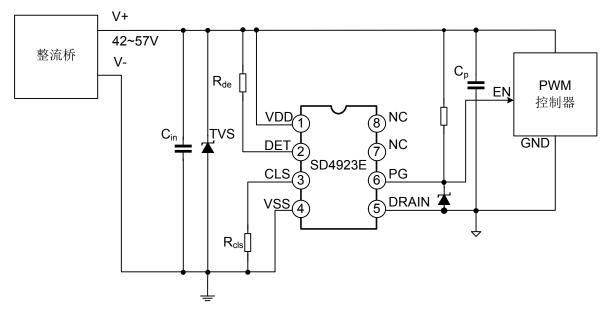

SD4923E是以太网供电系统中的受电设备控制器,该控制器完全兼容IEEE 802.3 af/at标准,集成了检测、分级、欠压保护、过热保护和电源良好指示信号等功能。 芯片内置一个100V的功率MOSFET,可以对系统进行浪涌限流和工作电流限流。

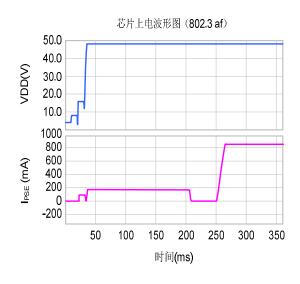

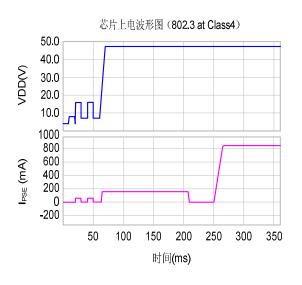

SD4923E处在以太网供电系统(802.3 af/at)中的工作过程如下:开始时供电设备(PSE)向PD设备提供两次处于2.8~10V之间的不同的检测电压,芯片SD4923E识别到检测电压,将外置的特征电阻24.9kΩ下拉至地VSS,供PSE设备检测;PSE设备检测成功后,将电压上拉至15.5~20.5V,SD4923E识别到该分级电压,关闭检测模块,CLS会输出2.5V电压来驱动外置的分级电阻,从而产生了分级电流供PSE检测;PSE分级成功后,将电压上拉至44~57V,并根据分级电流提供相应的功率,芯片检测到该工作电压,开始对PD设备进行浪涌限流操作,DRAIN端电压将以180mA的电流值进行放电,当DRAIN端电压下降至小于2.4V时,芯片输出高电平的电源良好信号PG,启动后面的开关电源,PD设备开始为负载正常供电。

#### 1. 检测

系统上电, PSE 设备向 PD 设备提供两次处于 2.8~10.1V 的电压, SD4923E 将开启检测模块, 特征电阻 24.9kΩ 被下拉至地, 形成两次不同电流, 供 PSE 检测。PSE 设备使用两次电压差值除以电流差,即可以计算出特征电阻值,若特征电阻处于 19.0~26.5kΩ 之间,表明检测成功,系统将进入分级状态。

当 PD 设备的输入电压处于 1.4~10.1V 时,检测模块始终打开,当电压高于 11.6V 时,检测模块将被关闭,DET 端口将呈现高阻。

#### 2. 分级

分级过程中, PSE 设备向 PD 设备提供一个 15.5V~20.5V 的电压, SD4923E 检测到电压高于 11.6V 且低于 22.7V, 将关闭检测模块, 开启分级模块, 该模块将 CLS 端口驱动至 2.5V 电压, 2.5/R<sub>cls</sub> 可以用于确定分级电流。PSE 设备将根据不同的分级电流为 PD 设备提供相应功率, 分级电流和功率等级的对应表如下。

| 级别 | 分级电流(mA) | PD 功率(W)   | 备注 |

|----|----------|------------|----|

| 0  | 0-4      | 0.44-12.95 | 默认 |

| 1  | 9-12     | 0.44-3.84  | 可选 |

| 2  | 17-20    | 3.84-6.49  | 可选 |

| 3  | 26-30    | 6.49-12.95 | 可选 |

| 4  | 36-44    | 12.95-25.5 | 可选 |

#### 3. 浪涌限流和上电操作

当分级操作完成后,PSE 将电压上拉至 44~57V 之间,SD4923E 检测到输入电压大于 22.7V,将关闭分级模块,同时输入电压高于 38V,UVLO 输出使能信号 UVLO\_A,此时限流模块开始工作,限流等级被设定在 180mA。DRAIN端将开始放电,当电压低于 2.4V 时,芯片将限流点切换至 960mA,并输出高电平的电源良好信号 PG,此后开关电源开始启动。

#### 4. 过流保护

正常工作时,当 DRAIN 端的输入电流高于 960mA 时,内置功率 MOSFET 将会进行限流操作,此时 DRAIN 端电

压将会上升,当 DRAIN 端电压高于 10V 时,芯片输出低电平 PG 信号,关闭开关电源。若 DRAIN 电压逐步下降,并下降至低于 2.4V 时,SD4923E 将会重新输出高电平的 PG 信号,重新开启开关电源。

#### 5. 电源良好信号指示

当 SD4923E 完成检测、分级操作后,若输入电压大于 38V 并且 DRAIN 电压小于 2.4V 时,芯片输出高电平的电压良好信号 PG,为开关电源提供开启指示信号。PG 信号以 DRAIN 端为参考,高电平的 PG 信号典型值为 5.6V,而低电平的 PG 信号小于 0.5V。PG 端至少可以吸入 200µA 电流。

#### 6. 欠压保护 UVLO

SD4923E 提供内部标准的欠压保护。当 VDD 超过 38V 时,PG 信号由下拉变化至高电平,MOSFET 开启,芯片开始正常工作;当 VDD 小于 31V 时,PG 信号由高电平变化至下拉,芯片进入保护状态,MOSFET 关断。

#### 7. 过温保护

当电路处于过温保护状态,芯片会关闭分级模块和功率 MOSFET,防止芯片损坏。过温保护的温度点为 150°C,过温保护的恢复具有迟滞特性以避免过温保护与正常工作状态的反复来回变化。迟滞区间为 20°C,即要等电路温度下降到 130°C,电路才能恢复正常工作。

#### 应用电路图

注: 以上线路及参数仅供参考,实际的应用电路请在充分的实测基础上设定参数。

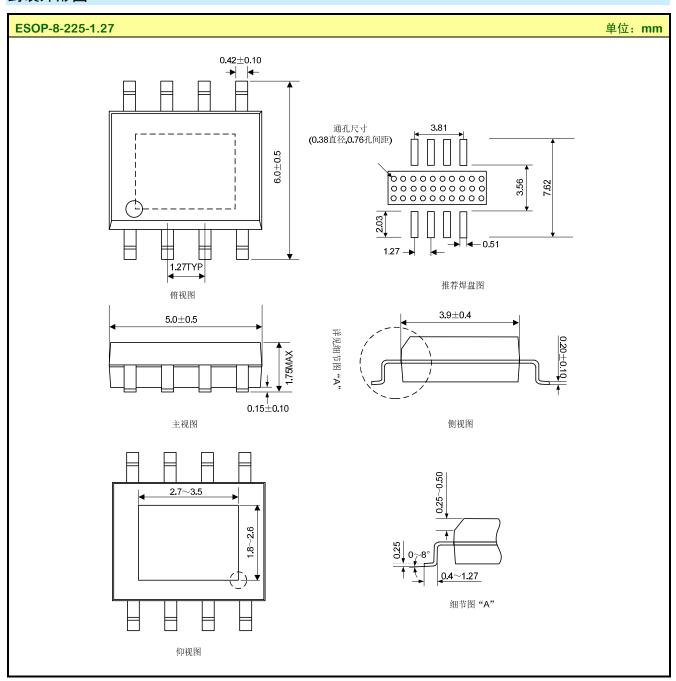

# 封装外形图

## MOS电路操作注意事项:

静电在很多地方都会产生,采取下面的预防措施,可以有效防止 MOS 电路由于受静电放电影响而引起的损坏:

- 操作人员要通过防静电腕带接地。

- 设备外壳必须接地。

- 装配过程中使用的工具必须接地。

- 必须采用导体包装或抗静电材料包装或运输。

### 声明:

- ◆ 士兰保留说明书的更改权,恕不另行通知!客户在下单前应获取最新版本资料,并验证相关信息是否完整和最新。

- ◆ 任何半导体产品特定条件下都有一定的失效或发生故障的可能,买方有责任在使用 Silan 产品进行系统设计和整机制造时遵守安全标准并采取安全措施,以避免潜在失败风险可能造成人身伤害或财产损失情况的发生!

- ◆ 产品提升永无止境,我公司将竭诚为客户提供更优秀的产品!

| 产品 | 名称:   | SD4923E       | 文档类型: | 说明                  | 书  |           |  |

|----|-------|---------------|-------|---------------------|----|-----------|--|

| 版  | 权:    | 杭州士兰微电子股份有限公司 | 公司主页: | 公司主页: http://www.si |    | an.com.cn |  |

| 版  | 本:    | 1.1           |       | 作                   | 者: | 王晨阳       |  |

| 修改 | 记录:   |               |       |                     |    |           |  |

|    | 1. 修改 | 女原浪涌/工作限流点范围  |       |                     |    |           |  |

| 版  | 本:    | 1.0           |       | 作                   | 者: | 王晨阳       |  |

| 修改 | 记录:   |               |       |                     |    |           |  |

|    | 1. 正式 | <b>戊版本发布</b>  |       |                     |    |           |  |