# CSM32RV20 User Manual

## 1 Introduction

#### 1.1 Feature and benefits

CSM32RV20 is a low-power MCU chip based on the RISC-V.

- Built-in RISC-V RV32IMAC Core (2.6 CoreMark/MHz)

- The working frequency is up to 32MHz

- Built-in 4kB SRAM

- The built-in 8B ALWAYS register and can save the data in the PD2

- Built-in 40kB embedded FLASH, 512B NVM, can ERASE and Program at least 100,000 times

- Built-in 2 SPI MASTER

- Built-in 1 I<sup>2</sup>C MASTER

- Built-in 4 UART, maximum rate 1Mbps

- Built-in 2 TIMER, each TIMER supports the 4 channel complementary PWM output

- With a rapid precision of 13/14/15/16bit ADC, 1.2v high precision reference;

- Wide ADC input voltage range:  $0 \sim VDD \text{ (VDD } \leq 4.8V)$

- The ADC supports 11 input channels and supports up to 9 touch key

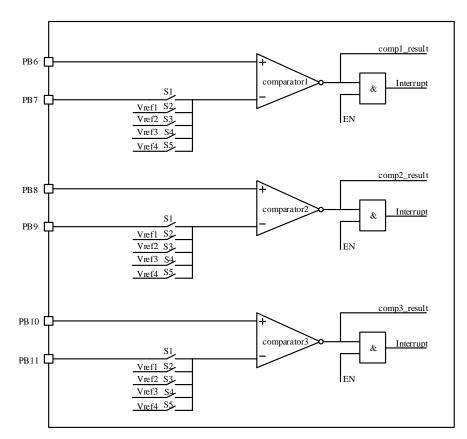

- Built-in 3 rapid comparators

- Built-in low voltage detection module

- Built-in RF detection module

- Most of the 30 GPIO, where PA supports external interrupts (with up to 16 external interrupts)

- Built-in hardware Watchdog

- Built-in 1 RTC, not working in PD2 mode

- Supports 4 low power modes, minimum power consumption less than 1 uA (Watchdog working)

- Built-in 32-bit real random number generator

- Support serial port and wireless ISP online upgrade (wireless ISP needs to be external to the Si24R1)

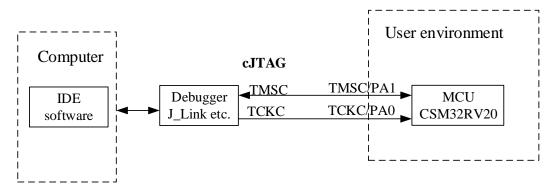

- Support the cjtag 2-line debugging interface

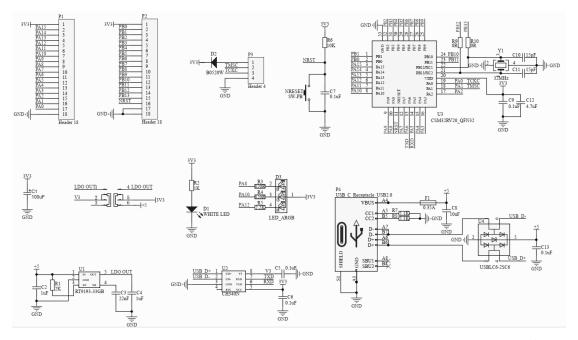

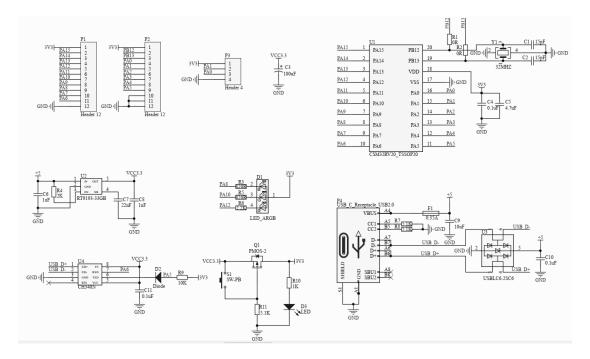

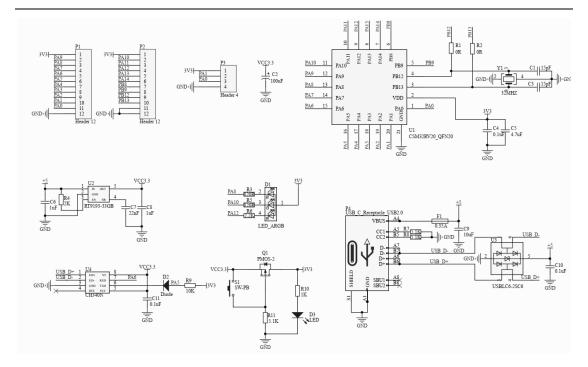

- Working voltage range: 1.8 ~ 5.5v

- Working temperature range:  $-40 \sim 105^{\circ}$ C

- 4x4mm QFN32 package TSSOP20 or QFN20 package

# 1.2 Pinning information

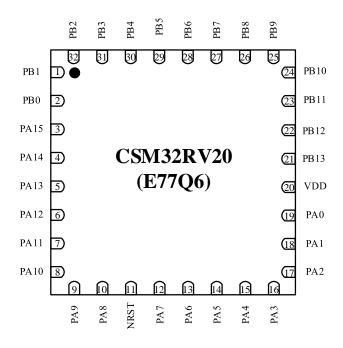

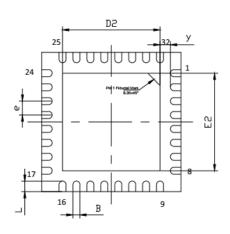

Figure1-1 Pin information (4x4 mm QFN32—E77Q6)

Table 1-1 Table 1-1 Pining description (4x4 mm QFN32—E77Q6)

| Pin | Name | I/O | Multiplexing function                     | Additional function |

|-----|------|-----|-------------------------------------------|---------------------|

| 1   | PB1  | Ю   |                                           | -                   |

| 2   | PB0  | Ю   |                                           | -                   |

| 3   | PA15 | Ю   | TIMER2_CH4N/UART4_TX/ EXTI[15]            | RF detection        |

| 4   | PA14 | Ю   | ADC_TRI/TIMER2_CH4/UART4_RX/ EXTI[14]     | -                   |

| 5   | PA13 | Ю   | TIMER2_CH3N/EXTI[13]                      | voltage output REFP |

| 6   | PA12 | Ю   | TIMER2_CH3/EXTI[12]                       | PGA input           |

| 7   | PA11 | Ю   | TIMER2_BKIN/TIMER2_CH2N/UART3_TX/EXTI[11] | voltage output REFN |

| 8   | PA10 | Ю   | TIMER1_BKIN/TIMER2_CH2/UART3_RX/EXTI[10]  | ADC_IN9             |

| 9   | PA9  | Ю   | TIMER1_CH1/UART1_TX/TIMER2_CH1N/EXTI[9]   | ADC_IN8             |

| 10  | PA8  | Ю   | SDA/UART1_RX/TIMER2_CH1/EXTI[8]           | ADC_IN7             |

| 11  | NRST | I   | External reset, low level reset           | -                   |

| 12  | PA7  | Ю   | SCL/MOSI/TIMER1_CH4N/EXTI[7]              | ADC_IN6             |

| 13  | PA6  | Ю   | UART1_TX/MISO/TIMER1_CH4/EXTI[6]          | ADC_IN5             |

| 14  | PA5  | Ю   | UART1_RX/SCK/TIMER1_CH3N/EXTI[5]          | ADC_IN4             |

# CSM32RV20

| 15 | PA4  | Ю | MOSI/TIMER1_CH1IN/TIMER1_CH3/UART2_TX/EXTI[4] | ADC_IN3 |

|----|------|---|-----------------------------------------------|---------|

| 16 | PA3  | Ю | MISO/TIMER1_CH1N/TIMER1_CH2N/UART2_RX/EXTI[3] | ADC_IN2 |

| 17 | PA2  | Ю | SCK/TIMER1_CH1/TIMER1_CH2/EXTI[2]             | -       |

| 18 | PA1  | Ю | TMSC/SDA/TIMER1_CH1N/EXTI[1]                  | -       |

| 19 | PA0  | Ю | TCKC/SCL/TIMER1_CH1/EXTI[0]                   | -       |

| 20 | VDD  | S | Power                                         | -       |

| 21 | PB13 | Ю | -                                             | OSC_OUT |

| 22 | PB12 | Ю | -                                             | OSC_IN  |

| 23 | PB11 | Ю | -                                             | COMP3-  |

| 24 | PB10 | Ю | -                                             | COMP3+  |

| 25 | PB9  | Ю | -                                             | COMP2-  |

| 26 | PB8  | Ю | -                                             | COMP2+  |

| 27 | PB7  | Ю | -                                             | COMP1-  |

| 28 | PB6  | Ю | -                                             | COMP1+  |

| 29 | PB5  | Ю | -                                             | -       |

| 30 | PB4  | Ю | SPI2_MISO                                     | -       |

| 31 | PB3  | Ю | SPI2_MOSI                                     | -       |

| 32 | PB2  | Ю | SPI2_SCK                                      | -       |

| -  | VSS  | S | Ground,on the bottom of the package           |         |

|    |      |   |                                               |         |

Note: S: Power supply pin; I: Input; O: Output; I/O: InOut;

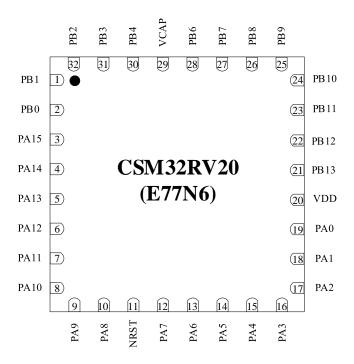

Figure 1-2 Pin information (4x4 mm QFN32—E77N6)

Table1-2 Pin description (4x4 mm QFN32—E77N6)

| Pin | Name | I/O | Multiplexing function                         | Additional function |

|-----|------|-----|-----------------------------------------------|---------------------|

| 1   | PB1  | Ю   |                                               | -                   |

| 2   | PB0  | Ю   |                                               | -                   |

| 3   | PA15 | Ю   | TIMER2_CH4N/UART4_TX/ EXTI[15]                | RF detection        |

| 4   | PA14 | Ю   | ADC_TRI/TIMER2_CH4/UART4_RX/ EXTI[14]         | -                   |

| 5   | PA13 | Ю   | TIMER2_CH3N/EXTI[13]                          | Voltage output REFP |

| 6   | PA12 | Ю   | TIMER2_CH3/EXTI[12]                           | PGA input           |

| 7   | PA11 | Ю   | TIMER2_BKIN/TIMER2_CH2N/UART3_TX/EXTI[11]     | Voltage output REFN |

| 8   | PA10 | Ю   | TIMER1_BKIN/TIMER2_CH2/UART3_RX/EXTI[10]      | ADC_IN9             |

| 9   | PA9  | Ю   | TIMER1_CH1/UART1_TX/TIMER2_CH1N/EXTI[9]       | ADC_IN8             |

| 10  | PA8  | Ю   | SDA/UART1_RX/TIMER2_CH1/EXTI[8]               | ADC_IN7             |

| 11  | NRST | Ι   | External reset, low level reset               | -                   |

| 12  | PA7  | Ю   | SCL/MOSI/TIMER1_CH4N/EXTI[7]                  | ADC_IN6             |

| 13  | PA6  | Ю   | UART1_TX/MISO/TIMER1_CH4/EXTI[6]              | ADC_IN5             |

| 14  | PA5  | Ю   | UART1_RX/SCK/TIMER1_CH3N/EXTI[5]              | ADC_IN4             |

| 15  | PA4  | Ю   | MOSI/TIMER1_CH1IN/TIMER1_CH3/UART2_TX/EXTI[4] | ADC_IN3             |

# CSM32RV20

| 16 | PA3  | Ю | MISO/TIMER1_CH1N/TIMER1_CH2N/UART2_RX/EXTI[3]                     | ADC_IN2 |

|----|------|---|-------------------------------------------------------------------|---------|

| 17 | PA2  | Ю | SCK/TIMER1_CH1/TIMER1_CH2/EXTI[2]                                 | -       |

| 18 | PA1  | Ю | TMSC/SDA/TIMER1_CH1N/EXTI[1]                                      | -       |

| 19 | PA0  | Ю | TCKC/SCL/TIMER1_CH1/EXTI[0]                                       | -       |

| 20 | VDD  | S | Power                                                             | -       |

| 21 | PB13 | Ю | -                                                                 | OSC_OUT |

| 22 | PB12 | Ю | -                                                                 | OSC_IN  |

| 23 | PB11 | Ю | -                                                                 | COMP3-  |

| 24 | PB10 | Ю | -                                                                 | COMP3+  |

| 25 | PB9  | Ю | -                                                                 | COMP2-  |

| 26 | PB8  | Ю | -                                                                 | COMP2+  |

| 27 | PB7  | Ю | -                                                                 | COMP1-  |

| 28 | PB6  | Ю | -                                                                 | COMP1+  |

| 29 | VCAP | S | LDO power supply output (only internal circuits are used, and 1uF |         |

| 29 | VCAF | S | is required to be decouped to the ground)                         | -       |

| 30 | PB4  | Ю | SPI2_MISO                                                         | -       |

| 31 | PB3  | Ю | SPI2_MOSI                                                         | -       |

| 32 | PB2  | Ю | SPI2_SCK                                                          | -       |

| -  | VSS  | S | Ground,on the bottom of the package                               |         |

|    |      |   |                                                                   |         |

Note: S: Power supply pin; I: Input; O: Output; I/O: InOut;

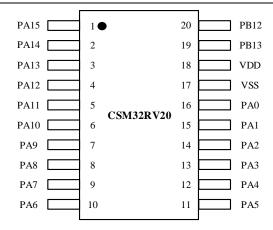

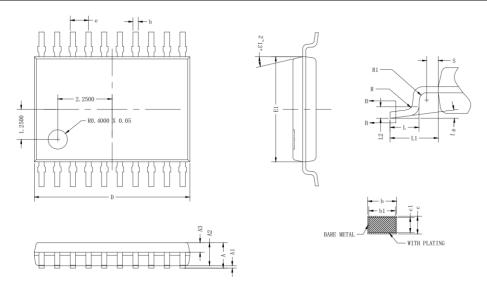

Figure 1-3 Pin information (TSSOP 20)

Table1-3 Pin description (TSSOP 20)

| Pin | Name | I/O | Multiplexing function                    | Additional function |

|-----|------|-----|------------------------------------------|---------------------|

| 1   | PA15 | Ю   | TIMER2_CH4N/TX4/ EXTI[15]                | RF detection        |

| 2   | PA14 | Ю   | ADC_TRI/TIMER2_CH4/RX4/ EXTI[14]         | -                   |

| 3   | PA13 | Ю   | TIMER2_CH3N/EXTI[13]                     | Voltage output REFP |

| 4   | PA12 | Ю   | TIMER2_CH3/EXTI[12]                      | PGA input           |

| 5   | PA11 | Ю   | TIMER2_BKIN/TIMER2_CH2N/TX3/EXTI[11]     | Voltage output REFN |

| 6   | PA10 | Ю   | TIMER1_BKIN/TIMER2_CH2/RX3/EXTI[10]      | ADC_IN9             |

| 7   | PA9  | Ю   | TIMER1_CH1/TX/TIMER2_CH1N/EXTI[9]        | ADC_IN8             |

| 8   | PA8  | Ю   | SDA/RX/TIMER2_CH1/EXTI[8]                | ADC_IN7             |

| 9   | PA7  | Ю   | SCL/MOSI/TIMER1_CH4N/EXTI[7]             | ADC_IN6             |

| 10  | PA6  | Ю   | TX1/MISO/TIMER1_CH4/EXTI[6]              | ADC_IN5             |

| 11  | PA5  | Ю   | RX1/SCK/TIMER1_CH3N/EXTI[5]              | ADC_IN4             |

| 12  | PA4  | Ю   | MOSI/TIMER1_CH1IN/TIMER1_CH3/TX2/EXTI[4] | ADC_IN3             |

| 13  | PA3  | Ю   | MISO/TIMER1_CH1N/TIMER1_CH2N/RX2/EXTI[3] | ADC_IN2             |

| 14  | PA2  | Ю   | SCK/TIMER1_CH1/TIMER1_CH2/EXTI[2]        | -                   |

| 15  | PA1  | Ю   | TMSC/SDA/TIMER1_CH1N/EXTI[1]             | -                   |

| 16  | PA0  | Ю   | TCKC/SCL/TIMER1_CH1/EXTI[0]              | -                   |

| 17  | VSS  | S   | Ground                                   | -                   |

| 18  | VDD  | S   | Power                                    | -                   |

| 19  | PB13 | О   | -                                        | OSC_OUT             |

| 20  | PB12 | I   | -                                        | OSC_IN              |

|     | •    | •   |                                          |                     |

Note: S: Power supply pin; I: Input; O: Output; I/O: InOut

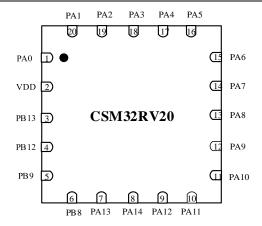

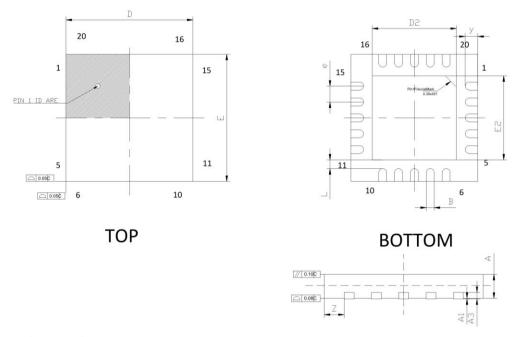

Figure 1-4 Pin information (3x3 mm QFN20)

Table1-4 Pin description (3x3 mm QFN20)

| Pin | Name | I/O | Multiplexing function                    | Additional function |

|-----|------|-----|------------------------------------------|---------------------|

| 1   | PA0  | Ю   | TCKC/SCL/TIMER1_CH1/EXTI[0]              | -                   |

| 2   | VDD  | S   | Power                                    | -                   |

| 3   | PB13 | Ю   | -                                        | OSC_OUT             |

| 4   | PB12 | Ю   | -                                        | OSC_IN              |

| 5   | PB9  | Ю   | -                                        | COMP2-              |

| 6   | PB8  | Ю   | -                                        | COMP2+              |

| 7   | PA13 | Ю   | TIMER2_CH3N/EXTI[13]                     | Voltage output REFN |

| 8   | PA14 | Ю   | ADC_TRI/TIMER2_CH4/RX4/ EXTI[14]         | -                   |

| 9   | PA12 | Ю   | TIMER2_CH3/EXTI[12]                      | PGA input           |

| 10  | PA11 | Ю   | TIMER2_BKIN/TIMER2_CH2N/TX3/EXTI[11]     | Voltage output REFP |

| 11  | PA10 | Ю   | TIMER1_BKIN/TIMER2_CH2/RX3/EXTI[10]      | ADC_IN9             |

| 12  | PA9  | Ю   | TIMER1_CH1/TX/TIMER2_CH1N/EXTI[9]        | ADC_IN8             |

| 13  | PA8  | Ю   | SDA/RX/TIMER2_CH1/EXTI[8]                | ADC_IN7             |

| 14  | PA7  | Ю   | SCL/MOSI/TIMER1_CH4N/EXTI[7]             | ADC_IN6             |

| 15  | PA6  | Ю   | TX1/MISO/TIMER1_CH4/EXTI[6]              | ADC_IN5             |

| 16  | PA5  | Ю   | RX1/SCK/TIMER1_CH3N/EXTI[5]              | ADC_IN4             |

| 17  | PA4  | Ю   | MOSI/TIMER1_CH1IN/TIMER1_CH3/TX2/EXTI[4] | ADC_IN3             |

| 18  | PA3  | Ю   | MISO/TIMER1_CH1N/TIMER1_CH2N/RX2/EXTI[3] | ADC_IN2             |

| 19  | PA2  | Ю   | SCK/TIMER1_CH1/TIMER1_CH2/EXTI[2]        | -                   |

| 20  | PA1  | Ю   | TMSC/SDA/TIMER1_CH1N/EXTI[1]             | -                   |

| -   | VSS  | S   | Ground,on the bottom of the package      |                     |

Note: S: Power supply pin; I: Input; O: Output; I/O: InOut;

# Contents

| 1  | Introduction |          |                                                         |    |  |

|----|--------------|----------|---------------------------------------------------------|----|--|

|    | 1.1          | Fea      | ture and benefits                                       | 1  |  |

|    | 1.2          | Pin      | ning information                                        | 2  |  |

| Co | ntents       |          |                                                         | 8  |  |

| 2  | Men          | nory and | d Bus architecture                                      | 17 |  |

|    | 2.1          | Sys      | stem architecture                                       | 17 |  |

|    | 2.2          | Me       | mory map                                                | 18 |  |

|    | 2.3          | Em       | bedded SRAM                                             | 19 |  |

|    | 2.4          | Em       | bedded FLASH/NVM                                        | 19 |  |

|    | 2.5          | Em       | bedded ROM                                              | 19 |  |

|    | 2.6          | DA       | TA_ALWAYS                                               | 19 |  |

| 3  | Low          | power    | mode(LPMODE)                                            | 20 |  |

|    | 3.1          | LP       | MODE                                                    | 21 |  |

|    |              | 3.1.1    | Entering LPMODE                                         | 21 |  |

|    |              | 3.1.2    | Exiting LPMODE                                          | 21 |  |

|    |              | 3.1.3    | Standby mode(IDLE)                                      | 21 |  |

|    |              | 3.1.4    | Sleep mode(SLEEP)                                       | 22 |  |

|    |              | 3.1.5    | Power-down mode1(PD1)                                   | 22 |  |

|    |              | 3.1.6    | Power-down mode2(PD2)                                   | 23 |  |

|    | 3.2          | Lov      | w power registers                                       | 24 |  |

|    |              | 3.2.1    | LPMODE register (LPMODE)                                | 24 |  |

|    |              | 3.2.2    | LPMODE flag register (LPRST_FLAG)                       | 24 |  |

| 4  | Rese         | et and C | lock Control                                            | 25 |  |

|    | 4.1          | Res      | set                                                     | 25 |  |

|    | 4.2          | Sof      | Etware reset register (SRST)                            | 25 |  |

|    | 4.3          | Clo      | ock                                                     | 26 |  |

|    |              | 4.3.1    | Functional introduction                                 | 26 |  |

|    | 4.4          | Clo      | ock control register                                    | 28 |  |

|    |              | 4.4.1    | Peripheral clock enable contolr register (CMU_PER_EN) . | 28 |  |

|    |              | 4.4.2    | Clock source selection (CMU_CLK_SEL)                    | 28 |  |

|    |              | 4.4.3    | Clock frequency prescaler register (CMU_CLK_DIV)        | 29 |  |

|    |              | 4.4.4    | Clock source enable register (CLK_SRC_EN)               | 30 |  |

|   |      | 4.4.5    | Clock state register (CMU_OSC_SR)                          | 31   |

|---|------|----------|------------------------------------------------------------|------|

|   |      | 4.4.6    | RCOSC frequency select register (RCOSC_SEL)                | 32   |

|   | 4.5  | CM       | IU register mapping                                        | 32   |

| 5 | Gene | eral and | alternate function I/Os                                    | 33   |

|   | 5.1  | GPI      | IO Functional description                                  | 33   |

|   |      | 5.1.1    | Main function                                              | 33   |

|   |      | 5.1.2    | Input configuration                                        | 36   |

|   |      | 5.1.3    | Output configuration                                       | 38   |

|   |      | 5.1.4    | Alternate function configuration                           | 39   |

|   |      | 5.1.5    | Analog function configuration                              | 39   |

|   | 5.2  | GPl      | IOA register description                                   | 40   |

|   |      | 5.2.1    | GPIOA Mode Control register (GPIOA_MODER)                  | 40   |

|   |      | 5.2.2    | GPIOA Output control register (GPIOA_OTYPER)               | 42   |

|   |      | 5.2.3    | GPIOA input mode control register(GPIOA_ITYPER)            | 44   |

|   |      | 5.2.4    | GPIOA pull up/down control register (GPIOA_PUPDR)          | 46   |

|   |      | 5.2.5    | GPIOA performance control register (GPIOA_SDR)             | 48   |

|   |      | 5.2.6    | GPIOA interrupt mode register (GPIOA_LPMR)                 | 50   |

|   |      | 5.2.7    | GPIOA external interrupt collect enable register (GPIOA_IN | TER) |

|   |      |          | 51                                                         |      |

|   |      | 5.2.8    | GPIOA input data register (GPIOA_IDR)                      | 51   |

|   |      | 5.2.9    | GPIOA output data register (GPIOA_ODR)                     | 52   |

|   |      | 5.2.10   | GPIOA set/reset register (GPIOA_BSR)                       | 52   |

|   |      | 5.2.11   | GPIOA alternate function high register $(GPIOA\_AFRH)$     | 53   |

|   |      | 5.2.12   | GPIOA alternate function low register (GPIOA_AFRL)         | 54   |

|   | 5.3  | GPI      | IOA register mapping                                       | 55   |

|   | 5.4  | GP       | IOB register description                                   | 56   |

|   |      | 5.4.1    | GPIOB Mode Control register (GPIOB_MODER)                  | 56   |

|   |      | 5.4.2    | GPIOB Output control register (GPIOB_OTYPER)               | 57   |

|   |      | 5.4.3    | GPIOB input mode control register (GPIOB_ITYPER)           | 60   |

|   |      | 5.4.4    | GPIOB pull up/down control register(GPIOB_PUPDR)           | 61   |

|   |      | 5.4.5    | GPIOB performance control register (GPIOB_SDR)             | 63   |

|   |      | 5.4.6    | GPIOB input data register (GPIOB_IDR)                      | 65   |

|   |      | 5.4.7    | GPIOB output data register (GPIOB_ODR)                     | 66   |

|   |      | 5.4.8    | GPIOB set/reset register (GPIOB_BSR)                       | 66   |

|   |       | 5.4.9    | GPIOB alternate function high register (GPIOB_AFRH) . | 67 |

|---|-------|----------|-------------------------------------------------------|----|

|   |       | 5.4.10   | GPIOB alternate function low register (GPIOB_AFRL)    | 68 |

|   | 5.5   | GPI      | IOB register mapping                                  | 69 |

| 6 | Inter | rupt     |                                                       | 70 |

|   | 6.1   | Inte     | errupt introduction                                   | 70 |

|   | 6.2   | CLI      | IC Registers                                          | 71 |

|   |       | 6.2.1    | CLIC Interrupt Pending (clicintip)                    | 72 |

|   |       | 6.2.2    | CLIC Interrupt Enable (clicintie)                     | 72 |

|   |       | 6.2.3    | CLIC Interrupt Configuration (clicintcfg)             | 73 |

|   |       | 6.2.4    | CLIC Configuration (cliccfg)                          | 74 |

|   | 6.3   | CLI      | IC Registers Mapping                                  | 75 |

|   | 6.4   | Ext      | ernal interrupt (EXTI)                                | 75 |

|   |       | 6.4.1    | EXTI introduction                                     | 75 |

|   |       | 6.4.2    | External interrupt input status register (EXTI_ISR)   | 76 |

|   |       | 6.4.3    | External interrupt input enable register (EXTI_IEN)   | 77 |

|   | 6.5   | EX       | TI register mapping                                   | 77 |

|   | 6.6   | Inte     | errupt operations                                     | 77 |

|   |       | 6.6.1    | Entering or exiting an interrupt                      | 77 |

|   |       | 6.6.2    | Interrupt Levels and Priorities                       | 78 |

|   | 6.7   | Inte     | errupt Control Status Registers                       | 79 |

|   |       | 6.7.1    | Machine Status Registe (mstatus)                      | 79 |

|   |       | 6.7.2    | Machine Trap Vector (mtvec)                           | 79 |

|   |       | 6.7.3    | Machine Interrupt Enable (mie)                        | 81 |

|   |       | 6.7.4    | Machine Interrupt Pending (mip)                       | 81 |

|   |       | 6.7.5    | Machine Cause (mcause)                                | 82 |

|   |       | 6.7.6    | Machine Trap Vector Table (mtvt)                      | 83 |

|   |       | 6.7.7    | Handler Address and Interrupt-Enable (mnxti)          | 84 |

|   |       | 6.7.8    | Machine Interrupt Status (mintstatus)                 | 85 |

|   |       | 6.7.9    | Scratch register for machine trap handlers (mscratch) | 85 |

|   |       | 6.7.10   | Machine exception program counter (mepc)              | 86 |

|   |       | 6.7.11   | Machine bad address or instruction (mtval)            | 86 |

|   | 6.8   | Inte     | errupt status register mapping                        | 87 |

| 7 | Real  | -time cl | ock (RTC)                                             | 88 |

|   | 7.1   | RTO      | C introduction                                        | 88 |

|   | 7.2  | Reg     | gister description                                   | 88  |

|---|------|---------|------------------------------------------------------|-----|

|   |      | 7.2.1   | Machine mode timer register (mtime)                  | 88  |

|   |      | 7.2.2   | Machine mode timer compare value register (mtimecmp) | 89  |

|   | 7.3  | Reg     | gister Mapping                                       | 90  |

| 8 | WD   | G       |                                                      | 91  |

|   | 8.1  | Ind     | ividual watch dog(IWDG)                              | 91  |

|   |      | 8.1.1   | Introduction                                         | 91  |

|   |      | 8.1.2   | IWDG register description                            | 92  |

|   |      | 8.1.3   | IWDG register mapping                                | 94  |

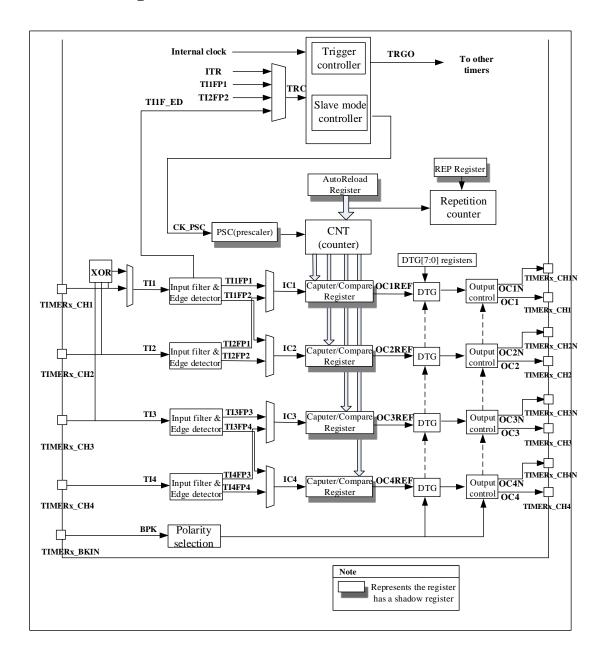

| 9 | Adva | anced-c | ontrol TIMER1&TIMER2                                 | 94  |

|   | 9.1  | Intr    | oduction                                             | 94  |

|   | 9.2  | Ma      | in characteristics                                   | 95  |

|   | 9.3  | Blo     | ck diagram                                           | 96  |

|   | 9.4  | Fun     | nctional description                                 | 96  |

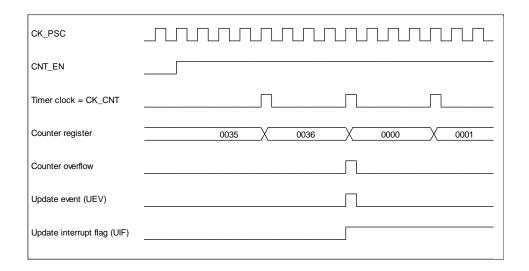

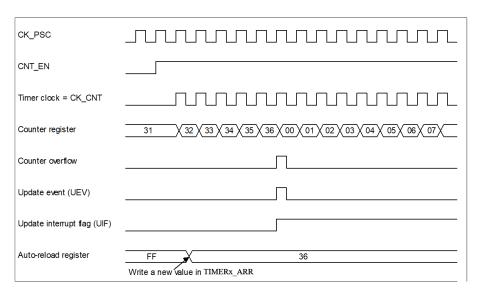

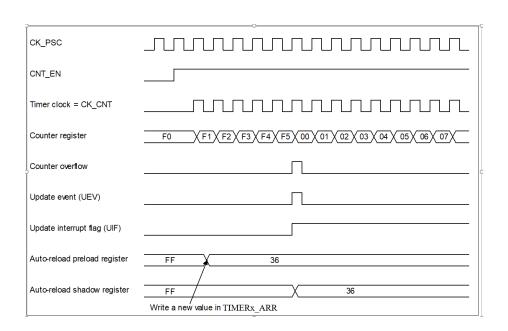

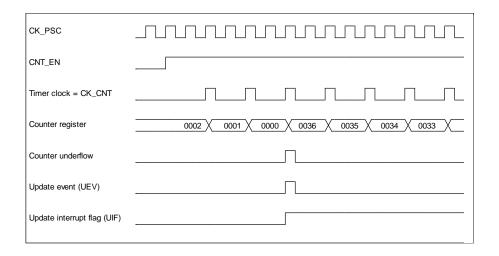

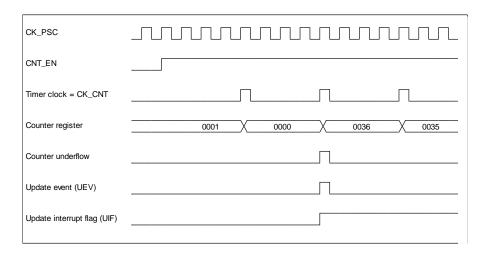

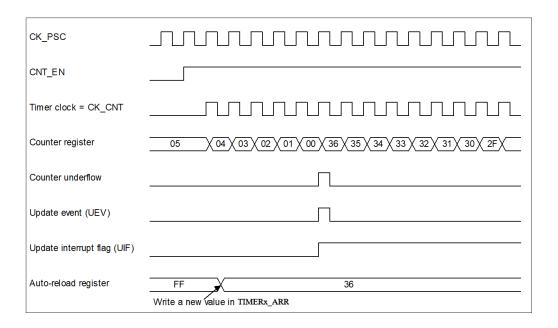

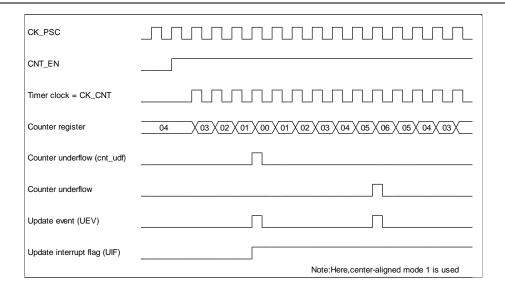

|   |      | 9.4.1   | Time-base unit                                       | 96  |

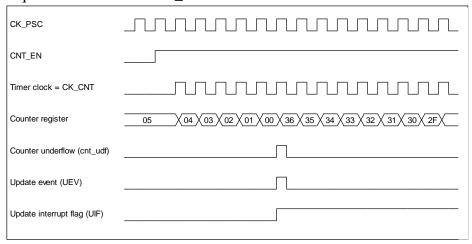

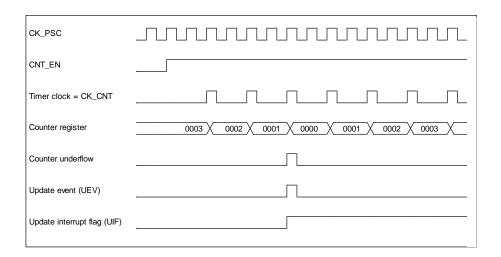

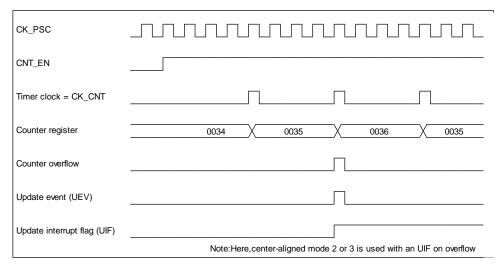

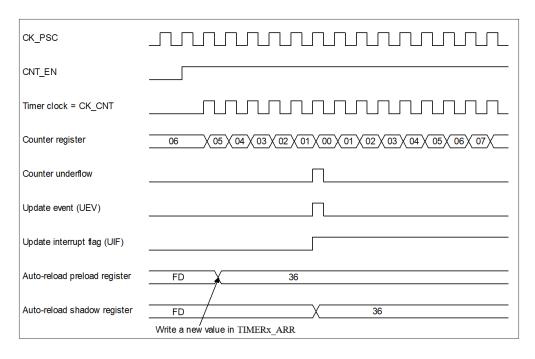

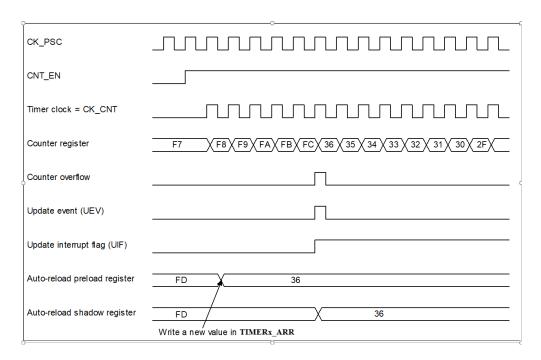

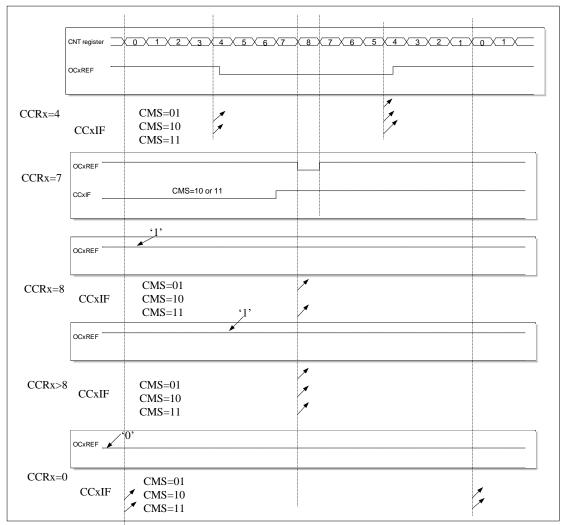

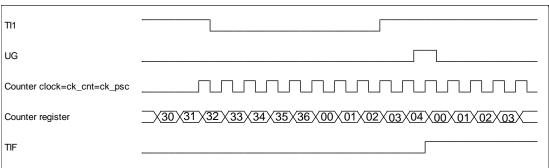

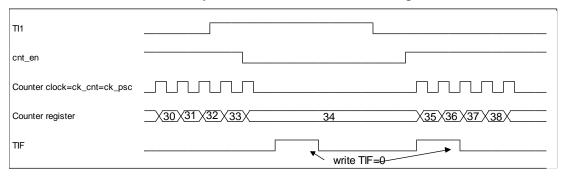

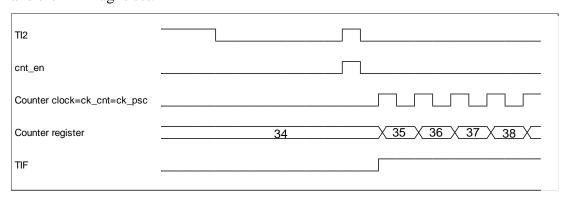

|   |      | 9.4.2   | Counter modes                                        | 98  |

|   |      | 9.4.3   | Repetition counter                                   | 107 |

|   |      | 9.4.4   | Clock selection                                      | 107 |

|   |      | 9.4.5   | Capture/compare channels                             | 109 |

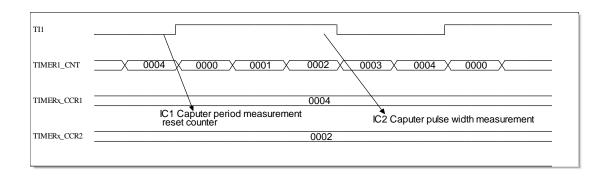

|   |      | 9.4.6   | Input capture mode                                   | 110 |

|   |      | 9.4.7   | PWM input mode                                       | 111 |

|   |      | 9.4.8   | Forced output mode                                   | 113 |

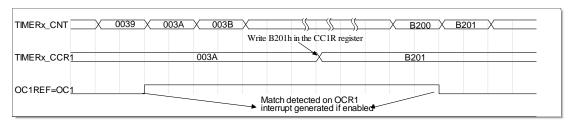

|   |      | 9.4.9   | Output compare mode                                  | 113 |

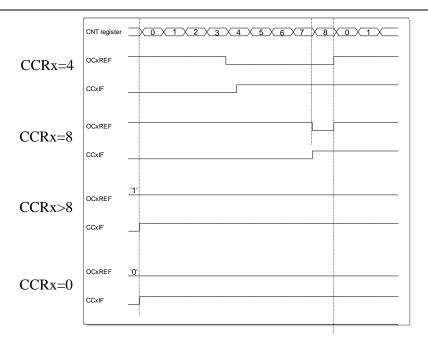

|   |      | 9.4.10  | PWM mode                                             | 114 |

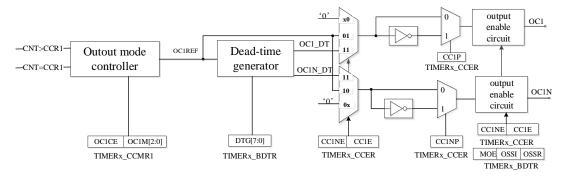

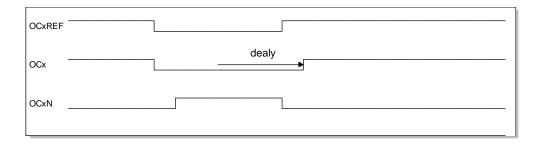

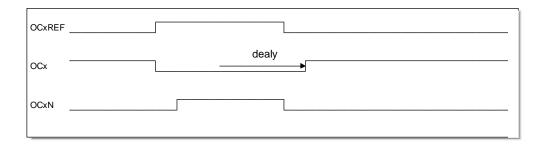

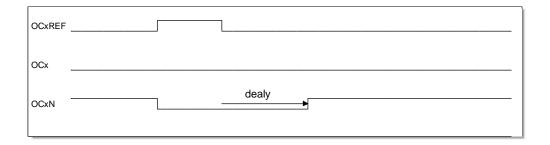

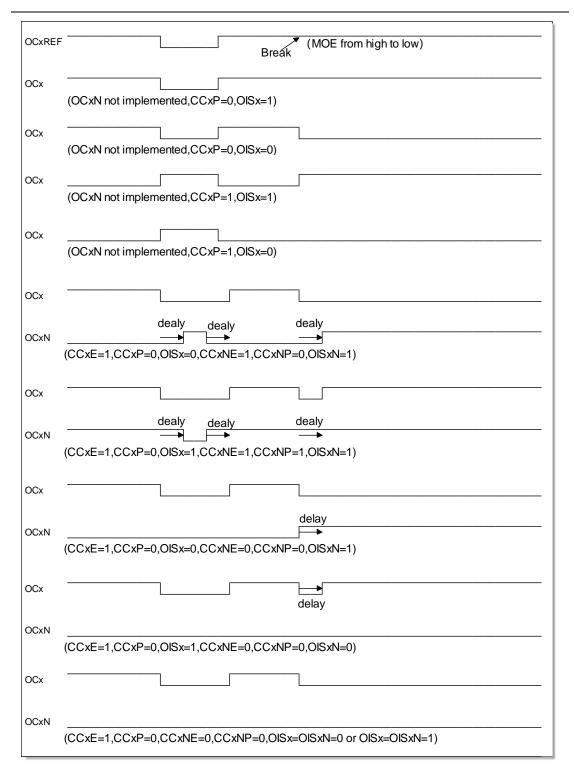

|   |      | 9.4.11  | Complementary outputs and dead-time insertion        | 118 |

|   |      | 9.4.12  | Using the break function                             | 120 |

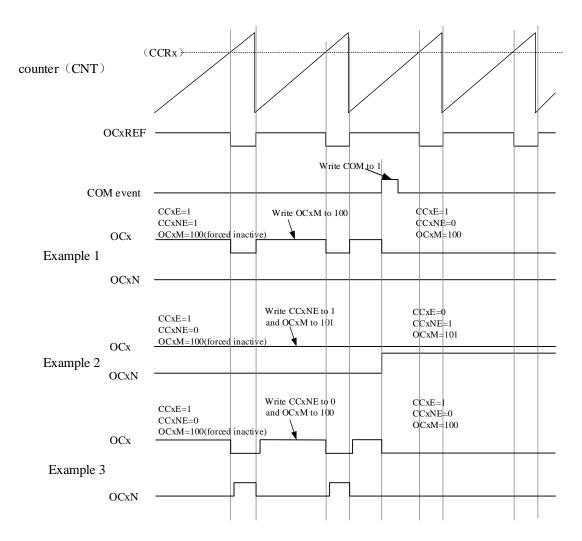

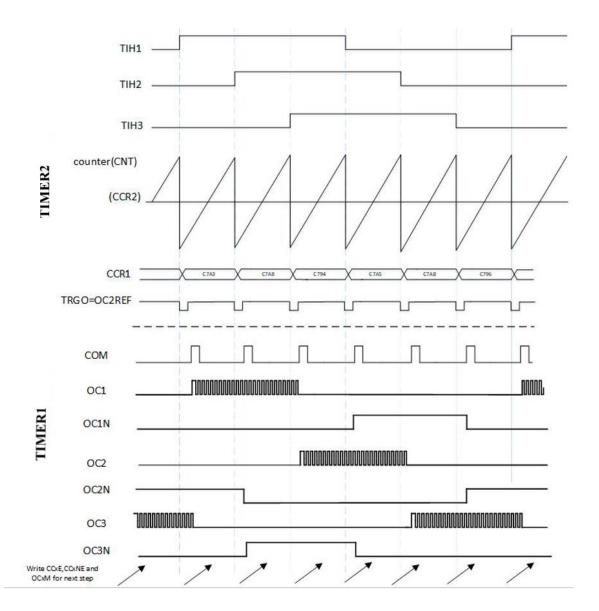

|   |      | 9.4.13  | 6-step PWM generation                                | 123 |

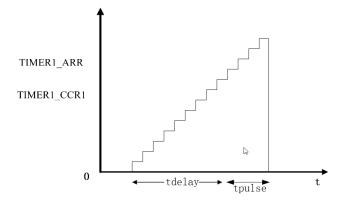

|   |      | 9.4.14  | One-pluse mode                                       | 124 |

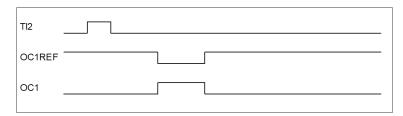

|   |      | 9.4.15  | Timer input XOR function                             | 125 |

|   |      | 9.4.16  | Interfacing with Hall sensors                        | 125 |

|   |      | 9.4.17  | Synchronization of timer and external trigger        | 127 |

|   | 9.5  | TIN     | MERx registers description                           | 130 |

|   |      | 9.5.1   | Control Register (TIMERx_CR1)                        | 130 |

|   |      | 9.5.2   | Filter register (TIMERx_ICF)                         | 135 |

|    | 9.5.3     | Interrupt enable register (TIMERx_DIER)        | 136 |

|----|-----------|------------------------------------------------|-----|

|    | 9.5.4     | Status registe (TIMERx_SR)                     | 137 |

|    | 9.5.5     | Event generation register (TIMERx_EGR)         | 139 |

|    | 9.5.6     | Capture/Compare mode register 1 (TIMERx_CCMR1) | 141 |

|    | 9.5.7     | Capture/Compare mode register 2 (TIMERx_CCMR2) | 144 |

|    | 9.5.8     | Capture/Compare enable register(TIMERx_CCER)   | 145 |

|    | 9.5.9     | Count register (TIMERx_CNT)                    | 149 |

|    | 9.5.10    | Prescaler register (TIMERx_PSC)                | 149 |

|    | 9.5.11    | Auto-reload register (TIMERx_ARR)              | 150 |

|    | 9.5.12    | Repetition counter register (TIMERx_RCR)       | 150 |

|    | 9.5.13    | Capture/Compare register 1 (TIMERx_CCR1)       | 151 |

|    | 9.5.14    | Capture/Compare register 2 (TIMERx_CCR2)       | 152 |

|    | 9.5.15    | Capture/Compare register 3 (TIMERx_CCR3)       | 153 |

|    | 9.5.16    | Capture/Compare register 4 (TIMERx_CCR4)       | 154 |

|    | 9.5.17    | Break and dead-time register(TIMERx_BDTR)      | 155 |

|    | 9.5.18    | Timer clock enable register (TIMER_CLKEN)      | 158 |

|    | 9.6 TIN   | M1&TIM2 register mapping                       | 158 |

| 10 | WUP       |                                                | 160 |

|    | 10.1 Intr | oduction                                       | 160 |

|    | _         | gister description                             |     |

|    | 10.3 Wu   | p data register (wup_data)                     | 160 |

|    | 10.3.1    | Wup interrupt enable register (wup_irq_en)     | 161 |

|    | 10.3.2    | Wup interrupt register (wup_irq)               | 161 |

|    | 10.4 Reg  | gister mapping                                 | 162 |

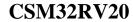

| 11 | Analog/   | digital conversion (ADC)                       | 163 |

|    | 11.1 Intr | oduction                                       | 163 |

|    | 11.2 Fur  | nctional description                           | 163 |

|    | 11.2.1    | Main features                                  | 163 |

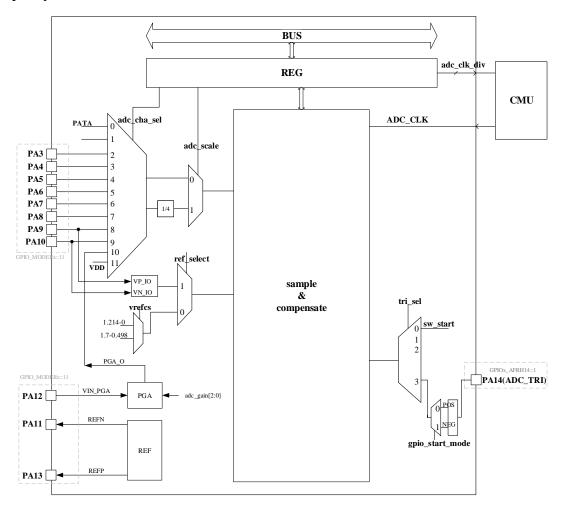

|    | 11.2.2    | Conversion timing.                             | 165 |

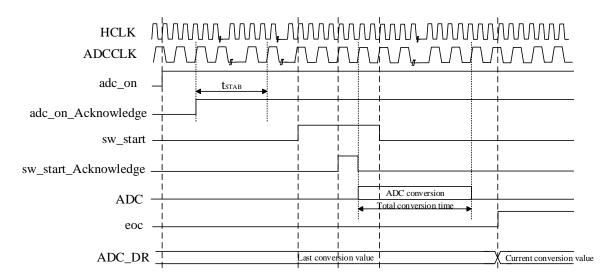

|    | 11.2.3    | Internal PATA temperature change curve         | 166 |

|    | 11.3 Reg  | gister description                             | 166 |

|    | 11.3.1    | ADC Status register (ADC_ISR)                  | 166 |

|    | 11.3.2    | ADC interrupt enable register (ADC_IER)        | 167 |

|    | 11.3.3    | ADC control register (ADC_CR)                  | 168 |

|    | 11   | 1.3.4 ADC channel select register (ADC_SEL)  | 168 |

|----|------|----------------------------------------------|-----|

|    | 11   | 1.3.5 ADC Data register (ADC_DR)             | 170 |

|    | 11   | 1.3.6 ADC general control register (ADC_CCR) | 170 |

|    | 11   | 1.3.7 ADC resolution register (ADC_CFG)      | 172 |

|    | 11.4 | Register mapping                             | 173 |

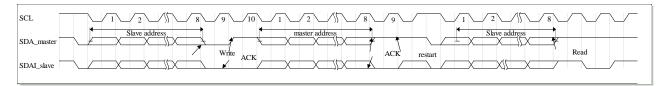

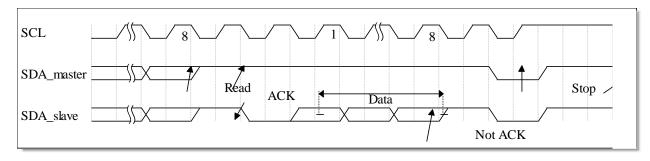

| 12 | 120  | C interface                                  | 174 |

|    | 12.1 | Introduction                                 | 174 |

|    | 12   | 2.1.1 Main features                          | 174 |

|    | 12.2 | Functional description.                      | 175 |

|    | 12.3 | I2C register description                     | 178 |

|    | 12   | 2.3.1 Status register (I2C_STATUS)           | 178 |

|    | 12   | 2.3.2 Control register (I2C_CTRL)            | 179 |

|    | 12   | 2.3.3 DATA register (I2C_DATA)               | 180 |

|    | 12.4 | Register mapping                             | 180 |

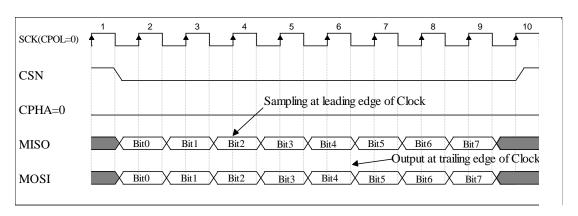

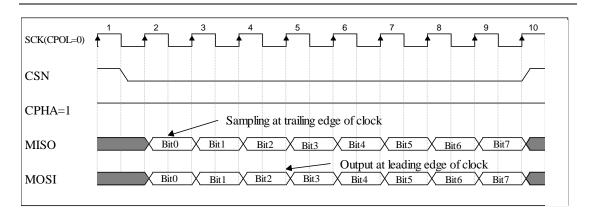

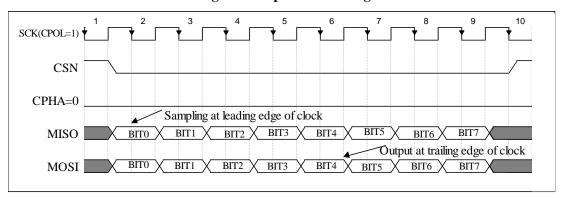

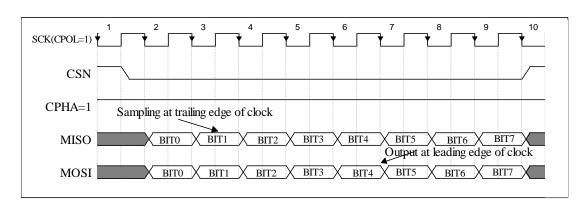

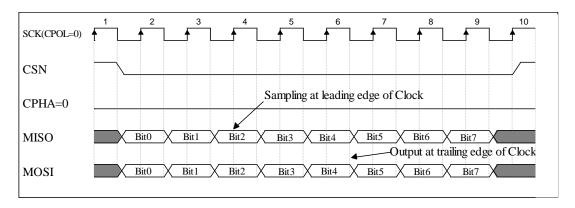

| 13 | Ser  | rial peripheral interface (SPI1)             | 181 |

|    | 13.1 | Introduction                                 | 181 |

|    | 13   | 3.1.1 Main features                          | 181 |

|    | 13.2 | Functional description                       | 181 |

|    | 13.3 | Register description                         | 184 |

|    | 13   | 3.3.1 Control register (SPI1_CTRL)           | 184 |

|    | 13   | 3.3.2 Date register (SPI1_DATA)              | 185 |

|    | 13   | 3.3.3 Status register (SPI1_STATUS)          | 186 |

|    | 13.4 | Register mapping                             | 186 |

| 14 | Ser  | rial peripheral interface (SPI2)             | 187 |

|    | 14.1 | Introduction                                 | 187 |

|    | 14   | 4.1.1Main features                           | 187 |

|    | 14.2 | Functional description                       | 187 |

|    | 14.3 | Register description                         | 188 |

|    | 14   | 4.3.1 Control register (SPI2_CTRL)           | 188 |

|    | 14   | 4.3.2 Data register (SPI2_DATA)              | 189 |

|    | 14   | 4.3.3 Status register (SPI2_STATUS)          | 190 |

|    | 14.4 | Register mapping                             |     |

| 15 | Asy  | ynchronous receiver/transmitter (UART)       | 191 |

|    | 15.1 | Introduction                                 | 191 |

|    | 15   | .1.1 Main features                                            | 191    |

|----|------|---------------------------------------------------------------|--------|

|    | 15.2 | Functional description                                        | 191    |

|    | 15.3 | UART pin mapping                                              | 193    |

|    | 15.4 | Register description                                          | 193    |

|    | 15   | .4.1 Control register (UART_CTRL)                             | 193    |

|    | 15   | .4.2 Data register (UART_DATA)                                | 195    |

|    | 15   | 4.4.3 Auto BPS configuration register (AUTOBPS_CONFIG)        | 196    |

|    | 15   | 3.4.4 Auto BPS result register (AUTOBPS_RESULT)               | 197    |

|    | 15.5 | Register mapping                                              | 197    |

| 16 | Lov  | w voltage detection (LVD)                                     | 198    |

|    | 16.1 | Introduction                                                  | 198    |

|    | 16.2 | Register description                                          | 198    |

|    | 16   | 5.2.1 Low voltage detection interrupt enable register (LVD_IF | RQ_EN) |

|    |      | 198                                                           |        |

|    | 16   | 5.2.2 Low voltage detection interrupt register (LV_IRQ)       | 198    |

|    | 16   | 5.2.3 Low voltage threshold register (LV_TH)                  | 199    |

|    | 16.3 | Register mapping                                              | 200    |

| 17 | Rai  | ndom number generation (RANDGEN)                              | 200    |

|    | 17.1 | Introduction                                                  | 200    |

|    | 17   | 7.2 Register description                                      | 200    |

|    | 17.3 | Register mapping                                              | 201    |

| 18 | Co   | mparator (COMP)                                               | 202    |

|    | 18.1 | Introduction                                                  | 202    |

|    | 18.2 | Register description                                          | 202    |

|    | 18   | 3.2.1 Comparator control register (COMP_CTRL)                 | 202    |

|    | 18   | 3.2.2 Comparator interrupt register (COMP_IRQ)                | 204    |

|    | 18   | 3.2.3 Comparator result registger (COMP_RESULT)               | 204    |

|    | 18.3 | Register mapping                                              | 205    |

| 19 | UA   | RT auto BPS (TRIM)                                            | 206    |

|    | 19.1 | Introduction                                                  | 206    |

|    | 19.2 | Register description                                          | 206    |

|    | 19   | 2.2.1 Configuration register (TRIM_CLK_CFG)                   | 206    |

|    | 19   | 2.2.2 Result register (TRIM_CLK_RESULT)                       | 207    |

|    | 19   | 2.2.3 Flag register (TRIM_CLK_FLAG)                           | 207    |

# CSM32RV20

|    | 19.3 | Usage method                                         | 208 |

|----|------|------------------------------------------------------|-----|

|    | 1    | 9.3.1 Baud rate adaptation                           | 208 |

| 20 | FL   | ASH/NVM burning                                      | 209 |

|    | 20.1 | FLASH/NVM Main features                              | 209 |

|    | 20.2 | FLASH/NVM mappig                                     | 209 |

|    | 20.3 | FLASH/NVM operation                                  | 210 |

|    | 20.4 | FLASH r/w protection                                 | 212 |

|    | 20.5 | FLASH/NVM burning                                    | 212 |

| 21 | De   | bug support                                          | 213 |

|    | 21.1 | Introduction                                         | 213 |

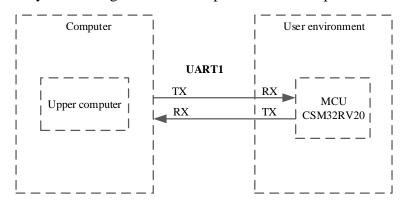

|    | 21.2 | cJTAG debug interface                                | 213 |

| 22 | RI   | SC-V Core                                            | 214 |

| 23 | Ch   | ip electronic signature                              | 215 |

|    | 23.1 | Chip version ID (Version ID)                         | 215 |

|    | 23.2 | MCUID                                                | 216 |

| 24 | Ele  | ectrical parameters                                  | 217 |

|    | 24.1 | Parameter conditions                                 | 217 |

|    | 2    | 4.1.1 Max/min value                                  | 217 |

|    | 2    | 4.1.2 Typical value                                  | 217 |

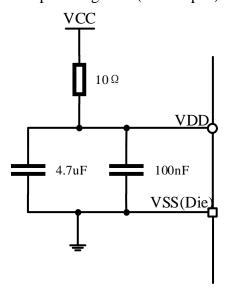

|    | 2    | 4.1.3 Power supply solution                          | 217 |

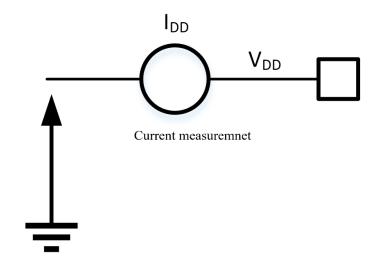

|    | 2    | 4.1.4 Current consumption measurement                | 218 |

|    | 24.2 | Absolute maximum ratings                             | 218 |

|    | 24.3 | Operating conditions                                 | 219 |

|    | 2    | 4.3.1 General operating conditions                   | 219 |

|    | 2    | 4.3.2 Internal system clock source parameters        | 220 |

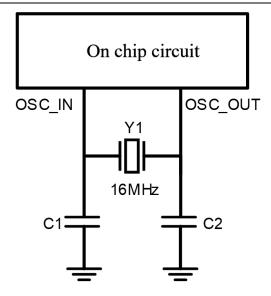

|    | 2    | 4.3.3 External system clock source parameters        | 220 |

|    | 2    | 4.3.4 I/O port parameters                            | 222 |

|    | 2    | 4.3.5 ADC parameters                                 | 223 |

|    | 2    | 4.3.6 Low voltage detection threshold                | 224 |

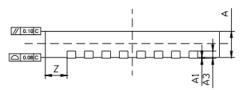

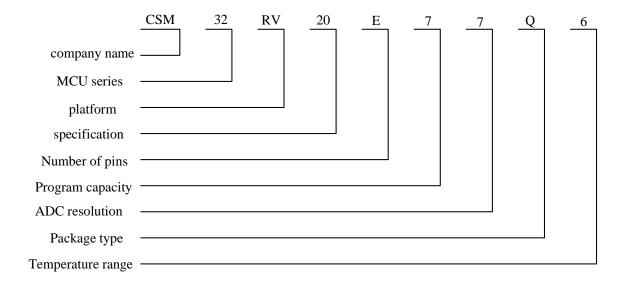

| 25 | Pa   | ckage information                                    | 225 |

|    | 25.1 | Chip screen printing style                           | 228 |

|    | 25.2 | Detailed description of chip screen printing letters | 229 |

| 26 | Ap   | pplication design-in information                     | 230 |

| 27 | Re   | vision history                                       | 232 |

# CSM32RV20

| 28 | Order information                         | .233 |

|----|-------------------------------------------|------|

| 29 | Technical Support and Contact information | .234 |

# 2 Memory and Bus architecture

# 2.1 System architecture

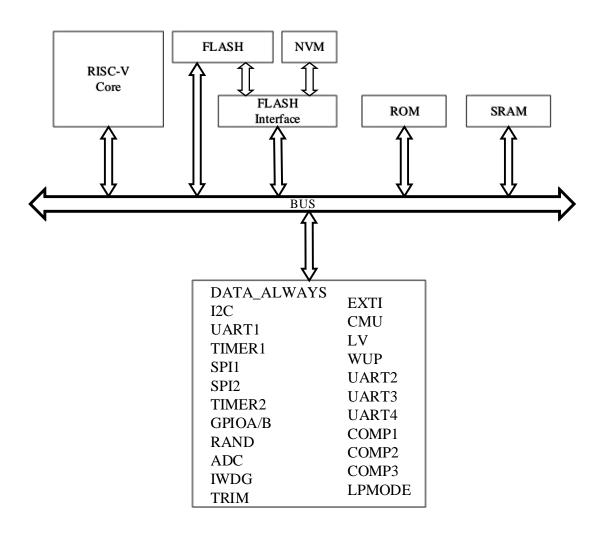

Figure 2-1 System architecture

# 2.2 Memory map

**Table2-1 Memory mapping**

| Base         | Тор         | Attr | Description      | Notes                             |

|--------------|-------------|------|------------------|-----------------------------------|

| 0x0000_0100  | 0x0000_0FFF | RWX  | <u>Debug</u>     | Debug Address Space               |

| 0x0200_0000  | 0x01FF_FFFF | RW   | CLIC             | On Core Complex Devices           |

| 0x2000_0000  | 0x2000_9FFF | RWX  | CODE             | 40kB FLASH Program Space          |

| [1]          |             | RWX  | NVM              | 512B NVM (save the data of users) |

| 0x2002_0000  | 0x2002_0FFF | RWX  | <u>DATA</u>      | 4kB SRAM                          |

| 0x2002_8000  | 0x2002_8007 | RWX  | DATA_ALWAYS      | Save the data in PD2 mode         |

| 0x2100_0000  | 0x2100_17FF | RWX  | CODE             | Bootloader ROM                    |

| 0x3000_0004  | 0x3000_000F | RW   | <u>12C</u>       |                                   |

| 0x3000_0010  | 0x3000_0017 | RW   | <u>UART1</u>     |                                   |

| 0x3000_0018  | 0x3000_005F | RW   | TIMER1           |                                   |

| 0x3000_0060  | 0x3000_006B | RW   | SPI1             |                                   |

| 0x3000_0070  | 0x3000_007B | RW   | SPI2             | Peripherals                       |

| 0x3000_0098  | 0x3000_0103 | RW   | TIMER2           |                                   |

| 0x3000_0200  | 0x3000_026F | RW   | <u>GPIOA/B</u>   |                                   |

| 0x3000_0238  | 0x3000_023F | RW   | RANDGEN          |                                   |

| 0x3000_0280  | 0x3000_0297 | RW   | ADC              |                                   |

| 0x3000_02A0  | 0x3000_02AB | RW   | <u>IWDG</u>      |                                   |

| 0x3000_02C0  | 0x3000_02C7 | RW   | <u>EXTI</u>      |                                   |

| 0x3000_02E0  | 0x3000_02F7 | RW   | <u>CMU</u>       | Peripherals                       |

| 0x3000_e0330 | 0x3000_0333 | RW   | LV               |                                   |

| 0x3000_0600  | 0x3000_0607 | RW   | <u>LPMODE</u>    |                                   |

| 0x3000_0610  | 0x3000_061B | RW   | WUP              |                                   |

| 0x3000_0700  | 0x3000_0707 | RW   | <u>UART2</u>     |                                   |

| 0x3000_0800  | 0x3000_0807 | RW   | <u>UART3</u>     |                                   |

| 0x3000_0900  | 0x3000_0907 | RW   | <u>UART4</u>     |                                   |

| 0x3000_0B00  | 0x3000_0D0B | RW   | <u>COMP1/2/3</u> |                                   |

|              |             |      |                  |                                   |

<sup>[1]</sup> NVM can only be accessed by the operating function flash\_operation(), which cannot be accessed by absolute address,more details see 20.3.

## 2.3 Embedded SRAM

CSM32RV20 has a built-in 4KB SRAM that supports byte, half-word (16 bit), or full-word (32 bit). The start address of SRAM is 0x2002\_0000.

## 2.4 Embedded FLASH/NVM

FLASH/NVM Key Features:

- FLASH size is  $10K \times 32$ bits (40K Bytes);

- NVM size is  $128 \times 32$  bits (512Bytes);

- FLASH/NVM is origanized by sector with 512 bytes per sector;

- Support for online reading and writing, which can be used to store user programs and data;

- Support read by byte, half-word or full-words, write by byte

- Support sector-by-sector erase

- Support whole Chip Erase(erase FLASH and NVM)

- FLASH supports read/write protection

## 2.5 Embedded ROM

Built-in ROM is used to store boot.

## 2.6 DATA\_ALWAYS

The DATA\_ALWAYS memory can save the data in the Power Down 2 mode. Each read and write takes up 12 system clock cycles and can only be written in words. In addition, MCU is executed for single cycle, without bus delay.

| address (HEX) | Reset value     | Function                                           |

|---------------|-----------------|----------------------------------------------------|

| 0x2002_8000   | Arbitrary value | Special memory, only lost data under power failure |

| 0x2002_8004   | Arbitrary value | Special memory, only lost data under power failure |

## 3 Low power mode(LPMODE)

After the system or the power supply is reset, the microcontroller is in the running state. Clock execution program code for the MCU using RCOSC in the running state by default. When the MCU does not need to continue running, you can use multiple low-power modes to save power consumption, such as waiting for an external interrupt. Based on the minimum power consumption, the fastest start time and the need of the available wake source, select the best compromise to help the user select a low power mode.

#### CSM32RV20 has 4 low power mode:

- Standby mode (the core is stopped, and the peripherals can still work);

- Sleep mode (all clocks can be stopped expect 3K clock);

- Power-down mode1 (see Table 3-1);

- Power-down mode2 (see Table 3-1, IO holds the state before Power-down);

Furthermore, in operating mode, power consumption can be reduced by:

- Reduce the system clock;

- Close the clock of the unused peripherals;

- Reasonable configuration of I / O

**Table3-1 LPMODE overview**

| Operating mode           | LPMODE | Main<br>LDO | LPLDO | RCOSC | OSC | 3K[1] | Wake-up source                    |

|--------------------------|--------|-------------|-------|-------|-----|-------|-----------------------------------|

| Standby<br>mode(IDLE)    | 2'b00  | ON          | ON    | ON    | ON  | ON    | Any interrupt, watch dog or reset |

| Sleep<br>mode(SLEEP)     | 2'b01  | ON          | ON    | OFF   | OFF | ON    | Any interrupt watch dog or reset  |

| Power-down<br>mode1(PD1) | 2'b10  | OFF         | ON    | OFF   | OFF | ON    | Any interrupt watch dog or reset  |

| Power-down<br>mode2(PD2) | 2'b11  | OFF         | OFF   | OFF   | OFF | ON    | Any interrupt watch dog or reset  |

[1] 3k refers to the low speed clock within the MCU, which rate is 3kHz and cannot be closed:

#### 3.1 LPMODE

## 3.1.1 Entering LPMODE

Execute WFI instruction after configuring LPMODE register, if there is no interrupt at present, MCU can enter low power mode directly. If there is an interrupt and the interrupt is enabled, the MCU can't enter the low power mode and continue to execute the program after the WFI instruction.

## 3.1.2 Exiting LPMODE

In order to successfully exit the low-power mode, it is necessary to enable the interrupt used for wake-up before executing the WFI instruction, and enable the corresponding clicintie (CLIC Interrupt Enable) register. After executing the WFI instruction and successfully entering the low-power mode, if the interrupt general enable has been turned on (mstate.MIE=1), when the enabled interrupt is generated, the MCU wakes up and jumps to the interrupt handler function to continue execution. If the interrupt master enable is not turned on (mstate.MIE=0), when the enabled interrupt is generated, the MCU wakes up and continues to run from the next instruction of the WFI instruction.

#### 3.1.3 Standby mode(IDLE)

In standby mode, the MCU core stops running; any enabled interrupt, watchdog, and reset can make the MCU exit standby mode immediately. Standby mode wake-up consumes the least amount of time, but consumes more power.

| Standby mode (gray part is not working module) |           |               |  |  |  |  |  |  |

|------------------------------------------------|-----------|---------------|--|--|--|--|--|--|

| RISC-V Core                                    | GPIO      | RTC           |  |  |  |  |  |  |

| FLASH/NVM                                      | SPI1/SPI2 | TIMER1/TIMER2 |  |  |  |  |  |  |

| RAM                                            | I2C       | WUP           |  |  |  |  |  |  |

| DATA_ALWAYS                                    | UART1     | WDT           |  |  |  |  |  |  |

| RCOSC                                          | LV        | COMP          |  |  |  |  |  |  |

| OSC                                            | RANDGEN   | ADC           |  |  |  |  |  |  |

| 3K                                             | UART2/3/4 | cJTAG         |  |  |  |  |  |  |

## 3.1.4 Sleep mode(SLEEP)

In standby mode, the MCU core stops running and the high-speed clock is turned off. Arbitrarily enabled interrupts, watchdogs, and resets allow the MCU to exit sleep mode. When the enabled interrupt is generated, it takes a few to several hundred clocks, depending on the clock source, before execution can continue. The relevant peripheral can only work in 3K clock.

Note: In the sleep mode, the clock source of RTC/SPI1/SPI2/TIMER1/TIMER2/I2C/UART1/ADC can only be 3K.

| Sleep mode (gray part is not working module) |           |               |  |  |  |  |  |  |

|----------------------------------------------|-----------|---------------|--|--|--|--|--|--|

| RISC-V 内核                                    | GPIO      | RTC           |  |  |  |  |  |  |

| FLASH/NVM                                    | SPI1/SPI2 | TIMER1/TIMER2 |  |  |  |  |  |  |

| RAM                                          | 12C       | WUP           |  |  |  |  |  |  |

| DATA_ALWAYS                                  | UART1     | WDT           |  |  |  |  |  |  |

| RCOSC                                        | LV        | COMP          |  |  |  |  |  |  |

| OSC                                          | RANDGEN   | ADC           |  |  |  |  |  |  |

| 3K                                           | UART2/3/4 | cJTAG         |  |  |  |  |  |  |

## 3.1.5 Power-down mode1(PD1)

After entering power-down mode 1, the MCU core stops working, the high-speed clock turns off, and the FLASH enters Deep Sleep. The power consumption of the MCU is further reduced. Arbitrary interrupts, watchdogs and resets allow the MCU to exit power-down mode 1.

Before entering the power-down mode 1, the clock source of MCU must be set to 16MHz or below, and the external clock must be closed (per\_en= 0).

After exiting power-down mode1(PD1), the user can configure the clock as needed.

| power-down mode1 (gray part is not working module) |           |               |  |  |  |  |  |  |  |  |

|----------------------------------------------------|-----------|---------------|--|--|--|--|--|--|--|--|

| RISC-V 内核 GPIO RTC                                 |           |               |  |  |  |  |  |  |  |  |

| FLASH/NVM                                          | SPI1/SPI2 | TIMER1/TIMER2 |  |  |  |  |  |  |  |  |

| RAM                                                | I2C       | WUP           |  |  |  |  |  |  |  |  |

| DATA_ALWAYS UART WDT                               |           |               |  |  |  |  |  |  |  |  |

| RCOSC | LV      | COMP  |

|-------|---------|-------|

| OSC   | RANDGEN | ADC   |

| 3K    |         | cJTAG |

## 3.1.6 Power-down mode2(PD2)

After entering Power Down Mode 2, the MCU core stops working, the high-speed clock and digital power supply are turned off, the FLASH enters Deep sleep, RAM and Registers data are lost, and the GPIOs are locked. This mode's power consumption is minimum.

Arbitrarily enabled interrupts, watchdogs, and resets can cause the MCU to exit Power Down Mode 2 and reset. After at least 160us, the user program starts to run again. After exiting from power-down mode 2, lprst\_flag is set to 1.

| Power-down mode2 (gray part is not working module) |           |               |  |  |  |  |  |  |

|----------------------------------------------------|-----------|---------------|--|--|--|--|--|--|

| RISC-V 内核                                          | GPIO      | RTC           |  |  |  |  |  |  |

| FLASH/NVM                                          | SPI1/SPI2 | TIMER1/TIMER2 |  |  |  |  |  |  |

| RAM                                                | I2C       | WUP           |  |  |  |  |  |  |

| DATA_ALWAYS                                        | UART      | WDT           |  |  |  |  |  |  |

| RCOSC                                              | LV        | COMP          |  |  |  |  |  |  |

| OSC                                                | RANDGEN   | ADC           |  |  |  |  |  |  |

| 3K                                                 |           | cJTAG         |  |  |  |  |  |  |

R

# 3.2 Low power registers

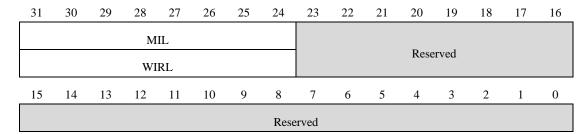

## 3.2.1 LPMODE register (LPMODE)

Address: 0x3000\_0600

Reset value:0x0000\_0000

| 31   | 30      | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17  | 16  |

|------|---------|----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|

| Rese | rved    |    |    |    |    |    |    |    |    |    |    |    |    |     |     |

| 15   | 14      | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1   | 0   |

| Rese | any a d |    |    |    |    |    |    |    |    |    |    |    |    | Lpm | ode |

| Kese | ived    |    |    |    |    |    |    |    |    |    |    |    |    | RW  |     |

| Bit  | Marking  | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:2 | Reserved | Reserved bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1:0  | lpmode   | <ul> <li>2'b00: standby mode; 2'b01: sleep mode;</li> <li>2'b10: power-down mode1; 2'b11: power-down mode 2.</li> <li>Note:</li> <li>1) The lpmode register also contains a set of mirror registers. When the chip receives a disturbance that causes the values of the registers and the mirror registers to be inconsistent, the chip resets and re-executes;</li> <li>2) Before entering the power-down mode 1, the clock source of MCU must be set to 16MHz or below, and the external clock must be closed (per_en= 0)</li> </ul> |

## 3.2.2 LPMODE flag register (LPRST\_FLAG)

Address: 0x3000\_0604

| 31 | 30 | 29 | 28 | 21 | 26 | 25 | 24 | 23      | 22 | 21 | 20 | 19 | 18 | 1 / | 16 | _ |

|----|----|----|----|----|----|----|----|---------|----|----|----|----|----|-----|----|---|

|    |    |    |    |    |    |    | ī  | Recerve | h  |    |    |    |    |     |    |   |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8      | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0          |

|----|----|----|----|----|----|----|--------|---|---|---|---|---|---|---|------------|

|    |    |    |    |    |    | D. |        | 1 |   |   |   |   |   |   | lprst_flag |

|    |    |    |    |    |    | K  | eserve | 1 |   |   |   |   |   |   |            |

| Bits | Marking    | Functional description                                              |

|------|------------|---------------------------------------------------------------------|

| 31:1 | Reserved   | Reserved bit                                                        |

|      |            | The flag of the chip is woken up from power-down mode 2 and resets. |

| 0    | lprst_flag | 1: Reset is generated by wake-up from power-down mode 2;            |

|      |            | 0: Reset generated by other means                                   |

## 4 Reset and Clock Control

## 4.1 Reset

Most registers will be reset to the reset value when the reset occurs.

When any of the following events occurs, a system reset is generated:

- 1. NRST low level (external reset);

- 2. Independent watchdog counting overflow (IWDG reset);

- 3. Software reset (SRST);

- 4. Power on reset;

- 5. Reset is generated by wake-up from power-down mode 2.

# 4.2 Software reset register (SRST)

Address: 0x3000\_0360

| 31 | 30 | 29 | 28 | 21 | 26 | 25 | 24 | 23      | 22 | 21 | 20 | 19 | 18 | 1 / | 16 |  |

|----|----|----|----|----|----|----|----|---------|----|----|----|----|----|-----|----|--|

|    |    |    |    |    |    |    | I  | Reserve | ed |    |    |    |    |     |    |  |

|    |    |    |    |    |    |    |    |         |    |    |    |    |    |     |    |  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7       | 6  | 5  | 4  | 3  | 2  | 1   | 0  |  |

|  | <br> | <br>• • |   | Ü       | •  | Ü | • | _ | - | · ·  |

|--|------|---------|---|---------|----|---|---|---|---|------|

|  |      |         | т |         | .1 |   |   |   |   | srst |

|  |      |         | K | Reserve | ea |   |   |   |   | RW   |

| Bit  | Marking  | Functional description              |

|------|----------|-------------------------------------|

| 31:1 | Reserved | Reserved bit                        |

| 0    | srst     | Write 1 to soft reset, system reset |

## 4.3 Clock

- Automatically filter the clock jitter when the crystal vibrates;

- The clock source of Peripheral clock and MCU clock can be configured independently;

- The frequency division ratios of Peripheral clock and MCU clock can be configured independently, reducing the power consumption of the system working frequency;

- The built-in frequency divider supports 1:1 ~ 1:31, duty ratio of 50%.

- Supports no burr clock switching.

#### 4.3.1 Functional introduction

#### 4.3.1.1 Clock architecture

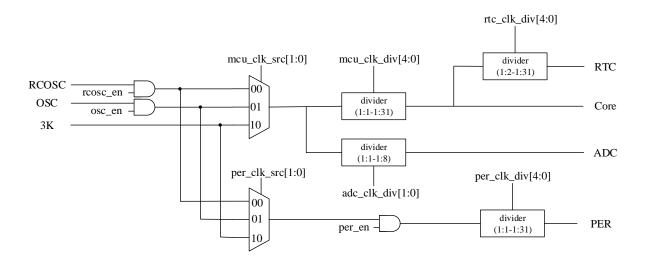

Figure 4-1 clock architecture

There are three clock sources in the clock module, which are internal high speed oscillator (RCOSC), external crystal (OSC) and internal low speed clock (3K). Each clock frequency divider supports 1:1~1:31, and supports separate use of osc and rcosc clock sources to reduce power consumption. Each module's clock input supports selecting any clock source.

## 4.3.1.2 Independent watchdog (IWDG) clock

The clock source of internal Independent watchdog is 3K clock, which works which cannot be disabled. Once the door dog is opened, it cannot be shut down unless it is reset. The chip supports the restart of the IWDG, which is configured in the FLASH download program.

#### 4.3.1.3 Control of clock module

- After the reset, RCOSC is selected as the current system clock by default;

- When a peripheral or MCU selects a clock source, the selected clock source cannot be disabled;

- Before switching the clock source, confirm whether the clock source to be switched is stable, otherwise you cannot complete the switch;

- The clock frequency of RTC should be less than 1/2 that of the MCU clock frequency.

Note: The mcu\_clk\_src is forbidden to be set to 01 when not using external OSC as the MCU clock source.

# 4.4 Clock control register

Base address: 0x3000\_02E4.

## 4.4.1 Peripheral clock enable contolr register (CMU\_PER\_EN)

Offset address:0x00

Reset value:0x0000\_0001

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24      | 23    | 22 | 21 | 20 | 19 | 18 | 17 | 16     |

|----|----|----|----|----|----|----|---------|-------|----|----|----|----|----|----|--------|

|    |    |    |    |    |    |    | Res     | erved |    |    |    |    |    |    |        |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8       | 7     | 6  | 5  | 4  | 3  | 2  | 1  | 0      |

|    |    |    |    |    |    | n  |         | 1     |    |    |    |    |    |    | per_en |

|    |    |    |    |    |    | K  | eservec | 1     |    |    |    |    |    |    | RW     |

| Bit  | Marking  | Functional description                                                              |

|------|----------|-------------------------------------------------------------------------------------|

| 31:1 | Reserved | Reserved bit                                                                        |

| 0    | per_en   | Peripheral clock enable bit, 0: disable peripheral clock 1: enable peripheral clock |

## 4.4.2 Clock source selection (CMU\_CLK\_SEL)

Offset address:0x04

| 31 | 30 | 29 | 28 | 27 | 26    | 25  | 24   | 23    | 22 | 21 | 20 | 19     | 18    | 17    | 16      |

|----|----|----|----|----|-------|-----|------|-------|----|----|----|--------|-------|-------|---------|

|    |    |    |    |    |       |     | Rese | erved |    |    |    |        |       |       |         |

| 15 | 14 | 13 | 12 | 11 | 10    | 9   | 8    | 7     | 6  | 5  | 4  | 3      | 2     | 1     | 0       |

|    |    |    |    |    | D     |     |      |       |    |    |    | per_cl | k_src | mcu_c | elk_src |

|    |    |    |    |    | Reser | vea |      |       |    |    |    | R      | W     | R     | W       |

| Bit  | Marking     | Functional description                                                            |

|------|-------------|-----------------------------------------------------------------------------------|

| 31:4 | Reserved    | Reserved bit                                                                      |

| 3:2  | per_clk_src | Peripheral clock selection:  00: clock from internal high-speed oscillator RCOSC; |

| 3.2  | per_erk_sre | 01: Clock from external high-speed crystal OSC                                    |

|     |             | 10: Clock from internal low-speed clock 3K                                      |

|-----|-------------|---------------------------------------------------------------------------------|

|     |             | 11: -                                                                           |

|     |             | MCU clock source selection:                                                     |

|     |             | 00: clock from internal high-speed oscillator RCOSC;                            |

|     |             | 01: Clock from external high-speed crystal OSC                                  |

| 1:0 | mcu_clk_src | 10: Clock from internal low-speed clock 3K                                      |

|     |             | 11: -                                                                           |

|     |             | Note: Setting mcu_clk_src to 01b is prohibited when external high-speed crystal |

|     |             | OSC is not selected as the clock source of MCU.                                 |

# 4.4.3 Clock frequency prescaler register (CMU\_CLK\_DIV)

Offset address:0x08

| 31       | 30                      | 29 | 28 | 27 | 26 | 25          | 24 | 23 | 22 | 21 | 20          | 19 | 18 | 17 | 16 |

|----------|-------------------------|----|----|----|----|-------------|----|----|----|----|-------------|----|----|----|----|

|          | Reserved                |    |    |    |    |             |    |    |    |    |             |    |    |    |    |

| 15       | 14                      | 13 | 12 | 11 | 10 | 9           | 8  | 7  | 6  | 5  | 4           | 3  | 2  | 1  | 0  |

| Dagamyad | Reserved rtc_clk_div RW |    |    |    |    | per_clk_div |    |    |    |    | mcu_clk_div |    |    |    |    |

| Reserved |                         |    |    |    | RW |             |    |    |    |    |             | RW |    |    |    |

| Bit   | Marking     | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 31:15 | Reserved    | Reserved bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 14:10 | rtc_clk_div | RTC prescaler:  0000x: RTC clock is divided by 2; 0001x: RTC clock is divided by 2;  0010x: RTC clock is divided by 4; 0011x: RTC clock is divided by 6;  0100x: RTC clock is divided by 8; 0101x: RTC clock is divided by 10;  0110x: RTC clock is divided by 12; 0111x: RTC clock is divided by 14;  1000x: RTC clock is divided by 16; 1001x: RTC clock is divided by 18;  1010x: RTC clock is divided by 20; 1011x: RTC clock is divided by 22;  1100x: RTC clock is divided by 24; 1101x: RTC clock is divided by 26;  1110x: RTC clock is divided by 28; 1111x: RTC clock is divided by 30.  Note: x is 0 or 1. |  |  |  |  |  |  |

| 9:5   | per_clk_div | Peripheral prescaler:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|     | 1           |                                          |

|-----|-------------|------------------------------------------|

|     |             | 00000: peripheral clock is not divided;  |

|     |             | 00001: peripheral clock is not divided;  |

|     |             | 00010: peripheral clock is divided by 2; |

|     |             | 00011: peripheral clock is divided by 3; |

|     |             | 00100: peripheral clock is divided by 4; |

|     |             | 00101: peripheral clock is divided by 5; |

|     |             |                                          |

|     |             | 11111: peripheral clock is divided by 31 |

|     |             | MCU prescaler:                           |

|     |             | 00000: MCU clock is not divided;         |

|     |             | 00001: MCU clock is not divided;         |

|     |             | 00010: MCU clock is divided by 2;        |

| 4:0 | mcu_clk_div | 00011: MCU clock is divided by 3;        |

|     |             | 00100: MCU clock is divided by 4;        |

|     |             | 00101: MCU clock is divided by 5;        |

|     |             |                                          |

|     |             | 11111: MCU clock is divided by 31        |

# 4.4.4 Clock source enable register (CLK\_SRC\_EN)

Offset address:0x0C

| 31 | 30       | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22       | 21     | 20 | 19 | 18 | 17 | 16 |

|----|----------|----|----|----|----|----|----|----|----------|--------|----|----|----|----|----|

|    | Reserved |    |    |    |    |    |    |    |          |        |    |    |    |    |    |

| 15 | 14       | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6        | 5      | 4  | 3  | 2  | 1  | 0  |

|    | Reserved |    |    |    |    |    |    |    | rcosc_en | osc_en |    |    |    |    |    |

|    |          |    |    |    |    |    |    |    | RW       | RW     |    |    |    |    |    |

| Bit  | Marking  | Functional description                                                            |  |  |  |  |  |

|------|----------|-----------------------------------------------------------------------------------|--|--|--|--|--|

| 31:2 | Reserved | Reserved bit                                                                      |  |  |  |  |  |

|      |          | RCOSC enable                                                                      |  |  |  |  |  |

| 1    | rcosc_en | 0:RCOSC is enabled; 1: RCOSC is disabled                                          |  |  |  |  |  |

|      |          | When RCOSC is used as the internal clock input, the current clock signal input is |  |  |  |  |  |

# CSM32RV20

|   |        | not turned off even if the rcosc_en is set to 0. RCOSC is not turned off until the |  |  |  |  |  |  |

|---|--------|------------------------------------------------------------------------------------|--|--|--|--|--|--|

|   |        | internal clock is switched to another clock source.                                |  |  |  |  |  |  |

| 0 |        | crystal (OSC) enable                                                               |  |  |  |  |  |  |

| U | osc_en | 0: crystal is enabled; 1: crystal is disabled                                      |  |  |  |  |  |  |

# 4.4.5 Clock state register (CMU\_OSC\_SR)

Offset address:0x10

| 31       | 30 | 29 | 28     | 27  | 26 | 25 | 24 | 23     | 22       | 21 | 20     | 19  | 18 | 17         | 16 |  |

|----------|----|----|--------|-----|----|----|----|--------|----------|----|--------|-----|----|------------|----|--|

| Reserved |    |    |        |     |    |    |    |        |          |    |        |     |    |            |    |  |

| 15       | 14 | 13 | 12     | 11  | 10 | 9  | 8  | 7      | 6        | 5  | 4      | 3   | 2  | 1          | 0  |  |

|          |    |    |        |     |    |    |    | osc_st | rcosc_st | MC | 'U_clk | _st | pe | per_clk_st |    |  |

|          |    |    | Reserv | rea |    |    |    | R      | R        |    | R      |     |    | R          |    |  |

| Bit  | Marking     | Functional description                                                           |  |  |  |  |  |

|------|-------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| 31:8 | Reserved    | Reserved bit                                                                     |  |  |  |  |  |

|      |             | OSC clock ready flag                                                             |  |  |  |  |  |

| 7    | osc_st      | 0:OSC is not stabilized;                                                         |  |  |  |  |  |

|      |             | 1:OSC has stabilized                                                             |  |  |  |  |  |

|      |             | RCOSC clock ready flag                                                           |  |  |  |  |  |

| 6    | rcosc_st    | 0:RCOSC is not stabilized;                                                       |  |  |  |  |  |

|      |             | 1:RCOSC has stabilized                                                           |  |  |  |  |  |

|      |             | The status of Clock Source which is selected to provide the clock for MCU        |  |  |  |  |  |

| 5.2  |             | 001: RCOSC is providing the clock for MCU                                        |  |  |  |  |  |

| 5:3  | mcu_clk_st  | 010: RCOSC is providing the clock for MCU                                        |  |  |  |  |  |

|      |             | 100: 3K is providing the clock for MCU                                           |  |  |  |  |  |

|      |             | The status of Clock Source which is selected to provide the clock for peripheral |  |  |  |  |  |

| 2:0  | man alls at | 001: RCOSC is providing the clock for peripheral                                 |  |  |  |  |  |

| 2.0  | per_clk_st  | 010: RCOSC is providing the clock for peripheral                                 |  |  |  |  |  |

|      |             | 100: 3K is providing the clock for peripheral                                    |  |  |  |  |  |

## 4.4.6 RCOSC frequency select register (RCOSC\_SEL)

Address: 0x3000\_0E00 Reset value:0x0000\_0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

|    |    |    |    |    |    |   | Rese | erved |   |   |   |   |   |   |   |

|----|----|----|----|----|----|---|------|-------|---|---|---|---|---|---|---|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8    | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Reserved  | rcosc_sel |

|-----------|-----------|

| NCSCI VCU | RW        |

| Bit  | Marking   | Functional description                                   |  |  |  |  |

|------|-----------|----------------------------------------------------------|--|--|--|--|

| 31:1 | Reserved  | Reserved bit                                             |  |  |  |  |

| 0    | #0000 col | RCOSC clock frequency selection                          |  |  |  |  |

| U    | rcosc_sel | 0: RCOSC frequency is 16MHz; 1: RCOSC frequency is 32MHz |  |  |  |  |

# 4.5 CMU register mapping

CMU register list

Base address: 0x3000\_02E4

| Register    | Offset | Description                              |

|-------------|--------|------------------------------------------|

| CMU_PER_EN  | 0x00   | Peripheral Clock Enable Control Register |

| CMU_CLK_SEL | 0x04   | Clock Source Selection Register          |

| CMU_CLK_DIV | 0x08   | Clock frequency prescaler Register       |

| CLK_SRC_EN  | 0x0C   | Clock Source enable Register             |

| CMU_OSC_SR  | 0x10   | Clock State Register                     |

| RCOSC_SEL   | -      | RCOSC frequency select                   |

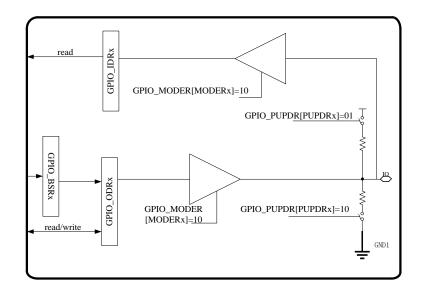

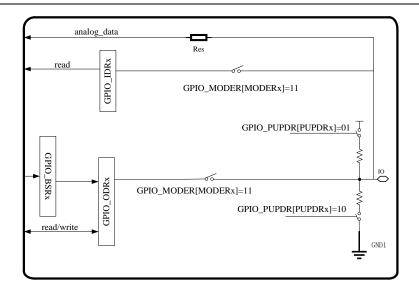

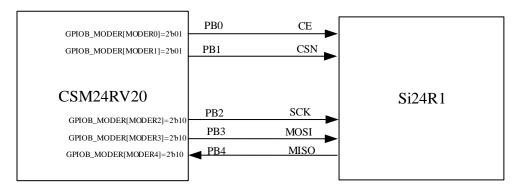

## 5 General and alternate function I/Os

GPIOs are user-configurable general-purpose IOs, and each GPIO port can be independently configured for input/output, peripheral multiplexing, or analog functions. GPIOA0~15 correspond to PA0~PA15, GPIOB0~13 correspond to PB0~PB13.

The bootloader default is PA5, PA6.

## 5.1 GPIO Functional description

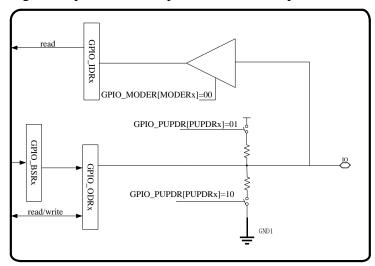

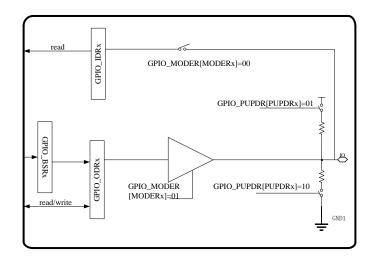

#### **5.1.1** Main function

- Output states: pull-up and pull-down functions, open-source output, opendrain output and push-pull output;

- In power-down mode 2, the I/Os will remain the state before power-down;

- The output of the GPIO can come from the ODR register of the GPIO or the peripheral function output;

- Input state: Suspended input, pull-up and pull-down input;

- The input data is stored in the IDR register of the GPIO or peripheral data input;

- Supports analog function data transfer;

- Peripheral function interface is optional;

- You can flexibly select the corresponding input port for each GPIO;

- The IO modes are selected by the GPIO\_MODER register for Input Mode,

Output Mode, Alternate function Mode, and Analog Mode;

#### **5.1.1.1** Alternate function

The external IO and internal module connection multiplexer of this chip is controlled by GPIOA\_AFRH and GPIOA\_AFRL registers. Write register GPIO\_MODER[MODERx] = 2'b10 configures GPIOx to multiplexing function, which can flexibly map the internal module ports to the PAD.

Each IO has a splitter to connect the multiplexed functions, and the GPIO\_AFRL and GPIO\_AFRH registers control which function is multiplexed to, see Table 5-1 for multiplexing details.

After reset, the multiplexing controller will connect the PAD to the AF0 function

by default. UART1 supports ISP.

## Table 5-1 GPIO alternate function table

| Pin Name | AF0             | AF0_DIR | AF1             | AF1_DIR | AF2             | AF2_DIR | AF3          | AF3_DIR |

|----------|-----------------|---------|-----------------|---------|-----------------|---------|--------------|---------|

| PA0      | TCKC            | I       | SCL             | Ю       | TIMER1_<br>CH1  | Ю       |              |         |

| PA1      | TMSC            | Ю       | SDA             | Ю       | TIMER1_<br>CH1N | 0       |              |         |

| PA2      | SPI1<br>_SCK    | О       | TIMER1_<br>CH1  | О       | TIMER1_<br>CH2  | Ю       |              |         |

| PA3      | SPI1_<br>MISO   | I       | TIMER1_<br>CH1N | О       | TIMER1_<br>CH2N | О       | UART2<br>_RX | Ю       |

| PA4      | SPI1_<br>MOSI   | О       | TIMER1_<br>CH1N | О       | TIMER1_<br>CH3  | Ю       | UART2<br>_TX | О       |

| PA5      | UART1_<br>RX    | I       | SPI1_<br>SCK    | О       | TIMER1_<br>CH3N | О       |              |         |

| PA6      | UART1_<br>TX    | О       | SPI1_<br>MISO   | I       | TIMER1_<br>CH4  | IO      |              |         |

| PA7      | SCL             | Ю       | SPI1_<br>MOSI   | О       | TIMER1_<br>CH4N | О       |              |         |

| PA8      | SDA             | Ю       | UART1_<br>RX    | Ю       | TIMER2_<br>CH1  | О       |              |         |

| PA9      | TIMER1_<br>CH1  | О       | UART1_<br>TX    | О       | TIMER2<br>_CH1N | О       |              |         |

| PA10     | TIMER1_<br>BKIN | I       |                 | О       | TIMER2_<br>CH2  | О       | UART3<br>_RX | Ю       |

| PA11     | TIMER2_<br>BKIN | I       |                 | О       | TIMER2_<br>CH2N | О       | UART3<br>_TX | О       |

| PA12     | -               | -       |                 | О       | TIMER2_<br>CH3  | О       |              |         |

| PA13     | -               | -       |                 |         | TIMER2_<br>CH3N | О       |              |         |

| PA14     | ADC_<br>TRI     |         |                 |         | TIMER2_<br>CH4  | IO      | UART4<br>_RX | Ю       |

| Pin Name | AF0           | AF0_DIR | AF1 | AF1_DIR | AF2             | AF2_DIR | AF3          | AF3_DIR |

|----------|---------------|---------|-----|---------|-----------------|---------|--------------|---------|

| PA15     |               |         |     |         | TIMER2_<br>CH4N | O       | UART4<br>_TX | О       |

| PB0      | -             | -       | -   | -       | -               | -       | -            | -       |

| PB1      | -             | -       | -   | -       | -               | -       | -            | -       |

| PB2      | SPI2_<br>SCK  | О       | -   | -       | -               | -       | -            | -       |

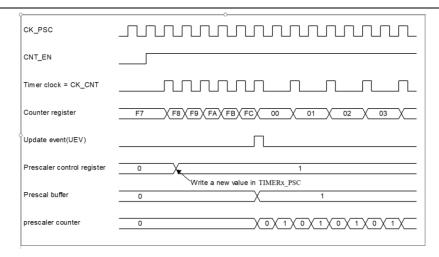

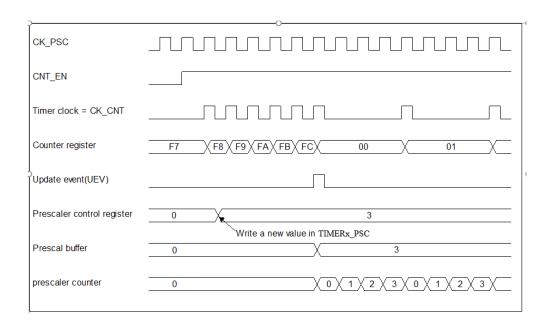

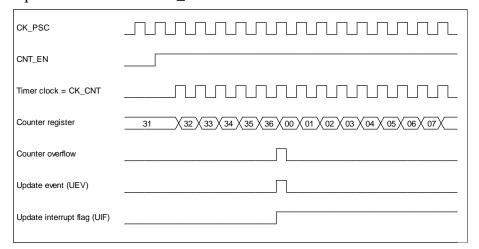

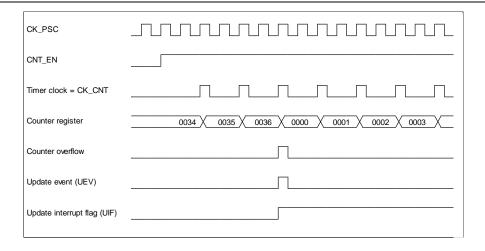

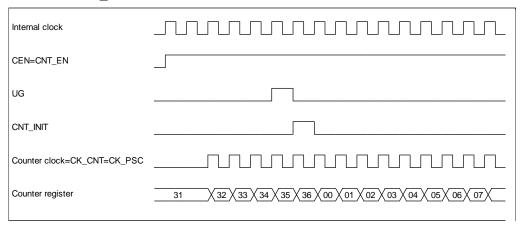

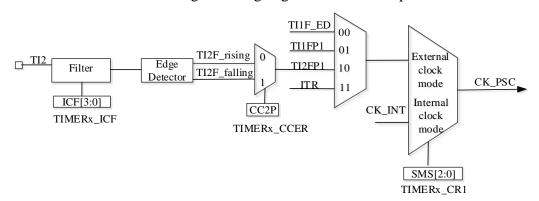

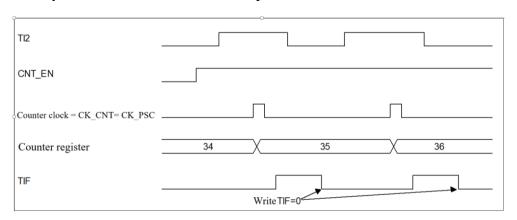

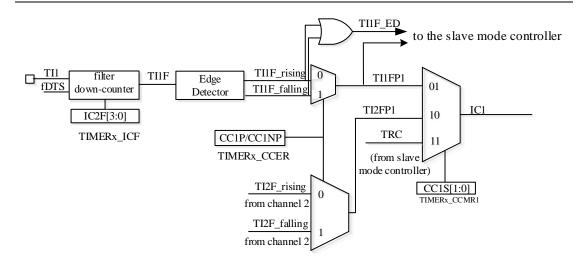

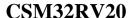

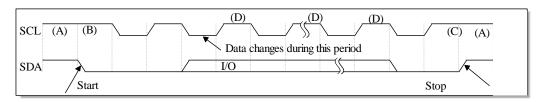

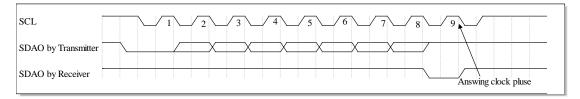

| PB3      | SPI2_<br>MOSI | О       | -   | -       | -               | -       | -            | -       |