### 产品特性

低功耗、单通道、16 位 DAC 积分非线性误差 INL <±1LSB 微分非线性误差 DNL<±1LSB 轨到轨工作 4.5 V 至 5.5 V 电源供电 上电复位至零电平或中间电平 硬件LDAC和软件LDAC覆盖功能 14 引脚 DFN 封装 内部基准电压缓冲及内部输出放大器

### 应用

伺服系统 数据采集系统 便携式电池供电仪表 数字增益和失调电压调整 可编程电压源和电流源 可编程衰减器

# 产品聚焦

统一的 5V 电源电压 完全正向设计 引脚兼容 ZYA5064 及 ADI 公司 AD5064-1 功能兼容 ADI 公司 AD5061

# 概述

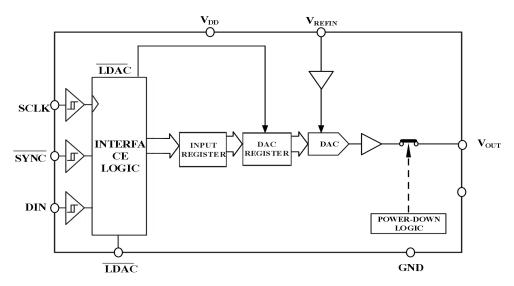

ZYA5061T 是低功耗、单通道、16 位缓冲电压输出数模转换器,提供 1 LSB INL 和 1 LSB DNL 的相对精度,其中 ZYA5061T 具有独立参考引脚。 ZYA5061T 可以采用 4.5 V 至 5.5 V 单电源供电,并提供土1 LSB 的微分精度特性。这些器件采用多功能三线式、低功耗、施密特触发器串行接口,能够以最高 50 MHz 的时钟速率工作,并与标准 SPI、QSPI、MICROWIRE 和 DSP 接口标准兼容。片内提供集成基准电压缓冲器和输出放大器。内置一个上电复位电路,确保 DAC 输出上电至零电平或中量程,并保持该电平,直到对该器件执行一次有效的写操作为止。器件的总非调整误差小于 2 mV。

图 1 功能框图

# 修订历史

| 版本   | 时间         | 修订内容   | 位置  |

|------|------------|--------|-----|

| V1.0 | 2022/11/14 | 手册初稿   |     |

| V1.1 | 2023/3/22  | 增加上电要求 | P16 |

|      |            |        |     |

|      |            |        |     |

|      |            |        |     |

|      |            |        |     |

# 目录

| 产品特性      | 1  |

|-----------|----|

| 应用        | 1  |

| 产品聚焦      | 1  |

| 概述        | 1  |

| 修订历史      | 2  |

| 技术规格      |    |

| 交流规格      | 5  |

| 时序特性      | 7  |

| 绝对最大额定值   | 8  |

| ESD 警告:   | 8  |

| 引脚配置和功能描述 | 9  |

| 典型性能参数    | 10 |

| 术语        | 12 |

| 工作原理      | 13 |

| DAC 架构  | 13 |

|---------|----|

| 基准电压缓冲  | 13 |

| 输出放大器   | 13 |

| 串行接口    | 14 |

| 输入移位寄存器 | 14 |

| 上电复位    | 16 |

| 功能      | 16 |

| 电源旁路和接地 | 17 |

| 应用信息    | 18 |

| 选择基准电压源 | 18 |

| 双极性工作模式 | 18 |

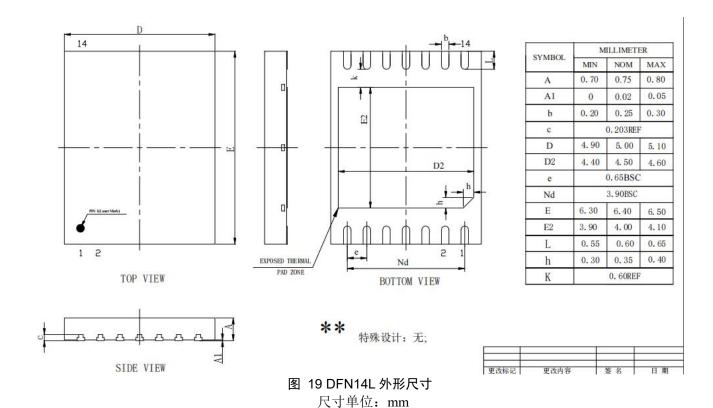

| 外形尺寸    | 20 |

| 江防华志    | 20 |

# 16bit、低功耗、单通道 DAC ZYA5061T

$V_{DD}$  = 4.5V 至5.5V,  $R_L$  = 5  $k\Omega$  至GND,  $C_L$  = 200pF 至GND, 2.5V ≤  $V_{REFIN}$  ≤  $V_{DD}$ , 除非另有说明,所有规格均相对于  $T_{MIN}$  至  $T_{MAX}$  而言。

#### 表 1

| 参数                    | 最小值 | 典型值       | 最大值             | 单位    | 测试条件/注释                                                                                   |

|-----------------------|-----|-----------|-----------------|-------|-------------------------------------------------------------------------------------------|

| 静态性能 <sup>2</sup>     | •   | •         | •               |       |                                                                                           |

| 分辨率                   | 16  |           |                 | Bits  |                                                                                           |

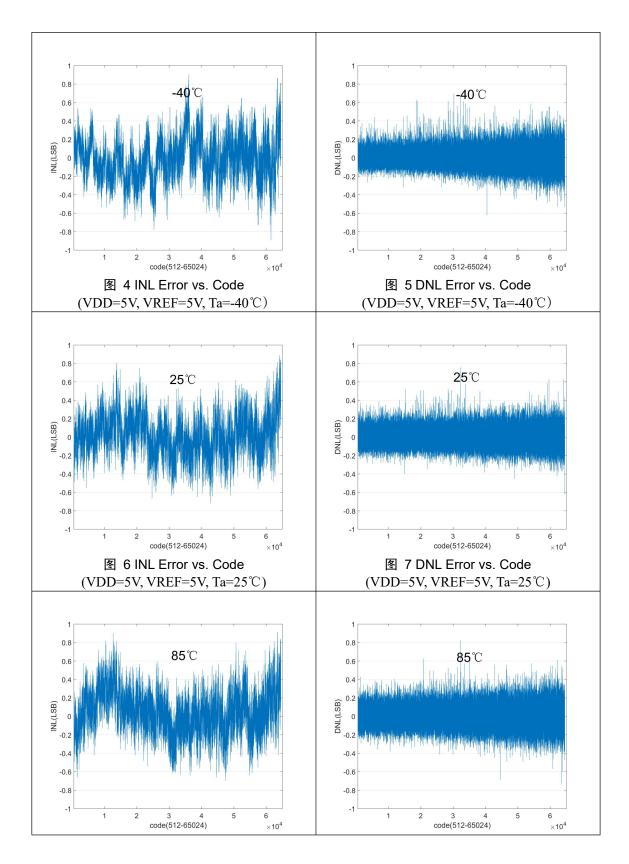

| 相对精度 INL              |     | $\pm 0.6$ | ±1              | LSB   | $T_A=-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$                                        |

| 微分非线性 DNL             |     | $\pm 0.5$ | ±1              | LSB   | T <sub>A</sub> =-40°C to +85°C                                                            |

| 总不可调整误差 TUE           |     |           | ±2              | mV    | $V_{DD} = 5 \text{ V}, V_{REF} = 5 \text{ V}$                                             |

| 直流失调误差                |     |           | ±1.8            | mV    |                                                                                           |

| 直流失调误差温度系数。           |     | ±2        |                 | μV/°C |                                                                                           |

| 满量程误差                 |     | ±0.01     | $\pm 0.07$      | % FSR | DAC 寄存器载入全 1                                                                              |

| 增益误差                  |     | ±0.005    | $\pm 0.05$      | % FSR |                                                                                           |

| 增益误差温度系数 <sup>3</sup> |     | ±1        |                 | ppm   | FSR/° C                                                                                   |

| 输出特性 <sup>3</sup>     |     |           |                 |       |                                                                                           |

| 输出电压范围                | 0   |           | V <sub>DD</sub> | V     |                                                                                           |

| 容性负载稳定性               |     |           | 0.5             | nF    | $R_L=5k \Omega$ , $R_L=100k \Omega$ , $RL=\infty$                                         |

| 直流输出阻抗(正常模<br>式)      |     | 0.5       |                 | Ω     | 输出阻抗容限为 ±10%                                                                              |

| 直流输出阻抗(省电模式)          |     |           |                 |       |                                                                                           |

|                       |     | 100       |                 | kΩ    | 输出阻抗容限为±20KΩ                                                                              |

| 输出与 1KΩ网络连接           |     | 1         |                 | kΩ    | 输出阻抗容限为±400Ω                                                                              |

| 短路电流                  |     | 60        |                 | mA    | DAC 满量程,输出接 GND                                                                           |

|                       |     | 45        |                 | mA    | DAC 零量程,输出接 V <sub>DD</sub>                                                               |

| 上电时间                  |     | 10        |                 | ms    |                                                                                           |

| 直流电源抑制比               |     | -100      |                 | dB    | V <sub>DD</sub> ±10%, DAC 编码=满量程                                                          |

| 基准输入                  |     |           |                 |       |                                                                                           |

| 基准电压输入范围              | 2.5 |           | $V_{DD}$        | V     |                                                                                           |

| 基准电流                  |     | 140       |                 | μA    |                                                                                           |

| 基准输入阻抗                |     | 32        |                 | ΚΩ    |                                                                                           |

| 逻辑输入3                 |     |           |                 |       |                                                                                           |

| 输入电流                  |     |           | ±1              | μΑ    |                                                                                           |

| 低输入电压                 |     |           | 0.8             | V     |                                                                                           |

| 高输入电压                 | 2.2 |           |                 | V     |                                                                                           |

| 引脚电容                  |     | 4         |                 | pF    |                                                                                           |

| 电源要求                  | i   | 1         | 1               |       |                                                                                           |

| $ m V_{DD}$           | 4.5 |           | 5. 5            | V     | 所有数字输入为 0 V 或 VDD DAC工作中不包括负载电流 V <sub>II</sub> = V <sub>DD</sub> 及 V <sub>IL</sub> = GND |

# 16bit、低功耗、单通道 DAC ZYA5061T

| lod    |   |   |    |  |

|--------|---|---|----|--|

| 正常模式 4 | 6 | 8 | mA |  |

- ¹温度范围-40℃~85℃,正常值25℃。

- <sup>2</sup>线性度计算的码字区间: 512~65024; 输出无负载。

- <sup>3</sup>设计保证。

- <sup>4</sup>接口不工作。所有 DAC 开启,输出无负载。

- <sup>5</sup>所有 DAC 进入掉电模式。

# 16bit、低功耗、单通道 DAC ZYA5061T

$V_{DD}$  = 4.5V 至5.5V,  $R_L$  = 5  $k\Omega$  至GND,  $C_L$  = 200pF 至GND, 2.5V ≤  $V_{REFIN}$  ≤  $V_{DD}$ , 除非另有说明,所有规格均相对于  $T_{MIN}$  至  $T_{MAX}$  而言。

#### 表 2

| 参数       | 最小值 | 典型值  | 最大值 | 单位     | 测试条件/注释                                               |

|----------|-----|------|-----|--------|-------------------------------------------------------|

| 动态性能     |     |      |     |        |                                                       |

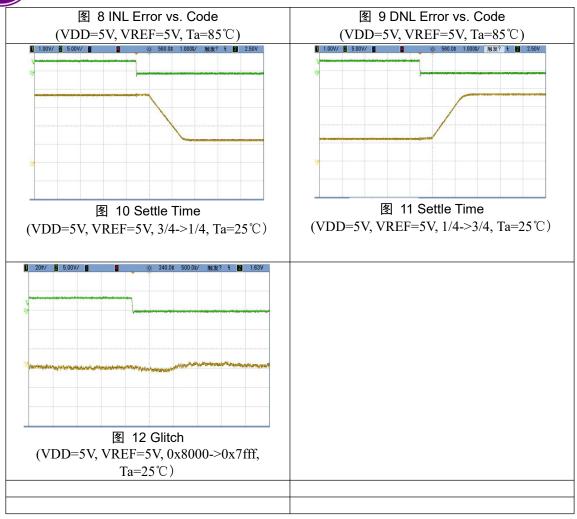

| 输出电压建立时间 |     | 5.8  | 8   | μs     | 单通道 1/4 到 3/4 量程稳定在<br>±2LSB, 输出无负载                   |

| 压摆率      |     | 1.7  |     | V/µs   |                                                       |

| 数模转换毛刺脉冲 |     | 3    |     | nV-sec | 主进位 1 LSB 变化                                          |

| 基准馈通     |     | -70  |     | dB     | V <sub>REF</sub> =3V±0.86Vp-p,频率范围<br>100Hz to 100KHz |

| 数字馈通     |     | 0.02 |     | nV-sec |                                                       |

| 数字串扰     |     | 1. 7 |     | nV-sec |                                                       |

| 模拟串扰     |     | 3. 7 |     | nV-sec |                                                       |

| AC 串扰    |     | 6    |     | nV-sec |                                                       |

| 3dB 带宽   |     | 340  |     | kHz    |                                                       |

| 总谐波失真    |     | -83  |     | dB     | $V_{REF}=3V\pm0.2Vp-p$ , 10 kHz                       |

| 输出噪声谱密度  |     | 64   |     | nV/√Hz | DAC code = $0x8000$ , 1 kHz                           |

|          |     | 60   |     | nV/√Hz | DAC code = 0x8000, 10 kHz                             |

| 输出噪声     |     | 6    |     | uVp-p  | 0.1Hz 到 10Hz                                          |

# 16bit、低功耗、单通道 DAC ZYA5061T

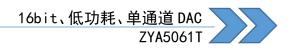

# 时序特性

所有输入信号都指定为  $t_R = t_F = 1$  ns/V ( $V_{DD}$  的 10% - 90%),并从电压水平( $V_{IL} + V_{IH}$ )/2 计时, $V_{DD} = 4.5$  V - 5.5V, 所有规格均相对于 T<sub>MIN</sub> - T<sub>MAX</sub>, 除非另有说明。

| 参数  | 描述                    | Min | Тур | Max | 单位 |

|-----|-----------------------|-----|-----|-----|----|

| t1  | SCLK 周期时间             | 20  | -71 |     | ns |

| t2  | SCLK 高电平时间            | 10  |     |     | ns |

| t3  | SCLK 低电平时间            | 10  |     |     | ns |

| t4  | SYNC下降沿到 SCLK 下降沿建立时间 | 17  |     |     | ns |

| t5  | 数据建立时间                | 5   |     |     | ns |

| t6  | 数据保持时间                | 5   |     |     | ns |

| t7  | SCLK 下降沿到SYNC上升沿时间    | 5   |     | 30  | ns |

| t8  | SYNC最小高电平时间           |     |     |     |    |

|     | 单个通道更新                | 3   |     |     | μs |

| t9  | SYNC上升沿到 SCLK 下降沿忽略   | 17  |     |     | ns |

| t10 | LDAC 低电平脉冲宽           | 20  |     |     | ns |

| t11 | SCLK 下降沿到LDAC上升沿      | 20  |     |     | ns |

| t12 | SCLK 下降沿到LDAC下降沿      | 10  |     |     | ns |

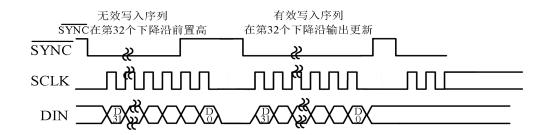

图 2 连续写操作

# 绝对最大额定值

除非另有说明, T<sub>A</sub>=25℃。

#### 表 4

| x 4                    |                                   |  |  |

|------------------------|-----------------------------------|--|--|

| 参数                     | 额定值                               |  |  |

| V <sub>DD</sub> 至 GND  | -0.3 V to +7 V                    |  |  |

| 数字输入电压至                | -0.3 V to V <sub>DD</sub> + 0.3 V |  |  |

| GND                    |                                   |  |  |

| V <sub>OUT</sub> 至GND  | -0.3 V to V <sub>DD</sub> + 0.3 V |  |  |

| V <sub>REF</sub> 至 GND | -0.3 V to V <sub>DD</sub> + 0.3 V |  |  |

| 工作温度范围                 |                                   |  |  |

| 工业级                    | -40°C to +85°C                    |  |  |

| 存储温度范围                 | -65°C to +150°C                   |  |  |

| 最高结温                   | +150°C                            |  |  |

| DFN 封装                 |                                   |  |  |

| θ <sub>JA</sub> 热阻     | (待测) °C/W                         |  |  |

| 回流焊峰值温度                |                                   |  |  |

| SnPb                   | 240°C                             |  |  |

| Pb-Free                | 260°C                             |  |  |

注意,超出上述绝对最大额定值可能会导致器件永久性损坏。这只是额定最值,不表示在这些条件下或者在任何其它超出本技术规范操作章节中所示规格的条件下,器件能够正常工作。长期在绝对最大额定值条件下工作会影响器件的可靠性。

## ESD 警告:

ESD(静电放电)敏感器件。

带电器件和电路板可能会在没有察觉的情况下放电。尽管本产品具有专利或专有保护电路,但在遇到高能量 ESD 时,器件可能会损坏。因此,应当采取适当的 ESD 防范措施,以避免器件性能下降或功能丧失。

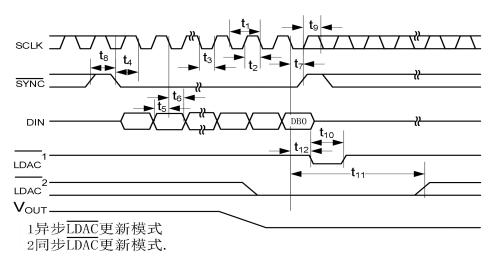

# 引脚配置和功能描述

图 3 ZYA5061T

#### 表 5 14 引脚 DFN 封装引脚功能描述

| 引脚编号 | JFN 到表引脚以<br>引脚名称 | 描述                                                                            |  |  |  |  |

|------|-------------------|-------------------------------------------------------------------------------|--|--|--|--|

|      |                   | VAC                                                                           |  |  |  |  |

| 1    | LDAC              | 加载 DAC 逻辑输入。这是用来更新 DAC 寄存器以及模拟输出。当一直为低 电平时,被选择的 DAC 寄存器将在第 32 个时钟的下降沿进行更新。如果在 |  |  |  |  |

|      |                   | 写周期中LDAC保持在高电平,则被选择的 DAC 输入移位寄存器会被更新,                                         |  |  |  |  |

|      |                   | 但模拟输出更新会延迟到LDAC下降沿。在这种模式下,所有模拟输出都可                                            |  |  |  |  |

|      |                   | 以同时在LDAC的下降沿上进行更新。                                                            |  |  |  |  |

| 2    | SYNC              | 低电平有效控制输入。这是输入数据的帧同步信号。当SYNC变低时,它启动 SCLK 和 DIN 缓冲,并启用移位寄存器。数据在接下来的第 32 个下降沿   |  |  |  |  |

|      |                   | 被传入。如果SYNC在第32个下降沿之前被抬高,SYNC的上升沿作为一个中断,写入序列会被忽略。                              |  |  |  |  |

| 3    | $V_{DD}$          | 电源输入引脚。ZYA5061T 可以采用 4.5V~5.5V 电源供电,电源应通过并联 的 10uF 电容和 0.1uF 电容去耦至 GND。       |  |  |  |  |

| 4    | NC                | 保留功能,要求悬空                                                                     |  |  |  |  |

| 5    |                   | 77 77 77 77 7 7 7 7 7 7 7 7 7 7 7 7 7 7                                       |  |  |  |  |

|      | V <sub>OUT</sub>  | DAC 的模拟输出电压                                                                   |  |  |  |  |

| 6    | POR               | 电源重置引脚。将这个引脚接在 GND 上使 DAC 输出在电源接通时达到零刻                                        |  |  |  |  |

|      |                   | 度。将这个引脚接在 VDD 上,使 DAC 输出达到量程中央。                                               |  |  |  |  |

| 7    | $V_{REFIN}$       | 这是 DAC 的基准电压输入引脚。                                                             |  |  |  |  |

| 8    | CLR               | 保留功能,可以悬空或接高电平、低电平                                                            |  |  |  |  |

| 9    | SDO               | 保留功能,可以悬空或接高电平、低电平                                                            |  |  |  |  |

| 10   | NC                | 保留功能,要求悬空                                                                     |  |  |  |  |

| 11   | NC                | 保留功能,要求悬空                                                                     |  |  |  |  |

| 12   | GND               | 器件上所有电路的接地基准点。                                                                |  |  |  |  |

| 13   | DIN               | 串行数据输入。器件有一个32位输入移位寄存器。数据在串行时钟输入的                                             |  |  |  |  |

|      |                   | 下降沿读入寄存器。                                                                     |  |  |  |  |

| 14   | SCLK              | 串行时钟输入。数据在 SCLK 的下降沿逐个输入移位寄存器。工作时钟速率                                          |  |  |  |  |

|      |                   | 最高达 50 MHz。                                                                   |  |  |  |  |

#### 相对精度或积分非线性(INL)

对于 DAC,相对精度或积分非线性是指 DAC 输出与通过 DAC 传递函数的两个端点的直线之间的最大偏差,单位为 LSB。

#### 差分非线性(DNL)

微分非线性是指任意两个相邻编码之间所测得变化值与理想的 1 LSB 变化值之间的差异。最大±1 LSB 的额定差分非线性可确保单调性。

#### 零代码误差

零代码误差衡量将零电平码 (0x0000) 载入 DAC 寄存器时的输出误差。理想情况下,输出应为 0 V。在ZYA5061T中,零代码误差始终为正值,因为 DAC 输出不能低于 0 V。零代码误差用 mV 表示。

#### 零代码误差温度系数

零编码误差漂移衡量零编码误差随温度的变化,用 V/°C表示。

#### 增益误差

增益误差是衡量 DAC 量程误差的指标,是指 DAC 传递 特性的斜率与理想值之间的偏差,用% FSR 表示。

#### 增益误差温度系数

增益温度系数衡量增益误差随温度的变化,用 ppm FSR/° C表示。

#### 满量程误差

满量程误差衡量将满量程代码 (0xFFFF) 载入 DAC 寄存器时的输出误差。理想情况下,输出应为  $V_{DD} - 1$  LSB。满量程误差用满量程范围的百分比 (%FSR) 表示。

#### 数模转换毛刺脉冲

数模转换毛刺脉冲是 DAC 寄存器中的输入代码变化时注入到模拟输出的脉冲。在数字输入代码主进位发生 1 LSB 转换(0x7FFF 到 0x8000)时测量,它一般定义为以 nV-sec 为单位的毛刺面积。

#### 直流电源抑制比(PSRR)

PSRR 表示电源电压变化对 DAC 输出的影响大小。是指 DAC 满量程输出的条件下 VOUT 变化量与 VDD 变化量之比,用 mV/V 表示。

#### 直流串扰

直流串扰是一个 DAC 输出电平因响应另一个 DAC 输出变化而发生的直流变化。其测量方法是让一个 DAC 发生满量程输出变化(或软件关断并上电),同时监控另一个保持中间电平的 DAC。单位为-V。

#### 数字馈通

数字馈通衡量从 DAC 的数字输入注入到 DAC 的模拟输出的脉冲,但在 DAC 输出未更新时进行测量。单位为 nV-sec,测量数据总线上发生满量程编码变化时的情况,即全 0 至全 1,反之亦然。

#### 基准馈通

基准馈通是指 DAC 输出未更新时的 DAC 输出端的 信号幅度与基准输入之比,用 dB 表示。

#### 数字串扰

数字串扰是指一个输出为中间电平的 DAC, 其输出 因响应另一个 DAC 的输入寄存器中满量程编码变 化(全 0 至全 1, 或相反)而引起的毛刺脉冲。该值在 独立模式下进行测量,用 nV-sec 表示。

#### DAC 间串扰

DAC 间串扰是指一个 DAC 的输出因响应另一个 DAC 的数字编码变化和后续的模拟输出变化,而引起的毛刺脉冲。其测量方法是使用写入和更新命令让一个通道发生满量程编码变化(全 0 到全 1,或相反),同时监控处于中间量程的另一个通道的输出。毛刺的能量用 nV-sec 表示。

#### 总谐波失真(THD)

总谐波失真是指理想正弦波与使用 DAC 时其衰减形式的差别。正弦波用作 DAC 的参考,而 THD 用来衡量 DAC 输出端存在的谐波。单位为 dB。

ZYA5061T 是一种 16 位、单通道、串行输入、电压输出的 DAC。集成了一个开机复位电路,以确保 DAC输出功率达到已知的输出状态。二进制编码直接输入 DAC,在外部参考电压源下,输出电压为

$$V_{OUT} = V_{REFIN} \times \frac{D}{65536}$$

其中 D 为加载到 DAC 寄存器(0 到 65535)的二进制代码的十进制表示。

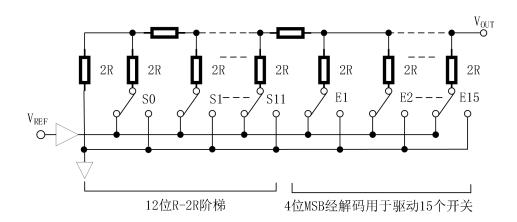

### DAC 架构

ZYA5061T 的 DAC 架构包含两个匹配的 DAC 部分。简化电路图如图所示。16 位数据字的高 4 位 MSB 经解码用于驱动 15 个开关(E1 至 E15)。每个开关都将 15 个匹配电阻中的一个与 DAC GND 或 VREF 缓冲输出相连。数据字的其余 12 位驱动 12 位电压模式 R-2R 梯形网络的 S0 至 S11 开关。

图 13 DAC 梯形结构

# 基准电压缓冲

ZYA5061T基于外部参考源运行,参考输入范围从 2.5V 到 V<sub>DD</sub>,该输入电压提供给 DAC 核心一个缓冲参考。

# 输出放大器

ZYA5061T 中配有一个能输出轨对轨电压的输出放大器,输出范围  $OV^{\sim}VDD$ 。放大器可以驱动  $5K\Omega$  电阻负载与 200pF 电容负载并联。

ZYA5061T 的 3 线串行接口(SYNC、SCLK 和 DIN)与 SPI、QSPI 和 MICROWIRE 接口标准以及大多数 DSP 兼容。

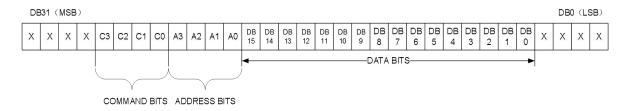

# 输入移位寄存器

输入移位寄存器(如图)为32位宽,第一个4位无需关注,第二个4位是命令位,C3到C0,然后是4位DAC地址位,A3到A0,最后是数据字位。数据字包含一个16位的输入代码,后面跟着四个无需关注位,这些数据在SCLK的第32个下降沿被传输到输入寄存器。

图 14 输入移位寄存器内容

#### 表 7 命令定义

| 命  | <b>*</b> |    |    |                     |

|----|----------|----|----|---------------------|

| C3 | C2       | C1 | C0 | 描述                  |

| 0  | 0        | 0  | 0  | 写入输入寄存器             |

| 0  | 0        | 0  | 1  | 以输入寄存器的内容更新 DAC 寄存器 |

| 0  | 0        | 1  | 0  | 保留                  |

| 0  | 0        | 1  | 1  | 写入输入寄存器并更新 DAC      |

| 0  | 1        | 0  | 0  | DAC 掉电/上电           |

| 0  | 1        | 0  | 1  | 清除码寄存器              |

| 0  | 1        | 1  | 0  | LDAC 寄存器            |

| 其  | 他        | •  | •  | 保留                  |

#### 表 8 地址命令

|    | 地址 |            |    |            |

|----|----|------------|----|------------|

| А3 | A2 | <b>A</b> 1 | A0 | 选定的 DAC 通道 |

| 0  | 0  | 1          | 0  | DAC        |

写入序列从SYNC线拉低开始,来自 DIN 线的数据在 SCLK 下降沿时被锁定在 32 位移位寄存器中。串行时钟频率可高达 50MHz,使器件兼容高速 DSP。在第 32 个时钟下降沿,最后一个数据位被锁存,写入的

命令被执行,即输入寄存器内容的改变(见表 7)或工作模式的改变。在这个阶段,SYNC线可以保持低或高。 无论哪种情况下,在下次写序列前它必须置高 3us 以上,这样下一个SYNC下降沿可以启动下一个写序列。 在写序列间需要将SYNC置高,尤其是低功耗模式下。

#### SYNC中断

在正常的写序列中,SYNC线至少在 32 个 SCLK 的下降沿期间保持为低电平,DAC 会在第 32 个下降沿更新。如果在第 32 个下降沿之前SYNC被拉高,写序列就会被中断。输入移位寄存器会复位,写序列被认为是无效的,不会造成 DAC 寄存器内容的更新和操作模式的改变。

图 15 SYNC中断功能

#### 省电模式

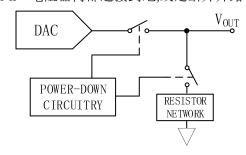

ZYA5061T 可以通过软件配置,有四种不同的工作模式:正常工作模式(默认模式)和三种单独的关机模式。命令0100 是掉电模式的保留命令,在输入移位寄存器中,掉电模式通过设置两位(DB9 和 DB8)设置。通过将相应的4位(DB3、DB2、DB1、DB0)设置为1,可以将DAC设至所选模式。

当控制寄存器中的位 DB9 和位 DB8 设置为 0 时,芯片工作在正常模式下。然而,对于这三个省电模式,如果 DAC 关闭,电源电流下降到最低功耗。不仅电源电流下降,而且输出引脚也从 DAC 的输出内部切换到一个已知值的电阻网络。这有一个优点,即当部件处于断电模式时,它的输出阻抗是已知的。有三个不同的选项:输出是通过  $1 \, \mathrm{k} \, \Omega$ 或  $100 \, \mathrm{k} \, \Omega$  电阻器内部连接到地,或是断开开路。输出阶段如图所示。

图 16 关断模式下的输出状态

#### 表 9 操作模式

| DB9 | DB8 | Operating Mode |

|-----|-----|----------------|

天津市滨海新区中新生态城中天大道 1620 号生态城科技园启发大厦 5 层 106 室

第 15 页 共 20 页

| 0 | 0 | Normal operation<br>Power-down modes |

|---|---|--------------------------------------|

| 0 | 1 | 1 kΩ to GND                          |

| 1 | 0 | 100 kΩ to GND                        |

| 1 | 1 | Three-state                          |

当所有通道掉电时,偏置发生器、DAC 核心和其他相关线性电路被关闭。但是,在关机模式下,DAC 寄存器的内容不受影响。

# 上电复位

ZYA5061T 包含一个上电初始化电路,用于在上电过程中初始化寄存器并控制输出电压。如果上电时 POR 引脚为低,DAC 输出电压为 0 V (注意: 0V 输出超出了 ZYA5061T 的线性范围);如果上电时 POR 引脚为高,输出电压为中心值,在此状态上输出电压一直保持不变,直到向 DAC 发出有效的写入指令。

上电期间当 VDD 超过 4 V 左右时,会启动上电初始化电路,接下来需要 3ms 的时间完成上电初始化。 在此期间,不应向 ZYA5061T 进行任何写入操作。

为了防止上电期间的意外操作,请在电源上电过程中控制数字输入信号(SYNC、SCLK、DIN、LDAC、CLR),建议由连接到 VDD 或 GND 的上拉电阻来控制这些信号。对于 VDD 上升时间较慢(超过 1ms)的应用,则在电源达到其最终值之后需要对 ZYA5061T 发送软复位指令。软复位指令的具体命令及使用规范,以及上电期间无法满足上述要求时的解决方案,详见 ZYA5061T FAQ。

对于不需要硬件LDAC功能的应用,LDAC引脚可以直接连接到 GND。

表 10 上电/掉电模式对应的 32 位输入寄存器的内容

| DB31<br>to<br>DB28 | DB27                          | DB26 | DB25 | DB24                                             | DB23<br>to<br>DB20 | DB10<br>to<br>DB19 | DB9             | DB8 | DB4<br>to<br>DB7                            | DB3 | DB2 | DB1 | DB0 |

|--------------------|-------------------------------|------|------|--------------------------------------------------|--------------------|--------------------|-----------------|-----|---------------------------------------------|-----|-----|-----|-----|

| Х                  | 0                             | 1    | 0    | 0                                                | Х                  | Х                  | PD1             | PD0 | Х                                           | DAC |     |     |     |

| Don't cares        | Don't Command bits (C2 to C0) |      |      | Address<br>bits (A3<br>to A0)—<br>don't<br>cares | Don't cares        | Power<br>mode      | Power-down mode |     | Power-down/power-up —set bit to 1 to select |     |     |     |     |

# LDAC功能

#### 硬件LDAC管脚

DAC 的输出可以使用硬件LDAC pin 更新,如图 2 所示。硬件LDAC引脚有两种使用方法:同步(LDAC持续低)和异步(LDAC脉冲)。

同步LDAC: LDAC保持低。在保持LDAC低的条件下,新数据读取后,在第 32 次 SCLK 脉冲下降沿上更新 DAC 寄存器。

异步LDAC: LDAC保持高,然后当一个低脉冲来临时更新 DAC。在写入输入寄存器的同时不更新输出。当 LDAC脉冲低时,DAC 寄存器将更新为输入寄存器的内容。

命令 0001 和 0011(参见表 6)不管 LDAC 的电平如何,都会更新 DAC 的输出。

天津市滨海新区中新生态城中天大道 1620 号生态城科技园启发大厦 5 层 106 室

第 16 页 共 20 页

#### 软件LDAC功能

使用命令 0110 写入 DAC,将加载LDAC控制寄存器(DB3 到 DB0)。默认值为 0;也就是说,LDAC引脚工作正常。将 DB3 到 DB0 位设置为 1 可以更新 DAC,而不考虑硬件LDAC引脚的状态,这样相当于硬件LDAC引脚被锁定在低位(LDAC寄存器操作模式见表 11)。

#### 表 11 LDAC覆写操作

| LDAC 位(DB3<br>到 DB0) | <br>LDAC引脚 | LDAC操作               |  |  |  |  |  |

|----------------------|------------|----------------------|--|--|--|--|--|

| 0                    | 1或0        | 由 LDAC 引脚决定          |  |  |  |  |  |

| 1                    | X (无关位)    | DAC 通道更新并覆盖 LDAC 引脚。 |  |  |  |  |  |

|                      |            | DAC 通道视 LDAC 为 1     |  |  |  |  |  |

利用寄存器,用户可以更加灵活地控制硬件引脚(见表 11 覆写操作)。如果将 DAC 的LDAC位(DB0 至 DB3)设为 0,则意味着该 DAC 的更新受硬件LDAC引脚的控制。

MSB LSB

| DB31 to<br>DB28 | DB27                                | DB26 | DB25 | DB24 | DB23 to<br>DB20                            | DB4<br>to<br>DB19 | DB3                                    | DB2 | DB1 | DB0 |  |

|-----------------|-------------------------------------|------|------|------|--------------------------------------------|-------------------|----------------------------------------|-----|-----|-----|--|

| Х               | 0                                   | 1    | 1    | 0    | X                                          | Х                 | DAC                                    |     |     |     |  |

| Don't cares     | Don't cares Command bits (C3 to C0) |      |      |      | Address bits<br>(A3 to A0)—<br>don't cares | Don't<br>cares    | Setting LDAC bit to 1 override LDA pin |     |     |     |  |

# 电源旁路和接地

当电路的精度要求很重要时,很有必要仔细考虑电路板上的电源和接地回路的布局。包含 ZYA5061T 的印制电路板上应该有独立的模拟和数字部分。如果 ZYA5061T 处于其他设备需要 AGND-to-DGND 连接的系统中,则只能在一点进行连接,并且尽可能接近 ZYA5061T。

给 ZYA5061T 供电的电源需要使用 10uF 和 0.1uF 电容器旁路。0.1uF 电容器应尽可能接近设备。10uF 电容器尽量为钽珠类型。

供电线路应该有尽可能大的线宽,以提供一个低阻抗路径和减少故障对供电线路的影响。通过铺地将时钟和其他快速切换的数字信号与 PCB 的其他部分屏蔽。尽可能避免数字和模拟信号的交叉。当信号线在板的相对一侧相交时,确保它们以直角相交,以减少耦合效应。最好的布局技术是:板材的部件一侧仅用于接地面,信号线放置在焊料一侧。

### 应用信息

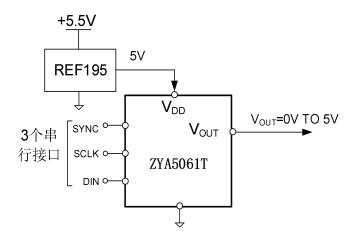

### 选择基准电压源

ZYA5061T 所需要的供电电流非常低,因此可以利用基准电压源提供器件所需的电压。 (参见图 17)。 当电源噪声相当高,或者系统电源电压不是 5 V 时(例如为 15 V),这种电源方案特别有用。基准电压源输 出一个稳定的电源电压用于 ZYA5061T。如果使用低压型 REF195,则在 DAC 输出端无负载时,它必须向 ZYA5061T提供 5 mA 电流。当 DAC输出端有负载时, REF195还需要向负载提供电流, 所需的总电流(DAC 输出上的负载为  $5 k\Omega$  ) 为  $5 mA+(5 V/5 k\Omega) = 6 mA$ 。

图 17 REF195 用作 ZYA5061T 的电源

# 双极性工作模式

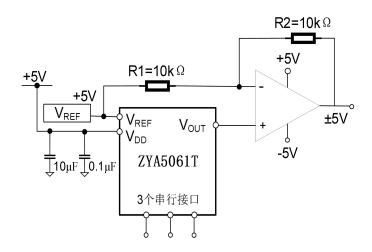

ZYA5061T 被设计用于单电源操作,但是使用图 18 中的电路也可以实现双极输出范围。电路为±5 V 的输出电压范围。在放大器输出端的轨对轨操作是使用双极性运算放大器来实现的。

任何输入码的输出电压可计算如下:

$$V_O = \left[ V_{DD} \times \left( \frac{D}{65,536} \right) \times \left( \frac{R1 + R2}{R1} \right) - V_{DD} \times \left( \frac{R2}{R1} \right) \right]$$

其中: D= 代表十进制输入码(0至65536)。

$V_{DD}$ =5V,  $R1 = R2 = 10 \text{ k } \Omega \text{ H}$ :

$$V_0 = \left(\frac{10 \times D}{65.536}\right) - 5V$$

输出电压范围为±5 V, 0x0000 对应-5 V 输出, 0xFFFF 对应+5 V 输出。

图 18 使用 ZYA5061T 的双极性工作模式

# 订购指南