## **USB PD EPR Sink Controller**

### Hynetek Semiconductor Co., Ltd.

# **HUSB238A**

#### **FEATURES**

- Fully Autonomous USB Type-C<sup>®</sup> and USB PD Sink Controller

- USB Type-C<sup>®</sup> Specification Reversion 2.1 and USB PD Specification Reversion 3.1 Supported

- Maximum 48V/5A PDO Supported

- GPIO Mode: Maximum 28 V/3.25 A EPR

FPDO and EPR AVS

- I<sup>2</sup>C Mode: Maximum 48 V/5 A EPR FPDO, EPR AVS and SPR PPS

- Automatic Legacy Protocols Detection Including BC1.2, Divider 3, QC2.0

- Support SOP' Detection

- Typical Low Power Operation: I<sub>VDD</sub>< 75 μA</li>

- Integrated VBUS Switch Driver

- Dead Battery Support

- VBUS Over-voltage Protection (OVP) and Under-voltage Protection (UVP)

- Over-temperature Protection (OTP) with Programmable Thresholds

- 2 kV HBM ESD Rating for USB IO Pins

- Small Package, 16 Lead QFN (3 mm x 3 mm)

#### **APPLICATIONS**

USB PD Sink Devices Wireless Charger

#### **GENERAL DESCRIPTION**

The HUSB238A is a highly integrated stand-alone USB Type-C® and Power Delivery (PD) Sink controller. The HUSB238A integrates the CC logic, USB PD protocol and the legacy protocols.

The HUSB238A can run in I<sup>2</sup>C mode and GPIO mode. In I<sup>2</sup>C mode, an I<sup>2</sup>C master can access the HUSB238A to configure settings, read back status and perform advanced functions such as DR Swap, VDM messages. The HUSB238A supports APDO, maximum 48 V/5 A EPR FPDO and EPR AVS in I<sup>2</sup>C mode.

While in GPIO mode, the configuration is achieved via the setting pins. The HUSB238A can be configured to support maximum 28V/3.25A PDO via VSET and ISET pins, only two resistors are used to set the voltage and current.

The ultra-low operation current of the HUSB238A helps the system to reduce the total power dissipation and suitable for a battery application.

The HUSB238A is available in QFN 3 mm x 3 mm-16L package.

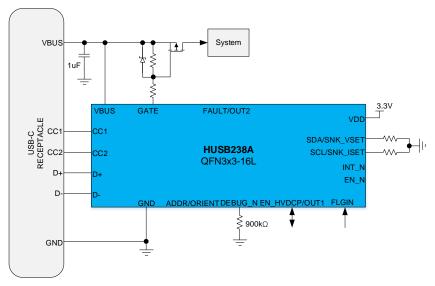

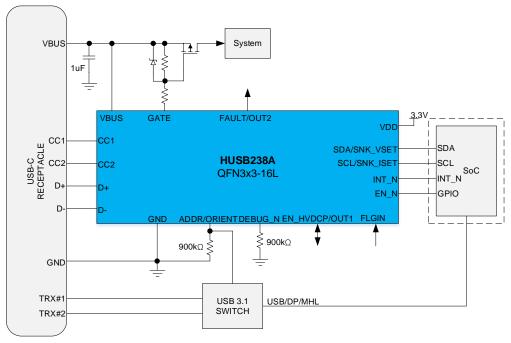

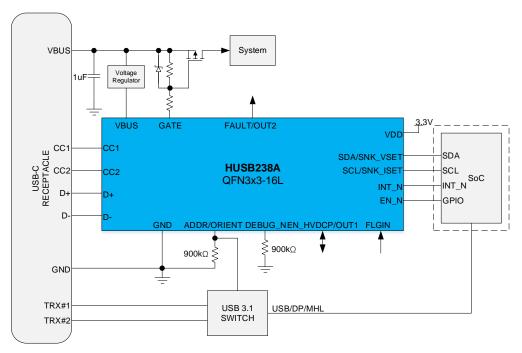

#### TYPICAL APPLICATION CIRCUIT

Figure 1. Typical Application Circuit

# **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Typical Application Circuit                 | 1  |

| Table of Contents                           | 2  |

| Revision History                            | 3  |

| Pin Configuration and Function Descriptions | 4  |

| Recommended Operating Conditions            | 6  |

| Specifications                              | 6  |

| Absolute Maximum Ratings                    | g  |

| Thermal Resistance                          | g  |

| ESD Caution                                 | g  |

| Functional Block Diagram                    | 10 |

| Theory of Operation                         | 11 |

| Enable Control                              | 11 |

| ADDR/ORIENT Pin                             | 11 |

| EN_HVDCP/OUT1 Pin                           | 11 |

| VBUS Pin                                    | 11 |

| Analog Input Pins                           | 11 |

| Digital Pins                                | 12 |

| Input and Output Pins                       | 12 |

| CC Logic                                    | 13 |

| SOP VDM Messages                            | 13 |

| Policy Engine                               | 13 |

| Fault Response                              | 14 |

| I <sup>2</sup> C Mode                       | 14 |

| Dead Battery                                | 14 |

| Sleep Mode                                  | 14 |

| Typical Application Circuits                | 15 |

| Package Outline Dimensions                  | 17 |

| Package Top Marking                         | 18 |

| Ordering Guide                              | 19 |

| Tape and Reel Information                   | 20 |

| Important Notice                            | 21 |

### **REVISION HISTORY**

| Version  | Date    | Descriptions    |

|----------|---------|-----------------|

| Rev. 1.0 | 07/2024 | Initial version |

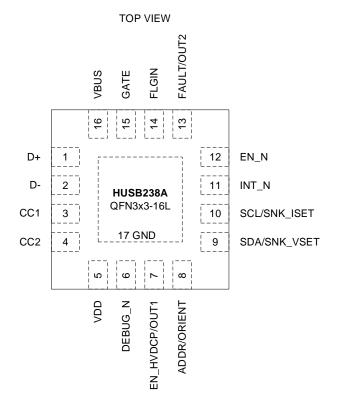

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. HUSB238A Pin Assignment

Table 1. HUSB238A-XXXXX-QN16R Pin Function Descriptions

| Pin No. | Pin Name      | Type1 | Description                                                                                                                                                                                                                                                                                            |

|---------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | D+            | Ю     | Positive line of the USB data line pair.                                                                                                                                                                                                                                                               |

| 2       | D-            | Ю     | Negative line of the USB data line pair.                                                                                                                                                                                                                                                               |

| 3       | CC1           | Ю     | USB Type-C CC1 line.                                                                                                                                                                                                                                                                                   |

| 4       | CC2           | Ю     | USB Type-C CC2 line.                                                                                                                                                                                                                                                                                   |

| 5       | VDD           | Р     | Input supply 1 for internal circuitry. It is recommended to tie this pin to the single cell battery or a 3.3 V power rail. When the power is not available this pin, the VBUS pin may power the internal circuitry if it is available. Place a $1\mu F$ ceramic capacitor across this pin and GND pin. |

| 6       | DEBUG_N       | Ю     | This pin is push-pull output to indicate the Debug Accessory Detection results.                                                                                                                                                                                                                        |

|         |               |       | Low = Debug Accessory detected                                                                                                                                                                                                                                                                         |

|         |               |       | High = Debug Accessory not detected                                                                                                                                                                                                                                                                    |

|         |               |       | A 900 k $\Omega$ resistor has to be placed this pin to GND pin.                                                                                                                                                                                                                                        |

| 7       | EN_HVDCP/OUT1 | Ю     | <b>Dual function pin</b> . In input mode, this pin (EN_HVDCP) is a digital input pin to enable the HVDCP protocol detection in Sink mode. The HUSB238A may perform different actions depending on the connection:                                                                                      |

|         |               |       | Connected to GND = Only perform BC1.2 detection                                                                                                                                                                                                                                                        |

|         |               |       | Connected to VDD = Perform HVDCP detection after BC1.2 DCP is detected                                                                                                                                                                                                                                 |

|         |               |       | In output mode, this pin (OUT1) is push-pull output whose output status can be configured by $I^2C$ .                                                                                                                                                                                                  |

|         |               |       | Note: a 900 $k\Omega$ resistor should be used when connecting to VDD or GND to reduce standby current.                                                                                                                                                                                                 |

| Pin No. | Pin Name     | Type1 | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|--------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8       | ADDR/ORIENT  | Ю     | For the HUSB238A-AAXXX-QN16R, this pin should keep floating. For the HUSB238A-BBXXX-QN16R, this pin is a <b>Dual function pin</b> . In input mode, this pin (ADDR) is a 3 state input to set the working mode. The working mode is defined as below, depending on the connection:  Connected to VDD = I <sup>2</sup> C mode with slave address 62H  Connected to GND = I <sup>2</sup> C mode with slave address 42H |

|         |              |       | Float = GPIO mode                                                                                                                                                                                                                                                                                                                                                                                                   |

|         |              |       | In output mode, this pin (ORIENT) is push-pull output to indicate the connection status.                                                                                                                                                                                                                                                                                                                            |

|         |              |       | Low = CC1 of USB Type-C receptacle is connected                                                                                                                                                                                                                                                                                                                                                                     |

|         |              |       | High = CC2 of USB Type-C receptacle is connected                                                                                                                                                                                                                                                                                                                                                                    |

|         |              |       | Note: a 900 k $\Omega$ resistor should be used when connecting to VDD or GND to reduce standby current.                                                                                                                                                                                                                                                                                                             |

| 9       | SDA/SNK_VSET | AIO   | <b>Dual functions pin</b> . In I <sup>2</sup> C mode (only for the HUSB238A-BBXXX-QN16R), this pin (SDA) is the data line of I <sup>2</sup> C bus.                                                                                                                                                                                                                                                                  |

|         |              |       | In GPIO mode, this pin (SNK_VSET) combined with SNK_ISET to determine the requested voltage.                                                                                                                                                                                                                                                                                                                        |

| 10      | SCL/SNK_ISET | AIO   | <b>Dual functions pin</b> . In I <sup>2</sup> C mode (only for the HUSB238A-BBXXX-QN16R), this pin (SDA) is the clock line of I <sup>2</sup> C bus.                                                                                                                                                                                                                                                                 |

|         |              |       | In GPIO mode, this pin (SNK_ISET) combined with SNK_VSET to determine the requested current.                                                                                                                                                                                                                                                                                                                        |

| 11      | INT_N        | AIO   | In I <sup>2</sup> C mode (only for the HUSB238A-BBXXX-QN16R), this pin (INT_N) is an open-<br>drain output to request the attention of processor by pulling down this pin. For the<br>HUSB238A-AAXXX-QN16R, keep this pin floating.                                                                                                                                                                                 |

| 12      | EN_N         | Al    | Chip enabled pin. It is pulled up internally and HUSB238A is enabled by pulling this pin to GND.                                                                                                                                                                                                                                                                                                                    |

| 13      | FAULT/OUT2   | DO    | General output pin. The output purpose can be configured as a FAULT pin. When used as FAULT pin, the device pulls this pin high if the power adapter cannot supply the required voltage or current or if an OVP/UVP/OTP event is detected. This pin can be also configured as General output pin (OUT2) controller by I <sup>2</sup> C master (only for the HUSB238A-BBXXX-QN16R).                                  |

| 14      | FLGIN        | DI    | General input pin. This input signal can be used to disable the GATE driver and generate an interrupt when there is a valid high voltage is detected. It can be also configured as just an interrupt source for INT N, not disabling GATE driver.                                                                                                                                                                   |

| 15      | GATE         | 0     | Open drain output. This pin is employed to control the external VBUS switch.                                                                                                                                                                                                                                                                                                                                        |

| 16      | VBUS         | P     | This pin has multiple functions including VBUS voltage detection, the discharge path for VBUS pin and the Input supply 2 for internal circuitry. When VDD is unpowered, the HUSB238A consumes power from this pin.                                                                                                                                                                                                  |

| 17      | GND          | Р     | Ground connection point                                                                                                                                                                                                                                                                                                                                                                                             |

Legend:

A = Analog Pin

P = Power Pin

D = Digital Pin I = Input Pin

O = Output Pin

### RECOMMENDED OPERATING CONDITIONS

Table 2.

| Parameter                               | Rating           |

|-----------------------------------------|------------------|

| VDD Input Voltage                       | 3 V to 5.5 V     |

| VBUS Input Voltage (VDD is available)   | 3.15 V to 29.4 V |

| VBUS Input Voltage (VDD is unavailable) | 4.5 V to 29.4 V  |

| Operating Temperature Range (Junction)  | -40 °C to 125 °C |

| Ambient Temperature Range               | -40 °C to 85 °C  |

## **SPECIFICATIONS**

$V_{DD}$  = 3 V to 5.5 V or  $V_{DD}$  < 3 V and VBUS = 4.5 V to 29.4 V,  $T_{J}$  = -40 °C to 125 °C for minimum and maximum specifications, and  $T_{A}$  = 25 °C for typical specifications, unless otherwise noted.

Table 3.

| Parameter                                                                     | Symbol                  | Test<br>Conditions/Comments                                                              | Min                | Tim  | Mov                | Unit |

|-------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------|--------------------|------|--------------------|------|

|                                                                               | Symbol                  | Conditions/Comments                                                                      | Min                | Тур  | Max                | Unit |

| Power Supply                                                                  |                         |                                                                                          |                    |      |                    |      |

| VDD UVLO Rising Threshold                                                     | V <sub>DD_UVLO_R</sub>  | Power Up to normal operation                                                             | 2.65               | 2.75 | 2.85               | V    |

| VDD UVLO Hysteresis                                                           | VDD_UVLO_HYS            | Hysteresis Voltage to be shutdown                                                        |                    | 0.1  |                    | V    |

| VDD Standby Current                                                           | I <sub>STBY</sub>       | EN_N=Low without attachment, V <sub>DD</sub> =4.5 V & V <sub>BUS</sub> =0 V              |                    | 50   | 75                 | μA   |

| VDD Operating Current in Active<br>Mode                                       | lop_vdd                 | EN_N=Low and attached as an Active Sink, V <sub>DD</sub> =4.5 V & V <sub>BUS</sub> =5 V  |                    | 4    | 4.5                | mA   |

| VBUS UVLO Threshold                                                           | V <sub>BUS_UVLO_R</sub> | V <sub>DD</sub> =0 V                                                                     | 3.67               | 4    | 4.4                | V    |

| VBUS UVLO Hysteresis                                                          | VBUS_UVLO_HYS           | Hysteresis Voltage to be shutdown                                                        |                    | 0.1  |                    | V    |

| VBUS Operating Current in Active Mode                                         | IOP_VBUS                | EN_N=Low and attached as an Active Sink, V <sub>DD</sub> =0 V & V <sub>BUS</sub> =29.4 V |                    | 4    | 4.5                | mA   |

| Open Drain Output Pins (GATE, INT_N)                                          |                         |                                                                                          |                    |      |                    |      |

| Output Low Voltage                                                            | V <sub>OL_OD</sub>      | Sink current=2 mA                                                                        |                    |      | 0.4                | V    |

| Enable Pin (EN_N)                                                             |                         |                                                                                          |                    |      |                    |      |

| Low Level Input Threshold                                                     | VIL_EN                  |                                                                                          |                    |      | 0.4                | V    |

| High Level Input Threshold                                                    | V <sub>IH_EN</sub>      |                                                                                          | 1.35               |      |                    | V    |

| Input and Output Pins (DEBUG_N, ADDR/ORIENT, EN_HVDCP/OUT1)                   |                         |                                                                                          |                    |      |                    |      |

| High Level Input Threshold                                                    | VIH_IO                  |                                                                                          | $0.8 \cdot V_{DD}$ |      |                    | V    |

| Output Low Voltage                                                            | $V_{OL\_PP}$            | Sink current=1 mA                                                                        |                    |      | $0.2 \cdot V_{DD}$ | V    |

| Output High Voltage                                                           | V <sub>OH_PP</sub>      | Source current=1 mA                                                                      | $0.8 \cdot V_{DD}$ |      |                    | V    |

| I <sup>2</sup> C Characteristics (SDA, SCL pins for the HUSB238A-BBXXX-QN16R) |                         |                                                                                          |                    |      |                    |      |

| Output Low Voltage                                                            | V <sub>OL_I2C</sub>     | Sink current is 2 mA                                                                     |                    |      | 0.4                | V    |

| Input Low Voltage                                                             | V <sub>IL_I2C</sub>     | I <sup>2</sup> C Pull up voltage is 3.3 V                                                |                    |      | 0.99               | V    |

| Input High Voltage                                                            | V <sub>IH_I2C</sub>     | I <sup>2</sup> C Pull up voltage is 3.3 V                                                | 2.31               |      |                    | V    |

| Input Voltage Hysteresis                                                      | V <sub>HYS_I2C</sub>    | I <sup>2</sup> C Pull up voltage is 3.3 V                                                | 0.17               |      |                    | V    |

| SCL Clock Frequency                                                           | fscl_i2C                |                                                                                          | 0                  |      | 400                | kHz  |

| Analog Input Pins (SNK_ISET, SNK_VSET)                                        |                         |                                                                                          |                    |      |                    |      |

| Pull up Source Current                                                        | Isnk_vset               | On SNK_VSET pin                                                                          | 95                 | 100  | 105                | μA   |

|                               |                        | Test                                             |        |             |        |       |

|-------------------------------|------------------------|--------------------------------------------------|--------|-------------|--------|-------|

| Parameter                     | Symbol                 | Conditions/Comments                              | Min    | Тур         | Max    | Unit  |

|                               | I <sub>SNK_ISET</sub>  | On SNK_ISET pin                                  | 95     | 100         | 105    | μA    |

| SNK_VSET Setting Resistor     | RSNK_VSET0             | VSET_VOLTAGE=5 V                                 | 0      |             | 2      | kΩ    |

|                               | RSNK_VSET1             | VSET_VOLTAGE=9 V                                 | 2.85   | 3           | 3.15   | kΩ    |

|                               | RSNK_VSET2             | VSET_VOLTAGE=12 V                                | 5.7    | 6           | 6.3    | kΩ    |

|                               | RSNK_VSET3             | VSET_VOLTAGE=15 V                                | 10.45  | 11          | 11.55  | kΩ    |

|                               | RSNK_VSET4             | VSET_VOLTAGE=20 V                                | 18.05  | 19          | 19.95  | kΩ    |

|                               | RSNK_VSET5             | VSET_VOLTAGE=28 V                                | 1      |             |        | МΩ    |

| SNK_VSET Setting Resistor     | RSNK_ISET0             | ISET_CURRENT=1.25 A                              | 0      |             | 1.5    | kΩ    |

|                               | RSNK_ISET1             | ISET_CURRENT=1.5 A                               | 2.137  | 2.25        | 2.362  | kΩ    |

|                               | RSNK_ISET2             | ISET_CURRENT=1.75 A                              | 3.8    | 4           | 4.2    | kΩ    |

|                               | RSNK_ISET3             | ISET_CURRENT=2 A                                 | 5.7    | 6           | 6.3    | kΩ    |

|                               | RSNK_ISET4             | ISET_CURRENT=2.25 A                              | 7.98   | 8.4         | 8.82   | kΩ    |

|                               | R <sub>SNK_ISET5</sub> | ISET_CURRENT=2.5 A                               | 10.925 | 11.5        | 12.075 | kΩ    |

|                               | R <sub>SNK_ISET6</sub> | ISET_CURRENT=2.75 A                              | 14.82  | 15.6        | 16.38  | kΩ    |

|                               | R <sub>SNK_ISET7</sub> | ISET_CURRENT=3 A                                 | 19.95  | 21          | 22.05  | kΩ    |

|                               | R <sub>SNK_ISET8</sub> | ISET_CURRENT=3.25 A                              | 1      |             |        | МΩ    |

| Type-C Pins (CC1, CC2)        |                        |                                                  |        |             |        |       |

| Sink Pull Down Resistor       | Rd                     | In Sink Mode                                     | 4.6    | 5.1         | 5.6    | kΩ    |

| CC Over-voltage Threshold     | Vccov                  | For any CC pin, VDD >                            |        | $V_{DD}$ +3 |        | V     |

|                               |                        | $V_{DD\_UVLO\_R}$                                |        |             |        |       |

|                               |                        | For any CC pin, VDD <                            |        | 6.3         |        | V     |

| \/DUO.D.                      |                        | (V <sub>DD_UVLO_R</sub> -0.1 V)                  |        |             |        |       |

| VBUS Present and Protection   | \ /D                   | D                                                | 0.07   | 4           | 4.4    | .,    |

| VBUS Present Rising Threshold | vVB <sub>PRS_R</sub>   | Rising edge to set VBUS_OK=1b                    | 3.67   | 4           | 4.4    | V     |

| VBUS Present Hysteresis       | vVB <sub>PRS_HYS</sub> | Hysteresis Voltage to set VBUS_OK=0b             |        | 0.7         |        | V     |

| VBUS UV falling Threshold     | vVB <sub>UV_F0</sub>   | Falling edge to detect disconnection when 26 V > |        | 86          |        | %     |

|                               |                        | RDO > 10 V, refer to the requested voltage       |        |             |        |       |

|                               | vVB <sub>UV_F1</sub>   | Falling edge to detect                           |        | 80          |        | %     |

|                               | V V D <sub>UV_F1</sub> | disconnection when 10 V ≥                        |        | 00          |        | /0    |

|                               |                        | RDO > 5 V, refer to the                          |        |             |        |       |

|                               |                        | requested voltage                                |        |             |        |       |

|                               | vVB <sub>UV_F2</sub>   | Falling edge to detect                           |        | 22.4        |        | V     |

|                               | 11201212               | disconnection when RDO ≥ 26                      |        |             |        |       |

|                               |                        | V                                                |        |             |        |       |

| VBUS UV Hysteresis            | vVBuv Hys              | Ĭ                                                |        | 0.1         |        | V     |

| VBUS Over-voltage Threshold   | VBUS_OV                | Refer to the requested voltage                   |        | 120         |        | %     |

| VBUS Over-voltage Hysteresis  | vVBov_Hys              | Traini to the requested voltage                  |        | 0.1         |        | V     |

| BC1.2 and HVDCP Detection     | V V DOV_H13            |                                                  |        | 0.1         |        |       |

| BC1.2 Source voltage          | VDPM_SRC_0V6           |                                                  |        | 0.6         |        | V     |

| D- Source Voltage for 3.3V    | VDM_SRC_3P3            |                                                  |        | 3.3         |        | v     |

| D+ Source Voltage for 3.3V    | VDP_SRC_3P3            |                                                  |        | 3.3         |        | V     |

| D- 3.3V Pull-up Resistance    | RDM_SRC_3P3            |                                                  |        | 1.24        |        | kΩ    |

| D+ 3.3V Pull-up Resistance    | RDP_SRC_3P3            |                                                  |        | 1.24        |        | kΩ    |

| Data Detect Voltage           | VDAT_REF               |                                                  |        | 325         |        | mV    |

| Digital Input Pin (FLGIN)     | ▼ DAI_NEF              |                                                  |        | 020         |        | 111 V |

| Digital Input High Voltage    | VIH_GPIO               | VI_GPIO for 3.3 V                                | 2      |             |        | V     |

| Digital Input Low Voltage     | VIH_GPIO<br>VIL_GPIO   | VI_GPIO for 3.3 V<br>VI_GPIO for 3.3 V           |        |             | 0.8    | V     |

| Digital hipat Low voltage     | I VIL_GPIO             | VI_OI IO IOI 0.0 V                               | I      |             | 0.0    | I *   |

| Parameter                       | Symbol              | Test<br>Conditions/Comments | Min                | Тур  | Max                | Unit |

|---------------------------------|---------------------|-----------------------------|--------------------|------|--------------------|------|

| Digital Output Pin (FAULT/OUT2) |                     |                             |                    |      |                    |      |

| Output Low Voltage              | V <sub>OL_PP</sub>  | Sink current=1 mA           |                    |      | $0.2V_{\text{DD}}$ | V    |

| Output High Voltage             | V <sub>OH_PP</sub>  | Source current=1 mA         | 0.8V <sub>DD</sub> |      |                    | V    |

| Thermal Shut Down               |                     |                             |                    |      |                    |      |

| Thermal Shut Down Threshold     | T <sub>TSD_R</sub>  | Rising Threshold            |                    | 150  |                    | °C   |

|                                 | T <sub>TSD_F</sub>  | Falling Threshold           |                    | 130  |                    | °C   |

| TSW Debounce Time               | t <sub>DB_TSW</sub> |                             |                    | 100  |                    | ms   |

| TSD Debounce Time               | t <sub>DB_TSD</sub> |                             |                    | 1000 |                    | ms   |

### ABSOLUTE MAXIMUM RATINGS

#### Table 4.

| Parameter                                                                                                    | Rating           |

|--------------------------------------------------------------------------------------------------------------|------------------|

| VBUS, GATE, CC1, CC2                                                                                         | -0.3 V to 33 V   |

| D+, D-, ADDR/ORIENT, VDD, INT_N, SDA/SNK_VSET, SCL/SNK_ISET, EN_HVDCP/OUT1, FLGIN, EN_N, FAULT/OUT2, DEBUG_N | -0.3 V to 7 V    |

| Operating Temperature Range (Junction)                                                                       | -40 °C to 125 °C |

| Soldering Conditions                                                                                         | JEDEC J-STD-020  |

| Electrostatic Discharge (ESD)                                                                                |                  |

| Human Body Model                                                                                             | ±2000 V          |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

#### **Table 5. Thermal Resistance**

| Package Type | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|--------------|-----------------|-----------------|------|

| QFN3x3-16L   | 70              | 41              | °C/W |

#### **ESD CAUTION**

#### **Electrostatic Discharge Sensitive Device.**

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

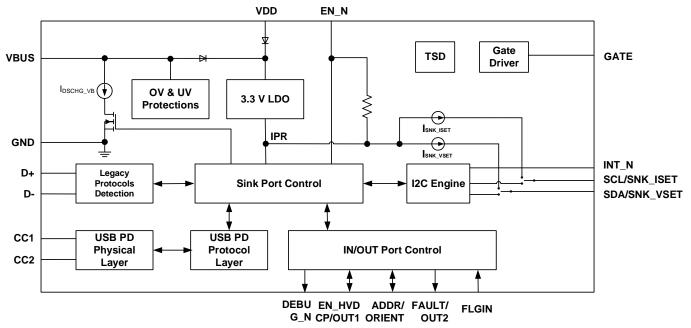

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 3. Functional Block Diagram

### THEORY OF OPERATION

The HUSB238A is a USB PD Sink controller. It supports PD protocol and legacy charging protocols detection and requests the desired power per the user settings. The HUSB238A can run in I<sup>2</sup>C mode (only for the HUSB238A-BBXXX-QN16R) and GPIO mode. In I<sup>2</sup>C mode, an I<sup>2</sup>C master can access the HUSB238A to configure settings, read back status and perform advanced functions such as DR Swap, VDM messages. While in GPIO mode, the configuration is achieved via the setting pins.

#### **ENABLE CONTROL**

HUSB238A has an enable pin (EN\_N) for the whole system control. When EN\_N is high, the whole system is disabled, When EN N is low, the whole system is enabled.

When EN\_N is low, and HUSB238A is in I<sup>2</sup>C mode (only for the HUSB238A-BBXXX-QN16R), there is an additional ENABLE bit to enable or disable the HUSB238A, when this ENABLE bit is 0b, all of functions of HUSB238A is turned off except the I<sup>2</sup>C accessibility, EN\_N detection and UVLO detection. Only when the ENABLE=1b, the disabled functions resume to work.

#### ADDR/ORIENT PIN

For ADDR/ORIENT pin, it is employed to select whether HUSB238A works as I<sup>2</sup>C mode (only for the HUSB238A-BBXXX-QN16R) or GPIO mode.

**Table 6. Work Mode Configuration**

| ADDR/ORIENT Connection                   | HUSB238A Work Mode Configured                |

|------------------------------------------|----------------------------------------------|

| Connected to VDD via a 900kΩ Resistor    | I <sup>2</sup> C mode with slave address=62H |

| Floating (MUST for HUSB238A-AAXXX-QN16R) | GPIO mode                                    |

| Connected to GND via a 900kΩ Resistor    | I <sup>2</sup> C mode with slave address=42H |

#### **EN HVDCP/OUT1 PIN**

For EN\_HVDCP/OUT1 pin, it is employed to determine whether HUSB238A can support HVDCP detection.

**Table 7. Legacy Protocol Detection Configuration**

| EN_HVDCP/OUT1 Connection              | HUSB238A Legacy Protocol Detection |

|---------------------------------------|------------------------------------|

| Connected to VDD via a 900kΩ Resistor | Perform BC1.2 and HVDCP protocols  |

| Floating                              | Perform BC1.2 and HVDCP protocols  |

| Connected to GND via a 900kΩ Resistor | Only perform BC1.2 detection       |

#### **VBUS PIN**

The VBUS pin has multiple functions for the applications. It could be an input power source, the discharging path and the monitor pin for protections and disconnection.

#### **ANALOG INPUT PINS**

After the initialization, the HUSB238A is able to output the status of current connection. When ADDR/ORIENT is floating during initialization, HUSB238A is in GPIO mode. In this mode, the SDA/SNK\_VSET, SCL/SNK\_ISET pins are repopulated as analog input pins.

#### SNK\_VSET PIN

This pin is used to set the request voltage. This pin is pulled up internally. Connect a resister with 1% tolerance between SNK\_VSET and GND to indicate the SNK\_VSET\_VOLTAGE value as shown in Table 8.

Table 8. SNK\_VSET Setting

| $R_{SNK\_VSET}$ ( $k\Omega$ ) | Preferred Voltage (V) |

|-------------------------------|-----------------------|

| 0                             | 5                     |

| 3                             | 9                     |

| 6.04                          | 12                    |

| 11                            | 15                    |

| 19.1                          | 20                    |

| R <sub>SNK_VSET</sub> (kΩ) | Preferred Voltage (V)           |

|----------------------------|---------------------------------|

| Open                       | 28 (if EPR CAP SNK=0b, then 20) |

The RDO voltage of the HUSB238A is determined by the lower value between SNK\_VSET and SNK\_PDO2\_VOLTAGE. SNK\_PDO2\_VOLTAGE is programmable by internal fuse options and the default value is 20 V. The requested voltage value can be changed dynamically with the resistance value change in GPIO mode.

#### SNK ISET PIN

This pin is used to set the request current. This pin is pulled up internally. Connect a resister with 1% tolerance between SNK\_ISET and GND to indicate the ISET\_CURRENT value as shown in Table 9.

Table 9. SNK\_ISET Setting

| R <sub>SNK_ISET</sub> (kΩ) | Preferred CURERNT (A) |

|----------------------------|-----------------------|

| 0                          | 1.25                  |

| 2.26                       | 1.5                   |

| 4.02                       | 1.75                  |

| 6.04                       | 2                     |

| 8.45                       | 2.25                  |

| 11.5                       | 2.5                   |

| 15.8                       | 2.75                  |

| 21                         | 3                     |

| Open                       | 3.25                  |

The RDO current of the HUSB238A is determined by the lower value between ISET\_CURRENT and SNK\_PDO2\_CURRENT. SNK\_PDO2\_CURRENT is programmable by internal fuse options and the default value is 3.25 A. The requested current value can be changed dynamically with the resistance value change in GPIO mode.

#### **DIGITAL PINS**

There are two additional digital pins for extended application. The two pins are FLGIN and FAULT/OUT2.

#### FAULT/OUT2

The FAULT/OUT2 pin is a digital output pin. It can be assigned as several functions.

Fault Indication: Output Low in default. The HUSB238A pulls this pin high when a fault occurs.

**ID Indication**: This pin indicates connection state.

#### **Table 10. ID Indication Definition**

| ID Status | Description                      |  |  |  |

|-----------|----------------------------------|--|--|--|

| Low       | Attached as a Source             |  |  |  |

| High-Z    | Attached as a Sink or unattached |  |  |  |

**OUT2**: Extended output pin, I<sup>2</sup>C master can write the register bit to change the output state.

#### **FLGIN**

The FLGIN pin is a digital input pin. It is an input source for interrupt. This interrupt can be set INT\_N low if it is not masked. Furthermore, this input signal can be mapped to disable GATE pin immediately by I<sup>2</sup>C master.

#### INPUT AND OUTPUT PINS

There are 3 pins that are implemented by dual functions. They are all input and output pins. However, they perform input pin only during initialization when the HUSB238A determines the settings by these pin. After the initialization, these pins switches to output pin with push-pull output. These pins are DEBUG\_N, EN\_HVDCP/OUT1 and ADDR/ORIENT.

#### **DEBUG N PIN**

The DEBUG\_N pin is a push-pull output that indicate HUSB238A connection status in Table 11:

#### Table 11. DEBUG\_N Pin Definition

| DEBUG_N Status | Description              |  |  |  |

|----------------|--------------------------|--|--|--|

| Low            | Debug Accessory detected |  |  |  |

| DEBUG_N Status | Description                  |

|----------------|------------------------------|

| High           | Debug Accessory not detected |

#### **ORIENT PIN**

The ORIENT pin is a push-pull output that indicate HUSB238A connection status in Table 12.

#### **Table 12. ORIENT Pin Definition**

| ORIENT Status | Description                       |  |  |  |

|---------------|-----------------------------------|--|--|--|

| Low           | CC1 is connected or Not connected |  |  |  |

| High          | CC2 is connected                  |  |  |  |

#### **OUT1 PIN**

The OUT1 pin is purely a general output pin, I2C master can write the register bit to change the output state.

#### **CC LOGIC**

The HUSB238A is able to support the USB Type-C Rev.2.1. CC1 and CC2 pins are used to detect the attachment or detachment with the external devices.

#### SOP VDM MESSAGES

The HUSB238A supports Structured VDMs. Therefore, the Discover Identity, Discover SVIDs, Discover Modes, Enter Mode and Exit Mode Commands are all supported by the HUSB238A. The HUSB238A can transmit Structure VDMs controlled by I<sup>2</sup>C master.

#### **POLICY ENGINE**

The following sections describes the system policy for typical applications.

#### SINK REQUESTED POWER DETERMINATION

The request data object (RDO) could be determined in different ways in different modes.

#### RDO IN GPIO MODE

The HUSB238A can request different voltage per the predetermined settings. There are two ways where the request voltage can be set. One is the configuration of SNK\_ISET and SNK\_VSET pin and another way is the SNK\_RDO2 Configurations. The HUSB238A compares the two values and uses the lower value as its target RDO in GPIO mode.

For example, if the SNK\_VSET and SNK\_ISET is configured as 9V / 3A. The SNK\_RDO2 Configurations is 12V / 2A. Then the RDO that HUSB238A requests from the PD source is 9V / 2A.

After the RDO is determined, the HUSB238A loops through the PD source PDOs from highest voltage first to find the first PDO that satisfies the following conditions:

- 1.  $SOURCE_PDO_VOLTAGE \leq RDO_VOLTAGE$

- 2. SOURCE PDO CURRENT ≥ RDO CURRENT

If both the conditions above are satisfied, then HUSB238A sends a request for this source PDO with operating current set to the RDO current value.

If either one of the condition is not satisfied, the HUSB238A continues to compare with the second highest voltage source PDO or requests 5V source PDO directly, depending on the RDO\_VOLTAGE\_SELECT.

The RDO results are also suitable for legacy charging protocol request. When performing the legacy charging protocol detection, the request voltage is also determined by this RDO results.

#### RDO IN PC MODE

Additionally, in I<sup>2</sup>C mode, HUSB238A can access the internal registers to dynamic change the RDO by I<sup>2</sup>C bus. After initialization, the HUSB238A may receive the Source Capabilities message from the PD source adapter and the HUSB238A saves the source capability information in registers SRC\_PDO\_5V to SRC\_PDO\_20V. The I<sup>2</sup>C master can visit the HUSB238A registers through the I<sup>2</sup>C bus and select a proper PDO by setting SRC\_PDO register and then writing 0x01 to GO\_COMMAND register.

The I<sup>2</sup>C master has the highest priority. If using I<sup>2</sup>C master to select a source PDO, it over writes the internal RDO which is created by SNK\_VSET, SNK\_ISET pins and internal factory fuse option, and the HUSB238A requests the I<sup>2</sup>C master selected source PDO once the I<sup>2</sup>C commands are written.

#### LEGACY CHARGER DETECTION

After the power on reset, the HUSB238A runs the PD PE or Apple Divider 3 and BC1.2 detections after the connection is established.

#### **EMARKER EMULATION**

The HUSB238A is able to respond a Discover Identity message in SOP' format anytime.

#### **FAULT RESPONSE**

The HUSB238A implements multiple protections to prevent any damage from failure. CCOV, OVP, UV, TSD, UVLO are all involved.

#### CC OVER VOLTAGE PROTECTION

Since CC1 and CC2 in Type-C connector is very close to VBUS pin, it is possible that the CC1 and CC2 pins are shorted to VBUS pin in some unexpected cases. It is important to guarantee that the CC1 and CC2 pins can be survived under such accidents. When the CC over-voltage condition occurs, the HUSB238A enters fault mode.

#### **OVER VOLTAGE PROTECTION**

The HUSB238A detects the VBUS pin voltage to achieve over-voltage protection function. The OVP threshold is changed with the Requested Voltage. When the over-voltage condition occurs, the HUSB238A enters fault Mode.

#### UNDER VOLTAGE PROTECTION

The HUSB238A detects the VBUS pin voltage to achieve a disconnection detection. When the under voltage fault occurs, the HUSB238A moves out the Attached.SNK state.

#### THREMAL SHUT DOWN

The HUSB238A integrates thermal shut down function. It monitors the internal junction temperature. If the junction temperature reaches the thermal shut down threshold  $T_{TSD,R}$  for  $t_{TSD}$ , the TSD fault can be set to entry the fault mode.

#### I<sup>2</sup>C MODE

After the initialization, the HUSB238A is able to output the status of current connection. When ADDR/ORIENT is connected to VDD or GND during initialization (only allowed for the HUSB238A-BBXXX-QN16R), HUSB238A is in I<sup>2</sup>C mode. In this mode, the INT N, SDA/SNK VSET, SCL/SNK ISET pins are repopulated as I<sup>2</sup>C interface pins.

#### INT N

The INT\_N pin is an active LOW open drain interruption output used to prompt the processor to access the I<sup>2</sup>C registers. An external pull-up resistor is recommended for INT\_N pin to output a high voltage level when this pin is not active.

#### SCL AND SDA

The HUSB238A implements a Fast-mode I<sup>2</sup>C interface. The SCL and SDA pins can detect the status of the input signals and drive the I<sup>2</sup>C bus when needed.

#### **DEAD BATTERY**

The HUSB238A works as PD sink role which requires Rd resistor to be presented on the CC pins even in the unpowered state for successful Type-C detection by source adapter.

#### **SLEEP MODE**

The HUSB238A has a specified Sleep Mode to save the power consumption from VDD or VBUS. This function can be enabled or disabled by internal fuse option.

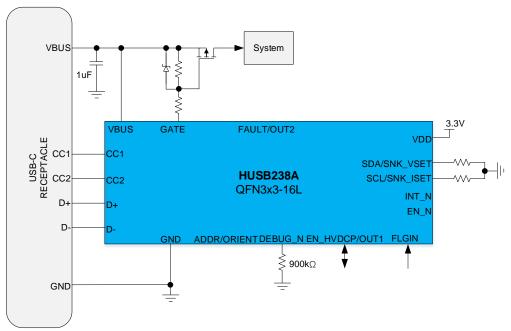

## TYPICAL APPLICATION CIRCUITS

Figure 4. HUSB238A configured as GPIO mode (Maximum 28V)

Figure 5. HUSB238A configured as PC mode (Maximum 28V)

Figure 6. HUSB238A configured as PC mode (Maximum 48V)

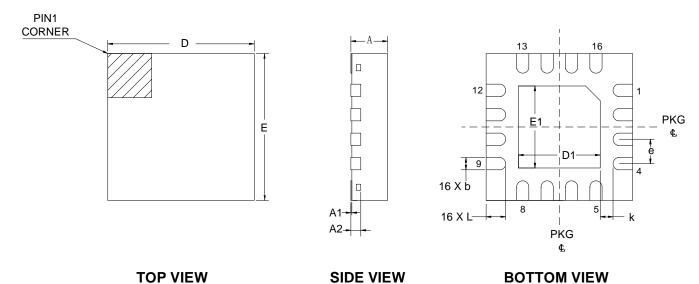

## PACKAGE OUTLINE DIMENSIONS

|         | DIMENSION IN MILLIMETERS |           |      |  |  |  |  |

|---------|--------------------------|-----------|------|--|--|--|--|

| SYMBOLS | MIN                      | NOM       | MAX  |  |  |  |  |

| Α       | 0.70                     | 0.75      | 0.80 |  |  |  |  |

| A1      | 0.00                     | 0.02      | 0.05 |  |  |  |  |

| A2      |                          | 0.203 REF |      |  |  |  |  |

| b       | 0.18                     | 0.25      | 0.30 |  |  |  |  |

| D       | 3.00 BSC                 |           |      |  |  |  |  |

| Е       | 3.00 BSC                 |           |      |  |  |  |  |

| D1      | 1.55                     | 1.70      | 1.80 |  |  |  |  |

| E1      | 1.55                     | 1.80      |      |  |  |  |  |

| е       | 0.50 BSC                 |           |      |  |  |  |  |

| L       | 0.30 0.40 0.50           |           |      |  |  |  |  |

| k       | 0.20 MIN                 |           |      |  |  |  |  |

Figure 7. QFN 3 mm × 3 mm -16L Package

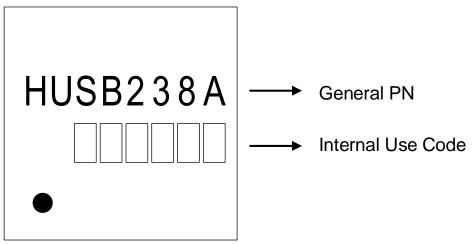

# **PACKAGE TOP MARKING**

Figure 8. Package Top Marking

# **ORDERING GUIDE**

| Model                | Package    | SOP' | SNK_PDO2 | RDO Mismatch | Package Option    |  |

|----------------------|------------|------|----------|--------------|-------------------|--|

| HUSB238A-BB001-QN16R | QFN3X3-16L | NO   | 28V/3A   | Next PDO     | Tape & Reel, 5000 |  |

| HUSB238A-BB002-QN16R | QFN3X3-16L | YES  | 28V/3A   | Next PDO     | Tape & Reel, 5000 |  |

| HUSB238A-BB003-QN16R | QFN3X3-16L | NO   | 20V/3A   | Next PDO     | Tape & Reel, 5000 |  |

| HUSB238A-BB004-QN16R | QFN3X3-16L | NO   | 5V/3A    | Next PDO     | Tape & Reel, 5000 |  |

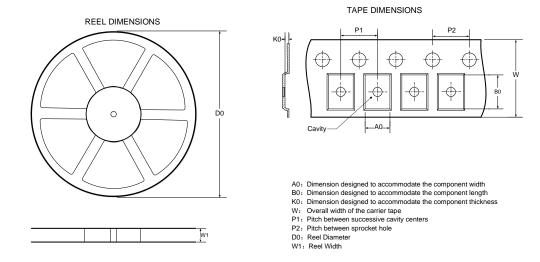

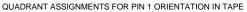

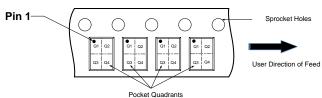

## TAPE AND REEL INFORMATION

#### DIMENSIONS AND PIN1 ORIENTATION

| Device               | Package Type | D0<br>(mm) | W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant | Quantity |

|----------------------|--------------|------------|------------|------------|------------|------------|------------|------------|-----------|------------------|----------|

| HUSB238A-XXXXX-QN16R | QFN3X3-16L   | 330.00     | 12.40      | 3.35       | 3.35       | 1.13       | 8.00       | 4.00       | 12.00     | Q1               | 5000     |

All dimensions are nominal

Figure 9. Tape and Reel Information

### IMPORTANT NOTICE

Hynetek Semiconductor Co., Ltd. and its subsidiaries (Hynetek) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to Hynetek's terms and conditions of sale supplied at the time of order acknowledgment.

Hynetek warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in Hynetek's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent Hynetek deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

Hynetek assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using Hynetek components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Hynetek does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which Hynetek components or services are used. Information published by Hynetek regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from Hynetek under the patents or other intellectual property of Hynetek.

Reproduction of significant portions of Hynetek information in Hynetek data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Hynetek is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of Hynetek components or services with statements different from or beyond the parameters stated by Hynetek for that component or service voids all express and any implied warranties for the associated Hynetek component or service and is an unfair and deceptive business practice.

Hynetek is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of Hynetek components in its applications, notwithstanding any applications-related information or support that may be provided by Hynetek. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify Hynetek and its representatives against any damages arising out of the use of any Hynetek components in safety-critical applications.

In some cases, Hynetek components may be promoted specifically to facilitate safety-related applications. With such components, Hynetek's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No Hynetek components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those Hynetek components which Hynetek has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of Hynetek components which have not been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

Hynetek has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, Hynetek will not be responsible for any failure to meet ISO/TS16949.

Please refer to below URL for other products and solutions of Hynetek Semiconductor Co., Ltd.

©2024 Hynetek Semiconductor Co., Ltd. All rights reserved.

Trademarks and registered trademarks are the property of their respective owners.

www.hynetek.com