# 36 V, Latch-Up Immune, 4-/8-Channel, Precision Analog Multiplexers

### **Features**

- Latch-Up Immune for all pins

- Break-Before-Make Construction

- Fast Switching Time: ton 166 nS; toff 135 nS

- Low On Resistance: 270 Ω

Off Leakage Current: 10 pA

- Charge Injection: 14.8 pC

- TTL and CMOS-Compatible Inputs

- Supply Voltage: ±5 V to ±18 V

- Specified Temperature Range: -40 °C to 125 °C

- ESD: 8 kV HBM

## **Applications**

- Analog Input/Output Module

- · Industrial and Process Control Systems

- Instruments

- ATE

- · Communication Systems

- · Relay Replacement

### **General Description**

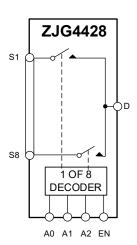

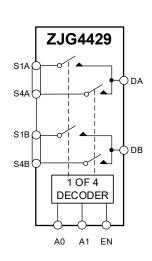

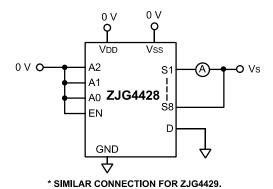

The ZJG4428 and ZJG4429 are analog multiplexers, with the ZJG4428 comprising eight single channels and the ZJG4429 comprising four differential channels. The ZJG4428 switches one of eight inputs to a common output as determined by the 3-bit binary address lines, A0, A1, and A2. The ZJG4429 switches one of four differential inputs to a common differential output as determined by the 2-bit binary address lines, A0 and A1. An EN input on each device is used to enable or disable the device. When disabled, all channels are switched off. They support bidirectional analog and digital signals on the source (Sx) and drain(D) pins.

The ZJG4428 and ZJG4429 provide latch-up immunity, preventing undesirable high current events between parasitic structures within the device typically caused by overvoltage events. A latch-up condition typically continues until the power supply rails are turned off and can lead to device failure. The latch-up immunity feature allows the ZJG4428 and ZJG4429 to be used in harsh environments.

The ZJG4428 and ZJG4429 are available in SOIC-16 and TSSOP-16 packages and are pin compatible with industry standards.

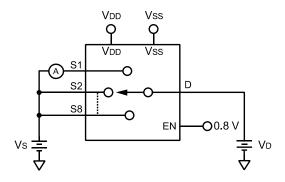

# **Functional Block Diagram**

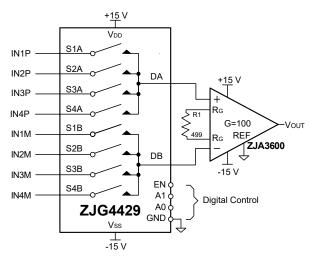

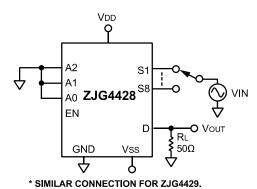

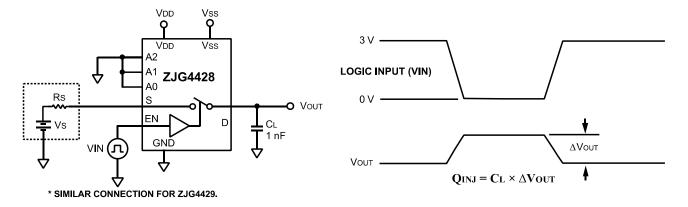

# **Typical Application**

## **Table of Contents**

| Features                                   | 1 |

|--------------------------------------------|---|

| Applications                               | 1 |

| General Description                        | 1 |

| Functional Block Diagram                   | 1 |

| Typical Application                        | 1 |

| Table of Contents                          | 2 |

| Revision History (Release B)               | 3 |

| Pin Configuration and Function Description | 4 |

| Absolute Maximum Ratings                   | 6 |

| Thermal Resistance                         | 6 |

| Specifications                      | /  |

|-------------------------------------|----|

| Typical Performance Characteristics | 9  |

| Terminology                         | 12 |

| Test Circuits                       | 13 |

| Applications Information            | 15 |

| Outline Dimensions                  | 17 |

| Ordering Guide                      | 18 |

| Product Order Model                 | 18 |

| Related Parts                       | 19 |

## Revision History (Release B) 1

Jan. 2025 — Release B

**English Version**

Added TSSOP-16 Pin Configuration, Terminology and Test Circuits

Updated Specifications, Ordering Guide, Product Order Model and Related Parts

Sep. 2024

Updated Specifications, Ordering Guide, Product Order Model and Related Parts

Apr. 2024 — Release A

Mar. 2023 — Initial

the pro

Information furnished by ZJW Microelectronics is believed to be accurate and reliable. However, no responsibility is assumed by ZJW Microelectronics for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of ZJW Microelectronics. Trademarks and registered trademarks are the property of their respective owners.

# **Pin Configuration and Function Description**

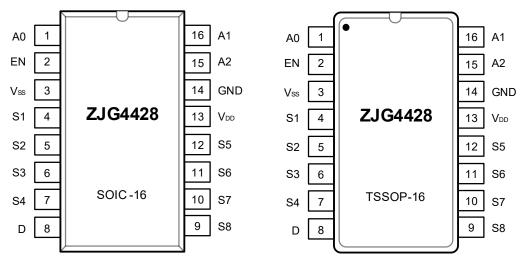

Figure 1. ZJG4428 Pin Configuration (SOIC-16 & TSSOP-16)

| Mnemonic | Pin No. | Description                                                                                                                              |  |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| A0       | 1       | Logic Control Input LSB.                                                                                                                 |  |

| EN       | 2       | Active High Digital Input. When low, the device is disabled, and all switches are off. When high, Ax logic inputs determine on switches. |  |

| Vss      | 3       | Most Negative Power Supply Potential. In single-supply applications, this pin can be connected to ground.                                |  |

| S1       | 4       | Source Terminal 1. This pin can be an input or an output.                                                                                |  |

| S2       | 5       | Source Terminal 2. This pin can be an input or an output.                                                                                |  |

| S3       | 6       | Source Terminal 3. This pin can be an input or an output.                                                                                |  |

| S4       | 7       | Source Terminal 4. This pin can be an input or an output.                                                                                |  |

| D        | 8       | Drain Terminal. This pin can be an input or an output.                                                                                   |  |

| S8       | 9       | Source Terminal 8. This pin can be an input or an output.                                                                                |  |

| S7       | 10      | Source Terminal 7. This pin can be an input or an output.                                                                                |  |

| S6       | 11      | Source Terminal 6. This pin can be an input or an output.                                                                                |  |

| S5       | 12      | Source Terminal 5. This pin can be an input or an output.                                                                                |  |

| $V_{DD}$ | 13      | ost Positive Power Supply Potential.                                                                                                     |  |

| GND      | 14      | round (0 V) Reference.                                                                                                                   |  |

| A2       | 15      | ogic Control Input MSB.                                                                                                                  |  |

| A1       | 16      | Logic Control Input.                                                                                                                     |  |

### **ZJG4428 Truth Table**

| A2 | A1 | A0 | EN | On Switch |

|----|----|----|----|-----------|

| Х  | X  | Х  | 0  | None      |

| 0  | 0  | 0  | 1  | 1         |

| 0  | 0  | 1  | 1  | 2         |

| 0  | 1  | 0  | 1  | 3         |

| 0  | 1  | 1  | 1  | 4         |

| 1  | 0  | 0  | 1  | 5         |

| 1  | 0  | 1  | 1  | 6         |

| 1  | 1  | 0  | 1  | 7         |

| 1  | 1  | 1  | 1  | 8         |

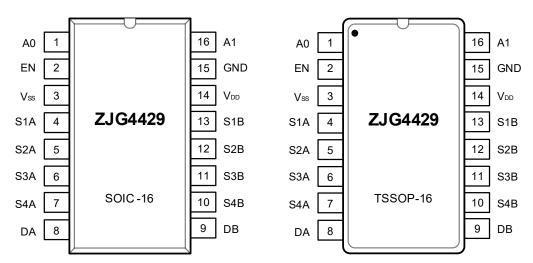

Figure 2. ZJG4429 Pin Configuration (SOIC-16 & TSSOP-16)

| Mnemonic | Pin No. | Description                                                                                                                              |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------|

| A0       | 1       | Logic Control Input LSB.                                                                                                                 |

| EN       | 2       | Active High Digital Input. When low, the device is disabled, and all switches are off. When high, Ax logic inputs determine on switches. |

| Vss      | 3       | Most Negative Power Supply Potential. In single-supply applications, this pin can be connected to ground.                                |

| S1A      | 4       | Source Terminal 1A. This pin can be an input or an output.                                                                               |

| S2A      | 5       | Source Terminal 2A. This pin can be an input or an output.                                                                               |

| S3A      | 6       | Source Terminal 3A. This pin can be an input or an output.                                                                               |

| S4A      | 7       | Source Terminal 4A. This pin can be an input or an output.                                                                               |

| DA       | 8       | Drain Terminal A. This pin can be an input or an output.                                                                                 |

| DB       | 9       | Drain Terminal B. This pin can be an input or an output.                                                                                 |

| S4B      | 10      | Source Terminal 4B. This pin can be an input or an output.                                                                               |

| S3B      | 11      | Source Terminal 3B. This pin can be an input or an output.                                                                               |

| S2B      | 12      | Source Terminal 2B. This pin can be an input or an output.                                                                               |

| S1B      | 13      | Source Terminal 1B. This pin can be an input or an output.                                                                               |

| $V_{DD}$ | 14      | Most Positive Power Supply Potential.                                                                                                    |

| GND      | 15      | Ground (0 V) Reference.                                                                                                                  |

| A1       | 16      | Logic Control Input MSB.                                                                                                                 |

### **ZJG4429 Truth Table**

| A1 | A0 | EN | On Switch Pair |

|----|----|----|----------------|

| X  | X  | 0  | None           |

| 0  | 0  | 1  | 1              |

| 0  | 1  | 1  | 2              |

| 1  | 0  | 1  | 3              |

| 1  | 1  | 1  | 4              |

ZJG4428/ZJG4429 **Data Sheet**

## **Absolute Maximum Ratings 1**

| Parameter                                                     | Rating                                   |

|---------------------------------------------------------------|------------------------------------------|

| Supply Voltage                                                | 40 V                                     |

| Input Voltage                                                 | $V_{SS}$ - 0.5 $V \sim V_{DD}$ + 0.5 $V$ |

| Continuous Current, S or D                                    | 20 mA                                    |

| Peak Current, S or D (Pulsed at 1 ms, 10% Duty Cycle Maximum) | 40 mA                                    |

| Operating Temperature Range                                   | -40 °C to 125 °C                         |

| Storage Temperature Range                                     | -65 °C to 150 °C                         |

| Junction Temperature                                          | -65 °C to 150 °C                         |

| Maximum Reflow Temperature 2                                  | 260 °C                                   |

| Lead Temperature, Soldering (10 sec)                          | 300 °C                                   |

| Electrostatic Discharge (ESD) 3                               |                                          |

| Human Body Model (HBM) 4                                      | 8 kV                                     |

| Charged Device Model (CDM) 5                                  | 2 kV                                     |

### Thermal Resistance 6

| Package Type | θ <sub>JA</sub> | θυς  | Unit |

|--------------|-----------------|------|------|

| SOIC-16      | 94              | 23.5 | °C/W |

| TSSOP-16     | 104             | 60   | °C/W |

These ratings apply at 25 °C, unless otherwise noted. Note that stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

IPC/JEDEC J-STD-020 Compliant.

Charged devices and circuit boards can discharge without detection.

Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>5</sup> ANSI/ESDA/JEDEC JS-002 Compliant.

$<sup>^{\</sup>rm 6}$   $\,$   $\theta_{JA}$  addresses the conditions for soldering devices onto circuit boards to achieve surface mount packaging.

<sup>&</sup>lt;sup>4</sup> ANSI/ESDA/JEDEC JS-001 Compliant.

# **Specifications**

The  $\bullet$  denotes the specification which apply over the specified temperature range, otherwise specifications are at  $V_{DD}$  = 15 V  $\pm$  10%,  $V_{SS}$  = -15 V  $\pm$  10%,  $V_{DD}$  = 0 V,  $V_{A}$  = 25 °C.

| Parameter                            | Symbol                             | Conditions                                                                                                                                                                  |   | Min.         | Тур.                  | Max.         | Unit     |

|--------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|-----------------------|--------------|----------|

| ANALOG SWITCH                        |                                    |                                                                                                                                                                             |   |              |                       |              |          |

| Analog Signal High                   |                                    |                                                                                                                                                                             |   |              | V <sub>DD</sub> - 1.4 |              | V        |

| Analog Signal Low                    |                                    | Output open circuit                                                                                                                                                         |   |              | V <sub>SS</sub> + 1.4 |              | ٧        |

| Analog Signal High                   |                                    |                                                                                                                                                                             |   |              | V <sub>DD</sub> - 2.2 |              | ٧        |

| Analog Signal Low                    |                                    | Output loaded, 1 mA                                                                                                                                                         |   |              | V <sub>SS</sub> + 2.2 |              | V        |

|                                      | _                                  | $-10 \text{ V} \le \text{V}_{\text{S}} \le +10 \text{ V}, \text{ I}_{\text{S}} = 1 \text{ mA}, \text{ V}_{\text{DD}} = 15 \text{ V}, \text{ V}_{\text{SS}} = -15 \text{ V}$ | • |              | 270                   | 530          | Ω        |

| On Resistance                        | Ron                                | -40 °C < T <sub>A</sub> < 85 °C                                                                                                                                             |   |              |                       | 430          | Ω        |

|                                      |                                    | $-10 \text{ V} \le \text{V}_{\text{S}} \le +10 \text{ V}, \text{ I}_{\text{S}} = 1 \text{ mA}, \text{ V}_{\text{DD}} = 15 \text{ V}, \text{ V}_{\text{SS}} = -15 \text{ V}$ |   |              | 5                     | 7            | %        |

| On-Resistance Flatness               | R <sub>FLAT(ON)</sub>              | 10 4 - 45 - 110 4, 15 - 111114, 400 - 10 4, 455 - 10 4                                                                                                                      | • |              |                       | 10           | %        |

|                                      |                                    | -40 °C < T <sub>A</sub> < 85 °C                                                                                                                                             |   |              |                       | 10           | %        |

| On-Resistance Match Between Channels | $\Delta R_{ON}$                    | $V_S = \pm 10 \text{ V}, I_S = 1 \text{ mA}$                                                                                                                                | • |              | 0.5                   | 3            | %        |

| LEAKAGE CURRENTS                     |                                    |                                                                                                                                                                             |   |              | l                     |              |          |

| 0 0"1 1                              | 1 (25)                             | V <sub>S</sub> = ±10 V, V <sub>D</sub> = ∓10 V                                                                                                                              |   | -0.5         | ±0.01                 | +0.5         | nA       |

| Source Off Leakage                   | I <sub>S</sub> (Off)               | 40.00 aT +05.00                                                                                                                                                             | • | -4           |                       | +4           | nA       |

|                                      |                                    | -40 °C < T <sub>A</sub> < 85 °C                                                                                                                                             |   | -1           | . 0.04                | 1            | nA       |

| Drain Off Leakage                    | I <sub>D</sub> (Off)               | $V_S = \pm 10 \text{ V}, V_D = \mp 10 \text{ V}$                                                                                                                            | • | -0.5<br>-0.2 | ±0.01                 | +0.5<br>+0.2 | nA<br>µA |

| 3                                    |                                    | -40 °C < T <sub>A</sub> < 85 °C                                                                                                                                             |   | -4           |                       | 4            | nA       |

|                                      |                                    |                                                                                                                                                                             |   | -0.5         | ±0.01                 | +0.5         | nA       |

| Channel On Leakage                   | $I_D,I_S(ON)$                      | $V_S = V_D = \pm 10 \text{ V}$                                                                                                                                              | • | -0.2         |                       | +0.2         | μΑ       |

|                                      |                                    | -40 °C < T <sub>A</sub> < 85 °C                                                                                                                                             |   | -4           |                       | 4            | nA       |

| DIGITAL INPUTS                       |                                    |                                                                                                                                                                             |   |              |                       |              |          |

| Input High Voltage                   | V <sub>INH</sub>                   |                                                                                                                                                                             | • | 2.4          |                       |              | V        |

| Input Low Voltage                    | $V_{INL}$                          |                                                                                                                                                                             | • |              |                       | 0.8          | ٧        |

| Input Current                        | I <sub>INL</sub> /I <sub>INH</sub> | V <sub>EN</sub> = 0 V or V <sub>DD</sub>                                                                                                                                    | • |              |                       | 1            | μΑ       |

| DYNAMIC CHARACTERIS                  | TICS 1                             |                                                                                                                                                                             |   |              |                       |              |          |

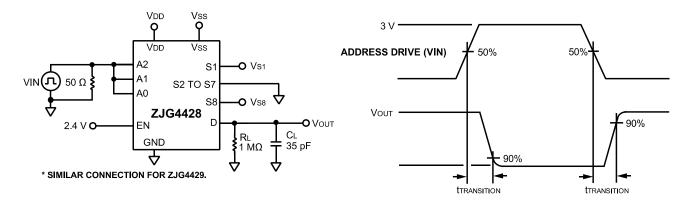

| t <sub>TRANSITION</sub>              |                                    | $R_L$ = 1 M $\Omega$ , $C_L$ = 35 pF, $V_{S1}$ = ±10 V, $V_{S8}$ = ±10 V                                                                                                    | • |              | 168                   | 320          | ns       |

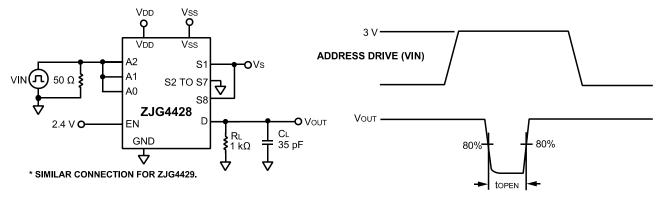

| topen                                |                                    | $R_L = 1 \text{ K}\Omega, C_L = 35 \text{ pF}, V_S = 5 \text{ V}$                                                                                                           |   | 50           | 139                   |              | ns       |

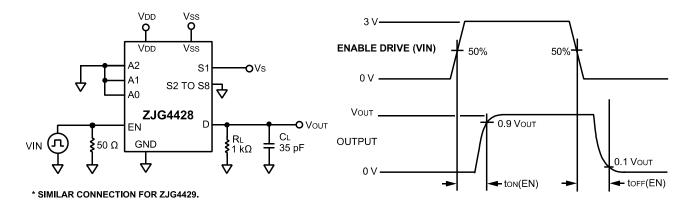

| t <sub>ON</sub>                      |                                    | $R_L = 1 \text{ k}\Omega, C_L = 35 \text{ pF}, V_S = 5 \text{ V}$                                                                                                           | • |              | 166                   | 330          | ns       |

| t <sub>OFF</sub>                     |                                    | $R_L = 1 \text{ k}\Omega, C_L = 35 \text{ pF}, V_S = 5 \text{ V}$                                                                                                           | • |              | 135                   | 170          | ns       |

| Settling Time                        |                                    | $t_{SETT}$ 0.1%, $R_L$ = 1 k $\Omega$ , $C_L$ = 35 pF, $V_S$ = 5 V                                                                                                          |   |              | 0.25                  |              | μs       |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design, not subject to production test.

ZJG4428/ZJG4429 Data Sheet

| Charge Injection                          | $V_S = 0 \text{ V, } R_S = 0  \Omega, C_L = 1 \text{ nF}$                                          |   |      | рС   |             |          |

|-------------------------------------------|----------------------------------------------------------------------------------------------------|---|------|------|-------------|----------|

| Off Isolation                             | $R_L = 1 \text{ k}\Omega$ , $C_L = 15 \text{ pF}$ , $f = 100 \text{ kHz}$ , $V_S = 7 \text{ Vrms}$ |   |      | dB   |             |          |

| Channel-to-Channel<br>Crosstalk           |                                                                                                    |   | -104 |      | dB          |          |

| C <sub>S</sub> (Off)                      |                                                                                                    |   |      | 2.6  |             | pF       |

| 0 (00)                                    | ZJG4428                                                                                            |   |      | 5.8  |             | pF       |

| C <sub>D</sub> (Off)                      | ZJG4429                                                                                            |   |      | 3.2  |             | pF       |

| POWER SUPPLY                              |                                                                                                    |   |      |      |             |          |

| I <sub>DD_ON</sub> , Iss_on               | V <sub>DD</sub> = 15 V, V <sub>SS</sub> = -15 V, V <sub>EN</sub> = 2.4 V                           | • |      | 0.07 | 0.15<br>0.2 | mA<br>mA |

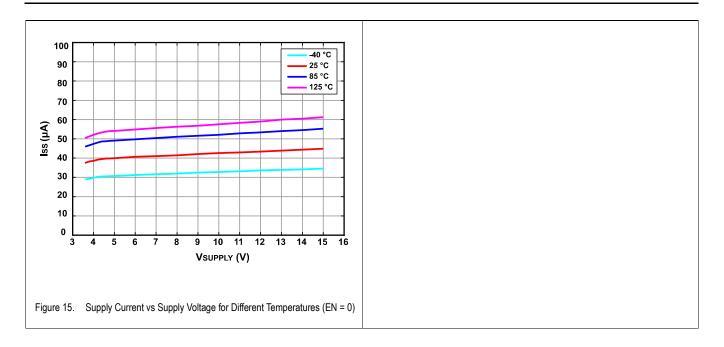

| I <sub>DD_OFF</sub> , I <sub>SS_OFF</sub> | V <sub>DD</sub> = 15 V, V <sub>SS</sub> = -15 V, V <sub>EN</sub> = 0.8 V                           | • |      | 0.05 | 0.15<br>0.2 | mA<br>mA |

| Power Supply Range                        |                                                                                                    |   | ±5   |      | ±18         | V        |

| TEMPERATURE RANGE                         | ·                                                                                                  |   |      |      | •           |          |

| Specified                                 |                                                                                                    |   | -40  |      | 125         | °C       |

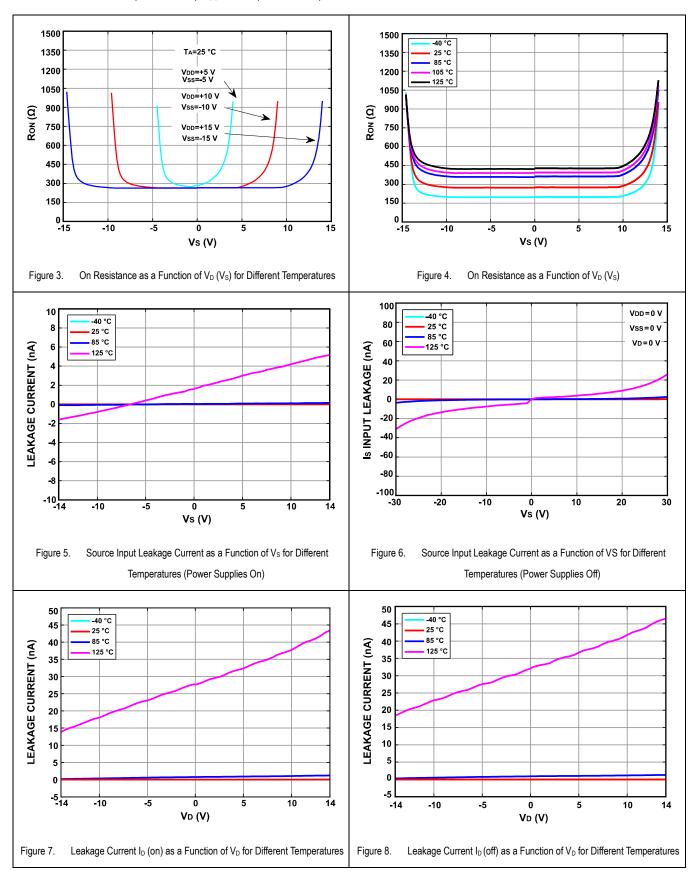

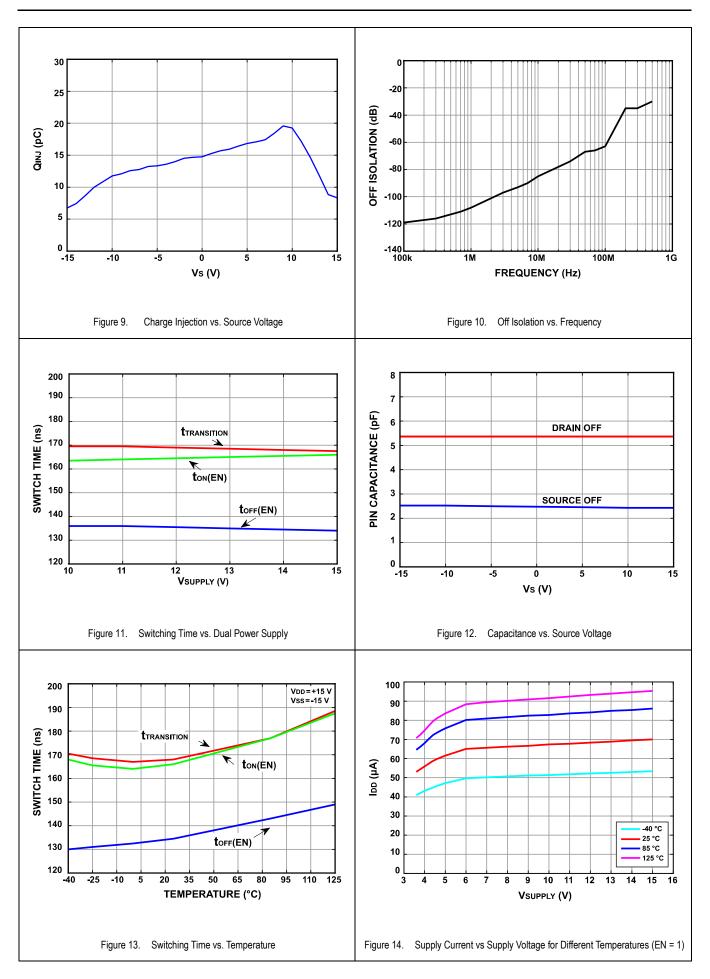

## **Typical Performance Characteristics**

Unless otherwise stated,  $V_{DD}$  = 15 V,  $V_{SS}$  = -15 V, GND = 0 V,  $T_A$  = 25 °C.

### **Terminology**

#### $V_{DD}$

Most positive power supply potential.

#### $V_{SS}$

Most negative power supply potential.

#### **GND**

Ground (0 V) reference.

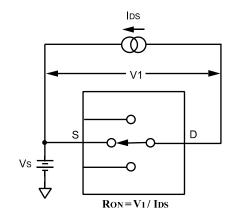

#### RON

Ohmic resistance between D and S.

#### $\Delta R_{ON}$

$\Delta R_{ON}$  represents the difference between the  $R_{ON}$  of any two channels as a percentage of the maximum  $R_{ON}$  of those two channels.

#### R<sub>FLAT</sub> (ON)

Flatness is defined as the difference between the maximum and minimum value of the on resistance measured over the specified analog signal range and is represented by R<sub>FLAT (ON)</sub>.

Flatness is calculated by

$$((R_{MAX} - R_{MIN})/R_{MAX} \times 100)$$

### **Ron Drift**

Change in  $R_{\text{ON}}$  when temperature changes by one degree Celsius.

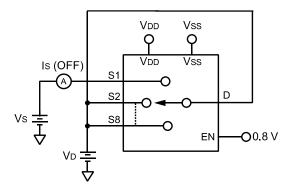

### Is (Off)

Source leakage current when the switch is off.

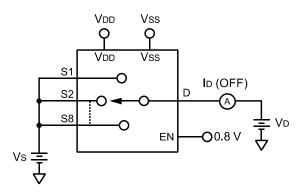

#### In (Off

Drain leakage current when the switch is off.

### I<sub>D</sub>, I<sub>S</sub> (On)

Channel leakage current when the switch is on.

### $V_D(V_S)$

Analog voltage on Terminal D and Terminal S.

### Is (Fault—Power Supplies On)

Source leakage current when exposed to an overvoltage condition.

### I<sub>D</sub> (Fault—Power Supplies On)

Drain leakage current when exposed to an overvoltage condition.

### Is (Fault—Power Supplies Off)

Source leakage current with power supplies off.

### Cs (Off)

Channel input capacitance for off condition.

### C<sub>D</sub> (Off)

Channel output capacitance for off condition.

### C<sub>D</sub>, C<sub>S</sub> (On)

On switch capacitance.

### $C_{\text{IN}}$

Digital input capacitance.

### ton (EN)

Delay time between the 50% and 90% points of the digital input and switch on condition.

### toff (EN)

Delay time between the 50% and 90% points of the digital input and switch off condition.

#### **t**TRANSITION

Delay time between the 50% and 90% points of the digital inputs and the switch on condition when switching from one address state to another.

### **t**OPEN

Off time measured between 80% points of both switches when switching from one address state to another.

### $V_{INL}$

Maximum input voltage for Logic 0.

#### VINE

Minimum input voltage for Logic 1.

#### I<sub>INL</sub> (I<sub>INH</sub>)

Input current of the digital input.

### **Off Isolation**

A measure of unwanted signal coupling through an off channel.

### **Charge Injection**

A measure of the glitch impulse transferred from the digital input to the analog output during switching.

#### $I_{DD}$

Positive supply current.

### Iss

Negative supply current.

### **Test Circuits**

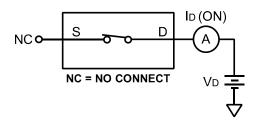

Figure 16. On Resistance

Figure 17. Is (Off)

Figure 18. I<sub>D</sub> (Off)

Figure 19. I<sub>D</sub> (On)

Figure 20. Input Leakage Current (with Overvoltage)

Figure 21. Input Leakage Current (with Power Supplies Off)

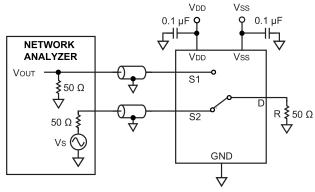

Figure 22. Off Isolation

$\label{eq:channel_crosstalk} \text{Channel crosstalk} = 20 \log \frac{\text{Vout}}{\text{Vs}}$

Figure 23. Channel-to-Channel Crosstalk

Figure 24. Switching Time of Multiplexer, trransition

Figure 25. Break-Before-Make Delay, topen

Figure 26. Enable Delay, ton (EN), toff (EN)

Figure 27. Charge Injection

### **Applications Information**

The ZJG4428 and ZJG4429 are 36 V precision high-voltage multiplexers designed to switch among multiple high-voltage signals. A latch-up happens at the system's front end can lead to severe consequences, often requires a full system reset or causes hardware damage. ZJG4428 and ZJG4429 mitigate this risk by ensuring that all pins—including input, output, and logic control pins—are inherently latch-up free. This key feature simplifies system design and maintenance while enhancing overall system reliability.

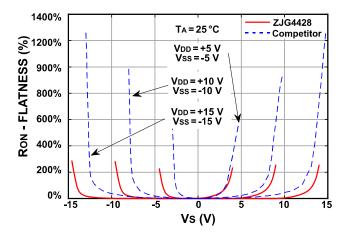

On-resistance (Ron) is a key parameter for analog switches and multiplexers. ZJG4428 offers a typical Ron of 270  $\Omega$ . Unlike many high-voltage analog switches and multiplexers, where Ron can significantly increase as the signal approaches the power rails, ZJG4428 exhibits superior Ron flatness over a wider voltage range, as shown in Figure 28. Powered by  $\pm 15$  V with a  $\pm 10$  V input voltage, the ZJG4428 exhibits a typical flatness of 5% and a maximum flatness of 7% at room temperature. In the extended industrial temperature range (-40 °C to 125 °C), the maximum flatness remains within 10%. This characteristic makes them ideal for high-precision data acquisition systems requiring 16-bit or greater accuracy.

Figure 28. ZJG4428 On Resistance vs. Input Voltage

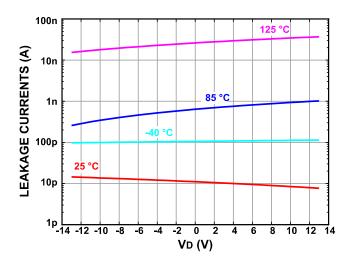

Leakage current when the switch is on is a critical DC specification for analog switches and multiplexers, as it decides system accuracy. Higher leakage current leads to increased measurement error, making the device less suitable for precision data acquisition systems. ZJG4428 exhibits excellent leakage current characteristics, as illustrated in Figure 29. When powered by  $\pm 15$  V with a  $\pm 10$  V input, they achieve a leakage current of 10 pA at room temperature. Over the temperature range of -40 °C to 85 °C, the leakage current remains below 4 nA, and even at -40 °C to 125 °C, it stays within 200 nA. These low leakage currents make them ideal for 14-bit or greater data acquisition systems.

Figure 29. ZJG4428 Leakage Current when Turned On

ZJG4428/ZJG4429 Data Sheet

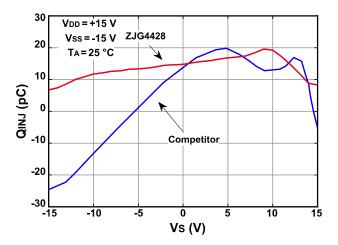

Charge injection, which occurs during switching, can interfere with input signals and degrade system linearity. As shown in Figure 30, ZJG4428 exhibits a lower charge injection of 14.8 pC and maintains superior flatness across the entire input range compared to competing parts.

Figure 30.  $\,$  ZJG4428 Charge Injection vs. Source Voltage  $V_S$

ZJG4428 and ZJG4429 offer fast switching times of 166 ns  $t_{ON}$  and 135 ns  $t_{OFF}$ . They are in break-before-make construction and the crosstalk between channels is just 104 dB. In the off state, they exhibit low input capacitance  $C_S$  of 2.6 pF and output capacitance  $C_D$  of 5.8 pF for ZJG4438 and 3.2 pF for ZJG4439. Their CMOS and TTL-compatible parallel interfaces simplify integration and ease of use.

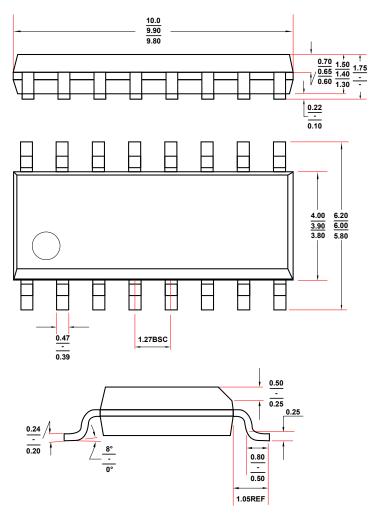

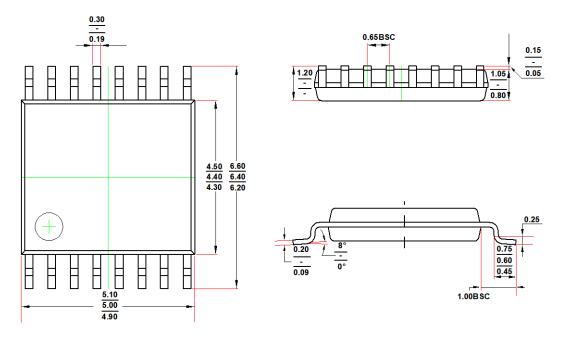

### **Outline Dimensions**

Figure 31. 16-Lead SOIC Package Dimensions Shown in Millimeters

Figure 32. 16-Lead TSSOP Package Dimensions Shown in Millimeters

# **Ordering Guide**

| Model   | Orderable Device | Function         | Temperature Range (°C) | Package     | External Package |          |

|---------|------------------|------------------|------------------------|-------------|------------------|----------|

|         | ZJG4428ASEBT     |                  |                        |             | Tube             |          |

| ZJG4428 | ZJG4428ASEBR     | 8:1 Multiplexer  |                        | SOIC-16     | 13" Reel         |          |

| ZJG4420 | ZJG4428AUEBT     |                  | o. i wullipiexer       | -40 to +125 | TSSOP-16         | Tube     |

|         | ZJG4428AUEBR     |                  |                        | TSSOP-16    | 13" Reel         |          |

|         | ZJG4429ASEBT     | 4:1 Differential |                        | SOIC-16     | Tube             |          |

| 7104400 | ZJG4429ASEBR     |                  | 4:1 Differential       | 40 to 105   | SOIC-16          | 13" Reel |

| ZJG4429 | ZJG4429AUEBT Mul | Multiplexer      | -40 to +125            | TSSOP-16    | Tube             |          |

|         | ZJG4429AUEBR     |                  |                        | TSSOP-16    | 13" Reel         |          |

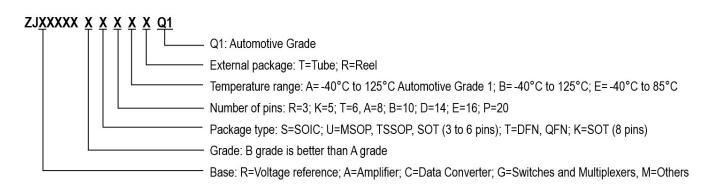

### **Product Order Model**

## **Related Parts**

| Part Number                  | Description                                                                                                          | Comments                                                                                                 |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|

| ADC                          | L                                                                                                                    | L                                                                                                        |  |  |

| ZJC2020                      | 20-bit 350 kSPS SAR ADC                                                                                              | Fully differential input, SINAD 101.4 dB, THD -118 dB                                                    |  |  |

| ZJC2000/2010                 | 18-bit 400 kSPS/200 kSPS SAR ADC                                                                                     | Fully differential input, SINAD 99.3 dB, THD -113 dB                                                     |  |  |

| ZJC2001/2011                 | 16-bit 500 kSPS/250 kSPS SAR ADC                                                                                     | Fully differential input, SINAD 95.3 dB, THD -113 dB                                                     |  |  |

| ZJC2002/2012                 | 40 1 % 500 1 0 0 0 10 50 1 0 0 0 0 0 0 0 0 0 0                                                                       | Pseudo-differential unipolar input, SINAD 91.7 dB, THD -105 dB                                           |  |  |

| ZJC2003/2013                 | 16-bit 500 kSPS/250 kSPS SAR ADC                                                                                     | Pseudo-differential bipolar input, SINAD 91.7 dB, THD -105 dB                                            |  |  |

| ZJC2004/2014                 | <br>  18-bit 400 kSPS/200 kSPS SAR ADC                                                                               | Pseudo-differential unipolar input, SINAD 94.2 dB, THD -105 dB                                           |  |  |

| ZJC2005/2015                 | TO BIL 400 KOT 0/200 KOT 0 0/K/ND0                                                                                   | Pseudo-differential bipolar input, SINAD 94.2 dB, THD -105 dB                                            |  |  |

| ZJC2007/2017                 | 14-bit 600 kSPS/300 kSPS SAR ADC                                                                                     | Pseudo-differential unipolar input, SINAD 85 dB, THD -105 dB                                             |  |  |

| ZJC2008/2018<br>ZJC2009      | Small size, 12-bit 1 MSPS SAR ADC                                                                                    | Pseudo-differential bipolar input, SINAD 85 dB, THD -105 dB                                              |  |  |

| ZJC2009<br>ZJC2100/1-18      |                                                                                                                      | Single-ended input, SOT23-6, 2.3 V to 5 V, SINAD 73 dB, THD -89 dB                                       |  |  |

| ZJC2100/1-16<br>ZJC2100/1-16 | 18-bit 400 kSPS/200 kSPS 4-ch differential SAR ADC, SINA<br>16-bit 500 kSPS/250 kSPS 4-ch differential SAR ADC, SINA |                                                                                                          |  |  |

| ZJC2102/3-18                 | 18-bit 400 kSPS/200 kSPS 8-ch pseudo-differential SAR AD                                                             |                                                                                                          |  |  |

| ZJC2102/3-16                 | 16-bit 500 kSPS/250 kSPS 8-ch pseudo-differential SAR AD                                                             | C, SINAD 91.7 dB, THD -105 dB                                                                            |  |  |

| ZJC2102/3-14                 | 14-bit 600 kSPS/300 kSPS 8-ch pseudo-differential SAR AD                                                             | C, SINAD 85 dB, THD -105 dB                                                                              |  |  |

| ZJC2104/5-18                 | 18-bit 400 kSPS/200 kSPS 4-ch pseudo-differential SAR AD                                                             |                                                                                                          |  |  |

| ZJC2104/5-16                 | 16-bit 500 kSPS/250 kSPS 4-ch pseudo-differential SAR AD                                                             | C, SINAD 91.7 dB, THD -105 dB                                                                            |  |  |

| DAC                          |                                                                                                                      |                                                                                                          |  |  |

| ZJC2541-18/16/14             | 18/16/14-bit 1 MSPS single channel DAC with                                                                          | Power on reset to 0 V (ZJC2541) or V <sub>REF</sub> /2 (ZJC2543), 1 nV-S glitch, SOIC-8, MSOP-10/8,      |  |  |

| ZJC2543-18/16/14             | unipolar output                                                                                                      | DFN-10 packages                                                                                          |  |  |

| ZJC2542-18/16/14             | 18/16/14-bit 1 MSPS single channel DAC with                                                                          | Power on reset to 0 V (ZJC2542) or V <sub>REF</sub> /2 (ZJC2544), 1 nV-S glitch, SOIC-14, TSSOP-16,      |  |  |

| ZJC2544-18/16/14             | bipolar output                                                                                                       | QFN-16 packages                                                                                          |  |  |

| Amplifier                    |                                                                                                                      |                                                                                                          |  |  |

| ZJA3000-1/2/4                | Single/Dual/Quad 36 V low bias current precision                                                                     | 3 MHz, 35 μV max Vos, 0.5 μV/°C max TCVos, 25 pA max Ibias, 1 mA/ch, input to V-                         |  |  |

| ZJA3001-1/2/4                | Op Amps                                                                                                              | (ZJA3000 only), RRO, 4.5 V to 36 V                                                                       |  |  |

| ZJA3018-2                    | OVP ±75 V, 36 V, Low Power, High Precision Op Amp                                                                    | 1.3 MHz, 10 $\mu$ V max Vos, 0.5 $\mu$ V/°C max TCVos, 25 pA max Ibias, 0.5 mA/ch, OVP ±75 V             |  |  |

| ZJA3008-2                    | 36 V, Low Power, High Precision Op Amp                                                                               | (ZJA3018 only), RRO, 4.5 V to 36 V                                                                       |  |  |

| ZJA3512-2                    | Dual 36 V 7 MHz precision JFET Op Amps                                                                               | 7 MHz, 35 V/μS, 50 μV max Vos, 1 μV/°C max TCVos, 2 mA/ch, RRO, 9 V to 36 V                              |  |  |

| ZJA3206/06/02-1/2            | Precision 24/11.6/5.3 MHz CMOS RRIO Op Amps                                                                          | 24/11.6/5.3 MHz, RRIO, 30 μV max Vos, 1 μV/°C max TCVos, 0.6 pA lb, 2.7 V to 5.5 V                       |  |  |

|                              |                                                                                                                      | CMRR 105 dB min (G = 1), 25 pA max lb, 25 µV max Vosi, ±2.4 V to ±18 V,                                  |  |  |

| ZJA3600/1                    | 36 V ultra-high precision in-amp                                                                                     | -40 °C to 125 °C                                                                                         |  |  |

| ZJA3611, ZJA3609             | 36 V precision wider bandwidth precision in-amp (G≥10)                                                               | CMRR 120 dB min (G = 10), 25 pA max Ibias, 25 µV max Vosi, 1.2 MHz BW (G = 10)                           |  |  |

| ZJA3676/7                    | Low power, G = 1 Single/Dual 36 V difference amplifier                                                               | Input protection to ±65 V, CMRR 104 dB min (G = 1), Vos 100 μV max, gain error 15 ppm                    |  |  |

| ZJA3678/9                    | Low power, G = 0.5/2 Single/Dual 36 V difference amplifier                                                           | max, 500 kHz BW (G = 1), 330 μA/channel, 2.7 V to 36 V                                                   |  |  |

| ZJA3669                      | High Common-Mode Voltage Difference Amplifier                                                                        | ±270 V CMV, 2.5 kV ESD, 96 dB min CMRR, 450 kHz BW, 4 V to 36 V, SOIC-8                                  |  |  |

| ZJA3100                      | 15 V precision fully differential amplifier                                                                          | 145 MHz, 447 V/μS, 50 nS to 16-bit, 50 μV max Vos, 4.6 mA lq, SOIC/MSOP-8, QFN-16                        |  |  |

| ZJA3236/26/22-2              | Low-cost 22/10/5 MHz CMOS RRIO Op Amps                                                                               | 22/11/5 MHz, RRIO, 2 mV max Vos, 6 µV/°C max TCVos, 0.6 pA lb, 2.7 V to 5.5 V                            |  |  |

| ZJA3622/8                    | 36 V low-cost precision in-amp                                                                                       | 0.5 nA max Ibias, 125 $\mu$ V max Vosi, 625 kHz BW (G = 10), 3.3 mA lq, $\pm$ 2.4 V to $\pm$ 18 V        |  |  |

| Voltage Referer              | nce                                                                                                                  |                                                                                                          |  |  |

| ZJR1004                      | 40 V supply precision voltage reference                                                                              | V <sub>OUT</sub> = 2.048/2.5/3/3.3/4.096/5/10 V, 5 ppm/°C max drift -40 °C to 125 °C                     |  |  |

| ZJR1001/2                    | 5.5 V low power voltage reference                                                                                    | V <sub>OUT</sub> = 2.048/2.5/3/3.3/4.096/5 V, 5 ppm/°C max drift -40 °C to 125 °C, ±0.05% initial error, |  |  |

| ZJR1003                      | (ZJR1001 with noise filter option)                                                                                   | 130 μA, ZJR1001/2 in SOT23-6, ZJR1003 in SOIC/MSOP-8                                                     |  |  |

| ZJR1302                      | 5.5 V low power compact precision voltage reference                                                                  | $V_{OUT}$ = 2.048/2.5/3/3.3/4.096 V, 30 ppm/°C max drift -40 °C to 125 °C, 130 $\mu$ A, SOT23-3          |  |  |

| Switches and M               | lultiplexers                                                                                                         |                                                                                                          |  |  |

| ZJG4438/4439                 | 36 V fault protection 8:1/dual 4:1 multiplexer                                                                       | Protection to ±50 V power on & off, latch-up immune, Ron 270 Ω, 14.8 pC, t <sub>ON</sub> 166 nS          |  |  |

| ZJG4428/4429                 | 36 V 8:1/dual 4:1 multiplexer                                                                                        | Latch-up immune, Ron 270 Ω, 14.8 pC charge injection, t <sub>oN</sub> 166 nS                             |  |  |

| Quad Matching                | '                                                                                                                    |                                                                                                          |  |  |

| adda materining              | 1100.0101                                                                                                            | Mismatch < 100 ppm, 10k:10k:10k:10k, 100k:100k:100k:100k, 100k:10k:10k:10k.                              |  |  |

| ZJM5400                      | ±75 V precision match resistors                                                                                      | 18:18:18:18, 1M:1M:1M:1M, 58:18:18:58, 58:1.258:1.258:58, 98:18:18:98, ESD: 3.5 kV                       |  |  |