# LT32U03

# **32Bit Micro Controller**

# 规格书

**V3.2**

## 目 录

| 目 | 录      | •••••             | 2                  |

|---|--------|-------------------|--------------------|

| 图 | 表目录    |                   | 15                 |

| 耒 | 各目录    |                   | 27                 |

| 1 | 总章     |                   | 30                 |

| 1 | -      |                   |                    |

|   |        |                   | 30                 |

|   |        | 方块图               |                    |

|   | 1.3 概述 |                   |                    |

|   | —      |                   |                    |

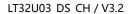

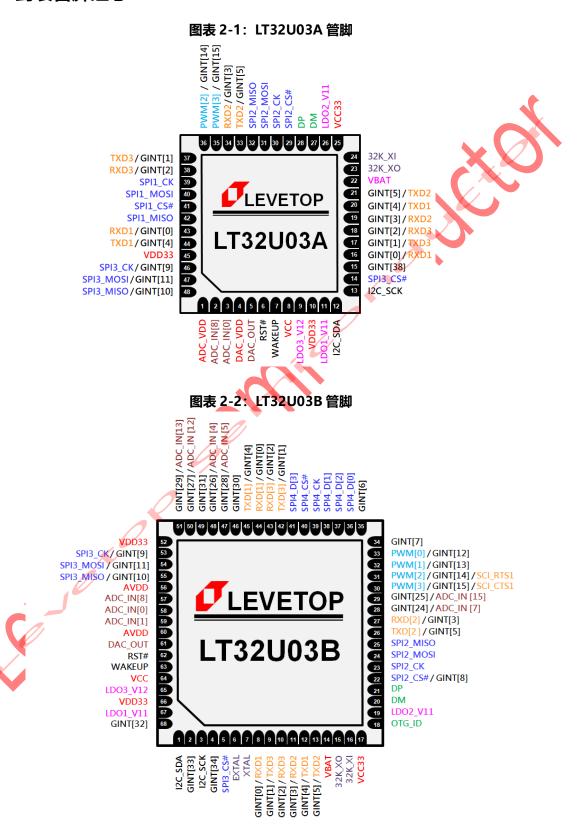

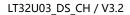

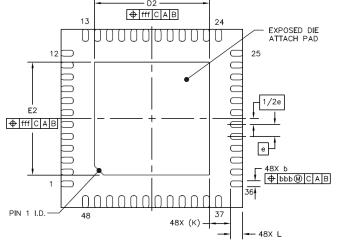

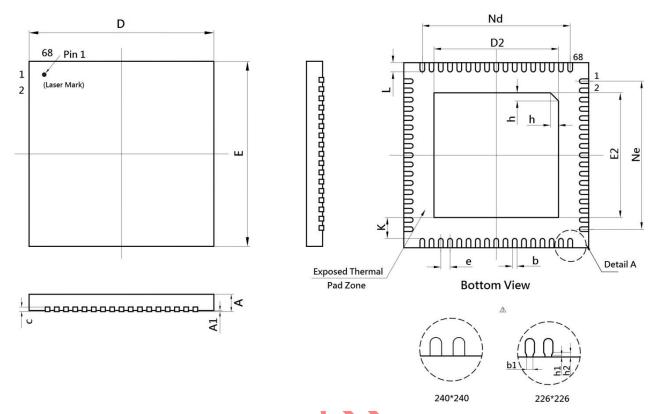

| 2 | 管脚描述   | <u>`</u>          | 38                 |

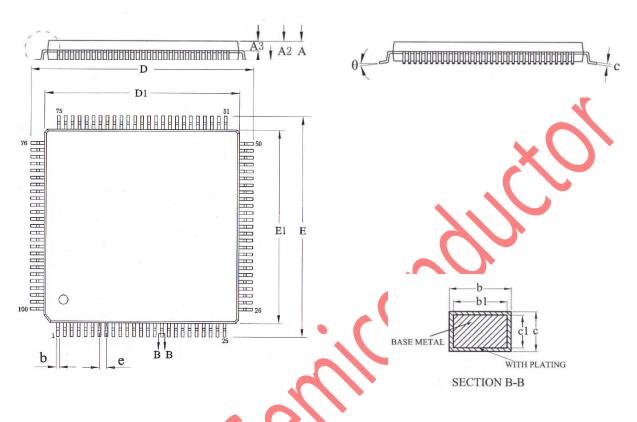

|   | 2.1 封装 | 管脚汇总              | 38                 |

|   | 2.2 管脚 | 信 <del>号</del> 说明 | 40                 |

|   | 2.2.1  | SCI / Uart 串口信号   | 40                 |

|   | 2.2.2  | I2C 控制信号          | 40                 |

|   | 2.2.3  | SPI 接口信号          | 41                 |

|   | 2.2.4  | GPIO/INT 接口信号     | 42                 |

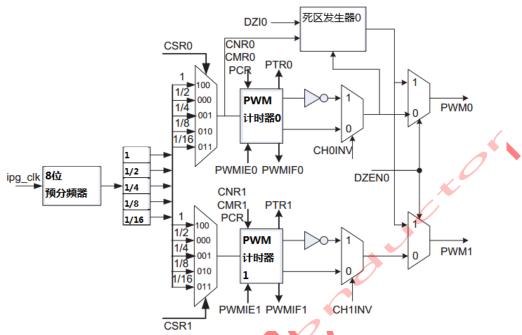

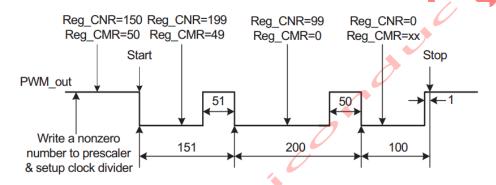

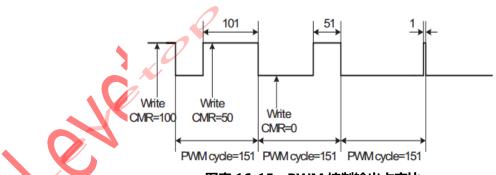

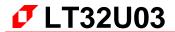

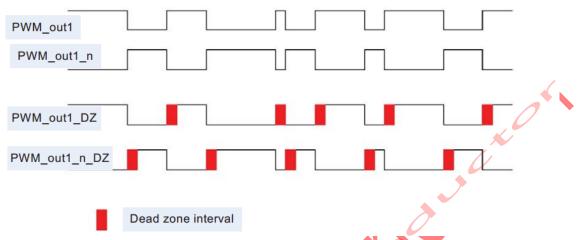

|   | 2.2.5  | PWM 控制信号          | 45                 |

|   | 2.2.6  | 模拟信号              | 45                 |

|   | 2.2.7  | USB 控制信号          | 46                 |

|   | 2.2.8  | 其他控制信号            | 47                 |

|   | 2.2.9  |                   | 47                 |

|   | 2.3 管脚 | 属性与复用功能           | 49                 |

| 3 | 系统存储   | 器映射               | 58                 |

|   | 3.1 概述 |                   | 58                 |

|   | 3.2 内存 |                   | 58                 |

| 4 | 内核配置   | i模块 (CCM)         | 62                 |

|   | 4.1 概述 |                   | 62                 |

|   |        |                   | 62                 |

|   |        |                   | 62                 |

|   | 4.3.1  |                   | 62                 |

|   | 4.3.2  |                   | 62                 |

|   |        |                   |                    |

|   | ··· 기마 |                   |                    |

|   |        | LT:               | 32U03_DS_CH / V3.2 |

|   | 4.5 内存 | 映射和寄存器               | 63  |

|---|--------|----------------------|-----|

|   | 4.5.1  | 编程模型                 | 63  |

|   | 4.5.2  | 内存映射                 | 64  |

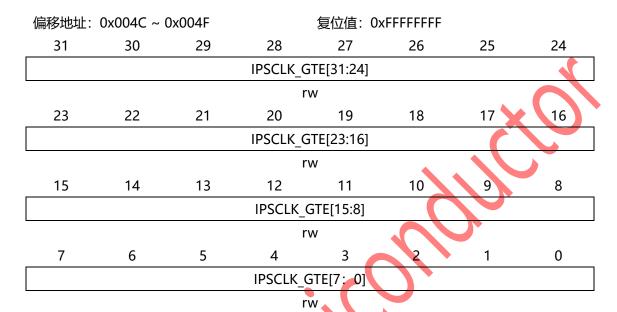

|   | 4.5.3  | 寄存器描述                | 65  |

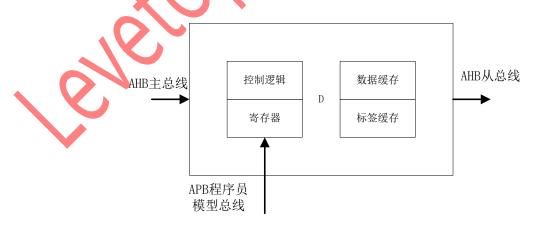

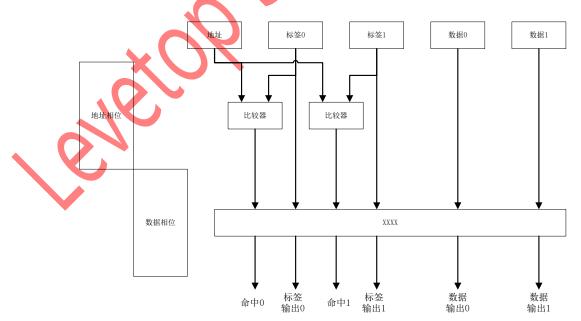

| 5 | 高速缓存   | ■模块 (Cache)          | 76  |

|   | 5.1 概述 |                      | 76  |

|   | 5.2 特性 |                      | 77  |

|   | 5.3 框图 |                      | 77  |

|   | 5.4 内存 | 映射和寄存器               | 78  |

|   | 5.4.1  | 内存映射                 | 78  |

|   | 5.4.2  | 寄存器描述                | 79  |

|   | 5.5 功能 | 描述                   | 97  |

|   | 5.5.1  | 缓存功能                 | 97  |

|   | 5.5.2  | 缓存控制                 | 98  |

|   | 5.5.3  | 缓存设置命令               |     |

|   | 5.5.4  | Cache 行命令            | 99  |

|   | 5.5.5  | 使用 Cache 地址执行一系列的行命令 | 100 |

|   | 5.5.6  | 使用物理地址执行一系列行命令       | 101 |

|   | 5.5.7  | 行命令结果                | 101 |

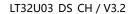

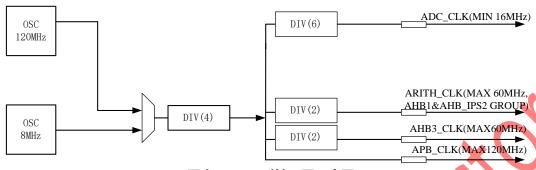

| 6 | 时钟电源   | <b>管理模块 (CPM)</b>    | 102 |

|   | 6.1 概述 |                      | 102 |

|   | 6.2 特性 |                      | 102 |

|   |        |                      |     |

|   |        | 模式                   |     |

|   | 6.4.1  | 低功耗模式操作              |     |

|   | 6.4.2  | 详细的功耗模式和唤醒源          |     |

|   | 6.5 内存 | 映射和寄存器               | 107 |

|   | 6.5.1  | 内存映射                 | 107 |

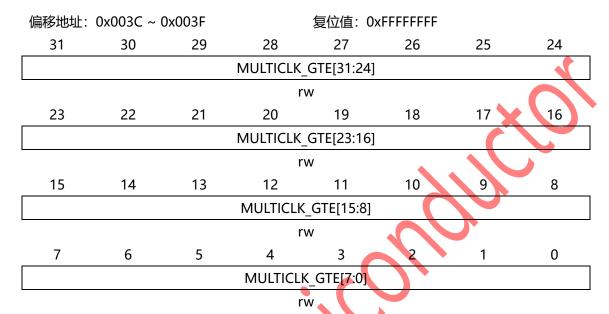

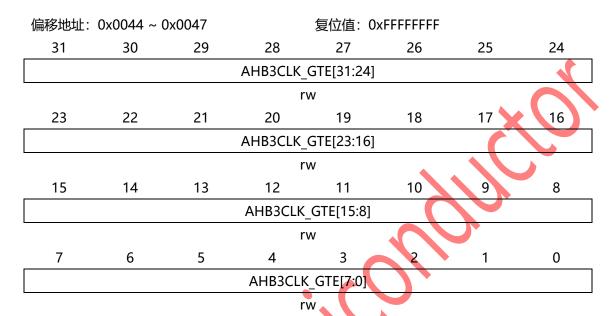

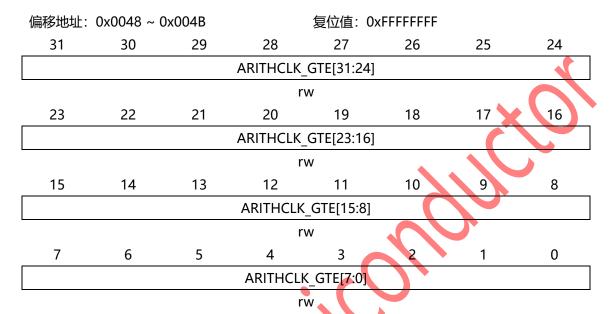

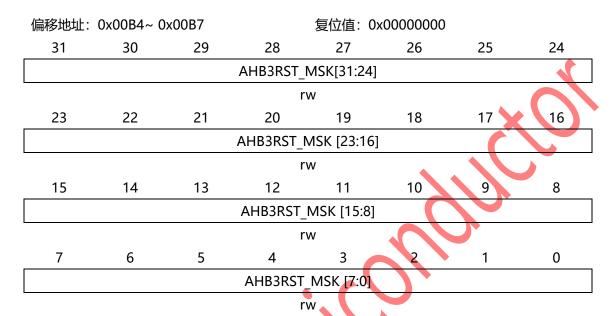

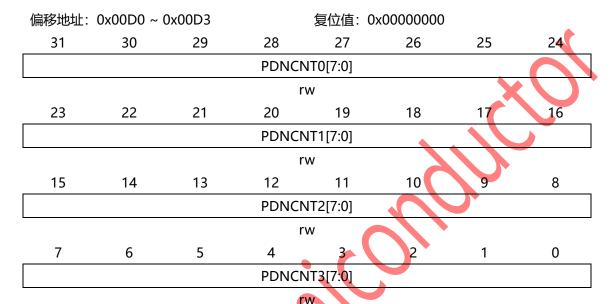

|   | 6.5.2  | 寄存器描述                | 109 |

|   | 6.6 功能 |                      | 172 |

|   | 6.6.1  | 时钟源的选择               | 172 |

|   | 6.6.2  | 系统时钟源切换配置            | 172 |

|   | 6.6.3  | 系统时钟分频配置             | 172 |

|   | 6.6.4  | 时钟源的校准               | 172 |

|   | 6.6.5  | 时钟源稳定时间配置            | 172 |

|   | 6.6.6  | 时钟配置示例               | 173 |

|   | 6.7 中断 | 描述                   | 173 |

|   | 6.7.1          | VCC_LVDT5V 中断                                        | 173 |

|---|----------------|------------------------------------------------------|-----|

|   | 6.7.2          | VCC_LVDT18V 中断                                       | 173 |

|   | 6.7.3          | 唤醒中断                                                 | 173 |

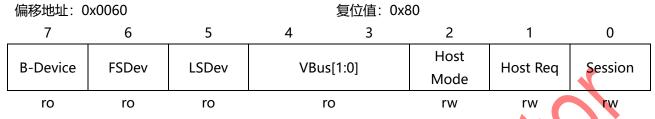

| 7 | USB2.0         | 控制器 (USB)                                            | 174 |

|   | 7.1 概述         | <u> </u>                                             | 174 |

|   | 7.2 特性         |                                                      | 174 |

|   | 7.3 系统         | 时钟                                                   | 174 |

|   | 7.4 复位         | <u> </u>                                             | 175 |

|   | 7.4.1          |                                                      | 175 |

|   | 7.4.2          | 主机模式 (Host Mode)                                     |     |

|   | 7.5 内部         | 3映射和寄存器                                              | 175 |

|   | 7.5.1          | 内存映射USBC 通用寄存器(Common Registers)                     | 176 |

|   | 7.5.2          | USBC 通用寄存器 (Common Registers)                        | 178 |

|   | 7.5.3          | USBC 索引寄存器 (Indexed Registers)                       | 191 |

|   | 7.5.4          | FIFO 寄存器 (FIFO Registers)                            | 215 |

|   | 7.5.5          | DMΔ 岑左哭 (DMΔ Registers)                              | 216 |

|   | 7.6 功能         | 描述复位 (Reset)                                         | 220 |

|   | 7.6.1          | 复位(Reset)                                            | 220 |

|   | 7.6.2          | 软连接 (Soft Connect)                                   | 220 |

|   | 7.6.3          | 帧起始包 (SOF)                                           |     |

|   | 7.6.4          | 挂起和恢复(Suspend/Resume)                                |     |

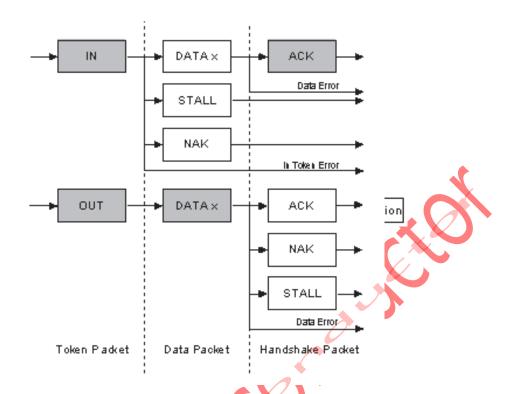

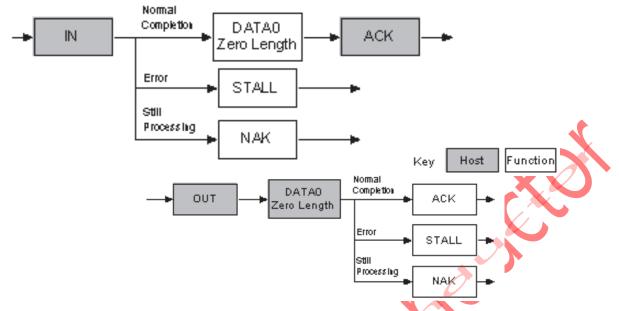

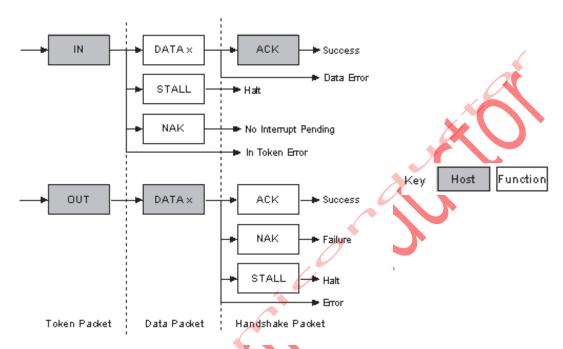

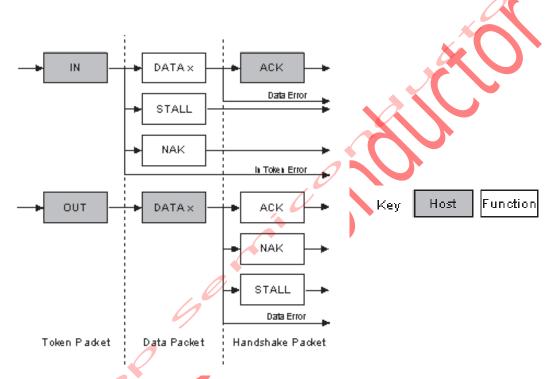

|   | 7.6.5          | IN 事务处理(In-Transaction Handling)                     |     |

|   | 7.6.6          | 发送包缓存(Transmit Packet Buffering)                     |     |

|   | 7.6.7          | OUT 事务处理(Out-Transaction Handling)                   |     |

|   | 7.6.8          | 接收包缓存(Receive Packet Buffering)                      |     |

|   | 7.6.9          | 外部参考时钟检测器(External clock reference detector)         |     |

|   |                | ·操作                                                  |     |

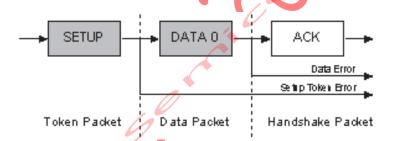

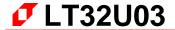

|   | 7.7.1          | 控制传输 (Control Transfer)<br>中断传输 (Interrupt Transfer) |     |

|   | 7.7.2<br>7.7.3 | 大型                                                   |     |

|   | 7.7.4          | 控制事务 (Control Transactions)                          |     |

|   | 7.7.5          | 批量输入事务(Bulk IN Transactions)                         |     |

|   | 7.7.6          | 批量输出事务(Bulk OUT Transactions)                        |     |

|   | 7.7.7          | 中断事务(Interrupt Transactions)                         |     |

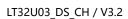

| 8 | 内部闪存           | 字模块 (EFLASH)                                         |     |

|   |                | <u></u>                                              |     |

|   |                |                                                      |     |

|   | 1014           |                                                      |     |

|    | 8.3  | 框图             |                                                          | 235 |

|----|------|----------------|----------------------------------------------------------|-----|

|    | 8.4  | 工作             | 模式                                                       | 236 |

|    | 8.5  | 内存             | 映射和寄存器                                                   | 236 |

|    | 8    | 3.5.1          | 内存映射                                                     | 236 |

|    | 8    | 3.5.2          | 寄存器描述                                                    | 238 |

|    | 8.6  | 功能             | 描述                                                       | 249 |

|    | 8    | 3.6.1          | 编程和擦除操作                                                  | 249 |

|    | 8    | 3.6.2          | FLASH 擦除流程说明                                             | 249 |

|    | 8    | 3.6.3          | FLASH 编程流程说明                                             | 249 |

|    | 8.7  | 中断             | 描述                                                       | 249 |

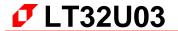

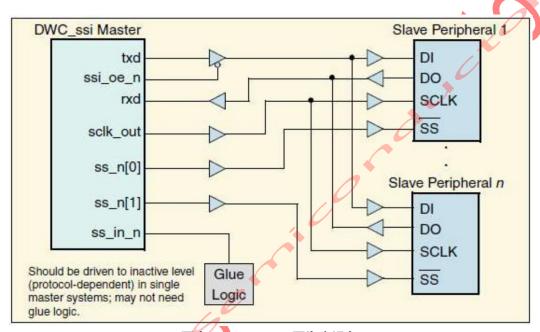

| 9  | 同步   | 串行             | 接口(SSI)                                                  | 250 |

|    | 9.1  | 概述             |                                                          | 250 |

|    | 9.2  | 特性             |                                                          | 250 |

|    | 9.3  | 操作             | 模式                                                       | 250 |

|    | 9.4  | 框图             |                                                          | 251 |

|    | 9.5  |                | 射和寄存器                                                    |     |

|    |      | ).5.1          | 内存映射                                                     | 251 |

|    |      | 9.5.2          | 寄存器描述                                                    |     |

|    | 9.6  | 功能             | 描述                                                       |     |

|    |      | 9.6.1          | 主模式                                                      | 288 |

|    | 9    | 0.6.2          | 时钟比率                                                     |     |

|    | 9    | 9.6.3          | 接收和发送 FIFO 缓存                                            | 289 |

|    | 9    | 0.6.4          | DMA 操作                                                   | 289 |

|    | 9    | 9.6.5          | 扩展 SPI 模式                                                |     |

|    |      | 9.6.6          | 芯片内执行 (XIP) 模式                                           |     |

|    |      | 9.6.7          | XIP 中的连续传输模式                                             |     |

|    |      |                | XIP 操作中的数据预取                                             |     |

|    |      | 中断             |                                                          |     |

|    |      | 9.7.1          | 发送 FIFO 空中断(ssi_txe_intr)                                |     |

|    |      | 0.7.2          | 发送 FIFO 溢出中断(ssi_txo_intr)                               |     |

|    |      | ).7.3<br>).7.4 | 接收 FIFO 完全中断(ssi_rxf_intr)                               |     |

|    |      | 9.7.4          | 接收 FIFO 溢出中断(ssi_rxo_intr)<br>接收 FIFO 下溢中断(ssi_rxu_intr) |     |

|    |      | ).7.6          | 组合中断请求(ssi intr)                                         |     |

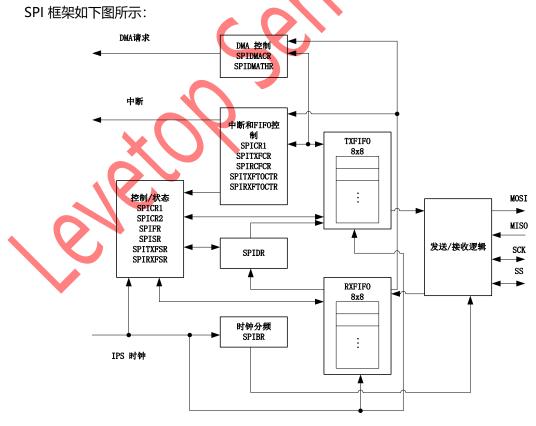

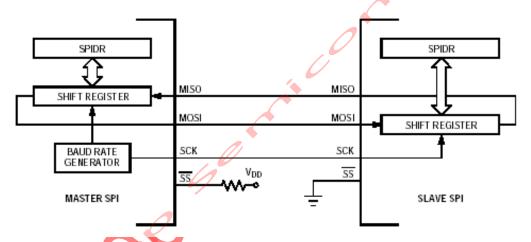

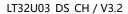

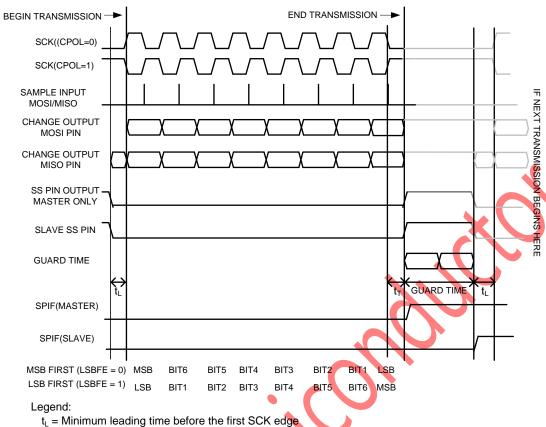

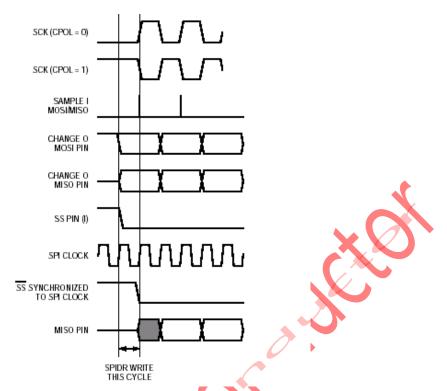

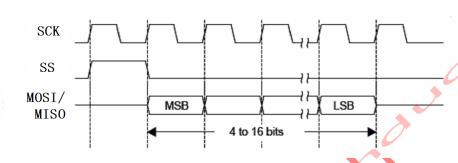

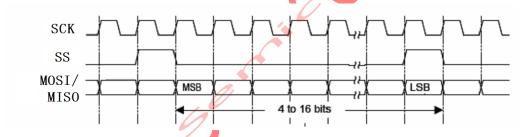

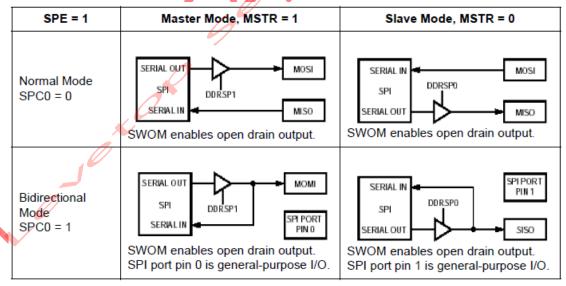

| 10 |      |                | 模块 (SPI)                                                 |     |

| -  |      |                |                                                          |     |

|    |      |                |                                                          |     |

|    | 10.2 | コマに            |                                                          | 293 |

|    |      |                | LT32U03_DS_CH / V3.2                                     |     |

|    | 10.3 框图 293                                    |     |

|----|------------------------------------------------|-----|

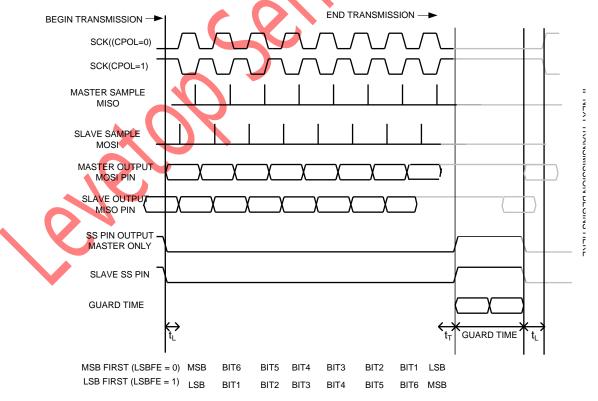

|    | 10.4 工作模式                                      | 294 |

|    | 10.5 外部管脚                                      | 294 |

|    | 10.5.1 MISO (主机输入/从机输出)                        | 294 |

|    | 10.5.2 MOSI (主机输出/从机输入)                        |     |

|    | 10.5.3 SCK (串行时钟)                              | 294 |

|    | 10.5.4 SS(从机选择)                                | 295 |

|    | 10.6 内存映射及和寄存器                                 | 296 |

|    | 10.6.1 内存映射                                    |     |

|    | 10.6.2 寄存器描述                                   |     |

|    | 10.7 功能描述                                      | 320 |

|    | 10.7.1 主机模式                                    | 320 |

|    | 10.7.2 从机模式                                    |     |

|    | 10.7.3 FIFO 操作                                 | 322 |

|    | 10.7.4 传输格式                                    | 322 |

|    | 10.7.5 SPI 波特率                                 |     |

|    | 10.7.6 从机选择 (SS) 输出                            |     |

|    | 10.7.7 双向模式                                    | 327 |

|    | 10.7.8 DMA 操作                                  | 328 |

|    | 10.7.9 高速模式                                    | 328 |

|    | 10.7.10 低功耗模式选项                                |     |

|    | 10.7.11 复位                                     |     |

|    | 10.8 中断描述                                      | 330 |

|    | 10.8.1 模式错误(MODF)中断                            | 330 |

|    | 10.8.2 EOT 中断(EOTF)                            | 330 |

|    | 10.8.3 帧丢失中断(FLOST)                            | 330 |

|    | 10.8.4 TXFIFO 超时中断(TXFTO)                      | 330 |

|    | 10.8.5 \TXFIFO 溢出中断 (TXFOVF)                   | 330 |

|    | 10.8.6 TXFIFO 下溢中断 (TXFUDF)                    | 331 |

| •  | 10.8.7 TXFIFO 服务中断标志(TXFSER)                   | 331 |

|    | 10.8.8 TXFIFO 超时中断                             | 331 |

|    | 10.8.9 RXFIFO 超时中断(RXFTO)                      | 331 |

|    | 10.8.10 RXFIFO 溢出中断(RXFOVF)                    | 331 |

|    | 10.8.11 RXFIFO 下溢中断 (RXFUDF)                   | 331 |

|    | 10.8.12 RXFIFO 服务中断标志(RXFSER)                  | 331 |

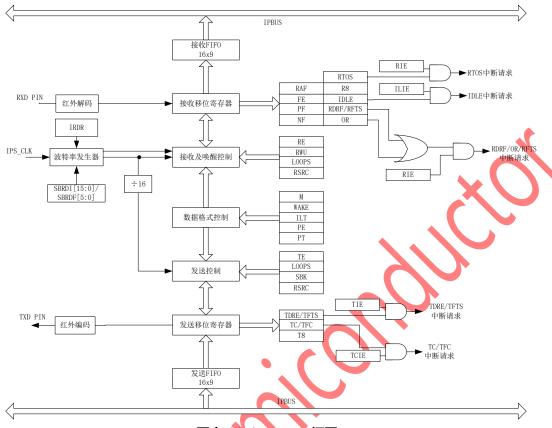

| 11 | 通用异步收发器 (UART)                                 | 332 |

|    | 11.1 概述                                        | 332 |

|    | 11.2 特性                                        |     |

|    | · ··—   'J   ································· | JJL |

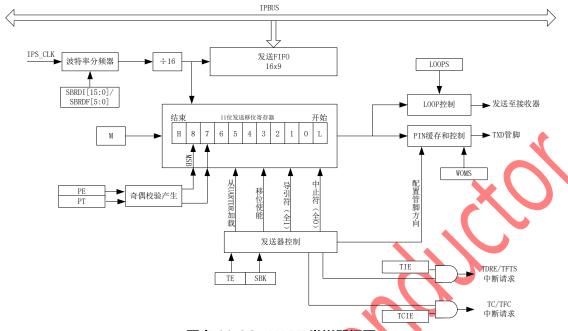

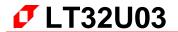

| 11.3 框图 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 333 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 11.4 工作 | 模式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 333 |

| 11.4.1  | 瞌睡模式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 333 |

| 11.5 外部 | 管脚                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 334 |

| 11.5.1  | RXD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 334 |

| 11.5.2  | TXD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 334 |

| 11.5.3  | RTSN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 334 |

| 11.5.4  | CTSN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 334 |

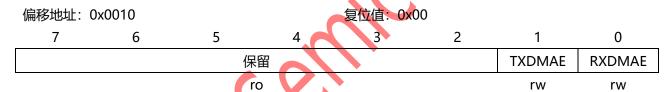

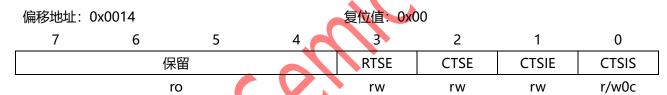

| 11.6 内存 | 映射和寄存器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 335 |

| 11.6.1  | 内存映射                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 335 |

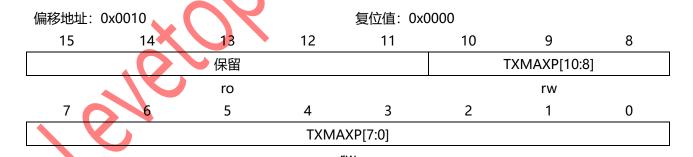

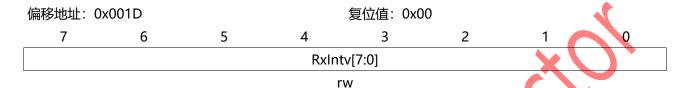

| 11.6.2  | 寄存器描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 336 |

| 11.7 功能 | 描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 359 |

| 11.7.1  | 数据格式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 359 |

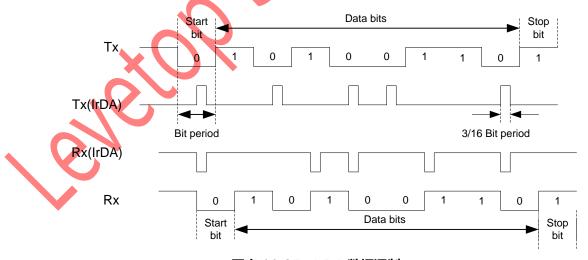

| 11.7.2  | 串行红外 (SIR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 360 |

| 11.7.3  | FIFO 操作                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 361 |

| 11.7.4  | 波特率计算                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 11.7.5  | 发送器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

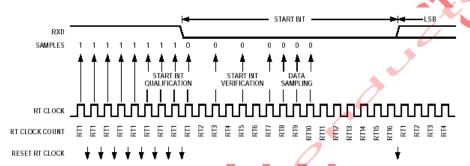

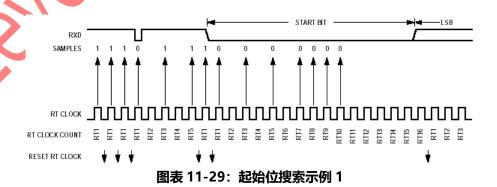

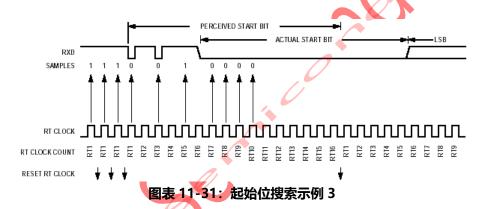

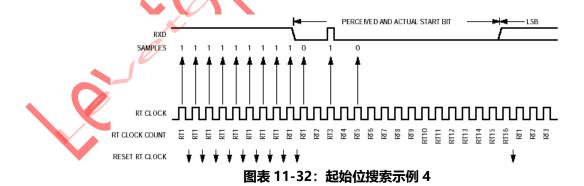

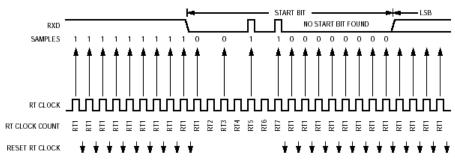

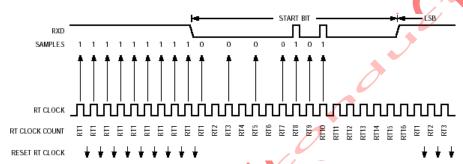

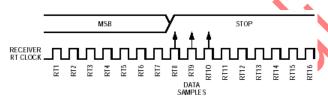

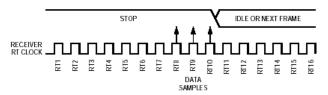

| 11.7.6  | 接收器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 11.7.7  | 1 ->035[6] 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 11.7.8  | 环路操作                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 11.7.9  | ×11 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 0000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 000 = 0 |     |

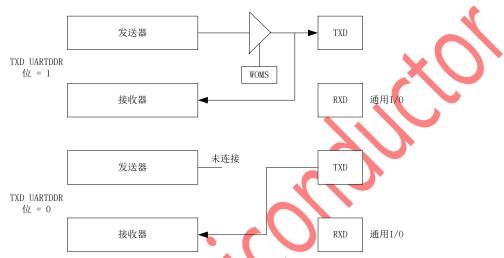

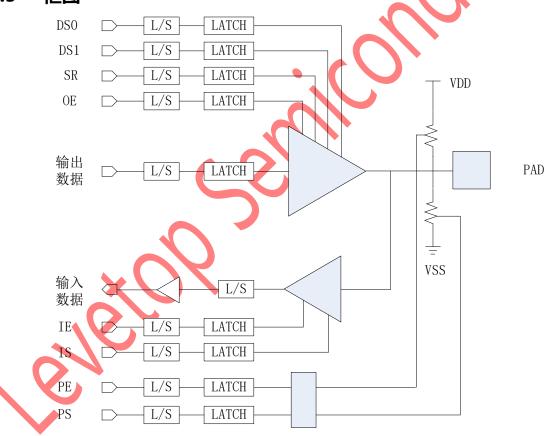

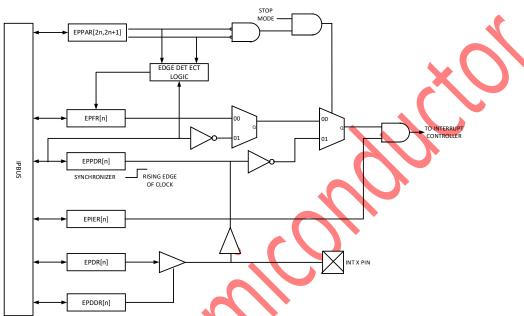

|         | I/O 端口                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|         | 复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 376 |

| 11.8 中断 | 描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 377 |

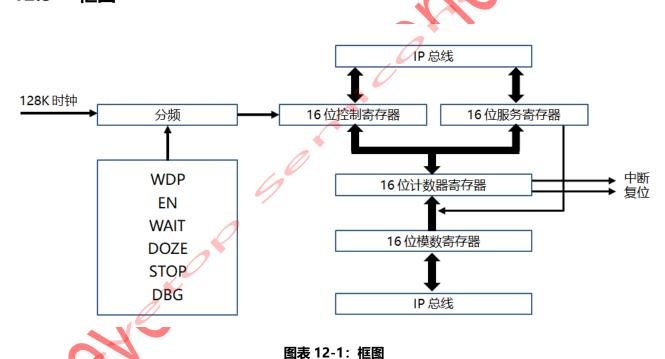

| 12 计时器模 | 缺(TC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 378 |

| 12.1 概述 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 378 |

| 12.2 特性 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 378 |

| 12.3 框图 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 378 |

| 12.4 工作 | 模式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 378 |

| 12.4.1  | 等待模式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |