## 1.5A Ultra-small Load Switch with Slew Rate Control

## **FEATURES**

Integrated P-channel MOSFET load switch

Input voltage: 1.2V to 5.5V

1.5A maximum continuous switch current

Switch on-resistance(typ.):

Rdson= $50m\Omega$  at  $V_{IN}=5.5V$

Rdson= $56m\Omega$  at  $V_{IN}=4.2V$

Rdson= $64m\Omega$  at  $V_{IN}=3.3V$

Rdson= $78m\Omega$  at  $V_{IN}=2.5V$

Rdson=109m $\Omega$  at  $V_{\text{IN}}$ =1.8V

Rdson=225mΩ at V<sub>IN</sub>=1.2V

Controlled slew rate to limit inrush current

Internal EN Pull-Down Resistor

Quick output discharge

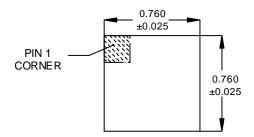

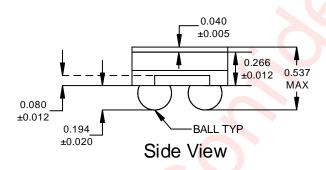

FOWLP 0.76mm×0.76mm×0.50mm-4B package

#### **APPLICATIONS**

- Smartphones and Tablets

- Portable Devices

- Wearables

## **GENERAL DESCRIPTION**

The AW35121 is a load switch with output slew rate control. The device integrates a  $64m\Omega$  (typ.) P-channel MOSFET, which can operate over a wide input range of 1.2V to 5.5V.

The AW35121 features output slew rate control, limiting inrush current during turn-on to protect downstream devices.

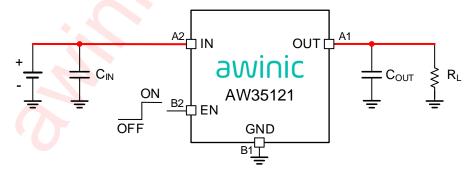

## TYPICAL APPLICATION CIRCUITS

Figure 1 Typical Application circuit of AW35121

1

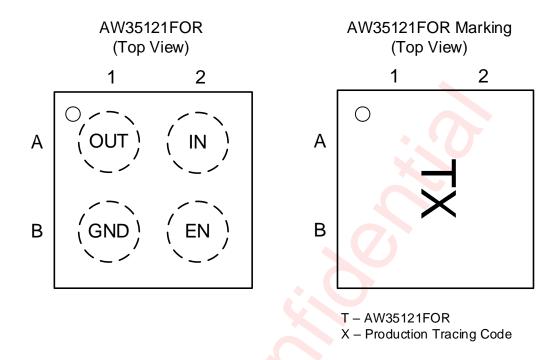

# PIN CONFIGURATION AND TOP MARK

Figure 2 Pin Configuration and Top Mark

## **PIN DEFINITION**

| Pin | Name | Description                                                                    |

|-----|------|--------------------------------------------------------------------------------|

| A1  | OUT  | Switch output                                                                  |

| A2  | IN   | Switch input and power supply                                                  |

| B1  | GND  | Device ground                                                                  |

| B2  | EN   | Switch control input, active high, internal $6.85 M\Omega$ pull down resistor. |

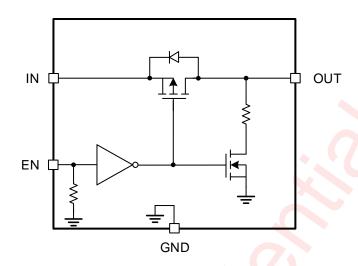

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 3 Functional Block Diagram

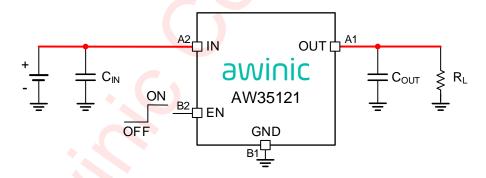

# **TYPICAL APPLICATION CIRCUITS**

Figure 4 Typical Application circuit of AW35121

# **ORDERING INFORMATION**

| Part Number | Temperature | Package                       | Marking | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery<br>Form                |

|-------------|-------------|-------------------------------|---------|----------------------------------|------------------------------|---------------------------------|

| AW35121FOR  | -40°C∼85°C  | FOWLP<br>0.76mm×0.76<br>mm-4B | Т       | MSL1                             | ROHS+HF                      | 3000 units/<br>Tape and<br>Reel |

# **ABSOLUTE MAXIMUM RATINGS**(NOTE1)

| PARAMETER                       | RANGE                                |               |  |  |  |  |

|---------------------------------|--------------------------------------|---------------|--|--|--|--|

| Supply Voltage Rai              | Supply Voltage Range V <sub>IN</sub> |               |  |  |  |  |

| Input Voltage Range             | Input Voltage Range EN               |               |  |  |  |  |

| Output Voltage Range            | OUT                                  | -0.3V to 6V   |  |  |  |  |

| Maximum Continuous Switch Curre | ent for VIN ≥ 2V <sup>(NOTE 2)</sup> | 1.5A          |  |  |  |  |

| Maximum Peak Switch Current for | or VIN $\geq 2.5V^{(NOTE 3)}$        | 2A            |  |  |  |  |

| Junction-to-ambient Thermal R   | esistance θ <sub>JA</sub> (NOTE 4)   | 184°C/W       |  |  |  |  |

| Operating Free-air Tempe        | rature Range                         | -40°C to 85°C |  |  |  |  |

| Maximum Junction Temp           | 150°C                                |               |  |  |  |  |

| Storage Temperatu               | -65°C to 150°C                       |               |  |  |  |  |

| Lead Temperature (Solderin      | 260°C                                |               |  |  |  |  |

|                                 |                                      |               |  |  |  |  |

| HBM (Human Body Mo              | ±2kV                                 |               |  |  |  |  |

| CDM(Charged Device M            | ±1.5kV                               |               |  |  |  |  |

| MM(Machine Mode                 | ±200V                                |               |  |  |  |  |

|                                 |                                      |               |  |  |  |  |

| Latch-Up <sup>(NOTE</sup>       | Latch Lin (NOTE 8)                   |               |  |  |  |  |

| Εαιοπ-Ορ                        |                                      | -IT: -200mA   |  |  |  |  |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: Limited by thermal design.

NOTE3: Limited by thermal design, and tested in 10ms width pulse current.

NOTE4: Thermal resistance from junction to ambient is highly dependent on PCB layout.

NOTE5: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin. Test method: ESDA/JEDEC JS-001-2017.

NOTE6: All pins. Test Condition: ESDA/JEDEC JS-002-2014.

NOTE7: All pins. Test Condition: JESD22-A115C.

NOTE8: Test Condition: JESD78E.

## RECOMMENDED OPERATING CONDITIONS

| Symbol          | Parameter               | Min. | Тур. | Max.            | Unit |

|-----------------|-------------------------|------|------|-----------------|------|

| V <sub>IN</sub> | Input Voltage           |      |      | 5.5             | V    |

| VEN             | EN Voltage              | 0    |      | 5.5             | V    |

| Vout            | Output Voltage          |      |      | V <sub>IN</sub> | V    |

| CIN             | Input capacitance       |      | 1    |                 | μF   |

| Соит            | Output load capacitance | 0.1  | 1    |                 | μF   |

# **ELECTRICAL CHARACTERISTICS**

$T_A$  = -40°C to 85°C unless otherwise noted. Typical values are guaranteed for  $V_{IN}$  = 5V,  $C_{IN}$  = 1 $\mu$ F,  $I_{IN}$ ≤ 1.5A and  $T_A$  = 25°C.

| PARAMETER         |                                   | TEST CONDITION                                                                              | MIN      | TYP  | MAX | UNIT  |

|-------------------|-----------------------------------|---------------------------------------------------------------------------------------------|----------|------|-----|-------|

| INPUT (           | CURRENTS                          |                                                                                             |          |      |     |       |

|                   |                                   | V <sub>IN</sub> =3.3V, V <sub>EN</sub> =3.3V, I <sub>OUT</sub> =0A, T <sub>A</sub> =25°C    | 4        | 2    | 12  | nA    |

|                   | Input quiescent                   | V <sub>IN</sub> =3.3V, V <sub>EN</sub> =3.3V, I <sub>OUT</sub> =0A, T <sub>A</sub> =85°C    |          | 9    |     | nA    |

| lα                | current                           | V <sub>IN</sub> =5.5V, V <sub>EN</sub> =5.5V, I <sub>OUT</sub> =0A, T <sub>A</sub> =25°C    | <b>\</b> | 5    | 25  | nA    |

|                   |                                   | V <sub>IN</sub> =5.5V, V <sub>EN</sub> =5.5V, I <sub>OUT</sub> =0A, T <sub>A</sub> =85°C    |          | 10   |     | nA    |

|                   |                                   | V <sub>IN</sub> =1.2V, V <sub>EN</sub> =0V, T <sub>A</sub> =25°C                            |          | 2    |     | nA    |

|                   |                                   | V <sub>IN</sub> =1.8V, V <sub>EN</sub> =0V, T <sub>A</sub> =25°C                            |          | 2    |     | nA    |

|                   |                                   | V <sub>IN</sub> =3.3V, V <sub>EN</sub> =0V, T <sub>A</sub> =25°C                            |          | 4    | 44  | nA    |

|                   | Shutdown                          | V <sub>IN</sub> =4.0V, V <sub>EN</sub> =0V, T <sub>A</sub> =25°C                            |          | 7    |     | nA    |

| I <sub>SD</sub>   | current from IN                   | V <sub>IN</sub> =4.5V, V <sub>EN</sub> =0V, T <sub>A</sub> =25°C                            |          | 22   |     | nA    |

|                   | to GND                            | V <sub>IN</sub> =5.0V, V <sub>EN</sub> =0V, T <sub>A</sub> =25°C                            |          | 62   | 970 | nA    |

|                   |                                   | V <sub>IN</sub> =5.0V, V <sub>EN</sub> =0V, T <sub>A</sub> =55°C                            |          | 90   |     | nA    |

|                   |                                   | V <sub>IN</sub> =5.0V, V <sub>EN</sub> =0V, T <sub>A</sub> =85°C                            |          | 350  |     | nA    |

|                   |                                   | $V_{IN}=5.5V$ , $V_{EN}=0V$ , $T_A=25$ °C                                                   |          | 171  |     | nA    |

| ILEAKEN           | EN pin leakage<br>current         | V <sub>IN</sub> =0V, V <sub>EN</sub> =5.0V                                                  |          |      | 1.5 | μΑ    |

| R <sub>EN</sub>   | EN pin pull down resistor         | V <sub>EN</sub> =5.0V                                                                       |          | 6.85 |     | МΩ    |

| POWER             | SWITCH                            |                                                                                             |          |      |     |       |

|                   |                                   | V <sub>IN</sub> =5.5V, V <sub>EN</sub> =high, I <sub>OUT</sub> =200mA, T <sub>A</sub> =25°C |          | 50   |     |       |

|                   |                                   | V <sub>IN</sub> =4.2V, V <sub>EN</sub> =high, I <sub>OUT</sub> =200mA, T <sub>A</sub> =25°C |          | 56   |     |       |

| R <sub>dson</sub> | Internal switch<br>MOSFET on-     | V <sub>IN</sub> =3.3V, V <sub>EN</sub> =high, I <sub>OUT</sub> =200mA, T <sub>A</sub> =25°C |          | 64   |     | mΩ    |

| I <b>X</b> ason   | state<br>resistance               | V <sub>IN</sub> =3.0V, V <sub>EN</sub> =high, I <sub>OUT</sub> =200mA, T <sub>A</sub> =25°C |          | 68   | 120 | 11152 |

|                   |                                   | V <sub>IN</sub> =1.8V, V <sub>EN</sub> =high, I <sub>OUT</sub> =200mA, T <sub>A</sub> =25°C |          | 109  |     |       |

|                   |                                   | $V_{IN}$ =1.2V, $V_{EN}$ =high, $I_{OUT}$ =200mA, $T_A$ =25°C                               |          | 225  |     |       |

| R <sub>DIS</sub>  | Output<br>discharge<br>resistance | arge   VIN-3.3V, VEN-IOW, TA-23 C, 50                                                       |          | 75   | 100 | Ω     |

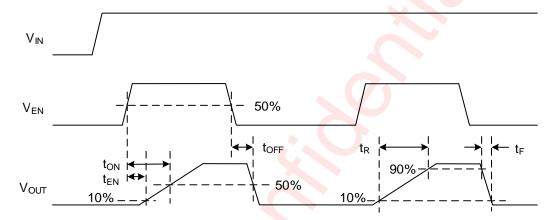

| <b>t</b> R        | Output rise time                  | V <sub>IN</sub> =3.6V, C <sub>OUT</sub> =1μF, R <sub>OUT</sub> =30Ω                         |          | 165  |     | μs    |

| t <sub>F</sub>    | Output fall time                  | $V_{IN}$ =3.6V, $C_{OUT}$ =1 $\mu$ F, $R_{OUT}$ =30 $\Omega$                                |          | 42   |     | μs    |

| ton               | Switch turn on time               | $V_{IN}$ =3.6 $V$ , $C_{OUT}$ =1 $\mu$ F, $R_{OUT}$ =30 $\Omega$                            |          | 238  |     | μs    |

| PA              | RAMETER                       | TEST CONDITION                                                      | MIN | TYP | MAX | UNIT |

|-----------------|-------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| toff            | Switch turn off time          | V <sub>IN</sub> =3.6V, C <sub>OUT</sub> =1μF, R <sub>OUT</sub> =30Ω |     | 12  |     | μs   |

| t <sub>EN</sub> | Enable time                   | $V_{IN}$ =3.6V, $C_{OUT}$ =1 $\mu$ F, $R_{OUT}$ =30 $\Omega$        |     | 130 |     | μs   |

| VIH             | EN input high threshold level |                                                                     | 1.2 |     |     | V    |

| VIL             | EN input low threshold level  |                                                                     |     |     | 0.5 | V    |

## **TIMING DIAGRAM**

Figure 5 AW35121 Timing Diagram

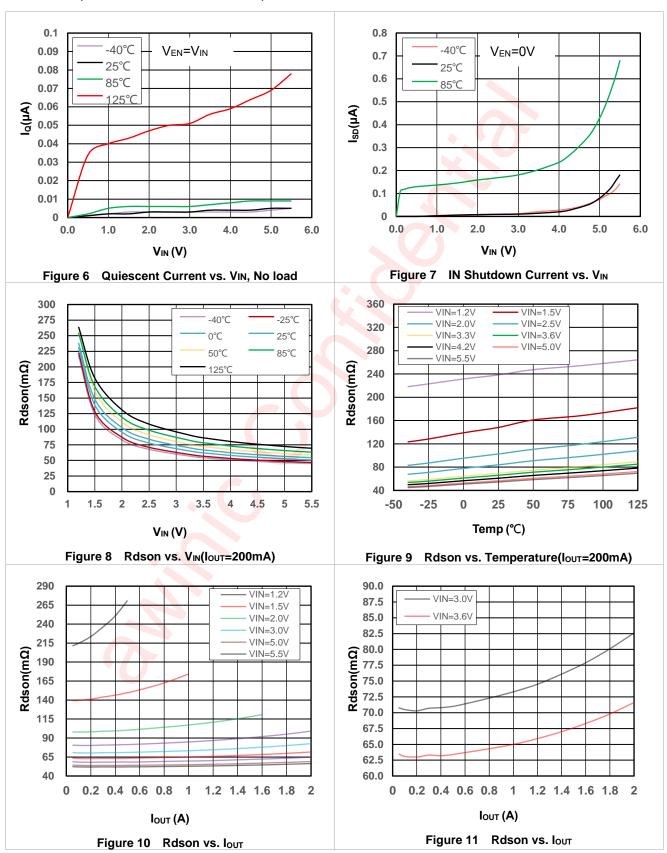

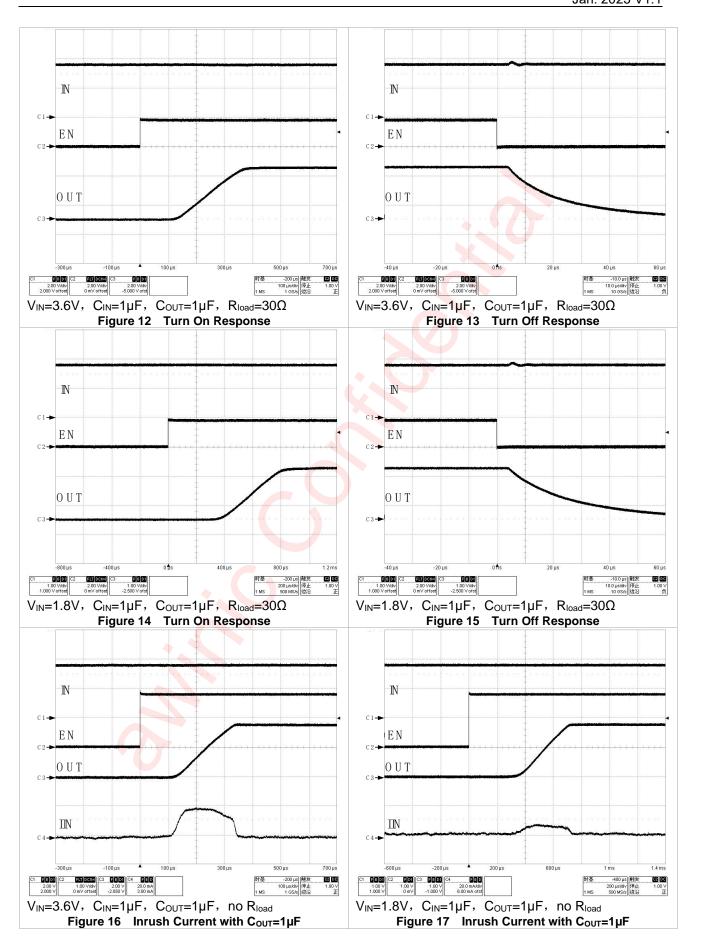

## **TYPICAL CHARACTERISTICS**

Ambient temperature is 25°C,  $C_{IN} = C_{OUT} = 1\mu F$ , unless otherwise noted.

## **DETAILED FUNCTIONAL DESCRIPTION**

The AW35121 integrates a high side P channel MOSFET load switch, and provides a low on-resistance for a low voltage drop across the device. A controlled slew rate is used in applications to limit the inrush current. The part can be turned on, with a supply voltage from 1.2V to 5.5V.

#### **TURN ON/OFF CONTROL**

Enable pin is active high. The device is opened when EN pin is tied low (disable) or pulled down by internal  $6.85M\Omega$  resistor, forcing PMOS switch off. The IN/OUT path is activated with a minimum Vin of 1.2V and EN forced to high level.

**Table 1. Functional Table**

| EN   | IN to OUT | OUT to GND |

|------|-----------|------------|

| Low  | OFF       | ON         |

| High | ON        | OFF        |

#### **SLEW RATE CONTROL**

When the switch is enabled, the device regulates the gate voltage of MOSFET, and controls the  $V_{OUT}$  slew rate during  $t_R$  to avoid a large input inrush current. The feature reduces the interference to the power supply.

#### QUICK OUTPUT DISCHARGE

The AW35121 includes the Quick Output Discharge (QOD) feature, in order to discharge the application capacitor connected on OUT pin. When EN pin is set to low level (disable state), a discharge resistance with a typical value of  $75\Omega$  connected between the output and ground, pulls down the output and prevents it from floating.

## **APPLICATION INFORMATION**

#### POWER SUPPLY RECOMMENDATIONS

The device is designed to operate with a  $V_{IN}$  range of 1.2V to 5.5V. This supply must be well regulated and placed as close to the device terminals as possible. It must also be able to withstand all transient and load currents, using a recommended input capacitance of  $1\mu F$  if necessary. If the supply is located more than a few inches from the device terminals, additional bulk capacitance may be required in addition to the ceramic bypass capacitors. If additional bulk capacitance is required, an electrolytic, tantalum, or ceramic capacitor of  $10\mu F$  may be sufficient.

#### MANAGING INRUSH CURRENT

When the switch is enabled, the output capacitors must be charged up from 0V to  $V_{IN}$ . A input inrush current will appear. The Inrush current can be calculated using Equation 1:

$$linrush = Cout \frac{dVout}{dt}$$

(1)

where:

- C<sub>OUT</sub> = Output capacitance

- dV<sub>OUT</sub> = Output voltage, equals to V<sub>IN</sub>

- dt = Rise time t<sub>R</sub>.

The AW35121 offers a controlled slew rate for minimizing inrush current.

#### **POWER DISSIPATION**

The power dissipation produced by the power MOSFET Rdson in ON-state can be calculated with the following equation:

$$P_{D} = Rdson \times (I_{OUT})^{2}$$

(2)

Where:

- P<sub>D</sub> = Power dissipation (W)

- Rdson = Power MOSFET on resistance (Ω)

- Iout = Output current (A)

#### THERMAL CONSIDERATIONS

Main contributor in term of junction temperature T<sub>J</sub>(max) is the power dissipation, and T<sub>J</sub>(max) should be restricted to 125°C under ON-state. Junction temperature is directly proportional to power dissipation in the device, it can be calculated by the following equation:

$$T_{J} = T_{A} + R_{\theta JA} \times P_{D} \tag{3}$$

Where:

- T<sub>J</sub> = Junction temperature of the device

- T<sub>A</sub> = Ambient temperature

- P<sub>D</sub> = Power dissipation of the device

- ReJA = Junction to ambient thermal resistance. This parameter is highly dependent on board layout.

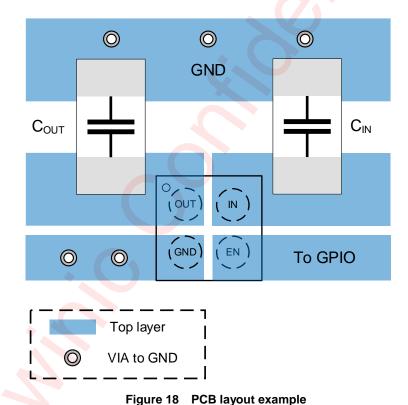

## **PCB LAYOUT CONSIDERATION**

AW35121 is a low ON-Resistance load switch. In order to obtain the optimal performance, PCB layout should be considered carefully. Here are some guidelines:

- 1. All the peripherals should be placed as close to the device as possible. Place the input capacitor  $C_{IN}$  on the top layer (same layer as the AW35121) and close to IN pin, and place the output capacitor  $C_{OUT}$  on the top layer (same layer as the AW35121) and close to OUT pin.

- 2. The AW35121 integrate an up to 1.5A rated PMOS FET, and the PCB design rules must be respected to properly evacuate the heat out of the silicon. By increasing PCB area, especially around IN and OUT pins, the  $R\theta_{JA}$  of the package can be decreased, allowing higher power dissipation. Blue bold paths on Figure 18 are power lines that will flow large current, please route them on PCB as straight, wide and short as possible.

- 3. Use rounded corners on the power trace from the power supply connector to AW35121 to decrease EMI coupling.

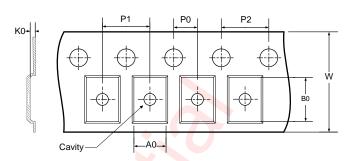

## TAPE AND REEL INFORMATION

# REEL DIMENSIONS D1 0

#### TAPE DIMENSIONS

- A0: Dimension designed to accommodate the component width

- B0: Dimension designed to accommodate the component length

- K0: Dimension designed to accommodate the component thickness

- W: Overall width of the carrier tape

- P0: Pitch between successive cavity centers and sprocket hole

- P1: Pitch between successive cavity centers

- P2: Pitch between sprocket hole

- D1: Reel Diameter

- D0: Reel Width

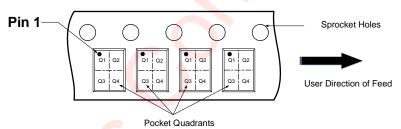

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Note: The above picture is for reference only. Please refer to the value in the table below for the actual size

#### **DIMENSIONS AND PIN1 ORIENTATION**

| D1   | D0   | A0   | В0   | K0   | P0   | P1   | P2   | W    | Pin1 Quadrant |

|------|------|------|------|------|------|------|------|------|---------------|

| (mm) | Fini Quadrant |

| 179  | 9.2  | 0.85 | 0.85 | 0.59 | 2    | 4    | 4    | 8    | Q1            |

All dimensions are nominal

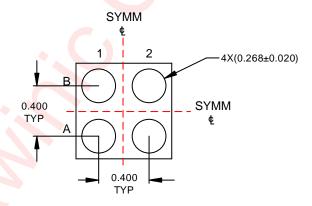

## **PACKAGE DESCRIPTION**

Top View

Bottom View

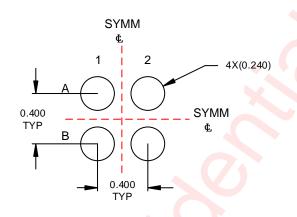

## **LAND PATTERN DATA**

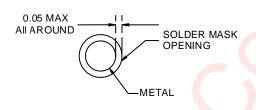

NON-SOLDER MASK DEFINED

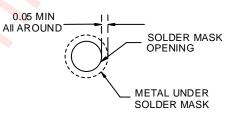

SOLDER MASK DEFINED

Unit: mm

# **REVISION HISTORY**

| Version                               | Date     | Change Record                                                                   |

|---------------------------------------|----------|---------------------------------------------------------------------------------|

| V1.0 Nov 2019 Datasheet V1.0 Released |          | Datasheet V1.0 Released                                                         |

| V1.1                                  | Jan 2023 | Modified Pin Configuration and Top Mark; Modified Figure 18 PCB layout example. |

### **DISCLAIMER**

Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.

16